電子發燒友網報道(文/梁浩斌)最近有不少關于HBM技術被應用到手機的消息,此前有消息稱蘋果會在20周年iPhone,也就是2027年推出使用HBM DRAM的iPhone手機,提高端側AI能力。近日著名博主《數碼閑聊站》又繼續爆料,華為會先于蘋果落地HBM DRAM。

但HBM在手機應用真的可行嗎?

從成本的角度來看,HBM首先在制造工藝上相比傳統的LPDDR更復雜。為了實現高帶寬,HBM是采用多層DRAM芯片通過硅通孔(TVS)垂直堆疊,比如HBM3E就是8層或12層;而這些DRAM芯片通過微凸點(Microbumps)連接到基底的邏輯芯片,再通過硅中階層跟處理器集成。

其中TSV提供了高密度、低延遲的垂直互連,相比LPDDR5的平面布局,HBM的數據傳輸路徑更短,減少信號延遲和損耗。同時每層DRAM都擁有獨立通道,比如HBM3每個堆疊支持8-16個通道,每個通道有128位寬的總線。相比之下,LPDDR5通常只有2-4個通道(16-32位寬)。

總體來看,HBM的生產成本大約是LPDDR的2-3倍,這導致了其應用到智能手機將大幅提高整機成本,可能只有部分萬元以上旗艦機型具備應用條件。

另一方面影響HBM登陸智能手機的是空間。雖然HBM本身利用垂直堆疊的2.5D、3D封裝理論上是比LPDDR集成度更高,但需要額外的硅中介層和更復雜的電源管理模塊,這可能增加模組厚度或占用主板空間,與手機輕薄化設計趨勢存在一定沖突。

在功耗方面,在手機低負載場景下,HBM復雜的架構下靜態功耗較高,而LPDDR5專為低功耗場景設計,待機功耗極低,在低負載場景下HBM有一定的劣勢。HBM的優勢在于高數據吞吐量場景,例如,HBM3E在處理1TB/s數據時,功耗可能在5-10W范圍內,而LPDDR5在類似場景下可能因帶寬瓶頸導致約8-15W的更高功耗。

根據SK海力士和美光的數據,8層堆疊24GB的HBM3E動態功耗約2-3pJ/bit,待機功耗約1-2W,峰值功耗約8-12W;6400MHz、16GB的LPDDR5,動態功耗約4-6pJ/bit,待機功耗約0.5-1W,峰值功耗約4-8W。

而在混合負載下,HBM的高帶寬優勢可能被其靜態功耗抵消,而LPDDR5的低功耗設計在中等帶寬需求下表現均衡,實際功耗取決于具體工作負載和SoC優化。

當然也有可能未來會采用定制化的方案,比如Marvell此前推出的XPU與定制HBM集成封裝的方案,也能夠降低芯片尺寸和功耗;或是開發出低容量、低堆疊層數的HBM,這樣也能降低靜態功耗和成本,更適合手機的需求。

所以,HBM未來在手機中的應用可能更多是技術展示的形式,作為品牌的圖騰應用在部分高端的智能手機上。尤其是在AI驅動的邊緣計算和AR/VR場景下,華為、蘋果等大廠可能會有動力去推動HBM的端側應用,通過高帶寬和低延遲支持本地化大模型推理或沉浸式體驗。而成本和空間問題可通過提高價格和優化設計緩解,但在實際應用中,還需解決散熱和SoC兼容性等挑戰。

-

HBM

+關注

關注

2文章

431瀏覽量

15831

發布評論請先 登錄

淺談錫膏在手機制造上的作用

UWB 智能門鎖系統在現有手機生態下的可行性分析

CW32L083RBT6在手機APP無線溫控器應用優勢

搭建soc時候,可以內部接并行的flash IP,寫了控制接口,轉換接口,這可行嗎?

HBM技術在CowoS封裝中的應用

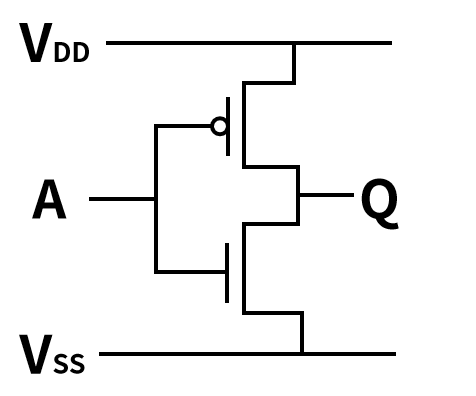

CMOS的邏輯門如何應用在電路中

晶臺光耦在手機PD快充上的應用

比肩HBM,SOCAMM內存模組即將商業化

人臉識別終端應用在不同領域,有什么優勢和注意事項?

HBM應用在手機上,可行嗎?

HBM應用在手機上,可行嗎?

評論