軟件仿真(Simulation),原型驗證(Prototyping),以及硬件仿真 (Emulation),是當前主要的三種有效的驗證方法,在芯片前端設計的功能性驗證階段起到了關鍵的作用。

近年來,由于大數據處理和AI芯片設計規模的擴大,以及市場競爭激烈導致的快速迭代需求,越來越多的芯片設計公司開始選擇硬件仿真,以提高芯片驗證效率,縮短芯片開發周期。

相較于軟件仿真和原型驗證,硬件仿真具有可支持設計容量大、擴展性好、工程構建時間短、仿真速度快、調試能力強、驗證場景豐富等特點,適合大型設計從模塊級、芯片級到系統級的仿真驗證。

硬件仿真驗證模式

硬件仿真支持的豐富的驗證模式,可以滿足芯片設計不同階段的驗證需求,常用于架構設計、前期開發、模塊開發、IP開發、系統深度調試等芯片開發階段。

常見的仿真驗證模式,主要包括:電路內仿真(In-Circuit Emulation,ICE仿真),事務級的仿真加速(Transaction Based Acceleration,TBA仿真),以及混合仿真(QEMU)等。在不同的芯片設計階段,可以選擇合適的仿真加速方法,來提升驗證效率。

電路內仿真(In-Circuit Emulation,ICE仿真)

電路內仿真是使用在線仿真器(In-Circuit Emulator)進行具有特定調試技術的硬件仿真加速,其中在線仿真器代替實際硬件以便在實際系統環境中運行和測試。此方法允許工程師在實際的系統環境中進行測試和調試,而無需等待硬件原型的生產。這可以大大加速開發過程,并提高最終產品的質量。

事務級的仿真加速(Transaction Based Acceleration,TBA仿真)

事務級的仿真加速是通過使用總線功能模型Bus Functional Model (BFM),將運行在軟件上的Testbench和運行在硬件仿真系統中的DUT進行事務級層面的軟硬聯合驗證。即在主機上運行的Testbench和在硬件仿真上運行的DUT是通過無時序的事物進行交互。通過這種方法,仿真速度可以大大提高,因為仿真的焦點從每個時鐘周期的具體操作轉移到了更高級別的事務。這種方法常用于大規模系統的設計驗證,可以提高仿真的效率。

混合仿真(Hybrid Emulation)

混合仿真是將硬件仿真與軟件仿真相結合,允許工程師同時觀察和調試系統的硬件和軟件部分。混合仿真可以提供對整個系統的全面視圖,并可以在更高的抽象級別進行仿真,可以進一步提高仿真速度和效率。是IC設計團隊在早期架構優化、軟硬件協同開發、RTL級仿真驗證中的重要驗證方法。

這些驗證模式都是硬件仿真的一部分或者擴展,它們提供了不同層次和粒度的仿真和驗證能力,以適應不同的設計需求和驗證目標。在實際的設計和驗證過程中,工程師可能會根據需要選擇適合的仿真方法。

混合仿真(QEMU)

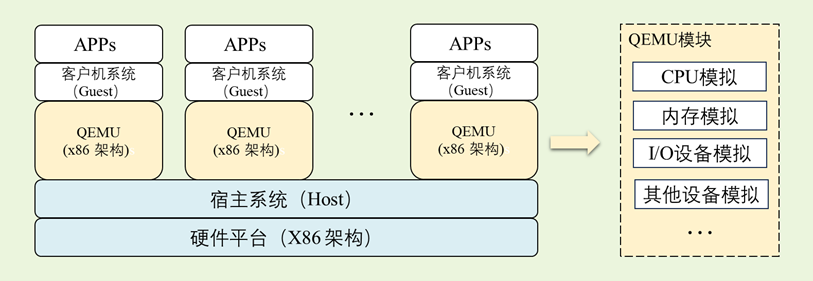

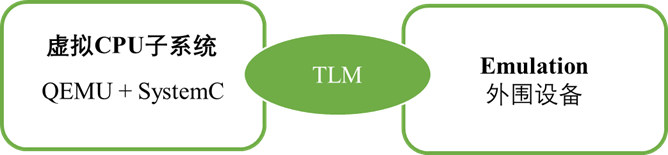

QEMUQEMU是純軟件實現的一個開源、跨平臺的虛擬化模擬器,幾乎可以模擬任何硬件設備。通常是模擬一臺能夠獨立運行操作系統的虛擬機,混合仿真時虛擬機會以為自己和真實硬件進行數據交互,而該“硬件”實際上卻是QEMU模擬,QEMU 將這些指令轉譯給真正的硬件。本質上,虛擬出的每個虛擬機對應宿主系統(Host)上的一個QEMU進程,而虛擬機的執行線程(如 CPU 線程、I/O 線程等)對應QEMU進程的一個線程。 圖1 QEMU架構圖SystemCSystemC是一個支持系統建模的開源的C++ library。混合仿真驗證前,通常優先開發抽象SystemC模型(如TLM模型),然后將此模型轉化為RTL并基于此模型上開發軟件。在此過程中,軟硬件的諸多錯誤能盡早被發現,從而節省開發時間。使用QEMU和SystemC可以共同組成虛擬驗證平臺,實現SoC系統級建模。

圖1 QEMU架構圖SystemCSystemC是一個支持系統建模的開源的C++ library。混合仿真驗證前,通常優先開發抽象SystemC模型(如TLM模型),然后將此模型轉化為RTL并基于此模型上開發軟件。在此過程中,軟硬件的諸多錯誤能盡早被發現,從而節省開發時間。使用QEMU和SystemC可以共同組成虛擬驗證平臺,實現SoC系統級建模。

圖2 SystemC Simulation

基于QEMU的混合仿真驗證

混合驗證是一種方法,它在使用硬件仿真進行DUT仿真的同時,利用虛擬原型建立目標SoC環境,并進行相應軟硬件的協同開發調試。混合仿真是IC設計團隊在早期架構優化、軟硬件協同開發、RTL級仿真驗證中的重要工具。

基于QEMU和硬件仿真系統的混合仿真,是在硬件仿真系統和QEMU上同時運行SoC的不同設計模塊,在SoC整體架構硬件實現之前提供嵌入式軟件和硬件的協同仿真,為系統架構的優化、RTL的早期開發、以及嵌入式軟件開發,提供準確,即時的仿真驗證環境,有力推動產品開發周期左移,從而加速SoC的研發進程。

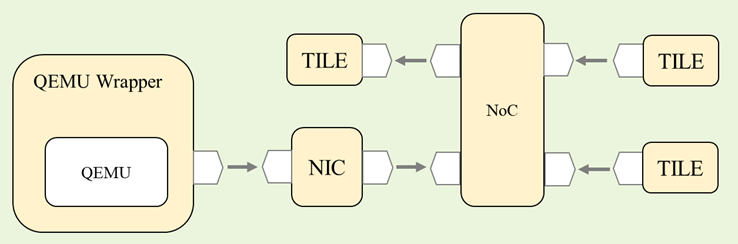

QEMU運行在Runtime Server上,一般通過SystemC實現TLM(Transaction Level Model)模型,提供虛擬CPU、Linux內核以及用戶態程序。QEMU通過標準SCEMI協議和硬件仿真器通信,硬件仿真器上可運行SOC外設等IP,從而實現完整的混合仿真環境。

圖3QEMU混合仿真

混合仿真帶來的好處

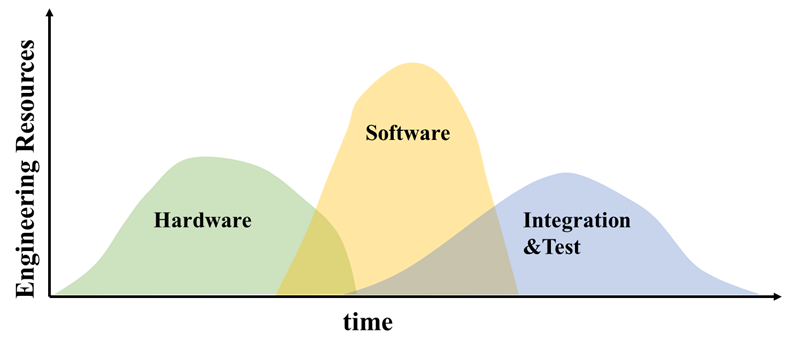

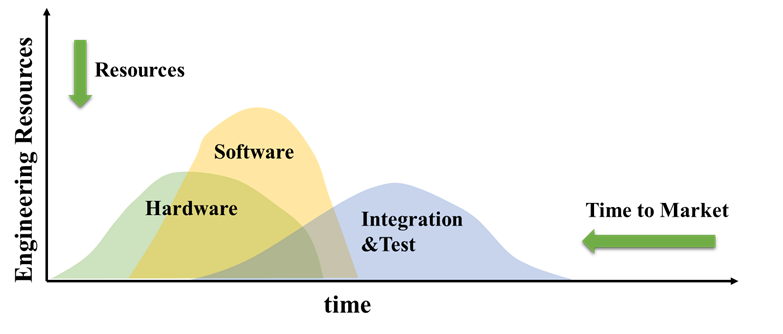

混合仿真帶來了諸多好處,主要表現在軟件開發和集成測試的工作可以大幅度提前,顯著地縮短了項目周期。在應用混合驗證之前,軟硬件開發和集成測試往往要等待硬件設計完成后才能開始,這將會導致項目周期延長。而在使用混合驗證之后,軟硬件開發和集成測試可以在硬件設計階段同時進行,這樣將會顯著地縮短整個項目周期。

圖4使用混合驗證前

圖5使用混合驗證后

基于OmniArk

和QEMU的混合仿真

思爾芯自主研發的OmniArk芯神鼎硬件仿真系統,采用超大規模可擴展陣列架構設計,設計容量最大10億門。支持TBA、ICE 、混合仿真等多種仿真驗證模式,可以滿足不同驗證場景需求。

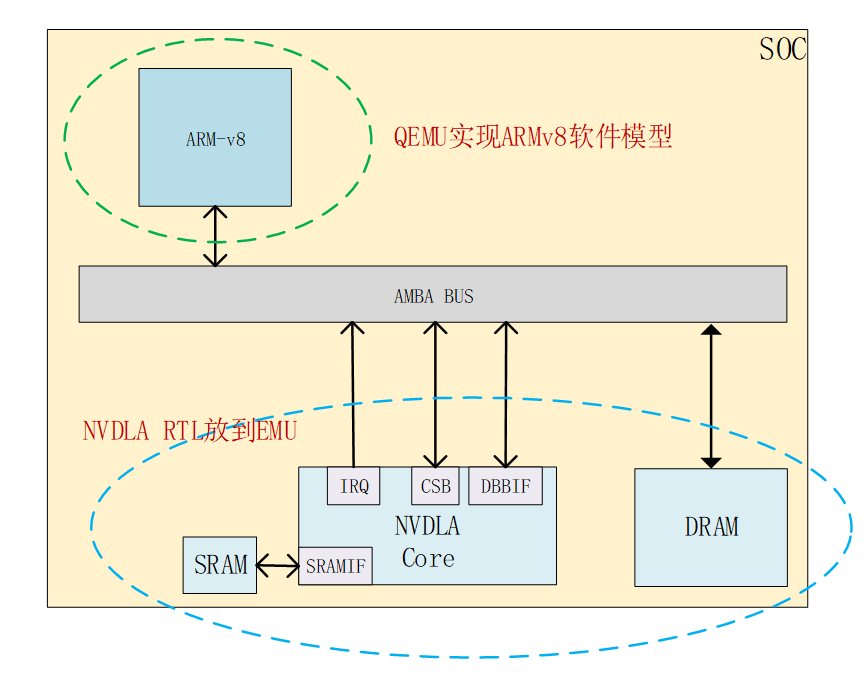

思爾芯提供的混合驗證解決方案,通過連接開源虛擬機QEMU工具和OmniArk芯神鼎硬件仿真系統,實現了虛擬原型硬件和嵌入式軟件協同混合驗證,為早期的設計架構的驗證優化、嵌入式軟件的協同開發、RTL級的仿真加速提供更準確、更及時的仿真驗證環境。以混合仿真一個SoC芯片設計為例。SoC整體系統架構如下圖所示,主要由ARMv8 CPU、AMBA BUS、NVDLA和DRAM等模塊組成。為了實現QEMU虛擬平臺與OmniArk芯神鼎硬件仿真系統的混合仿真,我們將NVDLA和DRAM移植到OmniArk芯神鼎硬件仿真系統中進行仿真,同時使用QEMU實現ARMv8的軟件模型。

圖7SoC系統框圖

在設計移植到OmniArk芯神鼎硬件仿真系統后,Runtime Server端采用QEMU模擬運行ARMv8,并通過TLM Wrapper將其掛載到AMBA總線上。OmniArk芯神鼎硬件仿真系統仿真運行NVDLA,通過AXI Transactor(簡稱Xtor)、GPIO Transactor掛載到AMBA總線上。Runtime Server和OmniArk芯神鼎硬件仿真系統之間通過SCE-MI協議進行軟硬件協同仿真。

圖8QEMU混合仿真系統框圖

- TLM Wrapper,建立一套基于TLM模型的通信機制,將QEMU包裝成TLM模型,使QEMU模擬的設備能夠與SystemC開發的模塊進行通信。

- AMBA Router,以軟件形式模擬AMBA總線,實現了標準的AMBA路由機制和仲裁機制,可將多個TLM模型連接并進行數據通信。

- AXI TLM,是一個基于AXI總線的TLM模型,負責將AXI接口設備適配到AMBA Router總線上。

- IRQ TLM,則是中斷TLM模型,負責將設備的中斷信號經TLM2C發送給QEMU模擬的CPU,由CPU作出響應處理。

總結

當前,許多全流程驗證工作都依賴于硬件仿真來完成。在早期,硬件仿真主要被用于代碼設計的后端階段,主要用于確認代碼功能的正確性。然而,隨著設計流程時間需求的加劇,更多的步驟開始被集成到硬件仿真中,包括早期的功耗分析、系統環境構建和邏輯調試等。

同時,硬件仿真系統的專用化趨勢日益顯著。對于那些需要處理大量數據,但算法相對單一的應用領域,例如加密算法和WIFI應用等,他們對仿真的需求正在逐步增大。在芯片設計過程中,根據設計的復雜性和特性,可能需要采用不同的仿真驗證模式。在芯片設計中,我們可能需要不同的仿真驗證模式以適應不同的設計復雜性和特性。因此,專用的硬件仿真技術提供了強大的支持,使硬件仿真具有更高的靈活性和適應性,滿足各種不同場景和需求的驗證任務。思爾芯自主研發的OmniArk芯神鼎硬件仿真系統,正是這種具有更高靈活性和適應性的硬件仿真系統,目前已在多個芯片設計企業成功使用。產品除了支持TBA、ICE 、混合仿真等多種仿真驗證模式外,還支持用戶設計的快速導入和全自動快速編譯、可以支持高速的仿真運行速度,同時具備強大的調試能力和對海量的數據處理能力,可以快速尋找和修復源代碼中潛在的深度錯誤和性能瓶頸。利用這個平臺,用戶可以更高效地進行芯片設計和優化,極大地提高了芯片設計的質量和效率。

-

仿真

+關注

關注

55文章

4526瀏覽量

138586 -

驗證平臺

+關注

關注

0文章

12瀏覽量

3089 -

qemu

+關注

關注

0文章

57瀏覽量

5976

發布評論請先 登錄

思爾芯2025年度成果回溯:拓技術疆土,促軟硬升級,見生態成效

思爾芯榮登“國產EDA工具口碑榜”,以“芯神瞳”原型驗證解決方案賦能芯片創新

在qemu上體驗芯來RISC-V處理器運行鴻蒙LiteOS-M內核

【喜報】芯神瞳原型驗證解決方案榮膺工博會“集成電路創新成果獎”

NVMe高速傳輸之擺脫XDMA設計23:UVM驗證平臺

如何在AMD Vitis Unified 2024.2中連接到QEMU

在AMD Versal自適應SoC上使用QEMU+協同仿真示例

NVMe高速傳輸之擺脫XDMA設計18:UVM驗證平臺

綠氫系統 PEM 電解槽直流接入仿真驗證深度解析

推動硬件輔助驗證平臺增長的關鍵因素

基于OmniArk芯神鼎硬件仿真系統和QEMU的混合驗證平臺

基于OmniArk芯神鼎硬件仿真系統和QEMU的混合驗證平臺

評論