硬件加速和基于FPGA的原型設計誕生于1980年代中期,開發(fā)者將當時初露頭角的現(xiàn)場可編程門陣列(FPGA)率先應用于硅前設計的原型驗證,由此催生了一種全新的驗證工具,打破了軟件仿真的主導局面。

最初,硬件加速的實現(xiàn)過程不僅復雜且依賴專業(yè)知識,因此發(fā)展受限。然而,在簡化啟動和調試方面,通過軟件與架構層面的持續(xù)優(yōu)化與創(chuàng)新,推動了這項技術的發(fā)展。從1990年代中期到21世紀初,硬件加速逐漸成熟,成為驗證復雜處理器和顯卡設計的關鍵方法。在這一時期,在線硬件加速(ICE)興起,它將被測設計(DUT)部署在預期的物理目標系統(tǒng)中,這種方法與FPGA原型設計密切相關。

硬件加速與FPGA原型設計的融合,形成了硬件輔助驗證(HAV)平臺,標志著下一階段的到來。HAV利用硬件加速實現(xiàn)了大規(guī)模設計的快速啟動和同步系統(tǒng)的全面調試——一個模塊中的一步操作會觸發(fā)整個設計的協(xié)同推進。FPGA原型設計則更注重執(zhí)行速度,能夠實現(xiàn)與最終設計非常接近的復雜異步操作。盡管這種方法提高了性能,但需要更長的啟動周期。與此同時,分割工具的進步使得大規(guī)模原型的開發(fā)突破了十億門的門檻。

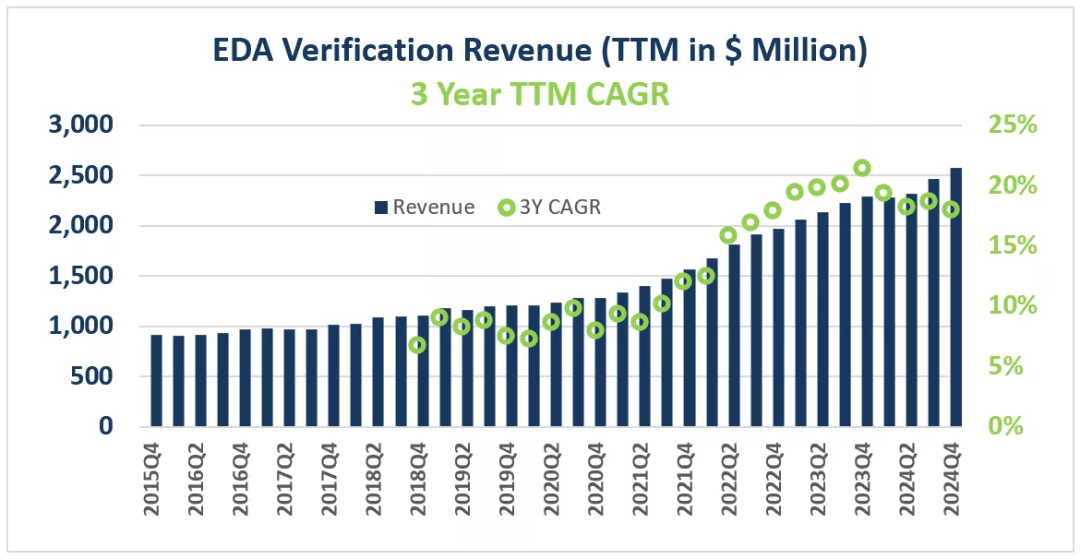

盡管HAV在2010年代中期之前發(fā)展相對停滯,但自2018年起,HAV的采用率大幅上升,總收入迅速增長,標志著HAV開始復興。如下圖所示,在整體驗證收入中,HAV是目前占比最大的組成部分。

推動HAV增長的因素

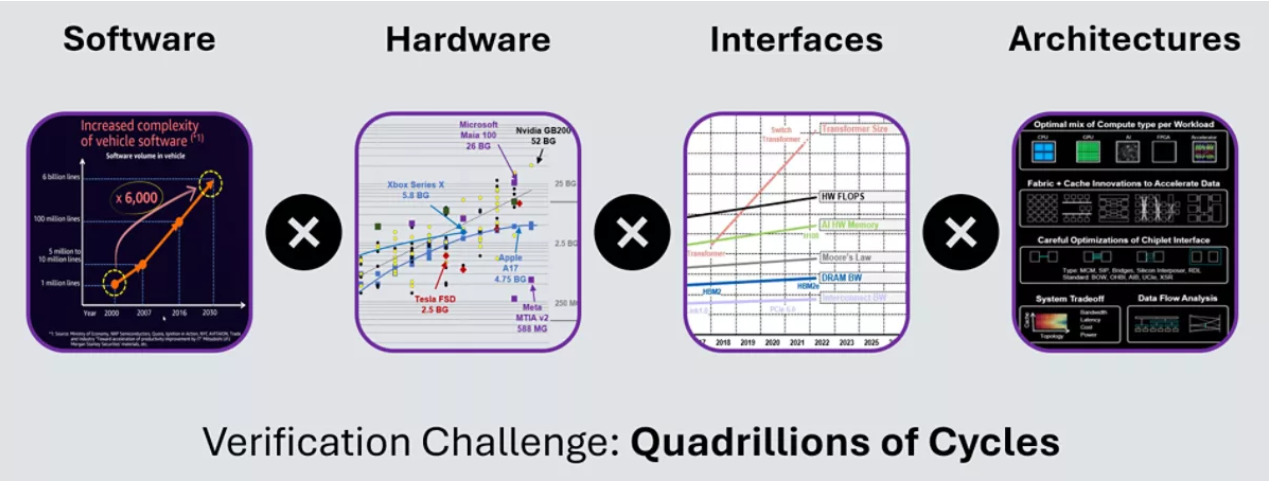

HAV增長的主要推動力在于當今片上系統(tǒng)(SoC)的硬件和軟件組件日益復雜。隨著硬件設計規(guī)模的擴大,完成全面驗證所需的周期數(shù)相應增加。軟件的日益密集也迫使進行更多測試,以確保功能和性能。將設計復雜度和軟件復雜度(即驗證周期數(shù))分別繪制在x軸和y軸上,得出的面積即代表總驗證工作量。總驗證工作量在兩個維度快速增長,凸顯出對HAV解決方案日益迫切的需求。

另一個同樣重要的增長推動力在于新型AI硬件的根本特性。與擅長運行軟件程序的傳統(tǒng)中央處理器(CPU)不同,AI加速器基于專為大規(guī)模并行計算設計的架構,以滿足機器學習算法的處理需求。

CPU與專用AI加速器之間的本質區(qū)別源于它們不同的設計理念和目標工作負載。CPU是通用計算的主力,針對指令順序處理進行了優(yōu)化,尤其擅長運行以逐步執(zhí)行任務為主的軟件應用程序。盡管如今的CPU集成了多個內核以實現(xiàn)并行處理,但其固有架構仍面向串行運算,在應對當前人工智能需求時存在擴展瓶頸。最尖端的服務器CPU,如AMD的EPYC系列就采用了這種設計,內核數(shù)高達192個,但在面對AI需求時仍顯不足。

相比之下,AI加速器(包括圖形處理單元GPU、張量處理單元TPU和定制專用集成電路ASIC)在架構上專為執(zhí)行AI算法而設計,能夠同時處理大型語言模型(LLM)中數(shù)以千億計的參數(shù)。AI加速器的核心優(yōu)勢在于能夠同時執(zhí)行大量計算,特別是神經(jīng)網(wǎng)絡計算中至關重要的矩陣乘法和卷積操作,需要并行處理海量數(shù)據(jù),而CPU通常難以勝任。

例如,英偉達的頂尖產(chǎn)品Blackwell GB202 GPU,擁有24,576個計算內核,就體現(xiàn)了這種范式轉變。然而,AI加速器的真正優(yōu)勢在于其集成到大規(guī)模系統(tǒng)中的能力。CPU的擴展受制于軟件和架構,而AI加速器則不同,可以通過高帶寬技術互連,形成統(tǒng)一的處理中心。英偉達的GB200 NVL72集成了72個Blackwell GPU和36個Grace CPU,有效地將單個系統(tǒng)內的AI內核總數(shù)推高至一百萬個以上。這種大規(guī)模并行處理能力對于運行復雜的AI模型至關重要,因為需要同時處理海量數(shù)據(jù)集并執(zhí)行復雜計算。

盡管存在架構差異,但CPU和AI加速器都需要通過執(zhí)行軟件工作任務,進行嚴格的硅前驗證。此過程涉及運行業(yè)界基準程序和最終用戶應用程序;AI加速器,還需要運行LLM。此外,內核間的協(xié)同一致性測試進一步擴展了驗證范圍。以RISC-V為例,驗證ISA擴展會進一步增加CPU硅前驗證的復雜性。由于每天需要多次迭代執(zhí)行軟件工作任務,因此為完成全面測試,需要數(shù)千萬億個驗證周期。

AI處理器的驗證

在驗證AI處理器時,一個獨特挑戰(zhàn)在于AI模型具有雙重運行模式:訓練和推理。訓練需要處理海量數(shù)據(jù),以對深嵌在多層深度神經(jīng)網(wǎng)絡內的網(wǎng)絡參數(shù)進行微調。該計算密集型階段可能持續(xù)數(shù)周甚至數(shù)月,要求達到每秒數(shù)PFLOP吞吐量和TB級內存帶寬。推理階段由于數(shù)據(jù)集較小,因此對原始計算的要求不高,但更加注重低延遲,以便在嚴格的能耗和成本約束下實現(xiàn)實時輸出。

這些運算的體量驚人。驗證AI硬件加速器和復雜計算集群(其中協(xié)同一致性至關重要)時,通常需要數(shù)千萬億個驗證周期,以確保性能、能效、準確性和可靠性達到預期。如此龐大的測試量遠遠超出了軟件仿真工具的能力,在面對AI工作任務的復雜性和并行性時也顯得力不從心。

▲導致千萬億個驗證周期需求的主要因素

HAV化解困局

隨著AI模型越來越復雜、工作負載規(guī)模愈加龐大,部署HAV平臺勢在必行。

硬件加速器和FPGA原型提供了周期精確、運行高速的環(huán)境運行這些工作負載,使開發(fā)者能夠在硅前階段識別并修正設計缺陷。

HAV持續(xù)增長的原因顯而易見:AI的興起引發(fā)了單靠軟件仿真已無法應對的驗證環(huán)節(jié)瓶頸。在通過實際工作負載來驗證復雜的AI硬件時,面對速度、容量和可擴展性的高要求,軟件仿真和HAV平臺的角色已然發(fā)生改變。盡管軟件仿真憑借強大的調試能力,在IP、模塊和子系統(tǒng)設計的驗證中仍不可替代,但HAV平臺已經(jīng)成為全系統(tǒng)、Multi-Die和芯粒(即系統(tǒng)之系統(tǒng),SoS)驗證的基石,可實現(xiàn)大規(guī)模的硅前驗證。

展望未來

推動HAV崛起的幾個關鍵趨勢,將繼續(xù)促進HAV的普及。首先,AI模型日益復雜,新型架構(尤其是在內存和通信接口方面快速演進的架構)不斷涌現(xiàn),將需要更強大且可擴展的驗證工具。其次,AI系統(tǒng)對能效和軟件安全日益重視,將推動HAV平臺的部署,用于在實際工作負載中對峰值和平均功耗進行精確分析并開展全面的安全驗證。再者,AI被廣泛應用于自動駕駛、醫(yī)療健康等各種場景,針對不同領域的定制化驗證方法將變得愈發(fā)重要。

為了滿足這些不斷變化的需求,HAV平臺必須采用多項關鍵創(chuàng)新。AI分析工具將提升錯誤檢測和根本原因分析能力,從而顯著提高驗證效率。基于云的硬件加速和原型驗證將提供可擴展性和可訪問性,使設計工作流程更加靈活。標準化的驗證方法和基準將促進行業(yè)協(xié)作與互操作性。在計算、AI訓練、邊緣AI、汽車、消費電子及有線/無線應用領域,由于驗證設置各不相同,模塊化驗證對于管理超過600億門級別的超大設計和復雜的SoS配置至關重要。此外,硬件加速和原型驗證的融合將帶來更順暢和一體化的驗證流程。

總之,AI的快速發(fā)展及軟件開發(fā)日益增長的復雜性與成本,直接促成了硬件輔助驗證平臺的復興。由于AI硬件加速器在大規(guī)模并行、高算力工作任務及性能與功耗方面的嚴苛要求,HAV已成為設計過程中的關鍵環(huán)節(jié)。

隨著AI不斷發(fā)展并全面滲透現(xiàn)代科技,HAV在確保性能、低功耗、準確性、可靠性和軟件安全方面的作用將愈發(fā)重要。通過持續(xù)創(chuàng)新并適應AI的發(fā)展趨勢,HAV平臺將在下一代硬件開發(fā)中繼續(xù)發(fā)揮關鍵作用。

-

FPGA

+關注

關注

1662文章

22472瀏覽量

638247 -

硬件

+關注

關注

12文章

3610瀏覽量

69112 -

AI

+關注

關注

91文章

40603瀏覽量

302270 -

新思科技

+關注

關注

5文章

972瀏覽量

52976

原文標題:AI 算力革命中,硬件輔助驗證(HAV)如何點亮硬件加速之路?

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

新思科技發(fā)布全新軟件定義硬件輔助驗證解決方案

SMT效率卡殼?別瞎忙了!這幾個關鍵因素才是提效核心!

三防漆干燥時間多久?影響固化速度的關鍵因素 |鉻銳特實業(yè)

軟件定義的硬件輔助驗證如何助力AI芯片開發(fā)

高導熱灌封膠如何驗證?詳解導熱系數(shù)的精準測試方法與影響因素 | 鉻銳特實業(yè)

地平線以算效構筑輔助駕駛的用戶體驗

如何選擇適合的國產(chǎn)X-Ray設備?5大關鍵因素分析

UPS電源—決定UPS電源性能的關鍵因素

選擇五號電池時的關鍵考慮因素

影響圖像采集卡性能的關鍵因素

選擇適合微機消諧器的關鍵因素

影響電機使用壽命的關鍵因素

硬件輔助驗證(HAV) 對軟件驗證的價值

影響接地電阻柜價格的關鍵因素?

推動硬件輔助驗證平臺增長的關鍵因素

推動硬件輔助驗證平臺增長的關鍵因素

評論