驅動半導體工業發展的動力是什么?是人們對自然學習語言、人工智能、自動駕駛、視頻監控、增強/虛擬現實、5G通信、個人醫療、可再生能源以及智能電網的需求。表面上看,這些需求五花八門,但透過現象看本質后,我們可以驚奇地發現他們存在許多共同點,比如數以億計的計算能力、無線網絡的擴展能力、高效的能源管理能力,以及多維感知的能力。而實現這些系統級能力的基礎是關鍵器件的性能升級,比如處理器的堆核升頻,網絡的異質互聯,以及感知層的提精降耗等等。

后摩爾時代,半導體產業面臨變革

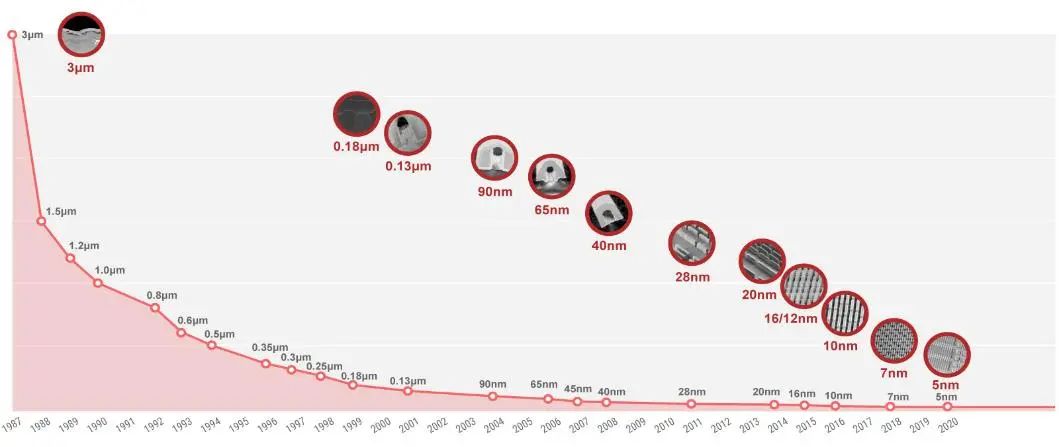

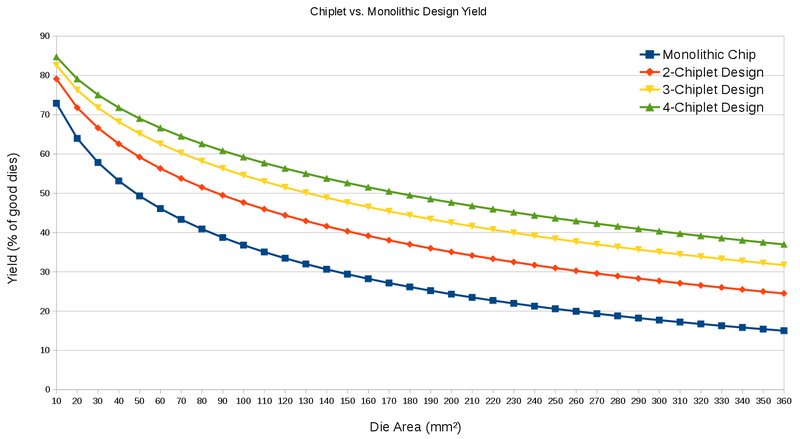

根據Omdia發布的數據顯示,目前半導體產業內增長最快速的三個應用領域分別為汽車處理、數據中心服務器處理和高級移動半導體領域,預計未來5年的增長率分別為16%、12%和7%。受高速、高算力和高帶寬需求的影響,這些應用領域的處理器工藝制程已經邁向新節點,達到了市場上最先進的5-7nm級別,預計到本世紀末將達到1nm的范疇。 圖 | Fab 數字制程節點快逼近1nm工藝節點的提高不僅意味著產品面世周期的延長,成本的指數型增長,還面臨隨著單芯片集成度不斷提高、算力越來越密集、晶圓面積不斷增大后,良率和產量開始走下坡的挑戰。有數據表明,當單芯片晶圓面積只有10 mm2時,良率可達70%以上,而當單芯片晶圓面積增長到360 mm2時,良率已經降至15%左右。所以業界開始尋求降本增產,加速產品上市的方法。而以chiplet構成的系統可以說是一個“超級”異構系統,給傳統的異構SoC增加了新的維度。業內專家稱,采用經過充分測試和驗證的chiplet可以大大縮短產品的上市時間,降低芯片的研發成本。這樣做的好處是可以根據需要利用不同的制程節點來優化目標設計。根據統計數據顯示,單芯片面積同為360 mm2時,采用4顆小芯片的方案良率可從上述的15%提升至37%左右。

圖 | Fab 數字制程節點快逼近1nm工藝節點的提高不僅意味著產品面世周期的延長,成本的指數型增長,還面臨隨著單芯片集成度不斷提高、算力越來越密集、晶圓面積不斷增大后,良率和產量開始走下坡的挑戰。有數據表明,當單芯片晶圓面積只有10 mm2時,良率可達70%以上,而當單芯片晶圓面積增長到360 mm2時,良率已經降至15%左右。所以業界開始尋求降本增產,加速產品上市的方法。而以chiplet構成的系統可以說是一個“超級”異構系統,給傳統的異構SoC增加了新的維度。業內專家稱,采用經過充分測試和驗證的chiplet可以大大縮短產品的上市時間,降低芯片的研發成本。這樣做的好處是可以根據需要利用不同的制程節點來優化目標設計。根據統計數據顯示,單芯片面積同為360 mm2時,采用4顆小芯片的方案良率可從上述的15%提升至37%左右。 圖 | 與單片芯片相比,晶粒chiplet技術可實現更高的產量不過有一點是無論如何都避免不了的,那就是先進工藝節點下多樣的低核心電壓,以及功能堆疊下的峰值電流的增加,因此從處理器到應用系統,所需的電源管理系統也變得愈加復雜。總結下來就是,更強大的數據處理能力將拉動更高復雜性、更高性能的電源管理市場的發展。談到電源管理,我們不得不說一說當前火熱的汽車電子市場。隨著汽車智能網聯、電動化趨勢的不斷發展,汽車電子成本占比將達到整車成本的50%,包括AI芯片、MCU、傳感器、通信模塊、電池管理、DC/DC電壓轉換器、牽引電機逆變器、車載充電器,以及其他系統的電氣化設備等,同時需求總量正呈現指數型攀升趨勢。此外,隨著汽車電動化和智能化的普及,新能源汽車的持續快速放量,電動汽車中的核心部件——功率半導體的需求量新增巨大。然而Si材料在經歷了70年的開發后,到達了它的材料極限,傳統的IGBT和HVMOS在效率和功率密度上都存在不足。此時,擁有更快切換速度、溫漂損失小、功率密度更高、集成度更高的第三代半導體材料制成的SiC和GaN FET被搬上了汽車電子的舞臺,并將逐漸占領市場。

圖 | 與單片芯片相比,晶粒chiplet技術可實現更高的產量不過有一點是無論如何都避免不了的,那就是先進工藝節點下多樣的低核心電壓,以及功能堆疊下的峰值電流的增加,因此從處理器到應用系統,所需的電源管理系統也變得愈加復雜。總結下來就是,更強大的數據處理能力將拉動更高復雜性、更高性能的電源管理市場的發展。談到電源管理,我們不得不說一說當前火熱的汽車電子市場。隨著汽車智能網聯、電動化趨勢的不斷發展,汽車電子成本占比將達到整車成本的50%,包括AI芯片、MCU、傳感器、通信模塊、電池管理、DC/DC電壓轉換器、牽引電機逆變器、車載充電器,以及其他系統的電氣化設備等,同時需求總量正呈現指數型攀升趨勢。此外,隨著汽車電動化和智能化的普及,新能源汽車的持續快速放量,電動汽車中的核心部件——功率半導體的需求量新增巨大。然而Si材料在經歷了70年的開發后,到達了它的材料極限,傳統的IGBT和HVMOS在效率和功率密度上都存在不足。此時,擁有更快切換速度、溫漂損失小、功率密度更高、集成度更高的第三代半導體材料制成的SiC和GaN FET被搬上了汽車電子的舞臺,并將逐漸占領市場。

驅動半導體工業發展的動力,

正讓測試面臨挑戰

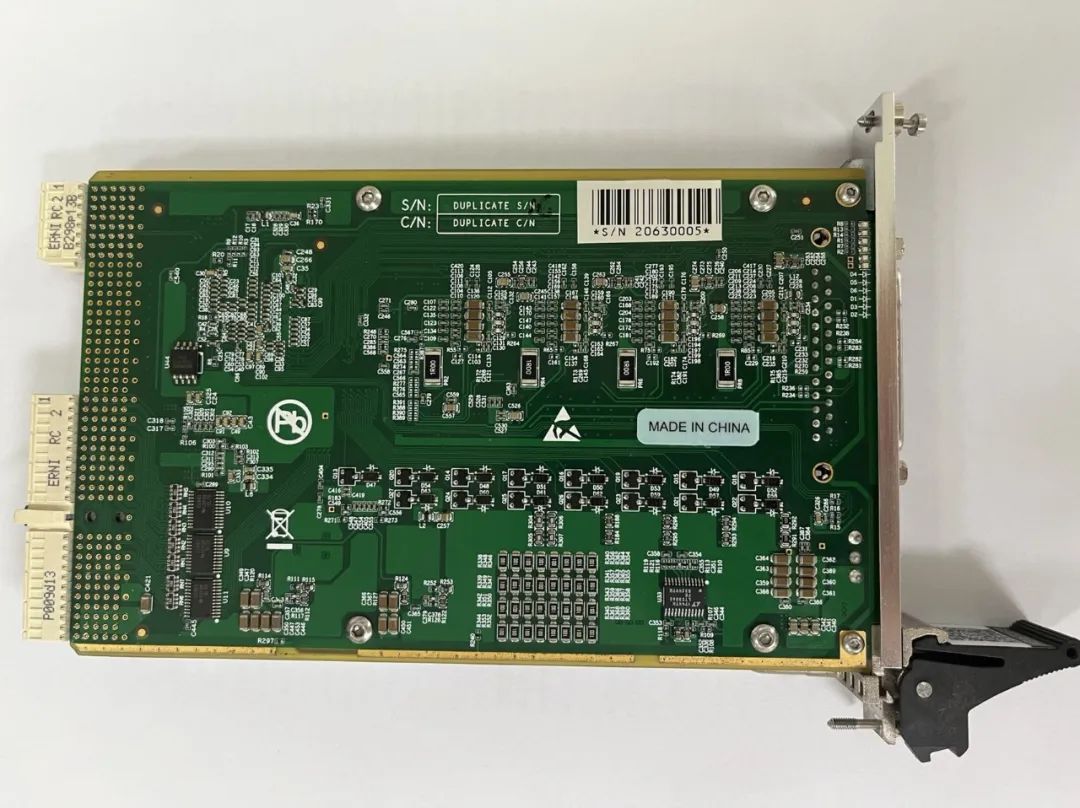

無論是云服務器、5G通信、人工智能還是汽車電動化智能化的發展,都會對半導體測試帶來挑戰。圖 | SoC測試示意圖比如SoC工作在多樣的低核心電壓(<1V)下,但整個系統的峰值電流又很高(10-100A),于是為了滿足這個趨勢的需求,業界開發出了低噪聲、高效率,被稱為負載電裝置的功率調節器。而這些器件在出廠前需要經過更高水平的負載和過流測試,更低且更精確的導通電阻RDS(on)的測量。再比如電動汽車的BMS,通常單節電池的電壓范圍是3.6V-4.7V,所以其輸出和測量精度就要求在0.1mV左右。同時,在25個單元電池的監控中,其浮地共模電壓要達到120V,以適應在最高單元上運行高達120V的現代BMS設計,所以這是一種高共模電壓下的高精度電壓測量。值得一提的是,針對這些高電壓、大電流、高精度的測試,聯合儀器的源測量單元板卡UI-X6320是非常完善的。

UI-X6320是標準的3U PXI板卡,具有高精度V/I 源測功能,4個通道。所有通道都具有高精度的可編程電壓電流功能,電壓電流可以從–24V到+24V@1000mA。所有通道可以直接連到外部DUT上,連接器是25pin的D-Sub標準接口,包括4個force通道,4個sense通道和地。

UI-X6320可以用來構建自動測試系統,測試效率高,可以縮減硬件測試時間,軟件集成化高, 開發容易快.基于PXI架構, UI-X6320可以和其他板卡配合使用,比如 數字化儀, RF射頻模塊,頻譜分析儀模塊,數字功能模塊等搭建混合功能測試系統,這種搭配使用采用的多核效率高,同時響應快。另外Additionally, 這種模塊化,集成化多通道的功能,可以對多個器件進行并性測試,從而提高測試產量。

UI-X6320單張板卡,集成有電源功能,高精度源灌功能,以及讀寫快速響應功能。這個高精度模塊可以實現高電壓同時電流測試,而且,在保持高精度的同時還具有高響應速率和高采樣率,能快 速發送和快速測量,甚至可以通過波形 的方式表現. 同時,板卡配置了繼電器,隔離效果好,有被測器件與測試板卡之間的隔離保護功能, 板卡具有remote sense功能,能夠進行測試中的校準補 償,保護小信號完整性同時,減少漏電 流的產生,準確度更高. 這些強大功能 能使得UI-X6320應用到寬電壓需求應用,例如研發測試,參數測試,功能測試, 量產測試,可以搭配測試RF,混合IC, ATE, 數據采集, 及控制系統等。

產品特點:

標準PXI總線產品

4通道,高精度V/Isource和measurement

支持電流源灌(四個象限)

FV/MI,FI/MV,FV/MU,FI,MI

+24V/-24V電壓量

6個可選測流量程,從5uA到1000mA

16位加壓加流精度

18位測壓測流精度

可編程鉗位電流功能

同步采集功能

繼電器關閉狀態,測試板和DUT間隔離性能好

可選外部供電

目標應用:

半導體測試

ASICstestin

ATE數字測試

寫在最后

我們生活在一個有趣的時代,半導體技術的未來及其在我們共同的未來中將扮演的角色從未如此令人興奮。今天的半導體產業正在經歷轉型,業務增長不再由數量或單位數量驅動,而開始關聯更多的復雜性和終端市場層面的多種技術集成。這些新興因素對未來的設計和制造設備提出了一系列新的挑戰,比如云、AI處理器、邊緣處理器、有線電源轉換和電信基礎設施的新生和變化,而正是這些變化讓我們保持在陡峭的學習曲線上。漢通達團隊希望與您一同踏上這段有趣的成長旅程,當您遇到測試挑戰時,歡迎聯系漢通達,在合作中實現共贏。

-

測試

+關注

關注

9文章

6203瀏覽量

131376 -

半導體

+關注

關注

339文章

30737瀏覽量

264227

發布評論請先 登錄

先進封裝時代,芯片測試面臨哪些新挑戰?

攜手伏達半導體:RedPKG解決方案助力封裝自主,加速產品創新

奧芯明:AI驅動半導體產業迎來“異構集成”新紀元,先進封裝成破局關鍵

Chiplet封裝設計中的信號與電源完整性挑戰

BW-4022A半導體分立器件綜合測試平臺---精準洞察,卓越測量

半導體歐姆接觸工藝 | MoGe?P?實現超低接觸電阻的TLM驗證

后摩爾定律時代,國產半導體設備的前瞻路徑分析

先進封裝轉接板的典型結構和分類

后摩爾時代破局者:物元半導體領航中國3D集成制造產業

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

打破海外壟斷,青禾晶元:引領半導體鍵合新紀元

后摩爾時代,半導體測試的挑戰與良策

后摩爾時代,半導體測試的挑戰與良策

評論