芯片是一個非常高尖精的科技領域,整個從設計到生產的流程特別復雜,籠統一點來概括的話,主要經歷設計、制造和封測這三個階段。封測就是金譽半導體今天要說到的封裝測試。

封裝測試是將生產出來的合格晶圓進行切割、焊線、塑封,使芯片電路與外部器件實現電氣連接,并為芯片提供機械物理保護,并利用集成電路設計企業提供的測試工具,對封裝完畢的芯片進行功能和性能測試。

為什么要封裝測試呢?

封裝測試的意義重大,獲得一顆IC芯片要經過從設計到制造漫長的流程,然而一顆芯片相當小且薄,如果不在外施加保護,會被輕易的刮傷損壞。此外,因為芯片的尺寸微小,如果不用一個較大尺寸的外殼,使用的時候將不易人工安置在電路板上,這個時候封裝測試技術就派上用場了。

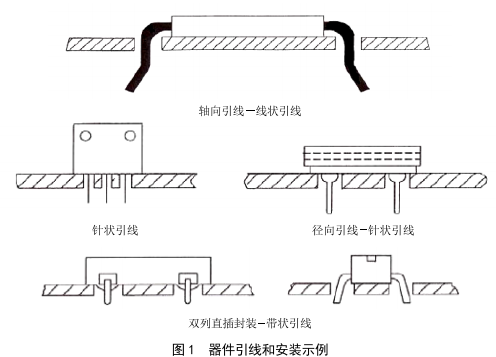

封裝測試有著安放、固定、密封、保護芯片和增強電熱性能的作用,而且還是溝通芯片內部世界與外部電路的橋梁——芯片上的接點用導線連接到封裝測試外殼的引腳上,這些引腳又通過印制板上的導線與其他器件建立連接。因此,封裝測試對集成電路起著重要的作用。

封測的主要工藝流程:

一、前段

●晶圓減薄(wafer grinding):剛出廠的晶圓(wafer)需要進行背面減薄,至封裝需要的厚度。在背面磨片時,要在正面粘貼膠帶來保護電路區域。研磨之后,再去除膠帶。

●晶圓切割(wafer Saw):將晶圓粘貼在藍膜上,再將晶圓切割成一個個獨立的Dice,再對Dice進行清洗。

●光檢查:檢查是否出現殘次品

●芯片貼裝(Die Attach):將芯片粘接在基板上,銀漿固化以防止氧化,再引線焊接。

二、后段

●注塑:防止外部沖擊,用EMC(塑封料)把產品封測起來,同時加熱硬化。

●激光打字:在產品上刻上相應的內容。例如:生產日期、批次等等。

●高溫固化:保護IC內部結構,消除內部應力。

●去溢料:修剪邊角。

●電鍍:提高導電性能,增強可焊接性。

●切片成型檢查殘次品。

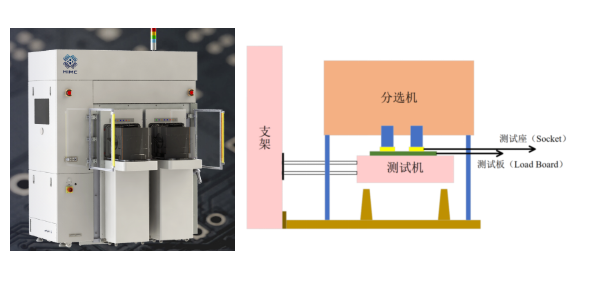

這就是一個完整芯片封測的過程。因封裝技術不同,工藝流程會有所差異,且封裝過程中也會進行檢測。封裝完成后的產品還需要進行終測(Final Test,FT),通過FT測試的產品才能對外出貨。

國內芯片封裝測試技術已經走在世界前列,這為我們全方面發展芯片行業提供了良好的基礎。中國封測業發展迅速,預計全球份額占比從2018年的22%將躍升至2025年的32%,如此高速的增長,芯片行業3大細分領域——設計、制造、封裝測試均將受益。相信在國人的努力下,我們的芯片設計和制造水平也會有一天能夠走向世界,引領時代。

審核編輯:湯梓紅

-

芯片

+關注

關注

463文章

54009瀏覽量

465969 -

封裝

+關注

關注

128文章

9249瀏覽量

148615 -

封裝測試

+關注

關注

9文章

161瀏覽量

24616

發布評論請先 登錄

芯片燒錄與芯片測試的關聯性:為什么封裝后必須進行IC測試?

先進封裝時代,芯片測試面臨哪些新挑戰?

霍爾芯片鹽霧試驗測試流程

詳解芯片封裝的工藝步驟

芯片封裝測試流程詳解

芯片封裝測試流程詳解

評論