假設您已經通過迭代信息傳遞相位邊限和回路頻寬在鎖相環(PLL)上花了一些時間。遺憾地是,還是無法在相位噪聲、雜散和鎖定時間之間達成良好的平衡。感到泄氣?想要放棄?等一下!你是否試過伽馬優化參數?

伽馬優化參數

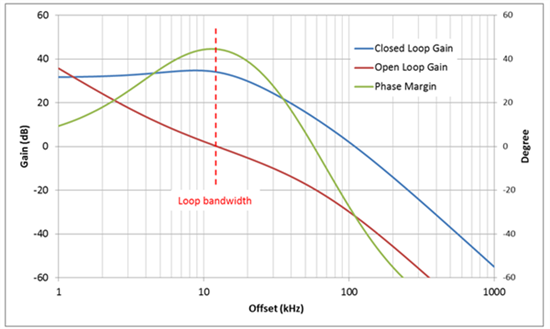

伽馬是一個數值大于零的變量。當伽馬等于1時,相位邊限在回路頻處會達到最大值(圖1)。很多回路濾波器設計方法設伽馬值為1,這是個很好的起點,但還有進一步優化的空間。

圖1:伽馬等于1時的波德圖

伽馬能夠有效用于優化帶內相位噪聲,尤其是因壓控振蕩器 (VCO) 帶來的提升斜率。此外,如果因為鑒相器頻率限制和電荷泵電流,您無法獲得更高的回路頻寬,伽馬能夠幫助您打破最大可實現回路頻寬的限制。不過,如果您將伽馬值設置的很大,則會明顯延長鎖定時間。

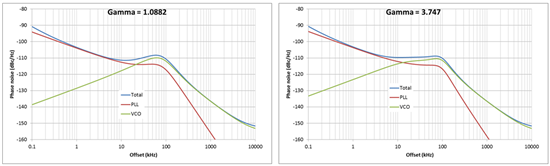

圖2所示為伽馬對相位噪聲的影響。回路頻寬和相位邊限相同,而伽馬值不同。伽馬值越高,由于噪聲整形回路濾波器平緩度提升,VCO的提升斜率也會變低。

圖2:相位噪聲vs伽馬值為1.0882時(a);相位噪聲vs伽馬值為3.747時(b)

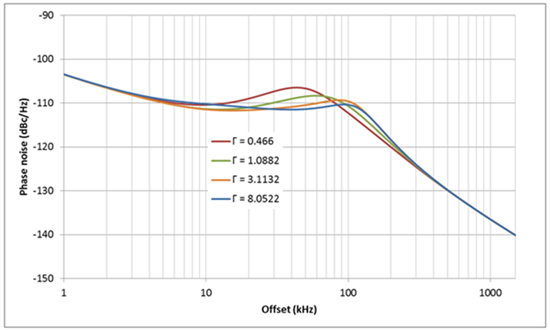

圖3所示為二階回路濾波器下可實現的最大回路頻寬 vs 不同的伽馬值。鑒相器頻率及電荷泵電流保持不變。

圖3:回路頻寬vs伽馬值

如果設計目標為 100kHz 回路頻寬,45 度相位邊限,當伽馬值限制為1時,您最多只能得到79kHz的回路頻寬。然而,如果您能接受更高的伽馬值,如伽馬值等于8,則可以實現設計目標。此時,回路頻寬為96.6kHz,相位邊限為43.4度。

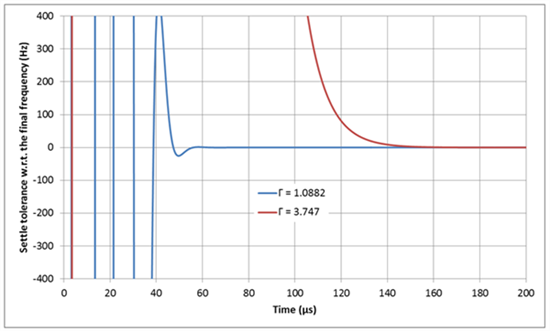

但較高的伽馬值也有其蔽處:鎖定時間更長。圖4所示為不同伽馬值下200MHz頻率躍變的鎖定時間;回路頻寬和相位邊限保持不變。當伽馬值和回路頻寬分別為1和3.7,穩定容差在±100Hz范圍內,模擬鎖定時間值分別為46.5μs與118μs。

圖4:鎖定時間vs伽馬值

使用案例

只要伽馬值優化參數不限于1,您就有更多的自由去開發您的PLL環。例如,如果目標是實現最小時基誤差,通常,您需要將回路頻寬與相位邊限設置為更高的數值。如果伽馬值等于1,由于相位邊限響應的峰值與回路頻寬一致,您可能無法得到期望的高回路頻寬值。這種情況下,您可以通過設置大于1的伽馬值,犧牲鎖定時間。這樣,您就可以得到更高的回路頻寬值。

了解如何利用PLLatinum?仿真工具快速計算伽馬值和PLL值。在“功能等級”復選框中選擇“高級”,打開伽馬優化參數選項。

審核編輯:何安淇

-

濾波器

+關注

關注

162文章

8412瀏覽量

185718 -

模擬

+關注

關注

7文章

1447瀏覽量

85384

發布評論請先 登錄

Altera公司鎖相環IP核介紹

探索CDC516:高性能3.3V鎖相環時鐘驅動器

CDC2516:高性能鎖相環時鐘驅動器的深度解析

CDC509:高性能3.3V鎖相環時鐘驅動器

CDCVF2505 3.3 - V 時鐘鎖相環時鐘驅動器:設計與應用指南

CDCVF25081:高性能鎖相環時鐘驅動器深度解析

TLC2932A高性能鎖相環芯片詳解:設計與應用指南

探索TLC2933A高性能鎖相環:特性、應用與設計要點

?CDCVF2510 3.3V鎖相環時鐘驅動器技術文檔總結

?CDCVF2510A 3.3V鎖相環時鐘驅動器技術文檔總結

基于鎖相環的無軸承同步磁阻電機無速度傳感器檢測技術

Analog Devices Inc. ADF4382x小數N分頻鎖相環 (PLL)數據手冊

鎖相環回路濾波器設計伽馬優化參數

鎖相環回路濾波器設計伽馬優化參數

評論