2019年OFC,Juniper公司展出基于硅光技術的100G QSFP28和400G QSFP-DD封裝的兩款光模塊,成為又一家推出光模塊產品的設備公司。

Juniper Networks,中文名:瞻博網絡,2016年8月,以1.65億美金收購硅光子公司Aurrion,獲得硅光技術。

硅光子公司Aurrion,成立于2008年,創始人為UCSB的Alexander Fang和John Bowers教授。Aurrion是一家光芯片的fabless公司,最核心的技術是InP等III-V材料與Si光芯片的異質集成技術,可以實現單片集成的硅光收發器。

這種技術已經經過Intel光模塊的商業驗證,Intel的硅基激光器技術也是與UCSB John Bowers教授合作開發獲得,兩者源出同門。

1.異質集成工藝

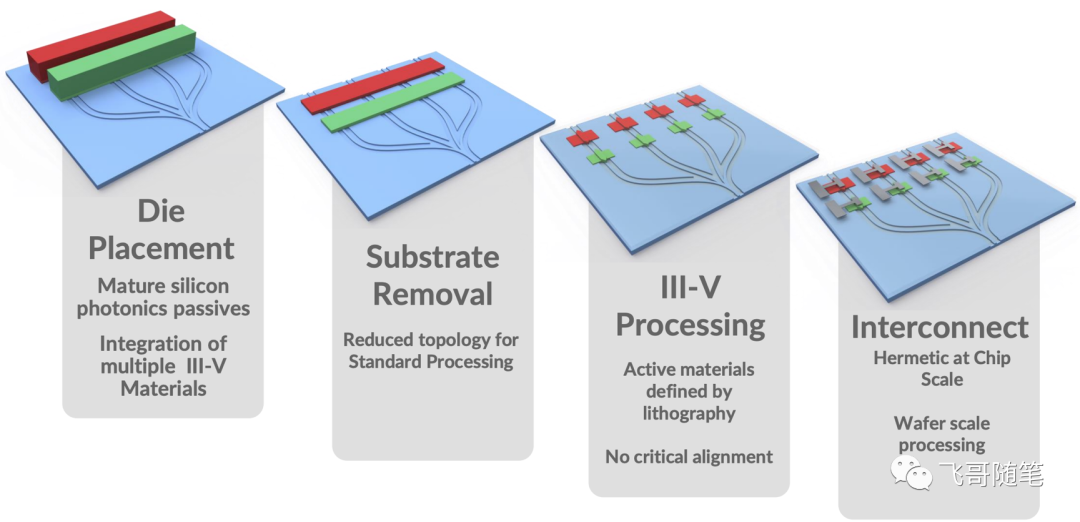

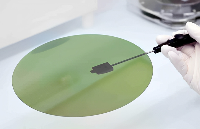

Juniper/Aurrion的異質集成工藝的一個簡單示意如下圖所示:

Juniper/Aurrion的異質集成工藝

[From:Juniper]

(1)先制作好硅光無源器件,將III-V族材料鍵合在硅晶圓上,這里可以鍵合多片,只在需要III-V族材料的區域鍵合即可;

(2)III-V族晶圓材料襯底的移除;

(3)III-V族器件的制作工藝,這里III-V族器件與硅波導的對準通過光刻工藝實現;

(4)制作電極、氣密性處理、后端測試等工藝。

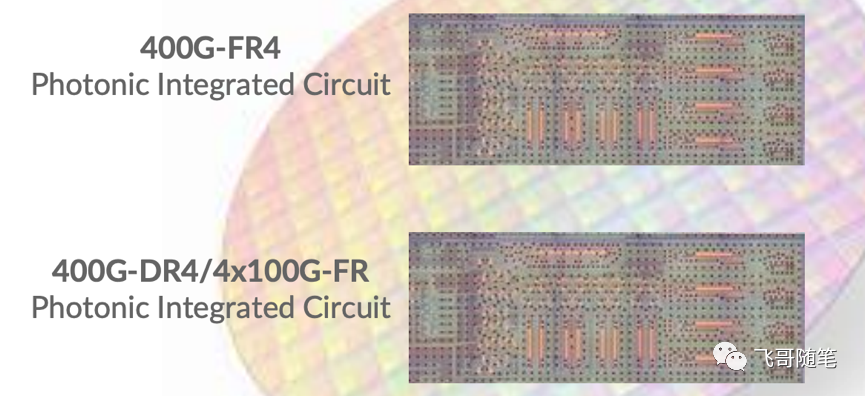

Juniper的400G FR4和DR4單片集成光芯片

[From:Juniper]

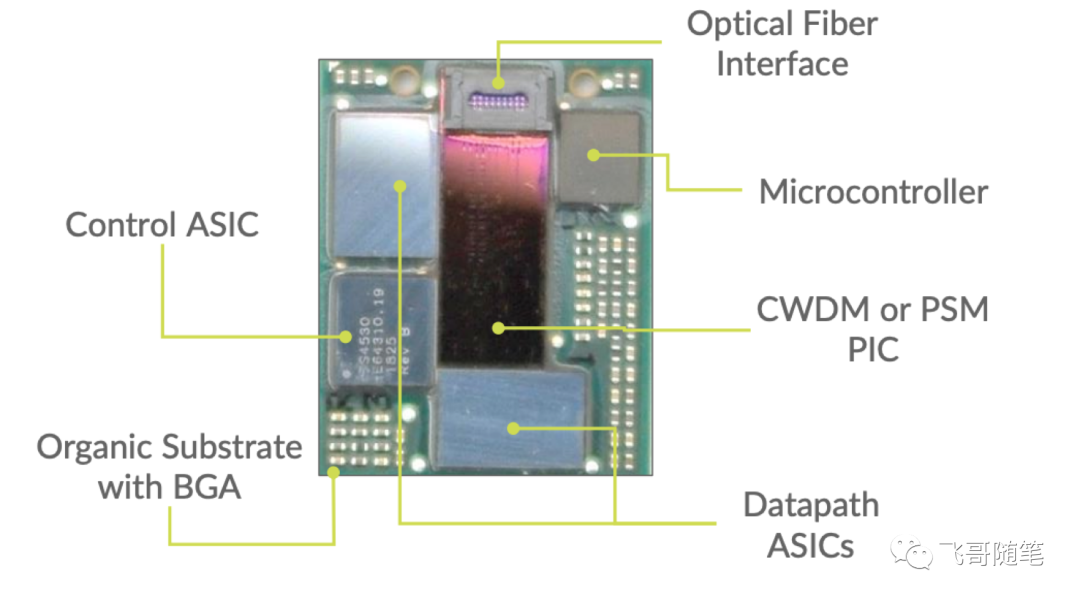

Juniper的Opto-ASIC芯片

[From:Juniper]

Juniper的硅光芯片將Tx和Rx端的所有功能器件都集成在了同一個Si芯片上,其工藝在主流的Fab廠制作。其光芯片的設計中,利用光開關制作了光環回結構,可以在生產線上進行環回測試,提升良率。

其Opto-ASIC是將硅光芯片、MCU和各種ASIC芯片利用flip-chip工藝封裝在同一個PCB襯底上,芯片的一端預留光纖接口,因光電芯片配合緊密,信號完整性更好。Opto-ASIC連接上光纖、加上電源芯片、少量阻容元件和PCB板就是一個光模塊。另外,Opto-ASIC支持回流焊工藝,這一點在實際生產中非常重要。

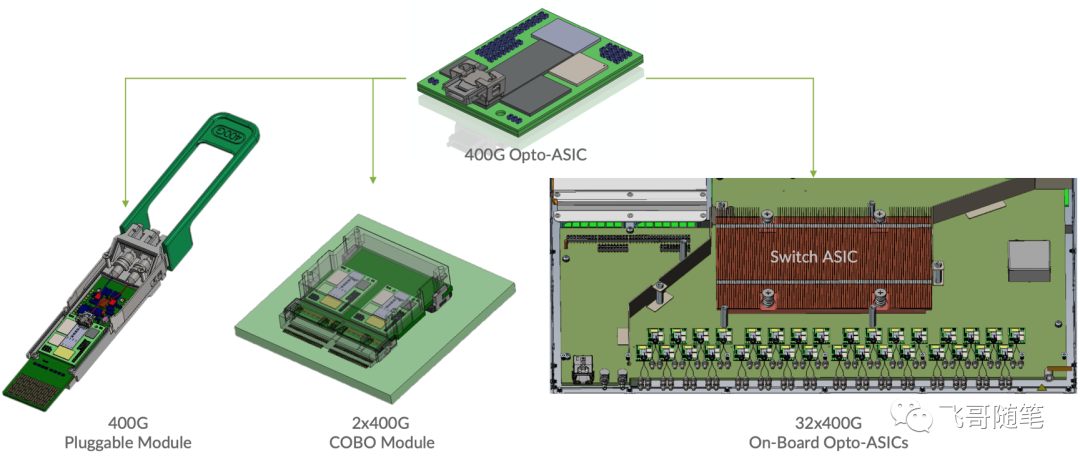

3. Pluggable、OBO、Co-package

Juniper的Opto-ASIC是一個兼容性很強的模塊化設計思路,Opto-ASIC只需要更換PIC就可以實現400G DR4和400G FR4的切換,兩種模塊還可共用同一套PCBA,這樣可以降低成本。

Juniper的400G DR4和FR4硅光模塊

[From:https://www.650group.com/blog/junipers-ofc-photonics-announcement-is-a-big-deal]

另外,Opto-ASIC還可以輕松實現COBO封裝和On-Board Opto-ASIC。下圖一個板載光學交換機的示意圖,將32個Opto-ASIC通過回流焊的方式焊接在交換機的PCB板上,Opto-ASIC光接口固定在前面板,實現32x400G端口的12.8Tbps交換容量的交換機。

Opto-ASIC的無限擴展

[From:Juniper]

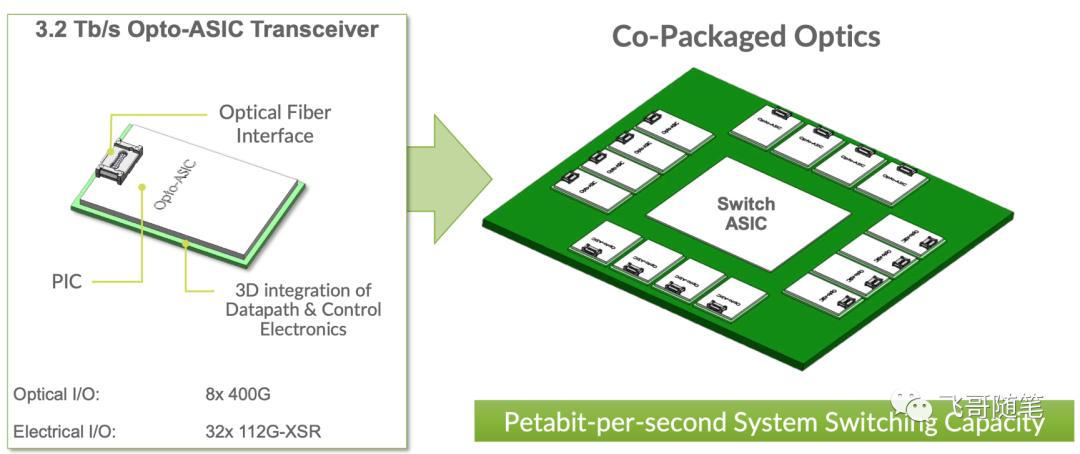

Juniper未來規劃通過3.2Tbps(光8x400G,電32 lanes 112G)的Opto-ASIC實現51.2Tbps的光電合封芯片。3.2TbpsOpto-ASIC通過3D封裝技術實現。

Juniper的Co-packaged Optics規劃

[From:Juniper]

責任編輯:lq

-

激光器

+關注

關注

18文章

2959瀏覽量

64604 -

Juniper

+關注

關注

1文章

17瀏覽量

11860 -

光模塊

+關注

關注

82文章

1632瀏覽量

63738

原文標題:震撼!Juniper的硅光子技術!

文章出處:【微信號:SSDFans,微信公眾號:SSDFans】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

集成電路制造中常用濕法清洗和腐蝕工藝介紹

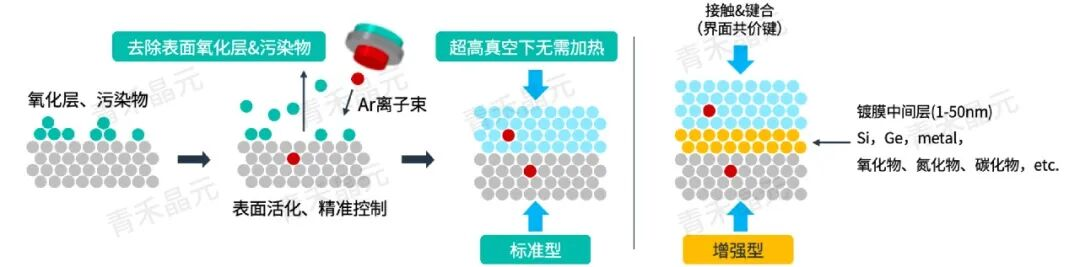

青禾晶元常溫鍵合方案,破解第三代半導體異質集成熱損傷難題

CoWoS產能狂飆的背后:異質集成芯片的“最終測試”新范式

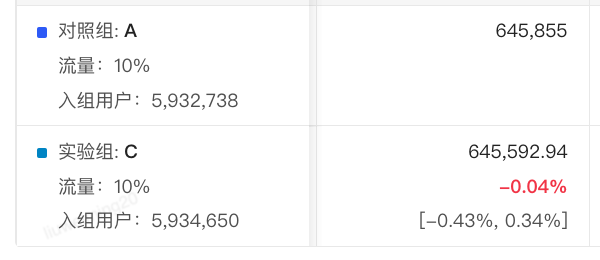

【原理到實戰】實驗異質性分析

集成電路制造中薄膜刻蝕的概念和工藝流程

【2025九峰山論壇】破局摩爾定律:異質異構集成如何撬動新賽道?

半導體外延工藝在哪個階段進行的

臺階儀應用 | 半導體GaAs/Si異質外延層表面粗糙度優化

概倫電子集成電路工藝與設計驗證評估平臺ME-Pro介紹

CMOS集成電路的基本制造工藝

最新議程出爐! | 2025異質異構集成封裝產業大會(HIPC 2025)

Juniper/Aurrion的異質集成工藝

Juniper/Aurrion的異質集成工藝

評論