十多年來,寬帶衛(wèi)星有效載荷通信系統(tǒng)都是使用數據轉換器構建的,這些數據轉換器使用低壓差分信號(LVDS)數據接口連接到現(xiàn)場可編程門陣列(FPGA)或專用集成電路(ASIC)。在該時間段內,這種組合能夠跟上不斷擴展的采樣率和相應的采樣帶寬,但是當數據轉換器的采樣率達到每個轉換器每秒約1.6 G采樣(SPS)時,達到了上限。新的JESD204B芯片間數據接口標準現(xiàn)在正在獲得芯片支持,以實現(xiàn)更高的突破。

設計人員面臨的問題是,使用LVDS連接1.6 GSPS的12位數據需要一個具有12條LVDS數據線的800MHz雙數據速率(DDR)接口-在很大程度上被認為是可靠關閉LVDS時序的實際上限。與FPGA的接口。在大多數情況下,需要使用模數轉換器(ADC)和FPGA之間的兩條800-MSPS總線(400-MHz DDR)進行2路解復用的數據流,以放寬時序要求。該方案的代價是通道數和板布線面積的兩倍。它還需要緊密匹配電路板布線中所有差分對的布局,這會導致效率低下和過大的電路板布局。節(jié)省板載空間對于空間有效載荷非常重要,因為在這種空間有效載荷下每盎司的發(fā)射成本很高,而且每平方毫米的板載空間都具有很高的價值。

同時,數據轉換器的核心速度現(xiàn)在已經超過LVDS接口速率的能力,并且商業(yè)數據轉換器行業(yè)已很大程度上轉向聯(lián)合電子設備工程委員會JESD204B串行接口標準。為了使有效載荷射頻(RF)收發(fā)器的帶寬增加到LVDS無法承受的范圍,航天工業(yè)組件制造商將需要使用這種新的標準接口。

什么是JESD204B?

JESD204B使用8位/ 10位編碼數據接口在差分通道上將數據芯片串行化。由于書面JESD204B規(guī)范的上限是12.5 Gbps的通道速率,因此可以突破寬帶通信設計人員正在尋找的信號帶寬的下一個水平,而這超出了LVDS。設計人員可以使用該通道速率將許多轉換器聚合到一個通道中,也可以采用多通道配置來從一個數據轉換器向FPGA傳輸數據或從FPGA傳輸大量數據。

由于JESD204B在鏈路對之間不需要匹配的走線長度,因此設計人員可以優(yōu)化電路板布線以節(jié)省電路板空間,并避免LVDS通常需要的額外布線,以使最短的直線走線與最長的路徑匹配。JESD204B規(guī)范具有內置的彈性緩沖,以適應走線長度的變化。對于需要同步接收器的系統(tǒng),JESD204B允許使用一種簡單的方法來使用分布式低頻SYSREF信號來實現(xiàn)多設備同步。

完善JESD204B生態(tài)系統(tǒng)

現(xiàn)在,主要的數據轉換器供應商提供了許多使用JESD204B標準的目錄(非空間級)產品,并且目錄FPGA供應商已經產生了JESD204B知識產權,以保持(并在大多數情況下超過)當前數據的速度能力。轉換器。不幸的是,空間級FPGA的SerDes輸入/輸出(I / O)速度受到限制,由于整個系統(tǒng)帶寬無法改善所提供的LVDS,因此減慢了空間應用中從LVDS到JESD204B的過渡。Microchip RTG4和Xilinx Virtex-5QV系列空間級FPGA都具有SerDes最高的加速能力,到現(xiàn)在為止還不到5 Gbps。

如果業(yè)界試圖在空間級組件中使用LVDS來超越1.6 GSPS,那么它將需要在數據轉換器與FPGA之間使用100多對匹配長度的差分連接。但是現(xiàn)在,有了JESD204B,諸如德州儀器(TI)ADC12DJ3200QML-SP之類的設備的數據量ADC僅使用8個差分連接就可以推入已達到6.4 GSPS的狀態(tài)。該器件通過運行八個JESD204B SerDes通道,每個通道以12.8 Gbps的速度實現(xiàn)6.4 GSPS的12位數據輸出。現(xiàn)在可以想象,通過擴展到更多的差分連接,加速鏈接或兩者兼而有之,可以繼續(xù)提高空間應用程序的數據轉換器采樣率。這將使通過RF鏈路往返于衛(wèi)星的信號帶寬和數據速率大大增加。

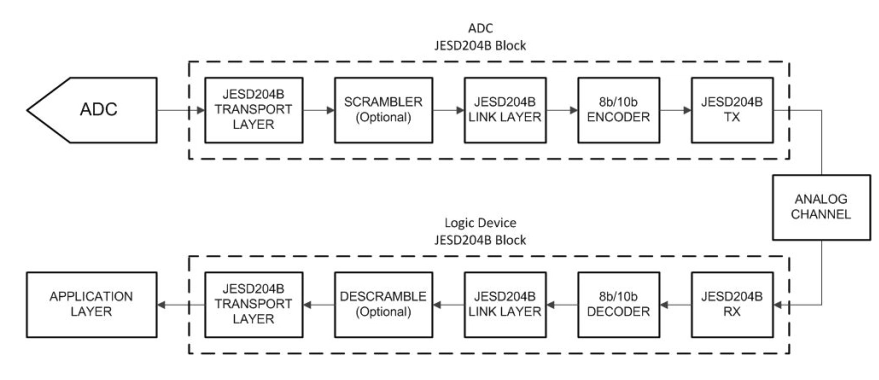

圖1顯示了標準下SerDes處理的示例。模擬通道代表設備之間板卡的高速數字數據信號。之所以在此處將其稱為模擬通道,是因為在板設計中以及用于阻抗匹配時,將12.8 Gbps SerDes鏈路視為模擬或RF信號。如果沒有給予此鏈接注意,則接收端的眼圖將不會張開并對齊以進行正確捕獲。JESD204B發(fā)送器是串行化后ADC的輸出數據,而JESD204B接收器是需要反序列化的FPGA輸入(在圖1中標記為“邏輯設備”)。

圖1此簡化的JESD204B接口圖顯示了從ADC到FPGA的數字鏈路作為模擬通道,以反映需要將電路板視為信號的電路板布局的需求。

但是,將空間應用中的數據通信轉移到JESD204B不僅需要空間級數據轉換器,還需要空間級FPGA,它們可以與它們一起工作以提供更高級別的信號帶寬。這些設備必須繼續(xù)提供太空任務所需的閉鎖和總電離劑量(TID)功能。

幸運的是,此類設備將很快面市。為了支持完整的JESD204B生態(tài)系統(tǒng),多家FPGA供應商宣布將發(fā)布具有更高SerDes速度并支持JESD204B的太空級FPGA。例如,賽靈思(Xilinx)宣布,它將把32種SerDes收發(fā)器支持12.5 Gbps的通道速率,將Kintex UltraScale類的FPGA版本過渡到XQRKU060中的空間級。圖2是連接到Alpha數據板的ADC12DJ3200QML-SP板的圖片,該板包含用于12.5 Gbps JESD204B互操作性測試的Xilinx XQRKU060。

圖2連接到Alpha數據空間開發(fā)套件(綠色)的ADC12DJ3200EVMCVAL(紅色)表明,設計人員可以使用JESD204B的空間級組件。

其他廠商也在效仿。NanoXplore宣布將提供一種太空級FPGA,其NG-LARGE中具有6.25 Gbps SerDes,而NG-ULTRA中具有12.5Gbps SerDes。Microchip宣布將在其太空級RT PolarFire FPGA的變體中支持24個10 Gbps的SerDes收發(fā)器。

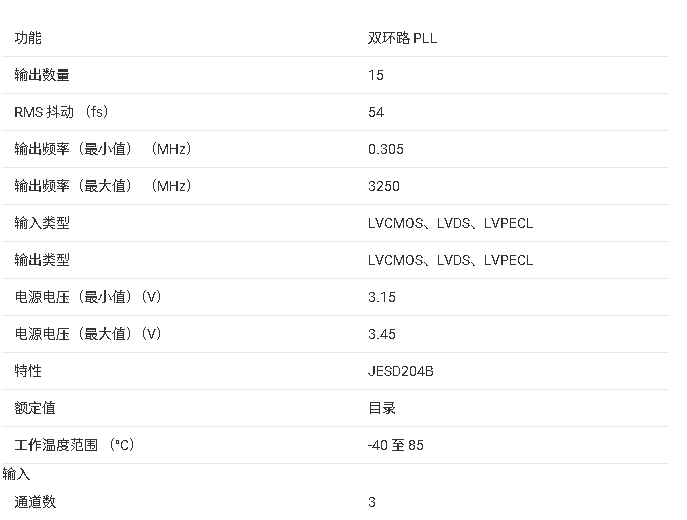

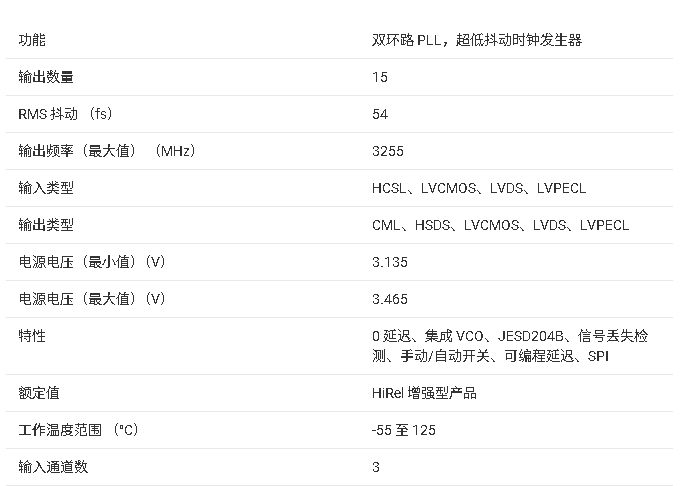

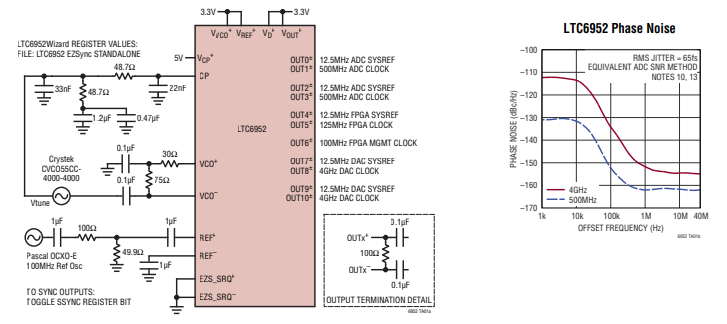

如果沒有合適的時鐘解決方案將所有組件同步連接在一起,F(xiàn)PGA-ADC系統(tǒng)將無法工作。現(xiàn)在,諸如太空級時鐘芯片德州儀器(TI)LMX2615-SP之類的設備可以提供高達15 GHz時鐘頻率的此功能。

JESD204B輻射特性

有效載荷設計人員在遇到重離子時需要了解使用JESD204B的設備的特性。盡管概率很小,但是串行鏈接可能會因軌道上的重離子撞擊而中斷。德州儀器(TI)在2019年核與空間輻射效應會議上發(fā)布了JESD204B接口的首個單事件效應表征。ADC12DJ3200QML-SP的結果摘要是:

串行鏈接始終會在重離子撞擊后自動自我恢復。

串行鏈路的平均恢復時間為1.3 μs,最壞情況下的測量值為11 μs。

但是請記住,這些只是一個示例設備的結果。每個集成電路將具有不同的結果,因此將需要對光束進行仔細的表征,以便根據組件選擇,屏蔽環(huán)境和工作軌道來確定總體誤碼率。如果重離子干擾鏈路,則必須采用具有JESD204B兼容規(guī)范的接收器并進行適當的錯誤處理,以實現(xiàn)快速恢復。

現(xiàn)在已經有了支持空間級組件中的JESD204B接口的數據轉換器,F(xiàn)PGA和時鐘設備,現(xiàn)在已經建立了一個生態(tài)系統(tǒng),可以在空間中應用該標準。設計人員現(xiàn)在可以開始處理寬帶衛(wèi)星通信和雷達有效載荷中的下一代系統(tǒng)帶寬。

菲利普·普拉特(Philip Pratt)是達拉斯德州儀器(TI)面向全球航空航天和國防應用客戶的高速數據轉換器團隊的營銷主管。

編輯:hfy

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636231 -

串行接口

+關注

關注

3文章

520瀏覽量

45216 -

lvds

+關注

關注

2文章

1237瀏覽量

69825 -

數據轉換器

+關注

關注

1文章

399瀏覽量

30668 -

JESD204B

+關注

關注

6文章

83瀏覽量

19897

發(fā)布評論請先 登錄

LMK04828 超低噪聲JESD204B兼容時鐘抖動清除器技術手冊

?LMK0482x系列超低噪聲JESD204B兼容時鐘抖動清除器技術文檔總結

LMK04616 超低噪聲低功耗JESD204B兼容時鐘抖動清除器總結

?LMK04828-EP 超低噪聲JESD204B兼容時鐘抖動清除器總結

LMK04832 超低噪聲、3.2 GHz、15 輸出、JESD204B 時鐘抖動清除器技術手冊

?LMK04368-EP 超低噪聲JESD204B/C雙環(huán)路時鐘抖動清除器總結

替代HMC7044超低噪高性能時鐘抖動消除器支持JESD204B

LTC6953具有11個輸出并支持JESD204B/JESD204C協(xié)議的超低抖動、4.5GHz時鐘分配器技術手冊

AD9680 JESD204B接口的不穩(wěn)定會導致較大的電流波動,怎么解決?

LTC6952具有11個輸出并支持JESD204B/JESD204C協(xié)議的超低抖動、4.5GHz PLL技術手冊

關于航天工業(yè)組件的JESD204B標準快速數據接口

關于航天工業(yè)組件的JESD204B標準快速數據接口

評論