據(jù)媒體報道,作為全球一號代工廠,臺積電已經開始大規(guī)模量產第六代CoWoS晶圓級芯片封裝技術,集成度大大提高。

我們知道,如今的高端半導體芯片越來越復雜,傳統(tǒng)的封裝技術已經無法滿足,Intel、臺積電、三星等紛紛研發(fā)了各種2.5D、3D封裝技術,將不同IP模塊以不同方式,整合封裝在一顆芯片內,從而減低制造難度和成本。

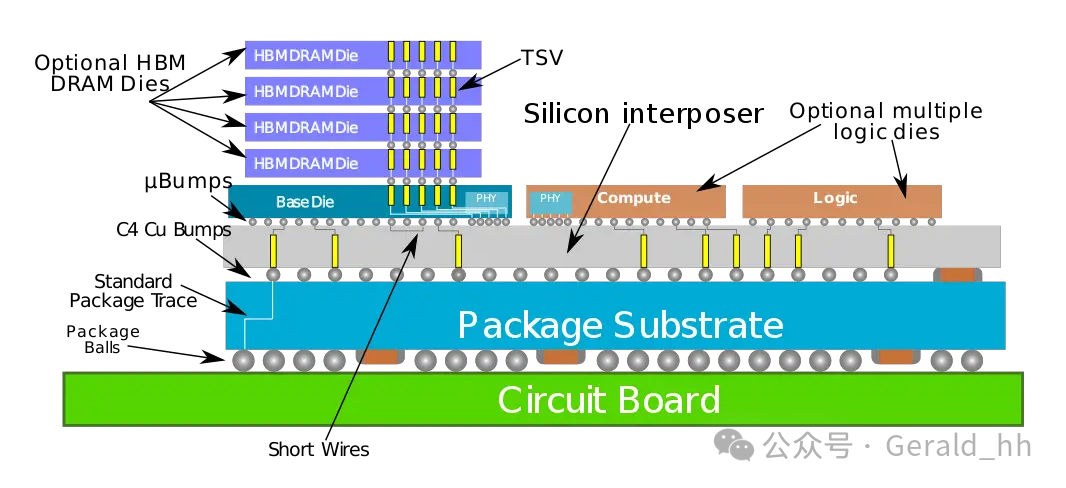

CoWoS的全稱為Chip-on-Wafer-on-Substrate,是一種將芯片、基底都封裝在一起的技術,并且是在晶圓層級上進行,目前只有臺積電掌握,技術細節(jié)屬于商業(yè)機密。

它屬于2.5D封裝技術,常用于HBM高帶寬內存的整合封裝,比如AMD Radeon VII游戲卡、NVIDIA V100計算卡都屬于此類。

CoWoS封裝結構簡圖

Radeon VII集成封裝了四顆HBM

臺積電當然也不會披露第六代CoWoS的細節(jié),只是說可以在單個封裝內,集成多達12顆HBM內存。

最新的HBM2E已經可以做到單顆容量16GB,12顆封裝在一起那就是海量的192GB!

不知道哦什么樣的芯片需要這么大的整合內存……

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

臺積電

+關注

關注

44文章

5803瀏覽量

176381 -

晶圓

+關注

關注

53文章

5410瀏覽量

132312 -

內存

+關注

關注

9文章

3211瀏覽量

76377 -

CoWoS

+關注

關注

0文章

169瀏覽量

11507

發(fā)布評論請先 登錄

相關推薦

熱點推薦

先進封裝市場迎來EMIB與CoWoS的格局之爭

技術悄然崛起,向長期占據(jù)主導地位的臺積電CoWoS方案發(fā)起挑戰(zhàn),一場關乎AI產業(yè)成本與效率的技術博弈已然拉開序幕。 ? 在AI算力需求呈指數(shù)級增長的當下,先進封裝技術成為突破芯片性能瓶

瑞薩電子推出第六代DDR5 RCD,傳輸速率達9600MT/s

電子發(fā)燒友網(wǎng)綜合報道 日前,瑞薩電子宣布推出業(yè)界首款面向DDR5寄存雙列直插式內存模塊(RDIMM)的第六代(Gen6)寄存時鐘驅動器(RCD),這款全新RCD率先實現(xiàn)了9600兆傳輸/秒(MT/s

臺積電CoWoS技術的基本原理

隨著高性能計算(HPC)、人工智能(AI)和大數(shù)據(jù)分析的快速發(fā)展,諸如CoWoS(芯片-晶圓-基板)等先進封裝技術對于提升計算性能和效率的重要性日益凸顯。

臺積電CoWoS平臺微通道芯片封裝液冷技術的演進路線

臺積電在先進封裝技術,特別是CoWoS(Chip on Wafer on Substrate)平臺上的微通道芯片液冷技術路線,是其應對高性能計算和AI芯片高熱流密度挑戰(zhàn)的關鍵策略。本報

【海翔科技】玻璃晶圓 TTV 厚度對 3D 集成封裝可靠性的影響評估

一、引言

隨著半導體技術向小型化、高性能化發(fā)展,3D 集成封裝技術憑借其能有效提高芯片集成度、縮短信號傳輸距離等優(yōu)勢,成為行業(yè)發(fā)展的重要方向 。玻璃晶

化圓為方,臺積電整合推出最先進CoPoS半導體封裝

電子發(fā)燒友網(wǎng)綜合報道 近日,據(jù)報道,臺積電將持續(xù)推進先進封裝技術,正式整合CoWoS與FOPLP,推出新一代CoPoS工藝。 ? 作為

性能躍升,安全護航 ---- 瀾起科技重磅發(fā)布全新第六代津逮? 性能核 CPU

上海2025年8月15日 /美通社/ -- 在數(shù)字化轉型浪潮與數(shù)據(jù)安全需求的雙重驅動下,瀾起科技今日重磅推出第六代津逮? 性能核 CPU (以下簡稱 C6P )。這款融合突破性架構、全棧兼容性

什么是晶圓級扇入封裝技術

在微電子行業(yè)飛速發(fā)展的背景下,封裝技術已成為連接芯片創(chuàng)新與系統(tǒng)應用的核心紐帶。其核心價值不僅體現(xiàn)于物理防護與電氣/光學互聯(lián)等基礎功能,更在于應對多元化市場需求的適應性突破,本文著力介紹晶圓級扇入

臺積電最大先進封裝廠AP8進機

。改造完成后AP8 廠將是臺積電目前最大的先進封裝廠,面積約是此前 AP5 廠的四倍,無塵室面積達 10 萬平方米。 臺積電AP8廠將用于

臺積電量產第六代CoWoS晶圓封裝:12顆封裝CPU可集成192GB內存

臺積電量產第六代CoWoS晶圓封裝:12顆封裝CPU可集成192GB內存

評論