這一節(jié)我們探索基于AXI總線的設(shè)計(jì),來看一看ZYNQ系列開發(fā)板的獨(dú)特優(yōu)勢,PS可以控制PL產(chǎn)生定制化的行為,而不需要去動硬件代碼。

這次實(shí)驗(yàn)是產(chǎn)生頻率和占空比可調(diào)的PWM(Pulse Width Modulation)信號,調(diào)用8次,產(chǎn)生8路PWM波,并用這些信號去控制8路LED燈,觀察實(shí)驗(yàn)效果。后面會做一個(gè)比較。

用的板子是zc702。

新建一個(gè)工程,命名為PWM_AXI_Lite

創(chuàng)建基于AXI總線的PWM波IP

IP設(shè)計(jì)為一個(gè)寄存器負(fù)責(zé)控制頻率,一個(gè)寄存器負(fù)責(zé)控制占空比。

創(chuàng)建一個(gè)IP核,tools-->Create and Package ,這里需要16個(gè)寄存器,創(chuàng)建方法見系列(六)、系列(七),這里命名為PWM_AXI_Lite。

在IP核工程里,新建一個(gè)PWM模塊文件,這里占空比設(shè)計(jì)的比較糙,直接就用一個(gè)計(jì)數(shù)值代替功能,后面的軟件設(shè)計(jì)要注意:

module PWM(

input clk,

input rst_n,

input cnt_set,

input fre_set,

output pwm_o

);

wire[31:0] cnt_set;

wire[31:0] fre_set;

reg [31:0] fre_cnt;

always @(posedge clk) begin

if(!rst_n) begin

fre_cnt end

else begin

if(fre_cnt fre_cnt else

fre_cnt end

end

assign pwm_o=(cnt_set>fre_cnt);

endmodule

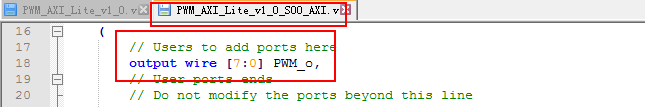

在自動產(chǎn)生的實(shí)例文件里,添加端口信號和自定義功能,后面要約束到LED上:

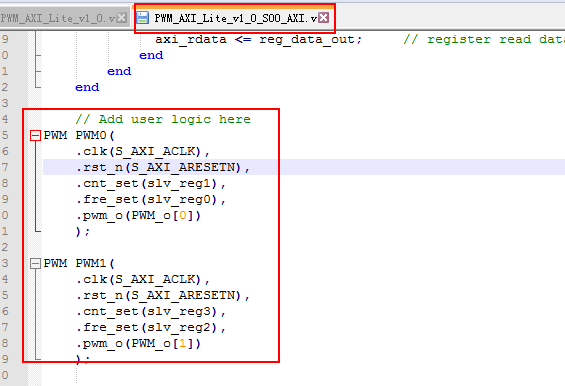

自定義的功能就是一個(gè)寄存器控制頻率(fre_set),一個(gè)寄存器控制占空比(cnt_set):

// Add user logic here

PWM PWM0(

.clk(S_AXI_ACLK),

.rst_n(S_AXI_ARESETN),

.cnt_set(slv_reg1),

.fre_set(slv_reg0),

.pwm_o(PWM_o[0])

);

PWM PWM1(

.clk(S_AXI_ACLK),

.rst_n(S_AXI_ARESETN),

.cnt_set(slv_reg3),

.fre_set(slv_reg2),

.pwm_o(PWM_o[1])

);

PWM PWM2(

.clk(S_AXI_ACLK),

.rst_n(S_AXI_ARESETN),

.cnt_set(slv_reg5),

.fre_set(slv_reg4),

.pwm_o(PWM_o[2])

);

PWM PWM3(

.clk(S_AXI_ACLK),

.rst_n(S_AXI_ARESETN),

.cnt_set(slv_reg7),

.fre_set(slv_reg6),

.pwm_o(PWM_o[3])

);

PWM PWM4(

.clk(S_AXI_ACLK),

.rst_n(S_AXI_ARESETN),

.cnt_set(slv_reg9),

.fre_set(slv_reg8),

.pwm_o(PWM_o[4])

);

PWM PWM5(

.clk(S_AXI_ACLK),

.rst_n(S_AXI_ARESETN),

.cnt_set(slv_reg11),

.fre_set(slv_reg10),

.pwm_o(PWM_o[5])

);

PWM PWM6(

.clk(S_AXI_ACLK),

.rst_n(S_AXI_ARESETN),

.cnt_set(slv_reg13),

.fre_set(slv_reg12),

.pwm_o(PWM_o[6])

);

PWM PWM7(

.clk(S_AXI_ACLK),

.rst_n(S_AXI_ARESETN),

.cnt_set(slv_reg15),

.fre_set(slv_reg14),

.pwm_o(PWM_o[7])

);

// User logic ends

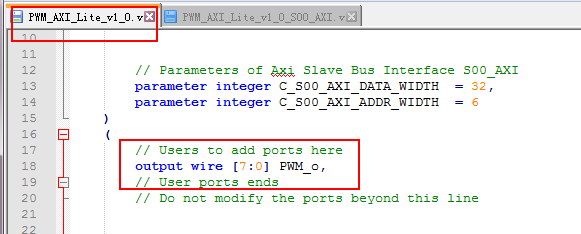

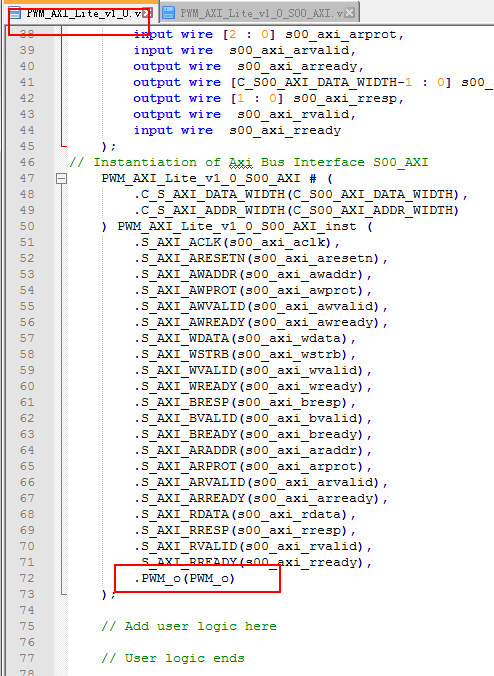

在頂層模塊添加好用戶信號,一個(gè)是端口里的,一個(gè)是調(diào)用里的:

修改完后重新打包好。

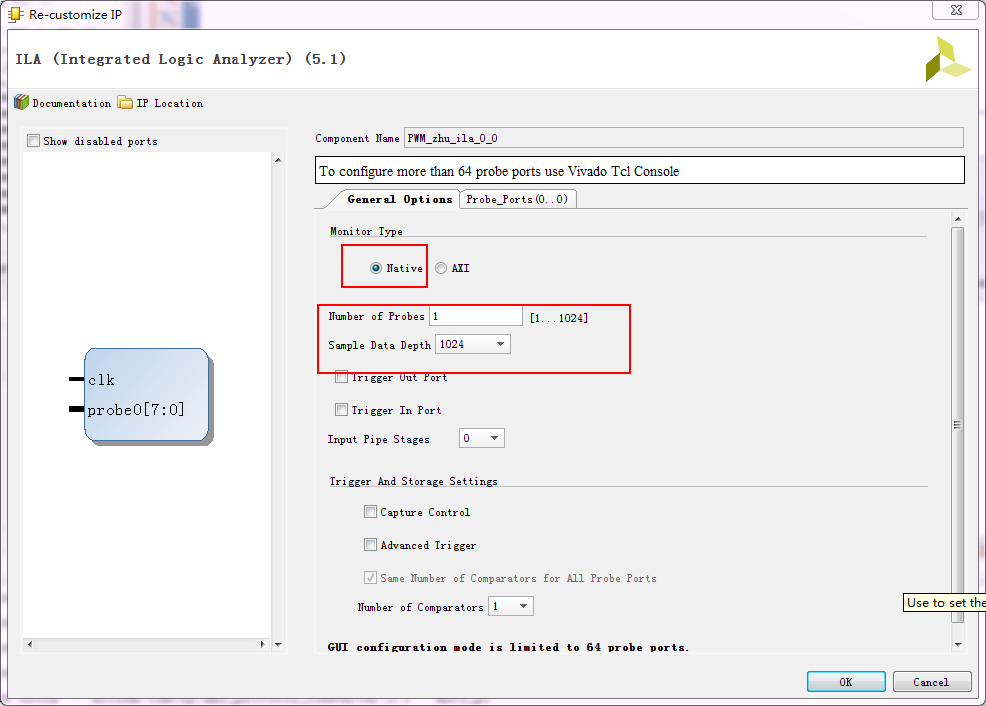

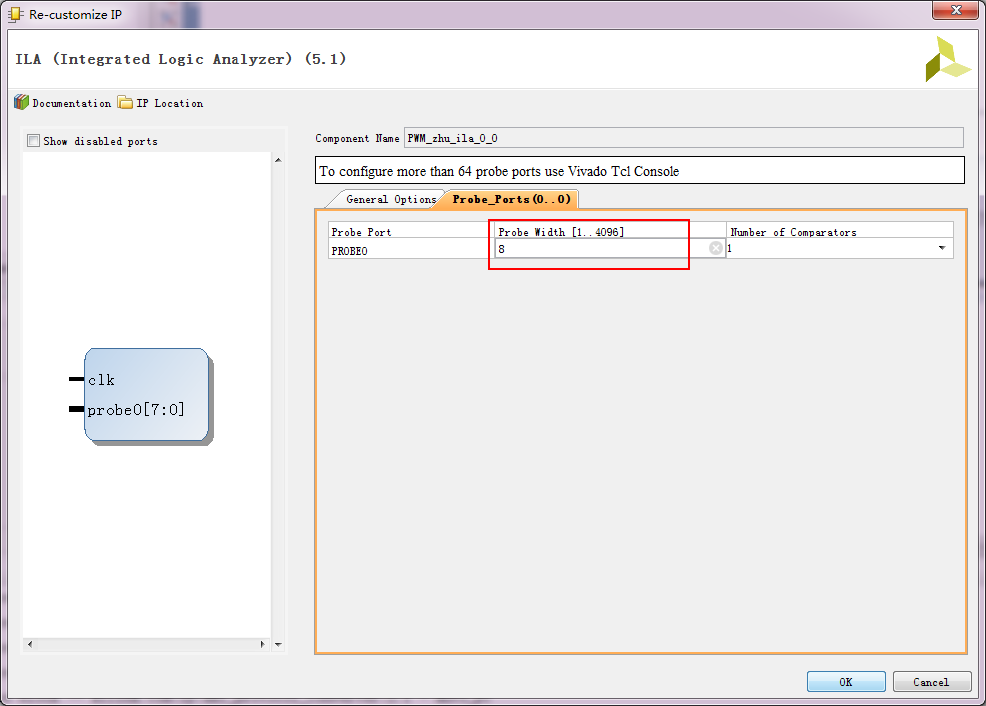

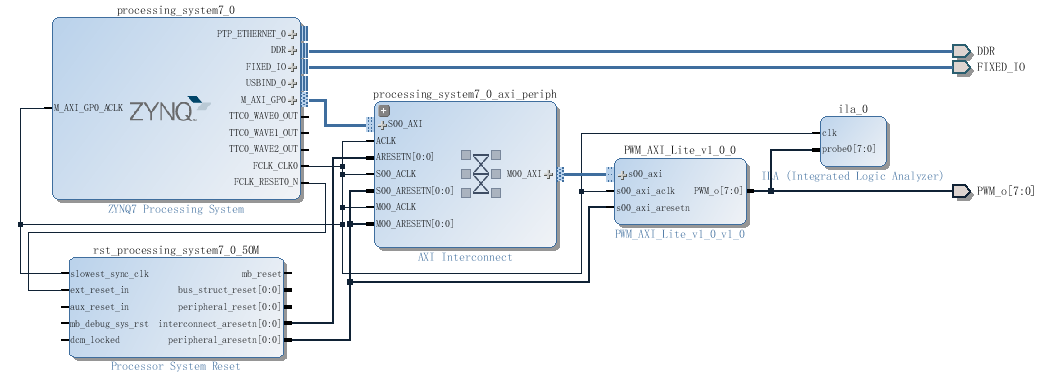

回到原先建的工程,將這個(gè)IP添加到IP庫里,然后Create Block Design,添加ZYNQ核和PWM_AXI_Lite,為了觀察PWM波信號,這里又添加了一個(gè)ILA(為了簡化,可以去掉),配置如下:

連接CLK 和 FCLK_CLK0 ,連接 Probe0 和 PWM_o,最后創(chuàng)建的系統(tǒng)如下:

添加約束文件,將8路PWM波綁定到8個(gè)LED上:

#GPIO PMOD1

set_property PACKAGE_PIN E15 [get_ports {PWM_o[7]}]

set_property IOSTANDARD LVCMOS25 [get_ports {PWM_o[7]}]

set_property PACKAGE_PIN D15 [get_ports {PWM_o[6]}]

set_property IOSTANDARD LVCMOS25 [get_ports {PWM_o[6]}]

set_property PACKAGE_PIN W17 [get_ports {PWM_o[5]}]

set_property IOSTANDARD LVCMOS25 [get_ports {PWM_o[5]}]

set_property PACKAGE_PIN W5 [get_ports {PWM_o[4]}]

set_property IOSTANDARD LVCMOS25 [get_ports {PWM_o[4]}]

#GPIO PMOD2

set_property PACKAGE_PIN V7 [get_ports {PWM_o[3]}]

set_property IOSTANDARD LVCMOS25 [get_ports {PWM_o[3]}]

set_property PACKAGE_PIN W10 [get_ports {PWM_o[2]}]

set_property IOSTANDARD LVCMOS25 [get_ports {PWM_o[2]}]

set_property PACKAGE_PIN P18 [get_ports {PWM_o[1]}]

set_property IOSTANDARD LVCMOS25 [get_ports {PWM_o[1]}]

set_property PACKAGE_PIN P17 [get_ports {PWM_o[0]}]

set_property IOSTANDARD LVCMOS25 [get_ports {PWM_o[0]}]

一系列常規(guī)操作,生成比特流文件后,Lanch到SDK。

SDK部分設(shè)計(jì)

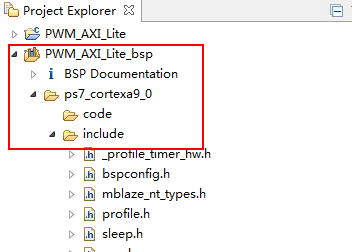

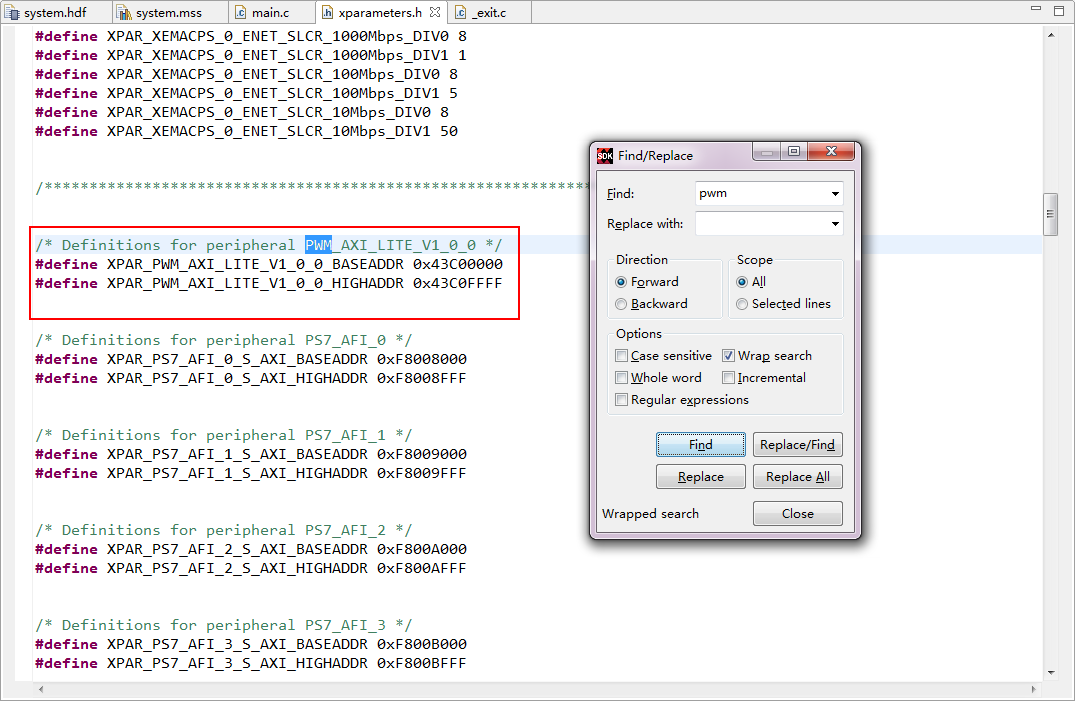

在BSP包里找到xparameter.h文件:

在xparameters.h文件里找到系統(tǒng)為我們的PWM IP配置的地址,待會我們要操作它的寄存器:

打開xparameters.h文件,Ctrl+F:

這個(gè)基地址就是我們的寄存器0的地址,然后我們將各路PWM波的頻率和占空比寫入:

#include

#include "xparameters.h"

#include "xil_io.h"

#include "sleep.h"

#include "xil_types.h"

int main(){

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR,40000000);

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR+4,30000000);

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR+8,40000000);

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR+12,20000000);

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR+16,40000000);

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR+20,10000000);

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR+24,40000000);

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR+28,8000000);

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR+32,40000000);

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR+36,6000000);

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR+40,40000000);

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR+44,4000000);

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR+48,40000000);

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR+52,2000000);

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR+56,40000000);

Xil_Out32(XPAR_PWM_AXI_LITE_V1_0_0_BASEADDR+60,100000);

return 0;

}

板子上電,然后Program FPGA,debug as后,在vivado里會自動打開調(diào)試界面,觸發(fā)后能看到8路波形,在板子上我們可以看到LED燈依次閃爍!

總結(jié):

這里我們達(dá)到了led依次閃爍的效果,如同系列(六)達(dá)到的效果,但是這里有本質(zhì)的區(qū)別,系列(六)需要CPU一直發(fā)送指令控制LED燈,而這次試驗(yàn)CPU寫入頻率和占空比后,現(xiàn)在8路PWM波自己工作,是PL完成的,不需要CPU發(fā)命令,CPU可以去干其他事情。這就是SOPC的優(yōu)勢!

編輯:hfy

-

FPGA

+關(guān)注

關(guān)注

1660文章

22421瀏覽量

636624 -

寄存器

+關(guān)注

關(guān)注

31文章

5609瀏覽量

130027 -

PWM

+關(guān)注

關(guān)注

116文章

5872瀏覽量

225759

發(fā)布評論請先 登錄

【ESP32-C2系列】WT99C262-SG開發(fā)板上手指南

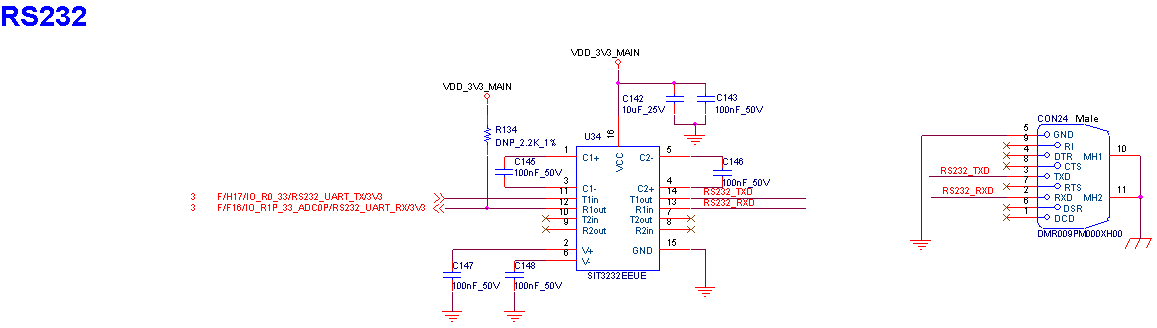

基于ZYNQ-MZ702P開發(fā)板實(shí)現(xiàn)以太網(wǎng)通信

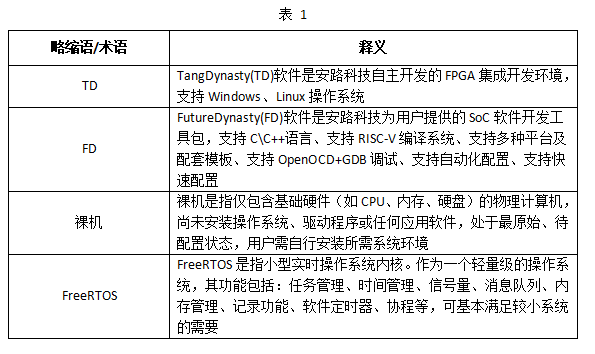

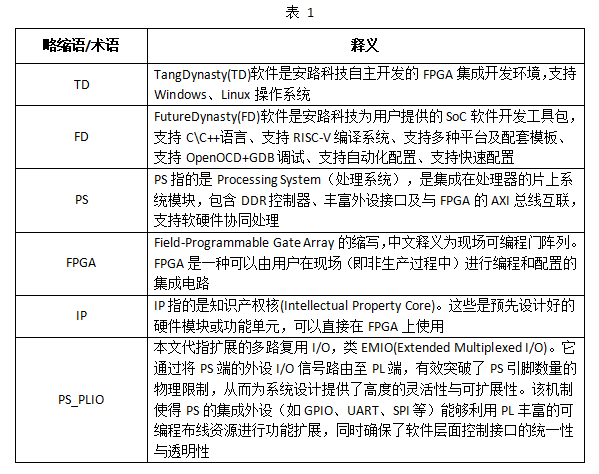

DR1 系列評估板 PS 端裸機(jī)與 FreeRTOS 開發(fā)案例手冊

DR1 系列核心板 PS+PL 異構(gòu)多核實(shí)戰(zhàn)案例手冊(二)

DR1 系列核心板 PS+PL 異構(gòu)多核實(shí)戰(zhàn)案例手冊(一)

工程師必入!288 元解鎖賽靈思開發(fā)板

ZYNQ PS與PL數(shù)據(jù)交互方式

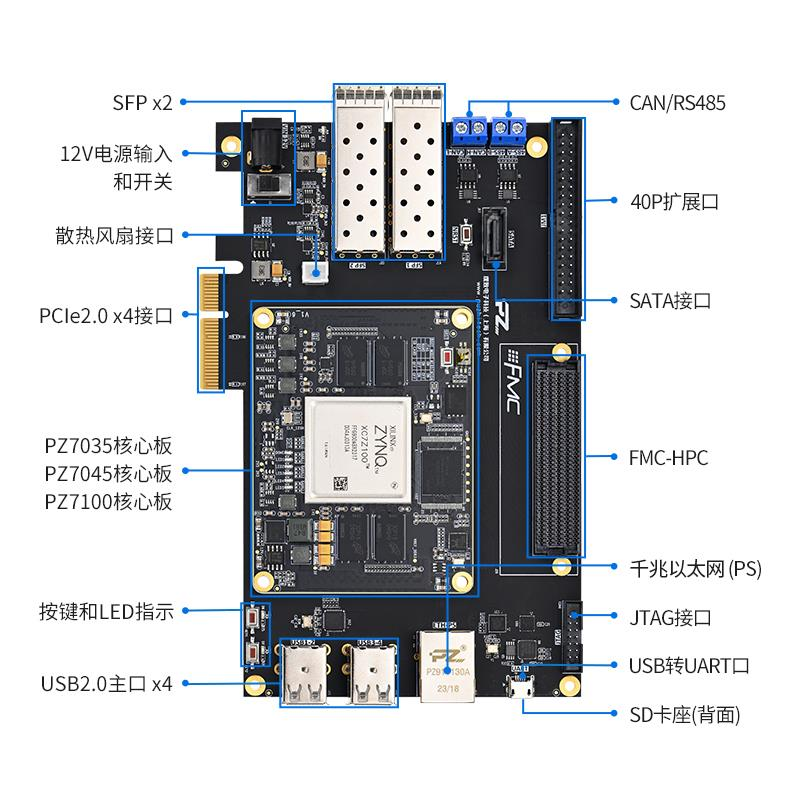

fpga開發(fā)板 璞致ZYNQ 7000 系列之 PZ7035/PZ7045/PZ7100-FH 核心板與開發(fā)板用戶手冊

ALINX AMD RFSoC射頻開發(fā)板選型指南

【新品】遠(yuǎn)距離圖傳數(shù)傳模塊開發(fā)板、藍(lán)牙模塊開發(fā)板、無線模塊開發(fā)板

正點(diǎn)原子Z15I ZYNQ 開發(fā)板資料發(fā)布!板載PCIe2.0、SPFx2、MIPI CSI等接口,資料豐富!

正點(diǎn)原子Z20 ZYNQ 開發(fā)板發(fā)布!板載FMC LPC、LVDS LCD和WIFI&藍(lán)牙等接口,資料豐富!

LTC3886輸出PWM波異常的原因?

基于小凌派RK2206開發(fā)板:OpenHarmony如何使用IoT接口控制PWM外設(shè)

ZYNQ系列開發(fā)板:PS控制PL產(chǎn)生需要的PWM波

ZYNQ系列開發(fā)板:PS控制PL產(chǎn)生需要的PWM波

評論