第一章:Zynq7000 系列 FPGA 介紹

Zynq 系列是賽靈思公司(Xilinx)推出的行業第一個可擴展處理平臺。旨在為 視頻監視、汽車駕駛員輔助以及工廠自動化等高端嵌入式應用提供所需的處理與計 算性能水平。

名稱由來

Zynq 這個詞很容易讓人聯想到 zinc,也就是電池、日光屏、合金制品和藥品 中最常見的化學元素鋅。鋅與其他金屬的合金可實現增強型功能,根據合金的不同 對象表現為不同的色彩。鋅最常見的用途就是電鍍,那么這個名稱與電鍍之間有什 么聯系?

在 2010 年 4 月硅谷舉行的嵌入式系統大會上,賽靈思發布了可擴展處理平臺 的架構詳情,這款基于無處不在的 ARM 處理器的SoC 可滿足復雜嵌入式系統的高性 能、低功耗和多核處理能力要求。賽靈思可擴展處理平臺芯片硬件的核心本質就是 將通用基礎雙 ARMCortex-A9MPCore 處理器系統作為“主系統”,結合低功耗 28nm 工藝技術,以實現高度的靈活性、強大的配置功能和高性能。由于該新型器件的可 編程邏輯部分基于賽靈思 28nm7 系列 FPGA,因此該系列產品的名稱中添加了

“7000”,以保持與 7 系列 FPGA 的一致性,同時也方便日后本系列新產品的命 名。

除了芯片外,賽靈思 Zynq-7000 系列還構成了最終平臺產品的基礎。賽靈思聯 盟計劃生態系統和 ARM 互聯社區的成員提供的軟件開發與硬件設計實現工具、廣泛 采用的操作系統、調試器、IP 及其他元素的工具就好像“電鍍”在一起一樣,從 而使可擴展處理平臺成為了可能。

Zynq-7000為何不是FPGA?

Zynq-7000 可擴展處理平臺是采用賽靈思新一代 FPGA(Artix-7 與 Kintex-

7FPGA)所采用的同一 28nm 可編程技術的最新產品系列。可編程邏輯可由用戶配

置,并通過“互連”模塊連接在一起,這樣可以提供用戶自定義的任意邏輯功能, 從而擴展處理系統的性能及功能。不過,與采用嵌入式處理器的 FPGA 不同,Zynq- 7000 產品系列的處理系統不僅能在開機時啟動,而且還可根據需要配置可編程邏 輯。采用這種方法,軟件編程模式與全功能的標準 ARM 處理 SoC 毫無二致。

“可擴展”意味著什么?

在軟件工程領域,可擴展性(有時會同前向兼容性相混淆)是指實現方案考慮 到未來發展需求的系統設計原理。這是一種能夠擴展系統的系統性舉措,也是實現 擴展所需的工作。擴展可體現為增加新功能,也可體現為現有功能的修改。其核心 主題就是在盡可能減少現有系統功能變動的基礎上實現變革。

在系統架構中,可擴展性意味著系統設計時包含了通過新功能擴展/改進自身 的機制和元素(hook),而且無需對系統基礎架構進行較大的修改。良好的架構反映 了實現上述目的的設計原理,也為今后可能的構建工作制定了發展藍圖。請注意, 這通常是指最終交付的產品中包含了尚不會(實際上可能永遠不會)用到的功能和 機制,但這種功能并不是可有可無的,而是可維護性的必要元素,有助于避免產品 過早被淘汰。

ZYNQ=processor

Zynq-7000 嵌入式處理平臺系列的每款產品均采用帶有 NEON 及雙精度浮點引擎

的雙核 ARMCortex-A9MPCore 處理系統,該系統通過硬連線完成了包括 L1,L2 緩

存、存儲器控制器以及常用外設在內的全面集成。該處理系統不僅能在開機時啟動 并運行各種獨立于可編程邏輯的操作系統(OS),而且還可根據需要配置可編程邏

輯。利用這種方法,軟件編程模式與全功能的標準 ARM 處理 SoC 毫無二致。

應用開發人員利用可編程邏輯強大的并行處理能力,不僅可以解決多種不同信 號處理應用中的大量數據處理問題,而且還能通過實施更多外設來擴展處理系統的 特性。系統和可編程邏輯之間的高帶寬 AMBA?-AXI 互聯能以極低的功耗支持千兆位 級數據傳輸,從而解決了控制、數據、I/O 和存儲器之間的常見性能瓶頸問題。

編程環境

Zynq-7000 系列提供了一個開放式設計環境,便于可編程邏輯中雙核 Cortex- A9MPCore 和定制加速器的并行開發,從而加速了產品上市進程。軟件開發人員可 以充分利用基于 Eclipse 的 XilinxPlatformStudio 軟件開發套件(SDK)、ARM 的 DS-5 和 ARMRealViewDesignSuite(RVDS),或 ARM 互聯社區和賽靈思聯盟計劃生態 系統的領先廠商(諸如 Lauterbach、WindRiver、PetaLogix、MathWorks、

MentorGraphics、Micrium 和 MontaVista 等)提供的編譯器、調試器和應用。

此外,利用賽靈思屢獲殊榮的 ISE?設計套件的優勢,Zynq-7000 系列的可編程 結構經定制可以最大化系統級性能,滿足特定應用的各種需求。該套件提供了包括 開發工具、AMB4AXI4 即插即用 IP 核和總線功能模型(BFM)等在內的完整硬件開發 環境,有助于加速設計和驗證工作。賽靈思通過收購高級綜合技術領先公司

AutoESL 進一步提升了在工具方面的進程,提供 C,C++以及系統 C 綜合優化 Zynq- 7000 器件架構。未來的版本也將促進 Zynq-7000 產品系列中處理器和可編程邏輯 之間關鍵算法的無縫銜接。

隨著時間的推移,ARM 互聯社區和賽靈思聯盟計劃生態系統的第三方廠商將進 一步擴展上述解決方案,這是賽靈思目標設計平臺的一部分,可提供包括 IP 核、

參考設計、開發套件及其他資源等在內的高效統一的開發環境,從而滿足特定應用 和設計領域要求。

可編程邏輯架構

Zynq-7000 系列的可編程邏輯完全基于賽靈思最新 7 系列 FPGA 架構來設計,可 確保 28nm 系列器件的 IP 核、工具和性能 100%兼容。最小型的 Zynq-7000、Zynq- 7010 和 Zynq-7020 均基于專門針對低成本和低功耗優化的Artix-7 系列;較大型 的 Zynq-7030 和 Zynq-7040 器件基于包括 4 至 12 個 10.3Gbps 收發器通道,可支持 高速片外連接的中端 Kintex-7 系列。所有四款產品均采用基于 2 個 12 位

1MspsADC(模數轉換器)模塊的新型模擬混合信號模塊。

第二章:開發板概述

2.1.開發板概述

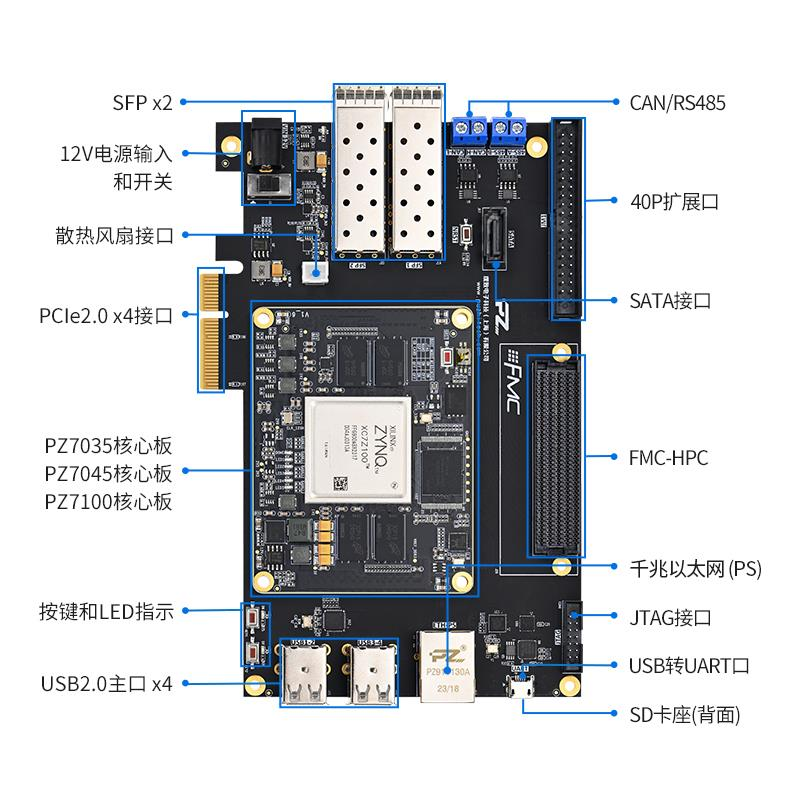

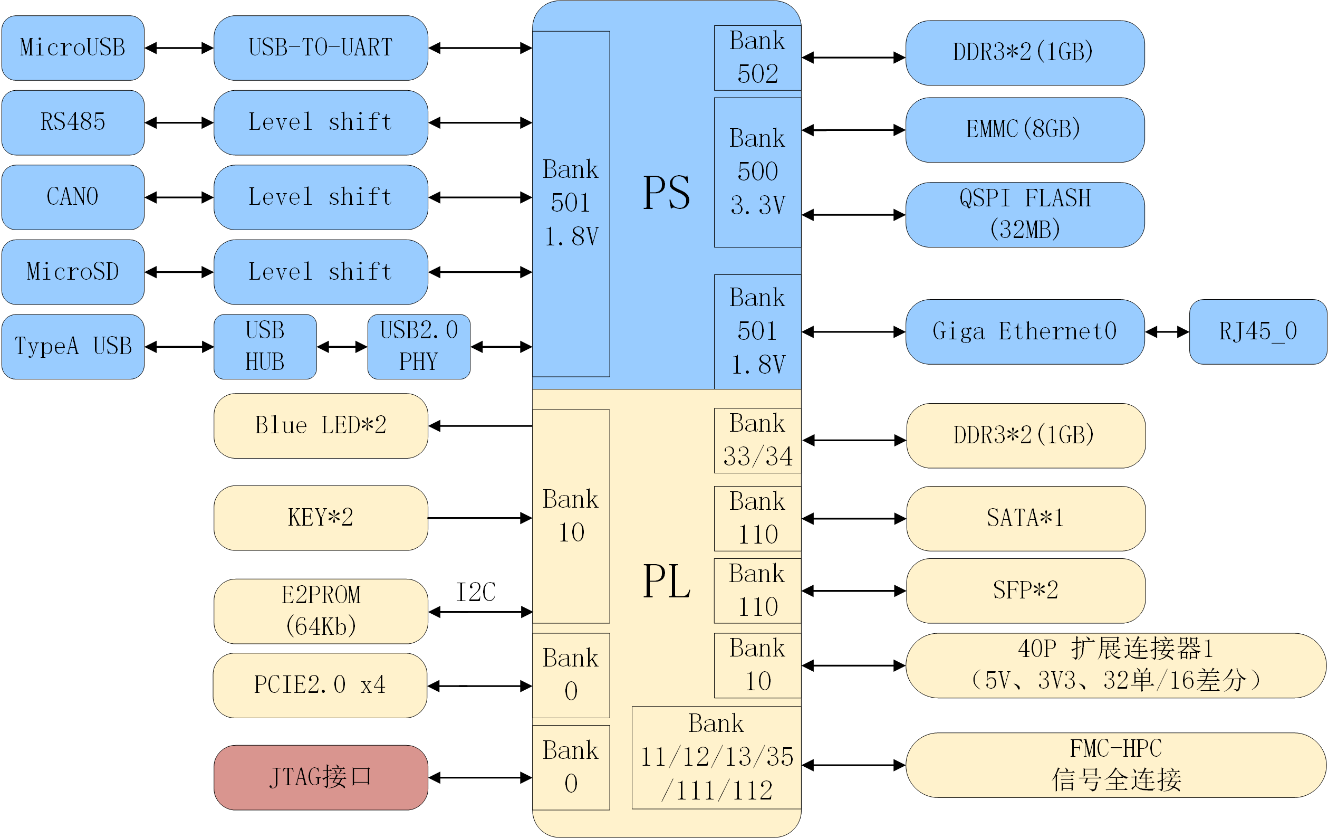

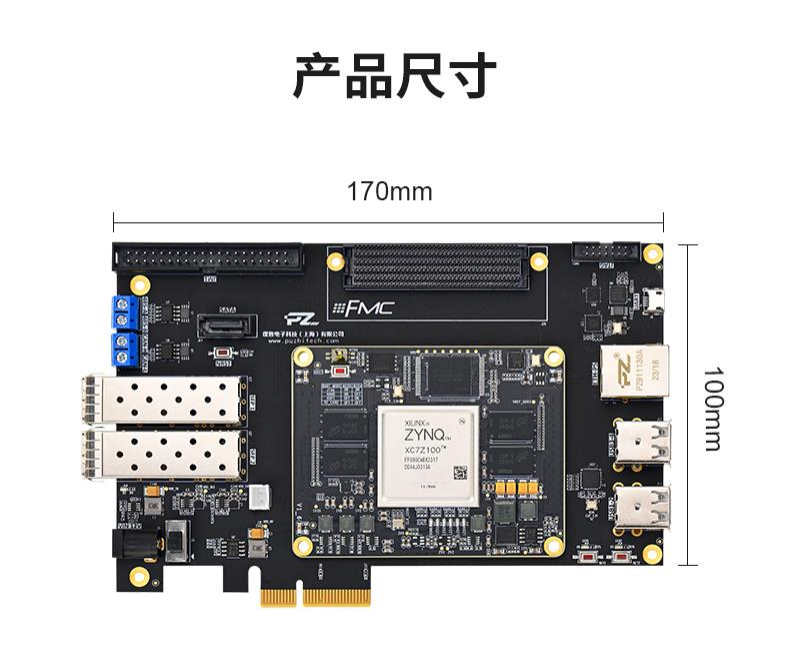

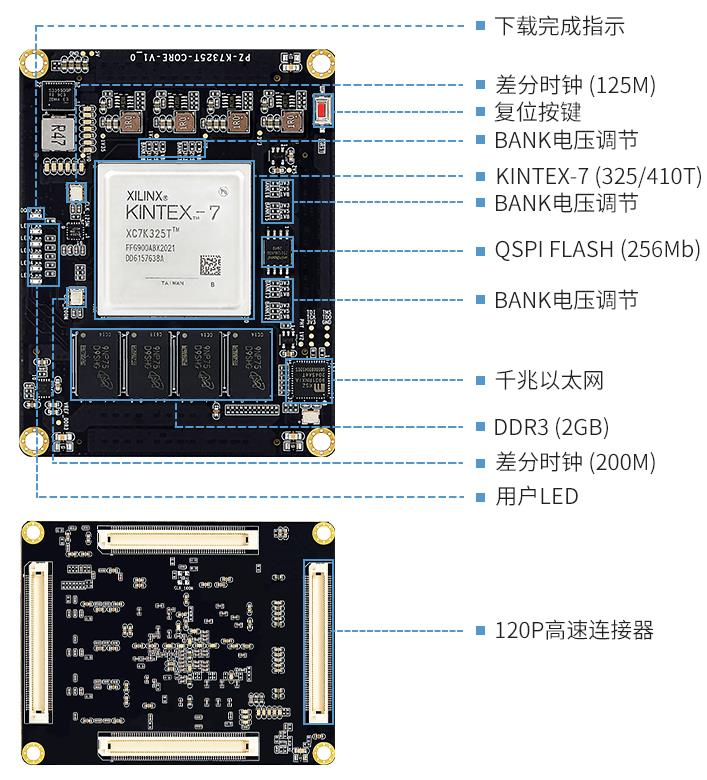

璞致電子科技 PZ7035-FH/PZ7045-FH/PZ7100-FH 開發板采用璞致電子科技自 研的核心板加底板模式。開發板分別采用 XILINX 公司的XC7Z035-2FFG900I、

XC7Z045-2FFG900I 和 XC7Z100-2FFG900I 芯片作為主控制器,三款開發板設計兼 容。開發板集成了豐富的外設資源,提供了詳盡的開發例程,為用戶的使用與驗 證提供便利。如下圖我們標示出各個外設在開發板的位置。

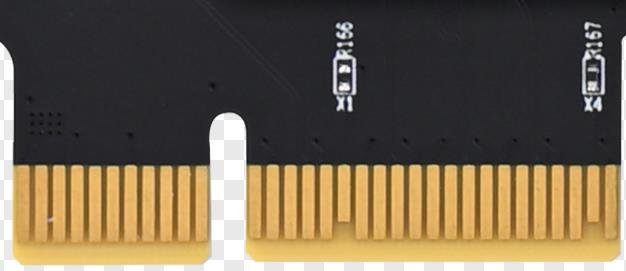

核心板通過四個 0.6mm 間距 120P 高速連接器扣接在底板上,使用上更加靈 活。既可以做學習使用,也可以使用核心板用于項目開發。

開發板尺寸為 170x100mm,單板的四個角各放置一個固定孔,用于安裝支撐 柱或固定單板,孔徑為 3.5mm。

添加圖片注釋,不超過 140 字(可選)

添加圖片注釋,不超過 140 字(可選)

添加圖片注釋,不超過 140 字(可選)

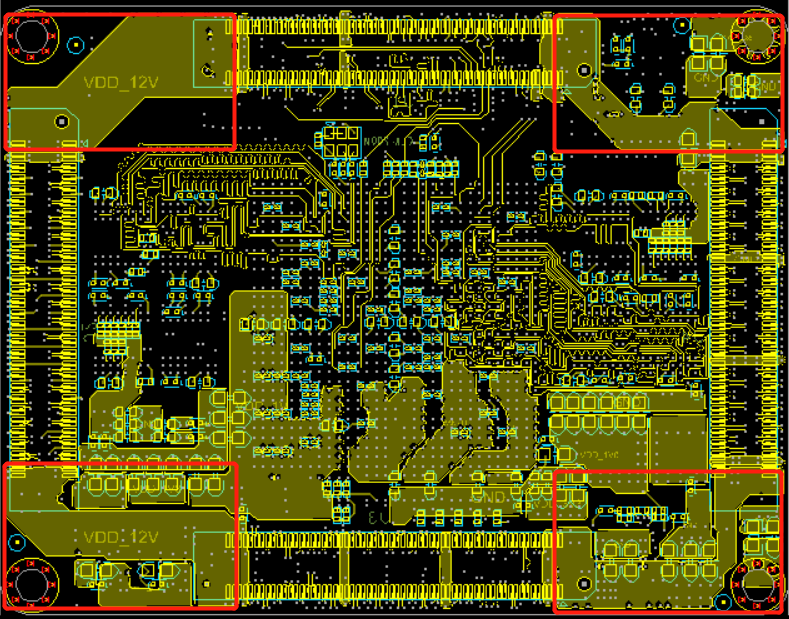

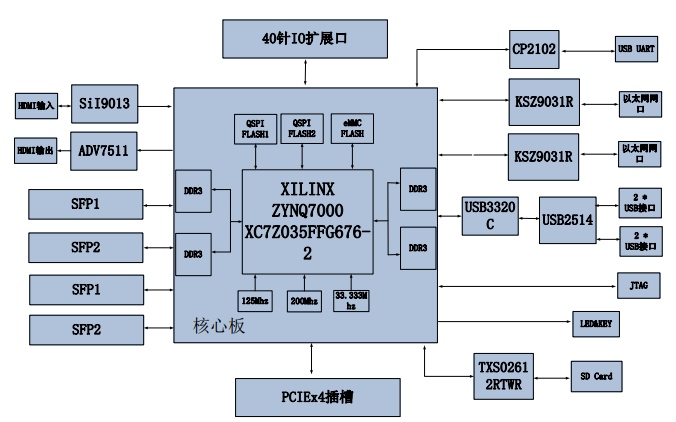

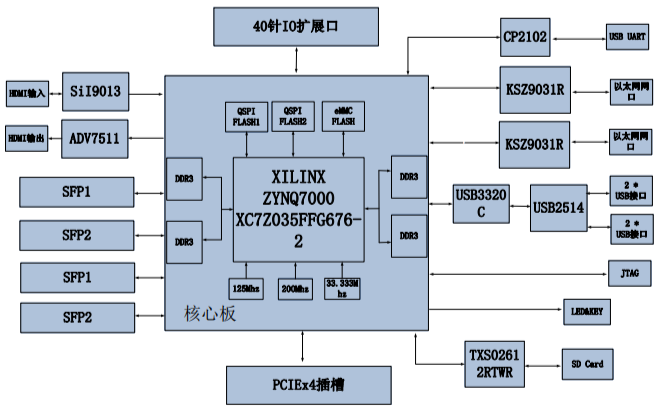

2.2.開發板資源與框圖

如下表與框圖已列出開發板板載資源,通過下表可以看到開發板所包含的 所有功能。

添加圖片注釋,不超過 140 字(可選)

添加圖片注釋,不超過 140 字(可選)

2.3.開發板尺寸

如下圖標出開發板尺寸為 170x100mm,開發板的四個角各放置一個固定孔, 用于安裝支撐柱或固定單板,孔徑為 3.5mm。開發板配置了風扇、散熱片以及亞 克力防護板,為方便展示,并沒有安裝到開發板上,下圖列出了散熱片和風扇 以及對應尺寸。

添加圖片注釋,不超過 140 字(可選)

第三章:PZ7035/PZ7045/PZ7100 核心板

3.1.核心板簡介

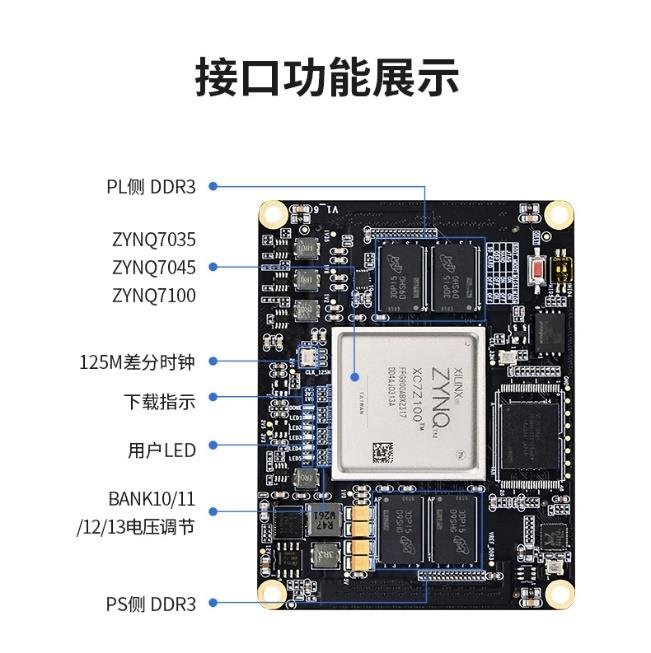

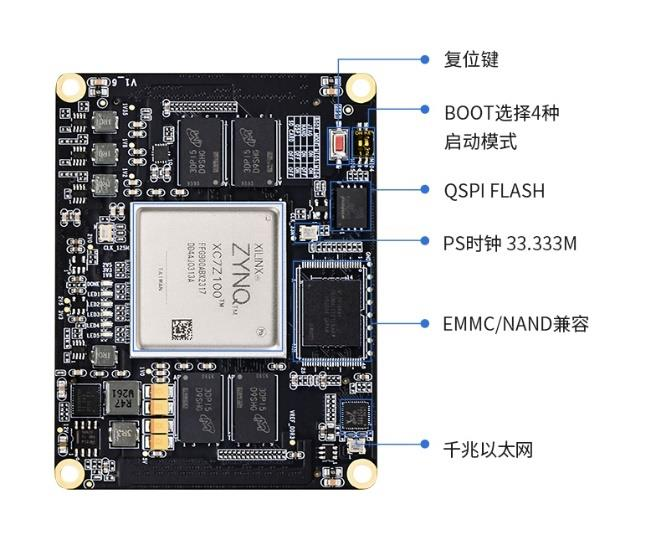

開發板采用了核心板扣接底板的方式,對于開發板的型號取決于使用的核 心板型號。核心板提供 PZ7035-SOM、PZ7045-SOM 和 PZ7100-SOM 三款,三款接 口完全兼容,通過更換核心板方式就可以實現開發板的型號更換。如下表列出 了三款核心板的參數以及之間的差異。

3.2.核心板規格

添加圖片注釋,不超過 140 字(可選)

3.3.核心板供電

核心板供電電壓范圍是 7-12V,在模塊的四個角都留有電源輸入管腳,電源管腳 在模塊內部已做了連通,此設計是為了方便底板的電源接入,設計時只需要連接一 個角上的電源管腳核心板即可工作,電源連接需用銅皮連接且打足夠的過孔保證電 源通流能力。模塊上的所有 GND 信號都需要連接到底板上,每個 GND 通過兩個過孔 與底板連接以確保通流能力。

給模組供電的電源輸出電壓需要穩定,如果電源不穩定,則需要在模組電源輸 入前級加一級 DCDC,從較高電壓轉到低壓,DCDC 電流輸出能力可以選 4A 左右,選 擇的 DCDC 芯片需要考慮效率,以免芯片發熱嚴重。

在核心板電源輸入處需至少放置 2 顆 220uF/25V—470uF/25V 電容保證電源質 量,因核心板電流較大,在成本允許情況下建議核心板單獨使用 DCDC 電源供電,

其他外設再用一路電源,電源分開。

添加圖片注釋,不超過 140 字(可選)

3.4.核心板時鐘

核心板為PS側提供了33.333333Mhz 的時鐘輸入,輸入的管腳位置為PS_CLK_500; 為 PL 側 提 供 了 200Mhz 的 差 分 時 鐘 輸 入 , PL 側 的 時 鐘 輸 入 管 腳 是 FPGA_13P_MRCC_34/FPGA_13N_MRCC_34,管腳位置是H9/G9;為 GTX 提供了一路 125Mhz 的差分時鐘輸入,輸入位置是 GTX 的 BANK110 的 CLK1,管腳位號是 AC8/AC7 的接入 了如下圖列出了連接方式。

需要注意的是:核心板上的 GTX CLK 可以給到 BANK109/110/111 使用,如使用 BANK112,需要在底板上加一路差分 125M 時鐘,可以參考開發板原理圖連接到 BANK112 的時鐘電路。

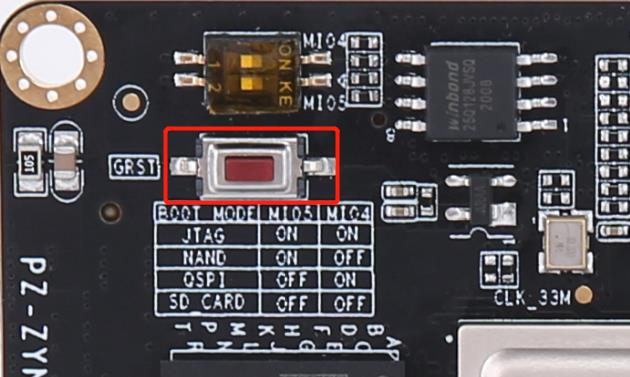

3.5.核心板全局復位

核心板提供了 nGST 復位按鍵,為系統復位按鍵,低電平有效。此引腳也引出到 了連接器,信號名稱為 SYS_nRST_I,方便用戶加入復位按鍵或者設計看門狗復位電 路。同時為了系統穩定,我們在核心板上加了復位芯片,復位輸出信號也引出到了 連接器上,信號名稱為 SYS_nRST_O,此信號可以用于單板其他外設的復位用,信號 電平是 3.3V。復位腳為 PS/PL 側共用復位,分別連接到 PS 側的 PS_POR_500 和 PL 側 的 IO_12P_9(管腳位置 AD18)引腳上。

如果底板上需要設計復位電路有以下幾種情況需考慮。

1)復位電路底板內部使用,只需要對地添加復位按鍵和一個 0.1uF 電容并口即 可。

2)復位電路需要預留在結構上供外部使用,需要添加對地按鍵,同時對地并聯 0.1uF 電容和 TVS 防靜電器件。

添加圖片注釋,不超過 140 字(可選)

3.7.網口連接

核心板上設計了一顆千兆以太網芯片,以太網芯片與 ZYNQ 芯片之間通過 RGMII 接口互聯,連接對應管腳見下表,以太網對外連接只需要一個帶變壓器的 RJ45 即可 使用,芯片地址 PHY_AD[2:0]=001,連接原理圖可參考下圖

注意:產品電路需要在網口信號線和 LED 上加靜電防護,0.1uF 電容選用耐壓 2KV 或者 3KV。

| RMGII 信號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| GTX_CLK | MIO16_501 | L19 |

| TXD0 | MIO17_501 | K21 |

| TXD1 | MIO18_501 | K20 |

| TXD2 | MIO19_501 | J20 |

| TXD3 | MIO20_501 | M20 |

| TX_EN | MIO21_501 | J19 |

| RX_CLK | MIO22_501 | L20 |

| RXD0 | MIO23_501 | J21 |

| RXD1 | MIO24_501 | M19 |

| RXD2 | MIO25_501 | G19 |

| RXD3 | MIO26_501 | M17 |

| RX_CTL | MIO27_501 | G20 |

| MDC | MIO52_501 | D19 |

| MDIO | MIO53_501 | C18 |

添加圖片注釋,不超過 140 字(可選)

3.8.EMMC管腳定義

板載 EMMC 容量 8GB,工作溫度為-40℃--+85℃,管腳定義如下表。

| EMMC 引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| EMMC_D0 | MIO10 | E22 |

| EMMC_D1 | MIO13 | F22 |

| EMMC_D2 | MIO14 | B22 |

| EMMC_D3 | MIO15 | C22 |

| EMMC_CLK | MIO12 | E21 |

| EMMC_CMD | MIO11 | A23 |

添加圖片注釋,不超過 140 字(可選)

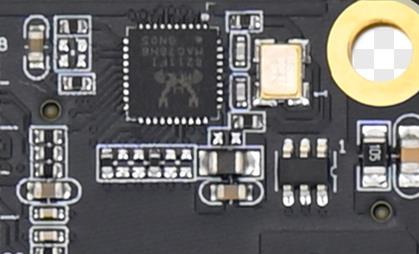

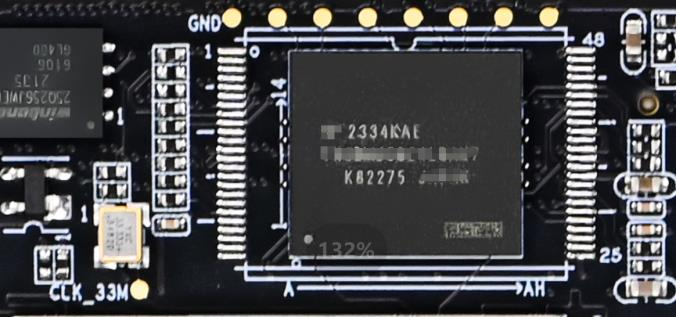

3.9.QSPIFLASH

核心板設計了一路 QSPI FLASH,容量為 256Mb,用戶可以定義為 QSPI X4 來加 速啟動。QSPI FLASH 可用于存儲啟動文件和用戶文件。

| QSPI FLASH 引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| DATA0 | MIO2 | F23 |

| DATA1 | MIO3 | C23 |

| DATA2 | MIO4 | E23 |

| DATA3 | MIO5 | C24 |

| QSPI_CS | MIO1 | D23 |

| QSPI_CLK | MIO6 | D24 |

添加圖片注釋,不超過 140 字(可選)

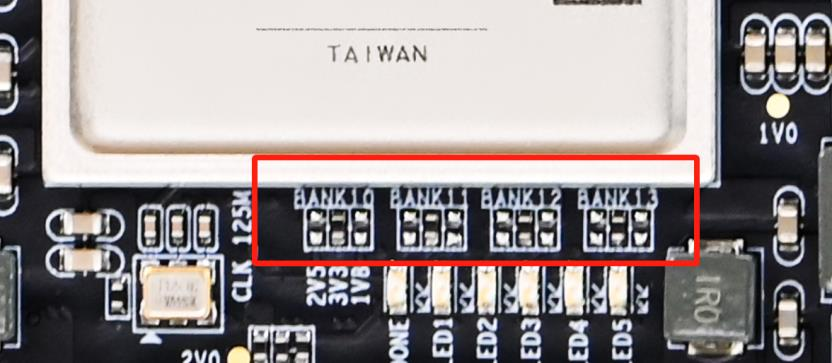

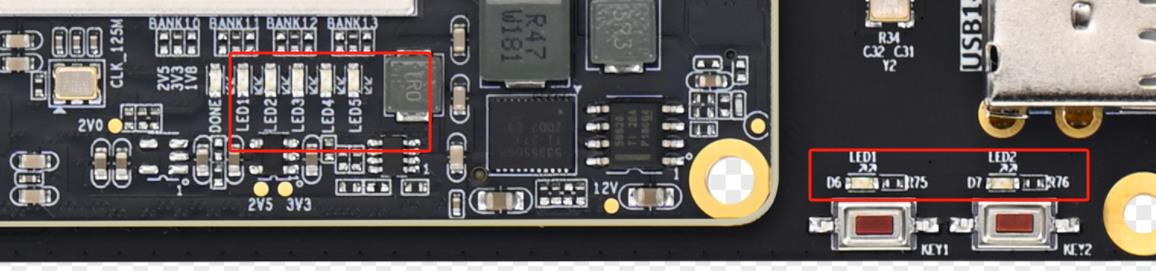

3.10.板載LED

為方便調試,核心板上放置了五顆 LED,LED 連接到 PL 側,LED 的管腳位置如下 表,當管腳輸出高電平時 LED 點亮,低電平 LED 滅。

| 序號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| LED1 | IO-L13N-9 | AA19 |

| LED2 | IO-L14P-9 | AB19 |

| LED3 | IO-L14N-9 | AB20 |

| LED4 | IO-L19P-9 | AD20 |

| LED5 | IO-L19N-9 | AE20 |

添加圖片注釋,不超過 140 字(可選)

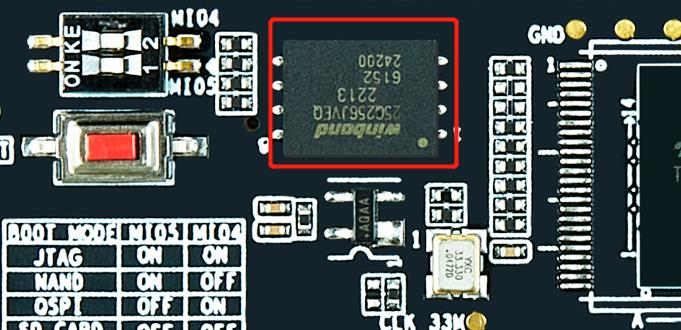

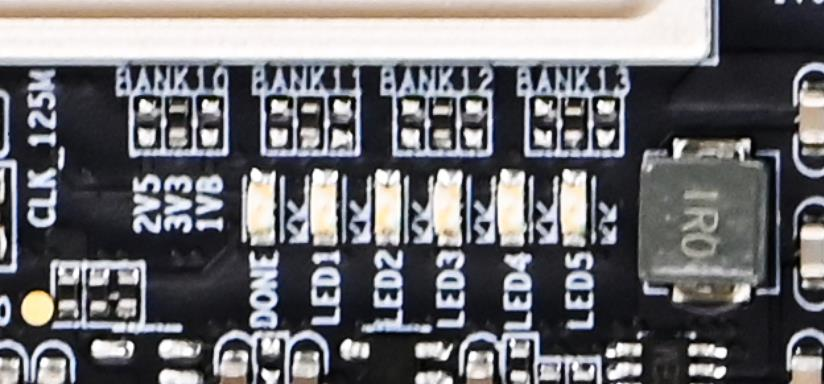

3.11.BANK接口電平選擇

單板上 BANK35 為 HP BANK,接口電平固定為 1.8V,BANK10/11/12/13 都可以通 過單板上提供的指示進行 0 歐姆電阻選焊,實現 1.8V/2.5V/3.3V 三種電平轉換。更 換電阻位置如下圖示,順序從左到右分別是 2.5V/3.3V/1.8V 選擇,默認焊接 3.3V 位 置,即 BANK10/11/12/13 默認接口電平為 3.3V。

添加圖片注釋,不超過 140 字(可選)

3.12.PS側DDR

PS 側配置了兩顆工業級 DDR3 芯片,單顆容量 512Mb,兩顆共計容量為 1GB, DDR3 管腳分配直接調用系統分配即可。也可以參考我司提供的例程。

15 / 32

3.13.PL側DDR

PL 側配置了兩顆工業級 DDR3 芯片,單顆容量 512Mb,兩顆共計容量為 1GB,型號 為 MT41K256M16TW-107IT:P,DDR3 管腳分配參見下表。

| DDR3 引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| DDR3_D0 | IO-L1N-33 | J3 |

| DDR3_D1 | IO-L4N-33 | L2 |

| DDR3_D2 | IO-L1P-33 | J4 |

| DDR3_D3 | IO-L4P-33 | L3 |

| DDR3_D4 | IO-L2N-33 | K1 |

| DDR3_D5 | IO-L6P-33 | K6 |

| DDR3_D6 | IO-L5N-33 | J5 |

| DDR3_D7 | IO-L5P-33 | K5 |

| DDR3_DM0 | IO-L2P-33 | L1 |

| DDR3_DQS_P0 | IO-L3P-33 | K3 |

| DDR3_DQS_N0 | IO-L3N-33 | K2 |

| DDR3_D8 | IO-L11P-33 | H4 |

| DDR3_D9 | IO-L10N-33 | G1 |

| DDR3_D10 | IO-L8P-33 | H6 |

| DDR3_D11 | IO-L7N-33 | F2 |

| DDR3_D12 | IO-L10P-33 | H2 |

| DDR3_D13 | IO-L12N-33 | G4 |

| DDR3_D14 | IO-L8N-33 | G6 |

| DDR3_D15 | IO-L11N-33 | H3 |

| DDR3_DM1 | IO-L12P-33 | G5 |

| DDR3_DQS_P1 | IO-L9P-33 | J1 |

| DDR3_DQS_N1 | IO-L9N-33 | H1 |

| DDR3_D16 | IO-L18P-33 | E1 |

| DDR3_D17 | IO-L17P-33 | E3 |

| DDR3_D18 | IO-L16N-33 | D3 |

| DDR3_D19 | IO-L14P-33 | F4 |

| DDR3_D20 | IO-L18N-33 | D1 |

| DDR3_D21 | IO-L13N-33 | E5 |

| DDR3_D22 | IO-L16P-33 | D4 |

| DDR3_D23 | IO-L17N-33 | E2 |

| DDR3_DM2 | IO-L14N-33 | F3 |

| DDR3_DQS_P2 | IO-L15P-33 | E6 |

| DDR3_DQS_N2 | IO-L15N-33 | D5 |

| DDR3_D24 | IO-L22P-33 | C2 |

| DDR3_D25 | IO-L24N-33 | A2 |

| DDR3_D26 | IO-L20N-33 | B4 |

| DDR3_D27 | IO-L20P-33 | B5 |

| DDR3_D28 | IO-L22N-33 | C1 |

|---|---|---|

| DDR3_D29 | IO-L24P-33 | A3 |

| DDR3_D30 | IO-L19P-33 | C4 |

| DDR3_D31 | IO-L23P-33 | B2 |

| DDR3_DM3 | IO-L23N-33 | B1 |

| DDR3_DQS_P3 | IO-L21P-33 | A5 |

| DDR3_DQS_N3 | IO-L21N-33 | A4 |

| DDR3_A0 | IO-L18P-34 | H7 |

| DDR3_A1 | IO-L21P-34 | L8 |

| DDR3_A2 | IO-L7N-34 | H11 |

| DDR3_A3 | IO-L10N-34 | D10 |

| DDR3_A4 | IO-L15N-34 | H8 |

| DDR3_A5 | IO-L8N-34 | D11 |

| DDR3_A6 | IO-L19P-34 | L7 |

| DDR3_A7 | IO-L10P-34 | E10 |

| DDR3_A8 | IO-L23P-34 | L10 |

| DDR3_A9 | IO-L9P-34 | H12 |

| DDR3_A10 | IO-L18N-34 | G7 |

| DDR3_A11 | IO-L20N-34 | J9 |

| DDR3_A12 | IO-L14P-34 | F9 |

| DDR3_A13 | IO-L7P-34 | J11 |

| DDR3_A14 | IO-L22N-34 | K10 |

| DDR3_BA0 | IO-L22P-34 | K11 |

| DDR3_BA1 | IO-L21N-34 | K8 |

| DDR3_BA2 | IO-L9N-34 | G11 |

| DDR3_CS | IO-L16P-34 | F8 |

| DDR3_RAS | IO-L14N-34 | E8 |

| DDR3_CAS | IO-L17P-34 | E7 |

| DDR3_WE | IO-L16N-34 | F7 |

| DDR3_ODT | IO-L20P-34 | J10 |

| DDR3_RESET | IO-L8P-34 | E11 |

| DDR3_CLK_P | IO-L12P-34 | D9 |

| DDR3_CLK_N | IO-L12N-34 | D8 |

| DDR3_CKE | IO-L17N-34 | D6 |

3.14.核心板信號與等長

核心板引出到連接器的信號都做了嚴格等長,可以參考璞致提供的信號等長表 格,里面詳細列出了信號名稱和信號走線長度。

3.15.核心板封裝庫

為方便用戶快速使用核心板,我們提供了對應的封裝庫,連接器相對位置和核 心板外框絲印都已擺放好,直接調用即可。原理圖封裝提供 AD/ORCAD 兩個版本,PCB 封裝提供 AD/Allegro 兩個版本,均已存放在對應的文件夾下。另外,文件夾下提供 了核心板的 DXF 文件,方便用戶對應結構。

3.16.核心板對應連接器

核心板采用了兩個高密連接器與底板連接,底板上使用的連接器對應型號是 FX8-120S-SV,用戶可以自行購買,也可以聯系璞致客服購買。

第四章PZ7035/PZ7045/PZ7100 底板

4.1.電源供電

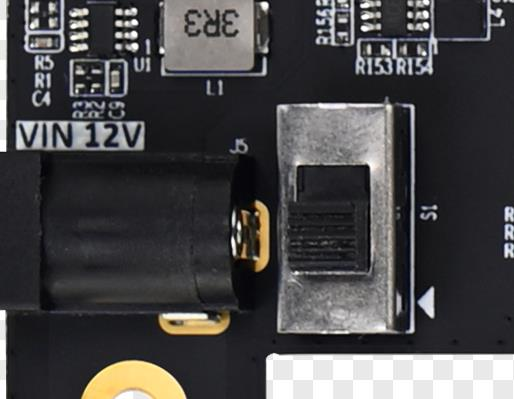

開發板采用 12V/3A 的適配器供電,電源接入后通過 DCDC 轉換成 8V、5V、3.3V 等多路電壓供板內器件使用。接入 12V 電源可以通過開關 S1開關來控制通斷, 電源 部分詳細電路可參考開發板對應的原理圖。

添加圖片注釋,不超過 140 字(可選)

4.2.時鐘電路

時鐘電路主要設計在核心板上,核心板為 PS 側提供了 33.33Mhz 的時鐘輸入, 輸入的管腳位置為 PS_CLK_500;為 PL 側提供了 200Mhz/125Mhz 時鐘,詳細電路可 參考核心板時鐘電路部分說明或核心板原理圖。

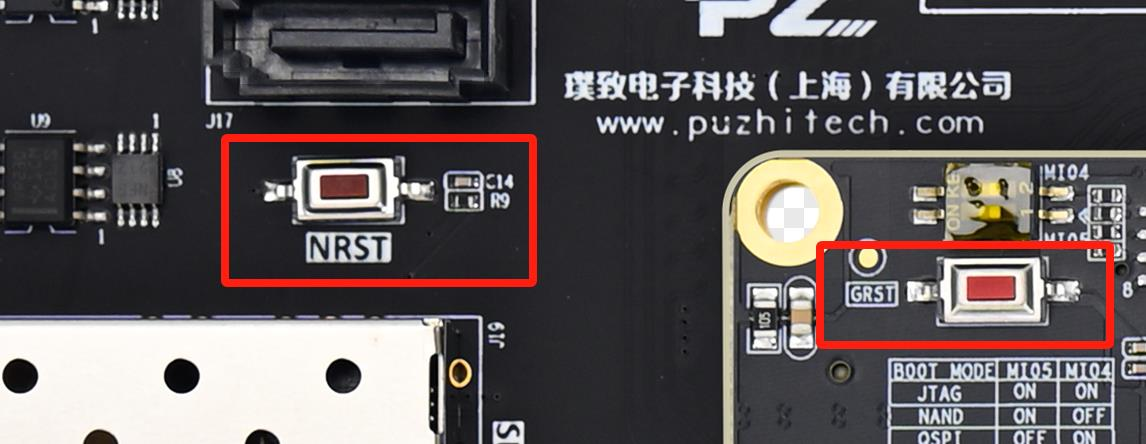

4.3.復位電路

開發板上有兩個復位按鍵,一路集成到核心板上了,一路在開發板上。復位信 號名稱是 SYS_nRST_I 。 同 時為 了系 統穩定 ,我們在核 心板上加 了 復位芯 片 MAX811TUES,復位輸出信號也引出到了連接器上,信號名稱為 SYS_nRST_O,此信號 可以用于單板其他外設的復位用,信號電平是 3.3V。復位腳為 PS/PL 側共用復位, 分別連接到 PS 側的 PS_POR_500 和 PL 側的 IO_12P_9(管腳位置 AD18)引腳上。

添加圖片注釋,不超過 140 字(可選)

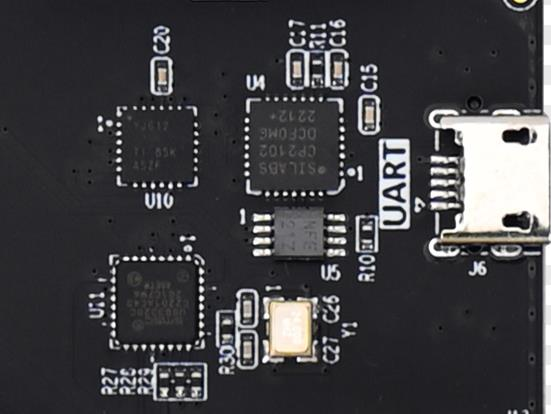

4.4.USB轉串口

開發板使用 Silicon Labs CP2102GM 芯片實現 USB 轉 UART, USB 接口采用 Micro USB,用戶只要用一根 Micro USB 線連接到 PC 上即可進行串口通信開發。

UART 的 TX/RX 信號與 ZYNQ 的 PS 側BANK501 相連,因為BANK501 的電平為 1.8V, 但 CP2102GM 的數據電平為 3.3V, 所以我們使用 TXS0102DCUR 進行電平轉換。

如下是信號對應關系表和原理圖,TX/RX 方向為 ZYNQ 端定義。

| UART0 引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| UART0_TX | MIO47 | A18 |

| UART0_RX | MIO46 | F20 |

添加圖片注釋,不超過 140 字(可選)

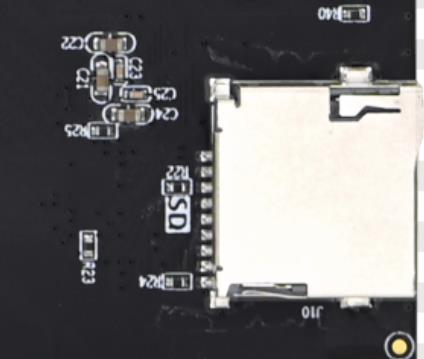

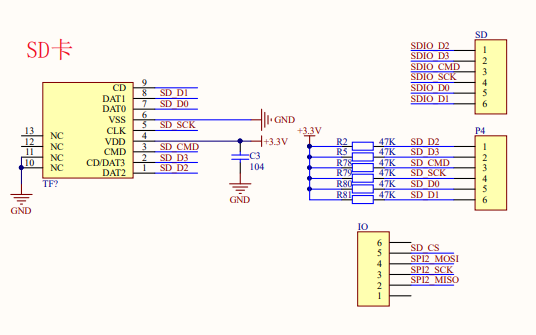

4.5.SD卡

開發板上設計了 SD 卡卡座,與 ZYNQ 的 PS 側 BANK501 相連,因為 BANK501 的電 平為 1.8V,但 SD 的數據電平為 3.3V,我使用TXS02612RTWR 進行電平轉換。

如下是 SD 卡的管腳分配與原理圖。

| SD 卡引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| SD_CLK | MIO40 | B20 |

| SD_CMD | MIO41 | J18 |

| SD_DATA0 | MIO42 | D20 |

| SD_DATA1 | MIO43 | E18 |

| SD_DATA2 | MIO44 | E20 |

| SD_DATA3 | MIO45 | H18 |

添加圖片注釋,不超過 140 字(可選)

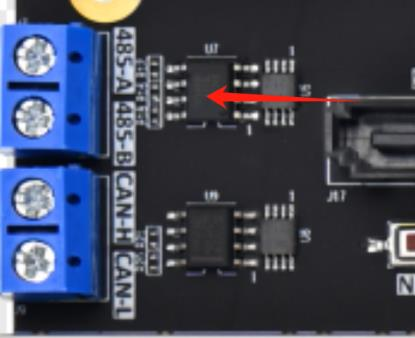

4.6.RS485接口

開發板使用 SP3485 芯片實現 RS485, RS485 對外接口采用 2 腳 KF301 連接器。

RS485 的 TX/RX 信號與 ZYNQ 的 PS 側 BANK501 相連,即為 URAT1,因為 BANK501 的電平為 1.8V,但 SP3485EN 的數據電平為 3.3V, 所以我們使用 TXS0102DCUR 進行 電平轉換。

另外 RS485 為半雙工通信,需要做信號方向切換,此部分璞致電子科技已為用戶 考慮周全,實現信號發送和接收的自由切換。

如下是信號對應關系表和原理圖,TX/RX 方向為 ZYNQ 端定義。

| RS485 引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| RS485_TX | MIO48 | C19 |

| RS485_RX | MIO49 | D18 |

?

4.7.CAN接口

開發板使用 SN65HVD230D 芯片實現 CAN 通信, CAN 對外接口采用 2 腳 KF301 連 接器。CAN 的 TX/RX 信號與 ZYNQ 的 PS 側 BANK501 相連,即為 CAN0,因為 BANK501 的 電平為 1.8V,但 SN65HVD230D 的數據電平為 3.3V, 所以我們使用 TXS0102DCUR 進行 電平轉換。

如下是信號對應關系表和原理圖,TX/RX 方向為 ZYNQ 端定義。

| CAN 引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| CAN_TX | MIO51 | F19 |

| CAN_RX | MIO50 | A19 |

添加圖片注釋,不超過 140 字(可選)

4.8.E2PROM

開發板上放置了一顆 64Kbit 的 EEPROM 芯片,型號為 AT24C64D-SSHM-T,與 FPGA 的 BANK34 通過 IIC 總線相連。EEPROM 讀地址是 0xA1,寫地址是 0xA0。

如下是 EEPROM 的管腳分配,詳細電路可以參考開發板原理圖。

| EEPROM 引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| IIC-SCL | IO-20P-10 | AA15 |

| IIC-SDA | IO-20N-10 | AA14 |

添加圖片注釋,不超過 140 字(可選)

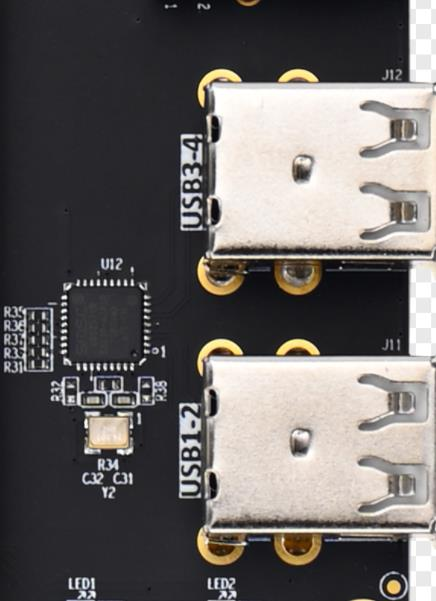

4.9.USB2.0接口

開發板設計了 USB PHY 和 USB HUB 芯片,擴展出 4 個 USB2.0 主接口。USB PHY 需要配置成 OTG 工作模式。

如下是 USB2.0 的引腳分配, 詳細電路可以參考開發板原理圖。

| USB 引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| USBPHY_DATA0 | MIO32 | K17 |

| USBPHY_DATA1 | MIO33 | G22 |

| USBPHY_DATA2 | MIO34 | K18 |

| USBPHY_DATA3 | MIO35 | G21 |

| USBPHY_DATA4 | MIO28 | L17 |

22 / 32

| USBPHY_DATA5 | MIO37 | B21 |

|---|---|---|

| USBPHY_DATA6 | MIO38 | A20 |

| USBPHY_DATA7 | MIO39 | F18 |

| USBPHY_STP | MIO30 | L18 |

| USBPHY_NXT | MIO31 | H21 |

| USBPHY_DIR | MIO29 | H22 |

| USBPHY_CLKOUT | MIO36 | H17 |

| USBPHY_nRSET | IO_6P_35 | J16 |

添加圖片注釋,不超過 140 字(可選)

4.10.千兆以太網

開發板上放置了一顆千兆以太網芯片。已集成到核心板上, 掛接在 PS 側,我們 定義為 PHY0。以太網芯片與 ZYNQ 芯片之間均通過 RGMII 接口互連。核心板上 PHY0 對外只需要連接集成變壓器的 RJ45 即可。PHY0 芯片地址 PHY_AD[2:0]=001,信號連 接參考下表,原理圖如下圖。

| RMGII 信號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| GTX_CLK | MIO16_501 | L19 |

| TXD0 | MIO17_501 | K21 |

| TXD1 | MIO18_501 | K20 |

| TXD2 | MIO19_501 | J20 |

| TXD3 | MIO20_501 | M20 |

| TX_EN | MIO21_501 | J19 |

| RX_CLK | MIO22_501 | L20 |

| RXD0 | MIO23_501 | J21 |

| RXD1 | MIO24_501 | M19 |

| RXD2 | MIO25_501 | G19 |

| RXD3 | MIO26_501 | M17 |

| RX_CTL | MIO27_501 | G20 |

| MDC | MIO52_501 | D19 |

| MDIO | MIO53_501 | C18 |

4.11.SFP接口

開發板上放置了兩路 SFP 接口,ZYNQ7035/7045/7100 支持的 GTX 接口最高速度 可以到 10Ghz。GTX 時鐘為 125Mhz,輸入管腳名稱是MGT-CLK1P-110/MGT-CLK1N-110, 管腳位置是 AC8/AC7。

如下表列出了引腳信號對應關系:

| SFP 引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| SFP1_TX_P | MGT_110_TX_P1 | AF2 |

| SFP1_TX_N | MGT_110_TX_N1 | AF1 |

| SFP1_RX_P | MGT_110_RX_P1 | AG4 |

| SFP1_RX_N | MGT_110_RX_N1 | AG3 |

| SFP1_TX_DISABLE | IO_7P_10 | AE12 |

| SFP1_RxRATE_SEL | IO_7N_10 | AF12 |

| SFP2_TX_P | MGT_110_TX_P0 | AH2 |

| SFP2_TX_N | MGT_110_TX_N0 | AH1 |

| SFP2_RX_P | MGT_110_RX_P0 | AH6 |

| SFP2_RX_N | MGT_110_RX_N0 | AH5 |

| SFP2_TX_DISABLE | IO_10P_10 | AG12 |

| SFP2_RxRATE_SEL | IO_10N_10 | AH12 |

添加圖片注釋,不超過 140 字(可選)

4.12.SATA接口

開發板上設計了 1 路 SATA 接口,如下表列出了管腳對應關系,詳細電路可以參 考開發板原理圖。

| SATA 接口 | 管腳名稱 | 管腳位置 |

|---|---|---|

| SATA1_TX_P | MGT_TX_P0_110 | AD2 |

| SATA1_TX_N | MGT_TX_N0_110 | AD1 |

| SATA1_RX_P | MGT_RX_P0_110 | AD6 |

| SATA1_RX_N | MGT_RX_N0_110 | AD5 |

添加圖片注釋,不超過 140 字(可選)

4.13.LED

核心板設計了五路 LED,開發板設計了兩路 LED,共計七路 LED。LED 高電平亮, 低電平滅。詳細電路可參考開發板原理圖。

| LED 位號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| LED1(核心板) | IO_13N_9 | AA19 |

| LED2(核心板) | IO_14P_9 | AB19 |

| LED3(核心板) | IO_14N_9 | AB20 |

| LED4(核心板) | IO_19P_9 | AD20 |

| LED5(核心板) | IO_19N_9 | AE20 |

| LED1(開發板) | IO_9P_10 | AD14 |

| LED2(開發板) | IO_9N_10 | AD13 |

添加圖片注釋,不超過 140 字(可選)

4.14.按鍵

開發板上設計了 2 路按鍵,按鍵上拉到 3.3V,按鍵后為低,即低電平有效。如 下表列出了按鍵的連接對應關系。

| 按鍵位號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| KEY1 | IO_21P_10 | AB12 |

| KEY2 | IO_21N_10 | AC12 |

添加圖片注釋,不超過 140 字(可選)

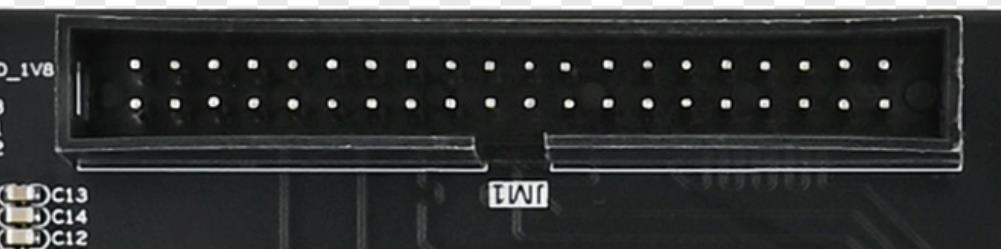

4.15.40P擴展接口

開發板板載了一個 40P 2.54mm 間距的簡易牛角座,用于擴展信號的連接,接口 電平默認 3.3V。

如下表標出了信號所在的芯片位置,詳細連接關系參考原理圖部分。

| JM1 信號順序 | 管腳名稱 | 管腳位置 | JM1 信號順序 | 管腳名稱 | 管腳位置 |

|---|---|---|---|---|---|

| 5 | IO_L8P_10 | AH14 | 6 | IO_L12P_MRCC_1 | AF14 |

| 7 | IO_L8N_10 | AH13 | 8 | IO_L12N_MRCC_1 | AG14 |

| 9 | IO_L5P_10 | AJ15 | 10 | IO_L22P_10 | AB15 |

| 11 | IO_L5N_10 | AK15 | 12 | IO_L22N_10 | AB14 |

| 13 | IO_L3P_10 | AJ14 | 14 | IO_L19P_10 | AC14 |

| 15 | IO_L3N_10 | AJ13 | 16 | IO_L19N_10 | AC13 |

| 17 | IO_L18P_10 | AD16 | 18 | IO_L6P_10 | AH17 |

| 19 | IO_L18N_10 | AD15 | 20 | IO_L6N_10 | AH16 |

| 21 | IO_L14P_SRCC_10 | AF15 | 22 | IO_L16P_10 | AE16 |

| 23 | IO_L14N_SRCC_10 | AG15 | 24 | IO_L16N_10 | AE15 |

| 25 | IO_L17P_10 | AE18 | 26 | IO_L23P_10 | AC17 |

| 27 | IO_L17N_10 | AE17 | 28 | IO_L23N_10 | AC16 |

| 29 | IO_L13P_MRCC_10 | AG17 | 30 | IO_L15P_10 | AF18 |

| 31 | IO_L13N_MRCC_10 | AG16 | 32 | IO_L15N_10 | AF17 |

| 37 | IO_L4P_10 | AJ16 | 38 | IO_L2P_10 | AH18 |

| 39 | IO_L4N_10 | AK16 | 40 | IO_L2N_10 | AJ18 |

添加圖片注釋,不超過 140 字(可選)

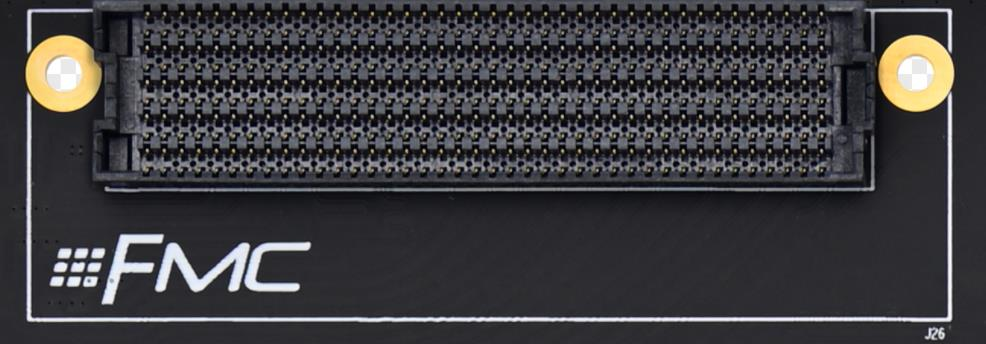

4.16.FMC擴展接口

開發板上設計了一路 FMC 連接器,接口類型為 HPC,如下表列出了信號對應關 系。詳細連接關系參考原理圖部分。

| FMC-HPC 管腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| LA00_P_CC | IO_L14P_SRCC_13 | R27 |

| LA00_N_CC | IO_ L14N_SRCC | T27 |

| LA01_P_CC | IO_L13P_MRCC_13 | R25 |

| LA01_N_CC | IO_ L13N_MRCC | R26 |

| LA02_P | IO_L19P_13 | P21 |

| LA02_N | IO_L19N_13 | R21 |

| LA03_P | IO_L3P_13 | N28 |

| LA03_N | IO_L3N_13 | P28 |

| LA04_P | IO_L17P_13 | T24 |

| LA04_N | IO_L17N_13 | T25 |

| LA05_P | IO_L22P_13 | U22 |

| LA05_N | IO_L22N_13 | V22 |

| LA06_P | IO_L2P_13 | T30 |

| LA06_N | IO_L2N_13 | U30 |

| LA07_P | IO_L4P_13 | N29 |

| LA07_N | IO_L4N_13 | P29 |

| LA08_P | IO_L8P_13 | W29 |

| LA08_N | IO_L8N_13 | W30 |

| LA09_P | IO_L7P_13 | V28 |

| LA09_N | IO_L7N_13 | V29 |

| LA10_P | IO_L23P_13 | U24 |

| LA10_N | IO_L23N_13 | V24 |

| LA11_P | IO_L21P_13 | R22 |

| LA11_N | IO_L21N_13 | R23 |

| LA12_P | IO_L10P_13 | W25 |

| LA12_N | IO_L10N_13 | W26 |

| LA13_P | IO_L6P_13 | R28 |

| LA13_N | IO_L6N_13 | T28 |

| LA14_P | IO_L9P_13 | V27 |

| LA14_N | IO_L9N_13 | W28 |

| LA15_P | IO_L18P_13 | P23 |

| LA15_N | IO_L18N_13 | P24 |

| LA16_P | IO_L16P_13 | P25 |

| LA16_N | IO_L16N_13 | P26 |

| LA17_P_CC | IO_L12P_MRCC_13 | U26 |

| LA17_N_CC | IO_L12N_MRCC_13 | U27 |

| LA18_P_CC | IO_L11P_SRCC_13 | U25 |

| LA18_N_CC | IO_L11N_SRCC_13 | V26 |

| LA19_P | IO_L20P_13 | T22 |

| LA19_N | IO_L20N_13 | T23 |

| LA20_P | IO_L15P_13 | N26 |

| LA20_N | IO_L15N_13 | N27 |

| LA21_P | IO_L24P_13 | V23 |

|---|---|---|

| LA21_N | IO_L24N_13 | W24 |

| LA22_P | IO_L1P_13 | P30 |

| LA22_N | IO_L1N_13 | R30 |

| LA23_P | IO_L5P_13 | T29 |

| LA23_N | IO_L5N_13 | U29 |

| LA24_P | IO_L8P_12 | AD30 |

| LA24_N | IO_L8N_12 | AE30 |

| LA25_P | IO_L3P_12 | Y26 |

| LA25_N | IO_L3N_12 | Y27 |

| LA26_P | IO_L20P_12 | AJ30 |

| LA26_N | IO_L20N_12 | AK30 |

| LA27_P | IO_L16P_12 | AF30 |

| LA27_N | IO_L16N_12 | AG30 |

| LA28_P | IO_L9P_12 | AC29 |

| LA28_N | IO_L9N_12 | AD29 |

| LA29_P | IO_L1P_12 | Y30 |

| LA29_N | IO_L1N_12 | AA30 |

| LA30_P | IO_L24P_12 | AJ26 |

| LA30_N | IO_L24N_12 | AK26 |

| LA31_P | IO_L10P_12 | AD25 |

| LA31_N | IO_L10N_12 | AE26 |

| LA32_P | IO_L23P_12 | AH26 |

| LA32_N | IO_L23N_12 | AH27 |

| LA33_P | IO_L17P_12 | AG26 |

| LA33_N | IO_L17N_12 | AG27 |

| FMC_IIC_SCL | IO_L11P_10 | AE13 |

| FMC_IIC_SDA | IO_L11N_10 | AF13 |

| DP0_M2C_P | MGT_RX_P0_111 | AC4 |

| DP0_M2C_N | MGT_RX_N0_111 | AC3 |

| DP1_M2C_P | MGT_RX_P1_111 | AB6 |

| DP1_M2C_N | MGT_RX_N1_111 | AB5 |

| DP2_M2C_P | MGT_RX_P2_111 | Y6 |

| DP2_M2C_N | MGT_RX_N2_111 | Y5 |

| DP3_M2C_P | MGT_RX_P3_111 | AA4 |

| DP3_M2C_N | MGT_RX_N3_111 | AA3 |

| DP4_M2C_P | MGT_RX_P0_112 | V6 |

| DP4_M2C_N | MGT_RX_N0_112 | V5 |

| DP5_M2C_P | MGT_RX_P1_112 | U4 |

| DP5_M2C_N | MGT_RX_N1_112 | U3 |

| DP6_M2C_P | MGT_RX_P2_112 | T6 |

| DP6_M2C_N | MGT_RX_N2_112 | T5 |

| DP7_M2C_P | MGT_RX_P3_112 | P6 |

| DP7_M2C_N | MGT_RX_N3_112 | P5 |

| GBTCLK0_M2C_P | MGT_CLK0_P_111 | U8 |

| GBTCLK0_M2C_N | MGT_CLK0_N_111 | U7 |

| GBTCLK1_M2C_P | MGT_CLK0_P_112 | N8 |

| GBTCLK1_M2C_N | MGT_CLK0_N_112 | N7 |

| DP0_C2M_P | MGT_TX_P0_111 | AB2 |

|---|---|---|

| DP0_C2M_N | MGT_TX_N0_111 | AB1 |

| DP1_C2M_P | MGT_TX_P1_111 | Y2 |

| DP1_C2M_N | MGT_TX_N1_111 | Y1 |

| DP2_C2M_P | MGT_TX_P2_111 | W4 |

| DP2_C2M_N | MGT_TX_N2_111 | W3 |

| DP3_C2M_P | MGT_TX_P3_111 | V2 |

| DP3_C2M_N | MGT_TX_N3_111 | V1 |

| DP4_C2M_P | MGT_TX_P0_112 | T2 |

| DP4_C2M_N | MGT_TX_N0_112 | T1 |

| DP5_C2M_P | MGT_TX_P1_112 | R4 |

| DP5_C2M_N | MGT_TX_N1_112 | R3 |

| DP6_C2M_P | MGT_TX_P2_112 | P2 |

| DP6_C2M_N | MGT_TX_N2_112 | P1 |

| DP7_C2M_P | MGT_TX_P3_112 | N4 |

| DP7_C2M_N | MGT_TX_N3_112 | N3 |

| HA00_P_CC | IO_L13P_MRCC_11 | AG21 |

| HA00_N_CC | IO_L13N_MRCC_11 | AH21 |

| HA01_P_CC | IO_L12P_MRCC_11 | AE22 |

| HA01_N_CC | IO_L12N_MRCC_11 | AF22 |

| HA02_P | IO_L5P_11 | AH23 |

| HA02_N | IO_L5N_11 | AH24 |

| HA03_P | IO_L11P_11 | AD23 |

| HA03_N | IO_L11N_11 | AE23 |

| HA04_P | IO_L7P_11 | AC24 |

| HA04_N | IO_L7N_11 | AD24 |

| HA05_P | IO_L21P_11 | Y22 |

| HA05_N | IO_L21N_11 | Y23 |

| HA06_P | IO_L1P_11 | AJ25 |

| HA06_N | IO_L1N_11 | AK25 |

| HA07_P | IO_L8P_11 | AG24 |

| HA07_N | IO_L8N_11 | AG25 |

| HA08_P | IO_L19P_11 | AB21 |

| HA08_N | IO_L19N_11 | AB22 |

| HA09_P | IO_L22P_11 | AA24 |

| HA09_N | IO_L22N_11 | AB24 |

| HA10_P | IO_L16P_11 | AK17 |

| HA10_N | IO_L16N_11 | AK18 |

| HA11_P | IO_L2P_11 | AK22 |

| HA11_N | IO_L2N_11 | AK23 |

| HA12_P | IO_L24P_11 | AC22 |

| HA12_N | IO_L24N_11 | AC23 |

| HA13_P | IO_L9P_11 | AF23 |

| HA13_N | IO_L9N_11 | AF24 |

| HA14_P | IO_L6P_11 | AG22 |

| HA14_N | IO_L6N_11 | AH22 |

| HA15_P | IO_L23P_11 | AA22 |

| HA15_N | IO_L23N_11 | AA23 |

| HA16_P | IO_L18P_11 | AF19 |

|---|---|---|

| HA16_N | IO_L18N_11 | AG19 |

| HA17_P_CC | IO_L14P_SRCC_11 | AF20 |

| HA17_N_CC | IO_L14N_SRCC_11 | AG20 |

| HA18_P | IO_L4P_11 | AJ23 |

| HA18_N | IO_L4N_11 | AJ24 |

| HA19_P | IO_L17P_11 | AH19 |

| HA19_N | IO_L17N_11 | AJ19 |

| HA20_P | IO_L20P_11 | W21 |

| HA20_N | IO_L20N_11 | Y21 |

| HA21_P | IO_L3P_11 | AJ21 |

| HA21_N | IO_L3N_11 | AK21 |

| HA22_P | IO_L10P_11 | AD21 |

| HA22_N | IO_L10N_11 | AE21 |

| HA23_P | IO_L15P_11 | AJ20 |

| HA23_N | IO_L15N_11 | AK20 |

| HB00_P_CC | IO_L12P_MRCC_35 | F15 |

| HB00_N_CC | IO_L12N_MRCC_35 | F14 |

| HB01_P | IO_L18P_35 | B17 |

| HB01_N | IO_L18N_35 | A17 |

| HB02_P | IO_L15P_35 | F17 |

| HB02_N | IO_L15N_35 | E17 |

| HB03_P | IO_L16P_35 | D16 |

| HB03_N | IO_L16N_35 | C16 |

| HB04_P | IO_L17P_35 | C17 |

| HB04_N | IO_L17N_35 | B16 |

| HB05_P | IO_L1P_35 | L15 |

| HB05_N | IO_L1N_35 | L14 |

| HB06_P | IO_L14P_SRCC_35 | D15 |

| HB06_N | IO_L14N_SRCC_35 | D14 |

| HB07_P | IO_L4P_35 | J14 |

| HB07_N | IO_L4N_35 | H14 |

| HB08_P | IO_L20P_35 | C12 |

| HB08_N | IO_L20N_35 | B12 |

| HB09_P | IO_L8P_35 | G15 |

| HB09_N | IO_L8N_35 | G14 |

| HB10_P | IO_L24P_35 | A13 |

| HB10_N | IO_L24N_35 | A12 |

| HB11_P | IO_L19P_35 | C14 |

| HB11_N | IO_L19N_35 | C13 |

| HB12_P | IO_L21P_35 | B15 |

| HB12_N | IO_L21N_35 | A15 |

| HB13_P | IO_L2P_35 | J13 |

| HB13_N | IO_L2N_35 | H13 |

| HB14_P | IO_L7P_35 | G17 |

| HB14_N | IO_L7N_35 | G16 |

| HB15_P | IO_L22P_35 | C11 |

| HB15_N | IO_L22N_35 | B11 |

| HB16_P | IO_L3P_35 | L13 |

|---|---|---|

| HB16_N | IO_L3N_35 | K13 |

| HB17_P_CC | IO_L11P_SRCC_35 | E13 |

| HB17_N_CC | IO_L11N_SRCC_35 | D13 |

| HB18_P | IO_L9P_35 | G12 |

| HB18_N | IO_L9N_35 | F12 |

| HB19_P | IO_L10P_35 | F13 |

| HB19_N | IO_L10N_35 | E12 |

| HB20_P | IO_L5P_35 | K15 |

| HB20_N | IO_L5N_35 | J15 |

| HB21_P | IO_L23P_35 | B14 |

| HB21_N | IO_L23N_35 | A14 |

添加圖片注釋,不超過 140 字(可選)

4.17.PCIE2.0接口

開發板設計了PCIE2.0 接口,為 x4 接口,如下表列出了PCIE 接口對應關系。

| PCIE2.0 | 管腳名稱 | 管腳位置 |

|---|---|---|

| PERST_N | IO_24N_10 | AB16 |

| REF_CLK_P | MGT_109_CLK_P0 | AD10 |

| REF_CLK_N | MGT_109_CLK_N0 | AD9 |

| PER0_P | MGT_109_TX_P3 | AK2 |

| PER0_N | MGT_109_TX_N3 | AK1 |

| PER1_P | MGT_109_TX_P2 | AJ4 |

| PER1_N | MGT_109_TX_N2 | AJ3 |

| PER2_P | MGT_109_TX_P1 | AK6 |

| PER2_N | MGT_109_TX_N1 | AK5 |

| PER3_P | MGT_109_TX_P0 | AK10 |

| PER3_N | MGT_109_TX_N0 | AK9 |

| PET0_P | MGT_109_RX_P3 | AE8 |

| PET0_N | MGT_109_RX_N3 | AE7 |

| PET1_P | MGT_109_RX_P2 | AG8 |

| PET1_N | MGT_109_RX_N2 | AG7 |

| PET2_P | MGT_109_RX_P1 | AJ8 |

| PET2_N | MGT_109_RX_N1 | AJ7 |

| PET3_P | MGT_109_RX_P0 | AH10 |

| PET3_N | MGT_109_RX_N0 | AH9 |

添加圖片注釋,不超過 140 字(可選)

4.18.JTAG接口

開發板設計了一個 JTAG 接口,購買開發板后,我們會提供配套的下載器,對應 連接線序就可以下載調試板卡。

添加圖片注釋,不超過 140 字(可選)

審核編輯 黃宇

-

FPGA

+關注

關注

1662文章

22480瀏覽量

638467 -

開發板

+關注

關注

26文章

6372瀏覽量

120065 -

核心板

+關注

關注

6文章

1413瀏覽量

32097

發布評論請先 登錄

[XILINX] 正點原子ZYNQ7035/7045/7100開發板發布、ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2!

ZYNQ7000開發平臺的AX7Z035開發板用戶手冊免費下載

AX7Z035 ZYNQ開發板的用戶手冊資料免費下載

瑞芯微RK3568核心板/評估板/開發板/工控板用戶手冊

【PZ7020-StarLite 入門級開發板】——FPGA 開發的理想起點,入門與工業場景的雙重優選

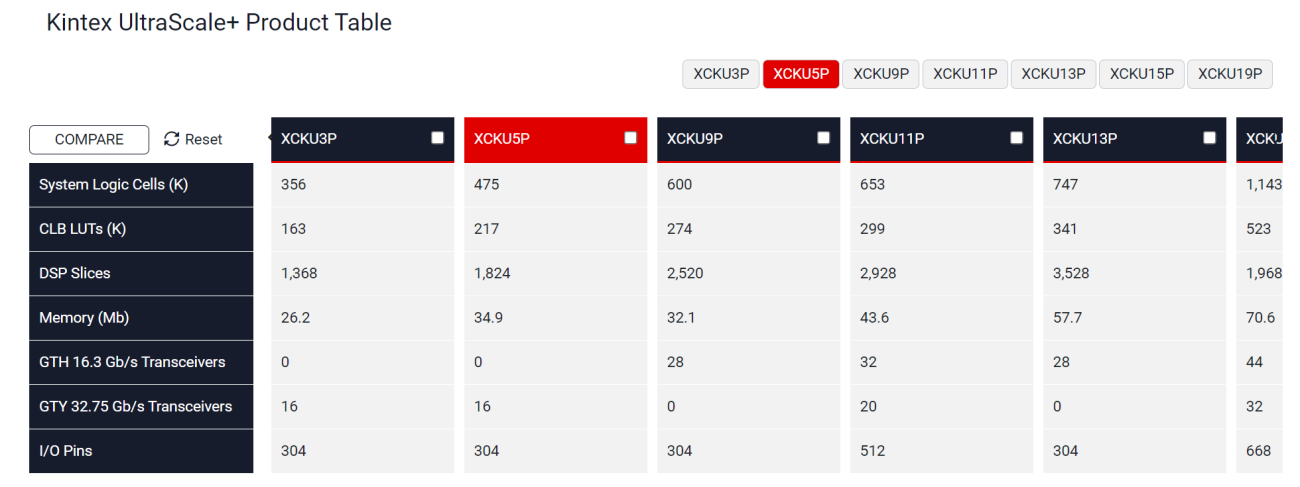

FPGA開發板—璞致 Kintex-7 系列核心板PZ-K7325T/PZ-K7410T 使用說明 XILINX核心板簡介

fpga開發板 璞致 Kintex UltraScale Plus PZ-KU3P 與 PZ-KU5P核心板與開發板用戶手冊

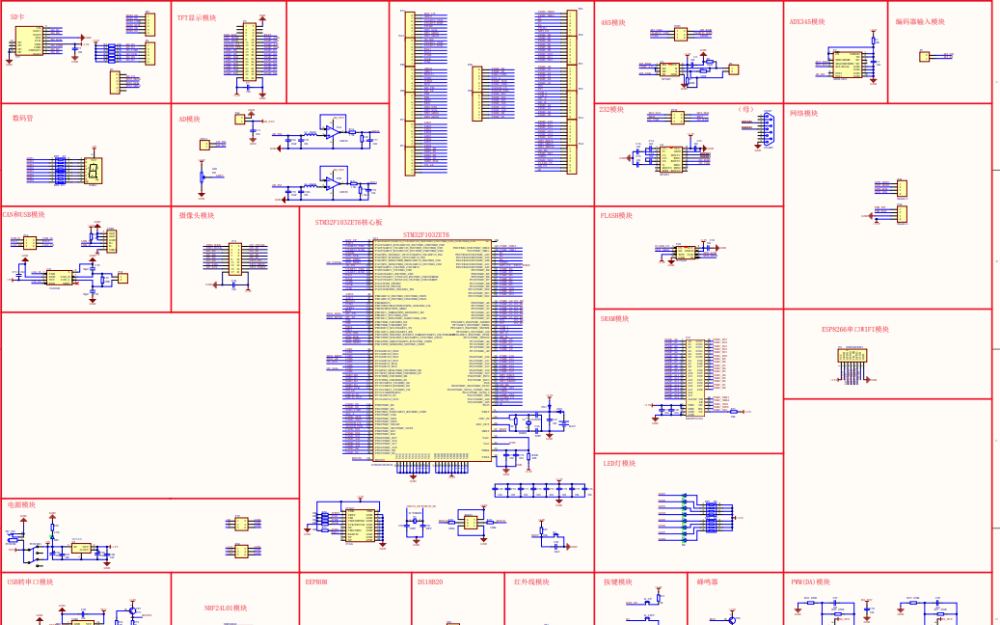

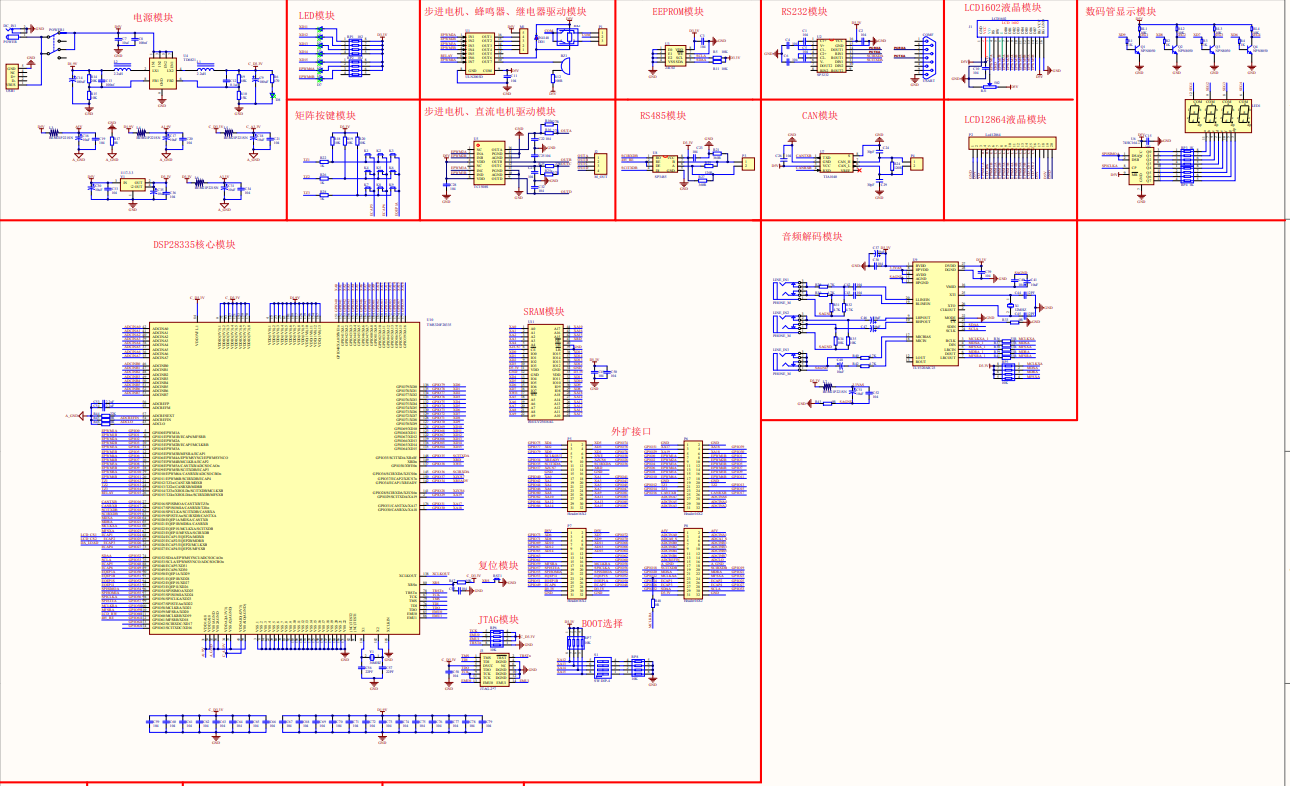

fpga開發板 璞致ZYNQ 7000 系列之 PZ7035/PZ7045/PZ7100-FH 核心板與開發板用戶手冊

fpga開發板 璞致ZYNQ 7000 系列之 PZ7035/PZ7045/PZ7100-FH 核心板與開發板用戶手冊

評論