2 axi_uart_rw案例

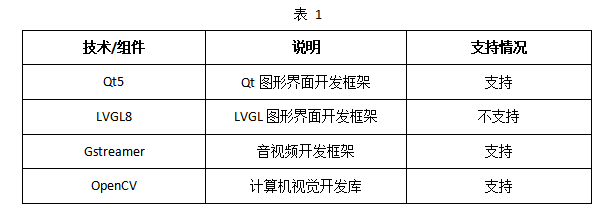

案例功能:PS端通過AXI4-Lite總線控制PL端AXI UARTLite IP核進行數據收發(fā),以此來演示評估板上RS485、RS422和RS232的串口收發(fā)功能。

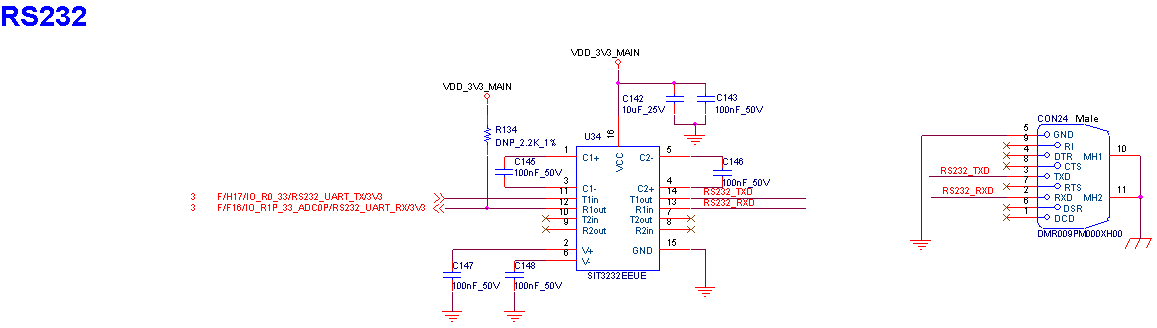

圖 15

圖 15

圖 16

圖 16

圖 17

圖 17

工程管腳約束可查看工程文件"constrains"目錄下的.adc約束文件。

2.1 TD工程說明

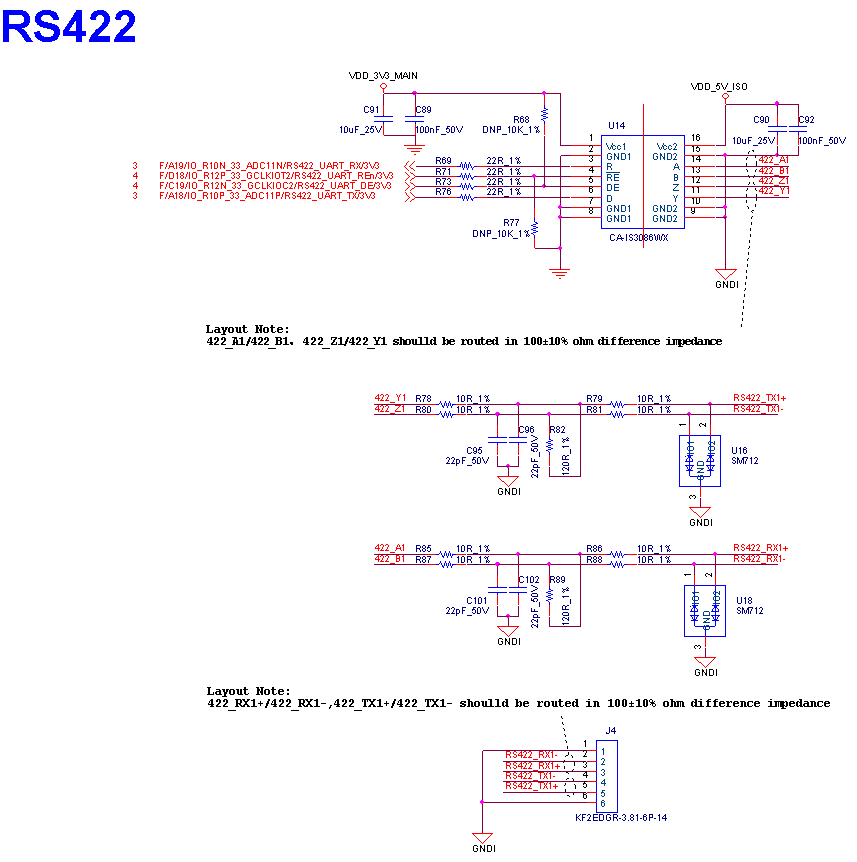

工程在PL端上使用AXI UARTLite IP核,ARM Processor System IP核(PS端)通過AXI4-Lite總線控制PL端AXI UARTLite IP核進行數據收發(fā),Design Integrator工程和地址分配如下:

圖 18

圖 18

圖 19

圖 19

2.2 IP核簡介

IP核開發(fā)相關資料可查閱產品資料“6-開發(fā)參考資料Anlogic官方參考文檔”目錄下文檔,IP核配置參數如下。

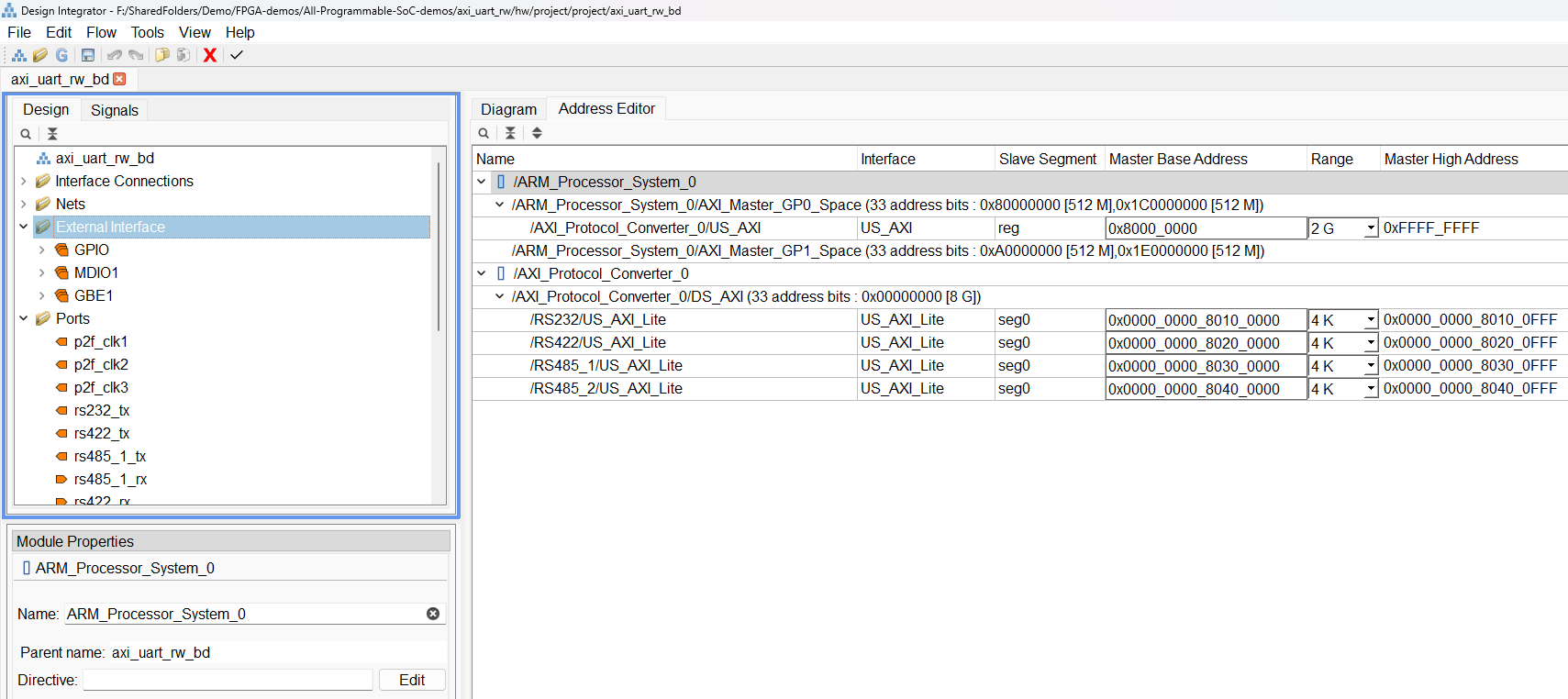

(1)ARM Processor System。

ARM Processor System IP核心配置和FSBL工程基本一致,僅修改GPIO PL(Width)的值為4,并從頂層引出,綁定管腳D15、B19、C19、D18,用于流控兩個RS485及一個RS422。其他詳細配置可參考位于產品資料“4-軟件資料LinuxFSBLfsbl-[版本號]”目錄下的FSBL工程。

圖 20

圖 20

(2)AXI UARTLite。

本案例工程使用了4個AXI UARTLite IP核,4個AXI UARTLite IP核的配置均相同。

圖 21

圖 21

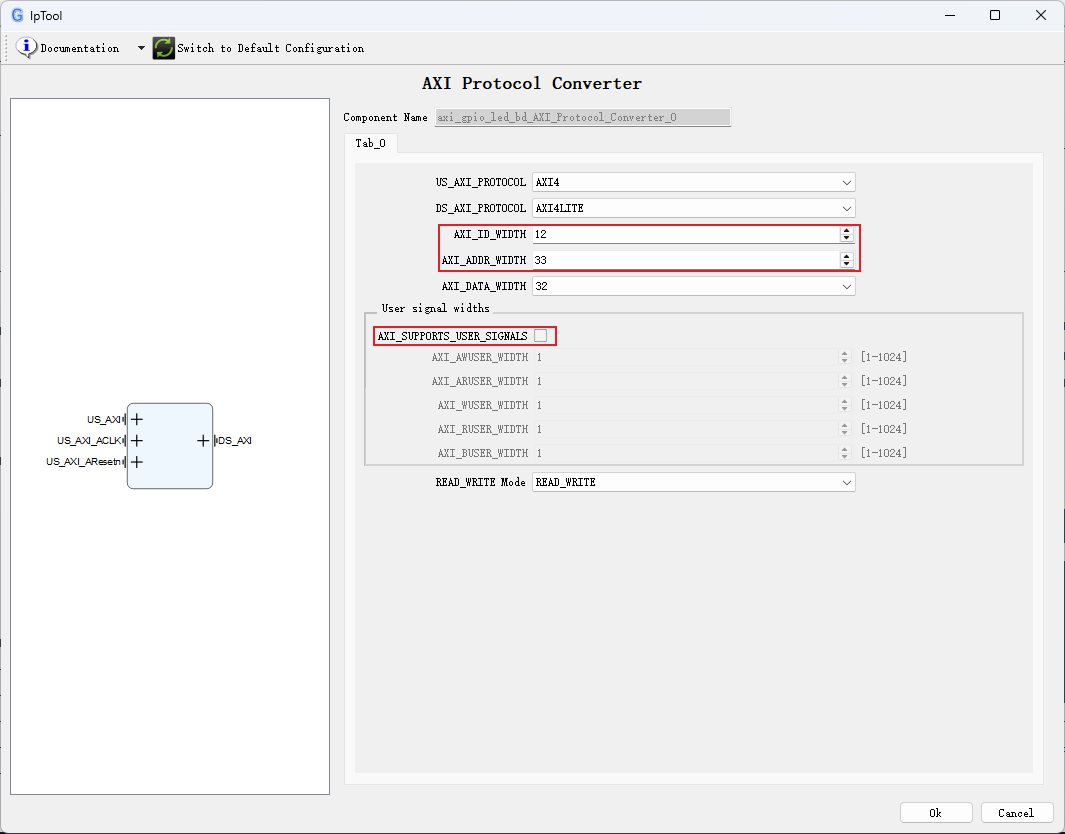

(3)AXIProtocol Converter。

圖 22

圖 22

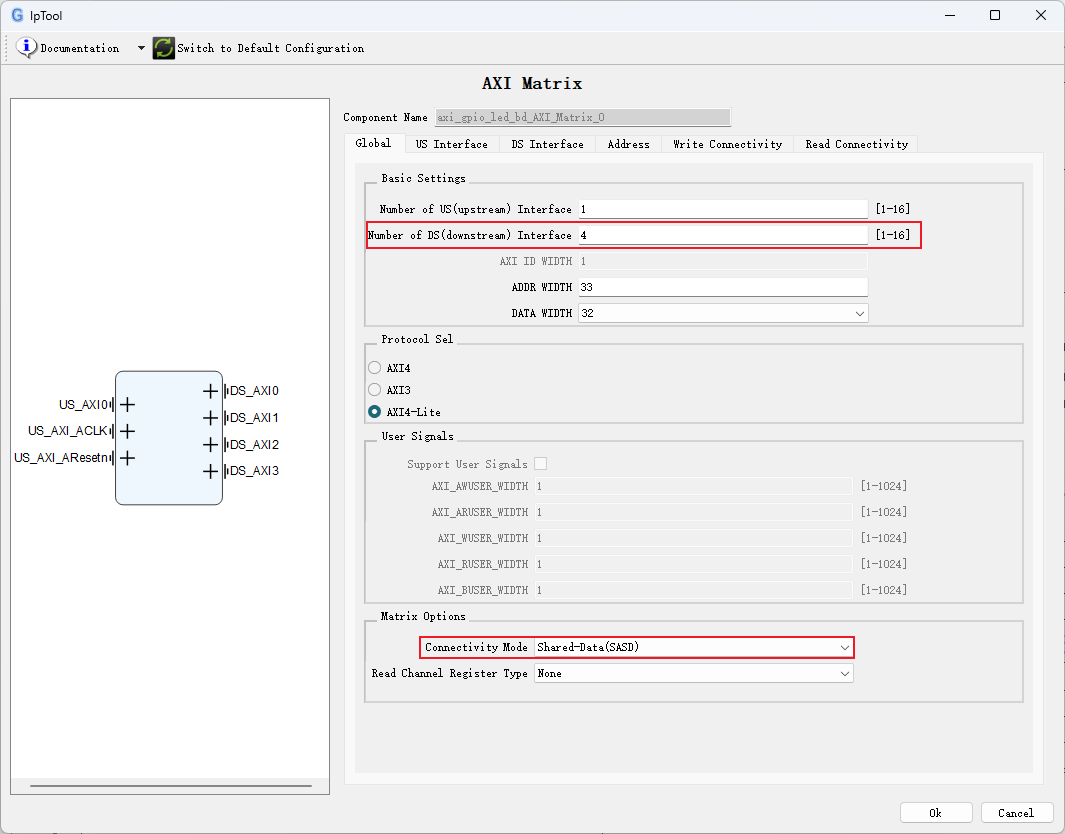

(4)AXI Matrix。

圖 23

圖 23

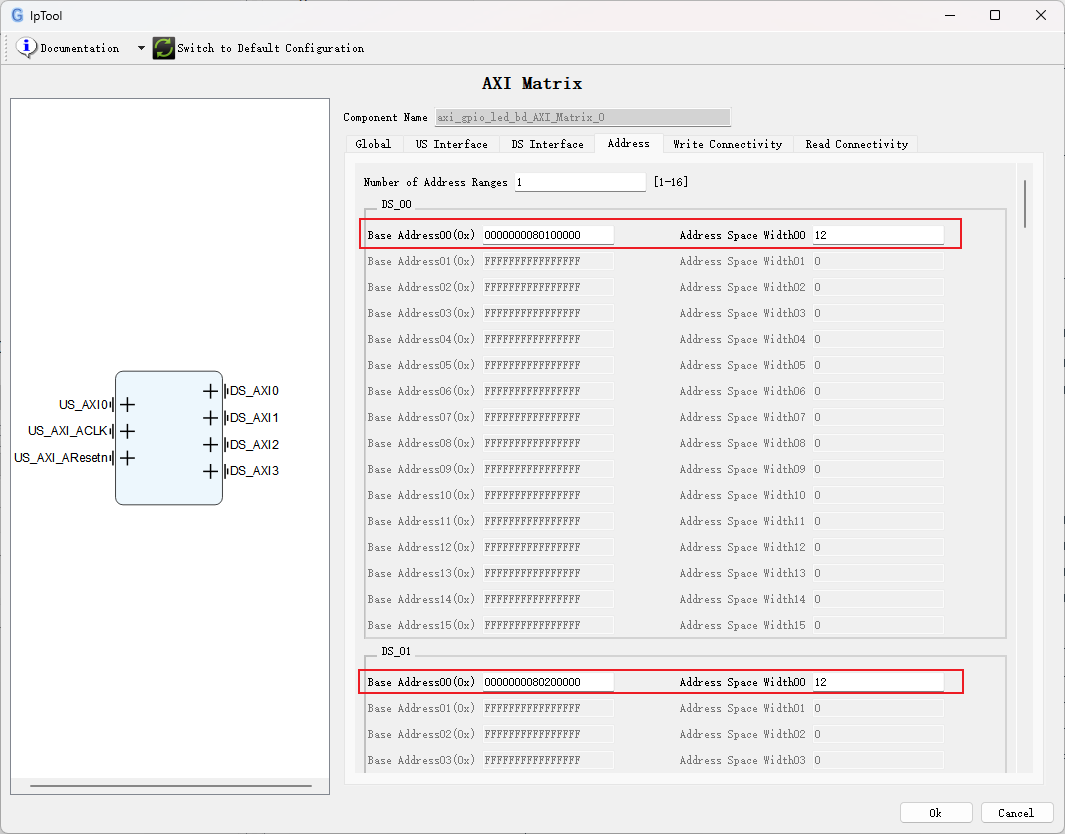

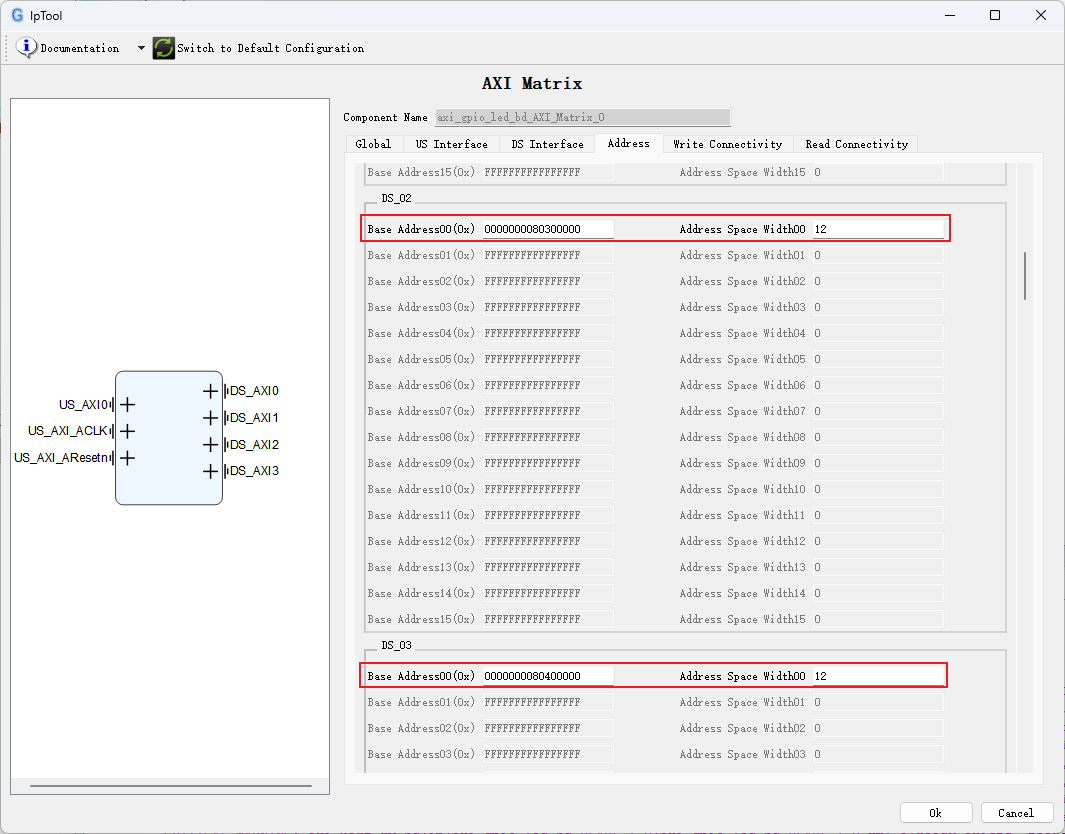

圖 24

圖 24

圖 25

圖 25

2.3 案例測試

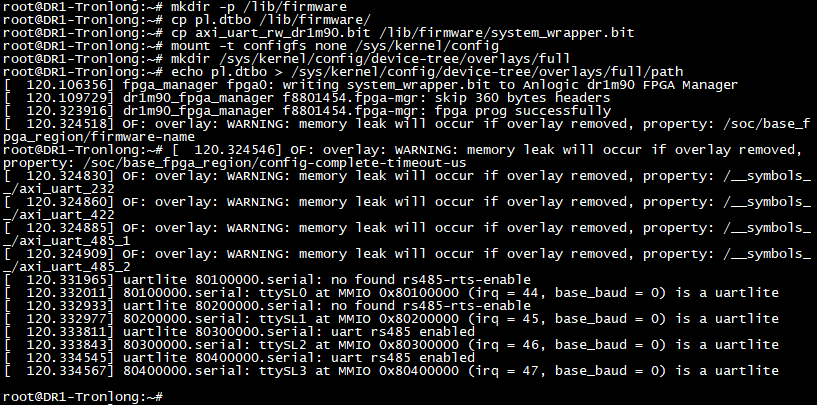

將本案例的動態(tài)設備樹鏡像文件pl.dtbo和PL端.bit鏡像文件拷貝至"/lib/firmware/"目錄下(若該目錄不存在,請新建),并將PL端可執(zhí)行文件重命名為system_wrapper.bit,然后執(zhí)行如下命令加載PL端鏡像。

Target# mkdir -p /lib/firmware

Target# cp pl.dtbo /lib/firmware/

Target# cp axi_uart_rw_dr1m90.bit /lib/firmware/system_wrapper.bit

Target# mount -t configfs none /sys/kernel/config

Target# mkdir /sys/kernel/config/device-tree/overlays/full //創(chuàng)建full目錄,可根據實際情況修改

Target# echo pl.dtbo > /sys/kernel/config/device-tree/overlays/full/path //dtbo文件名稱請根據實際情況修改

圖 26

圖 26

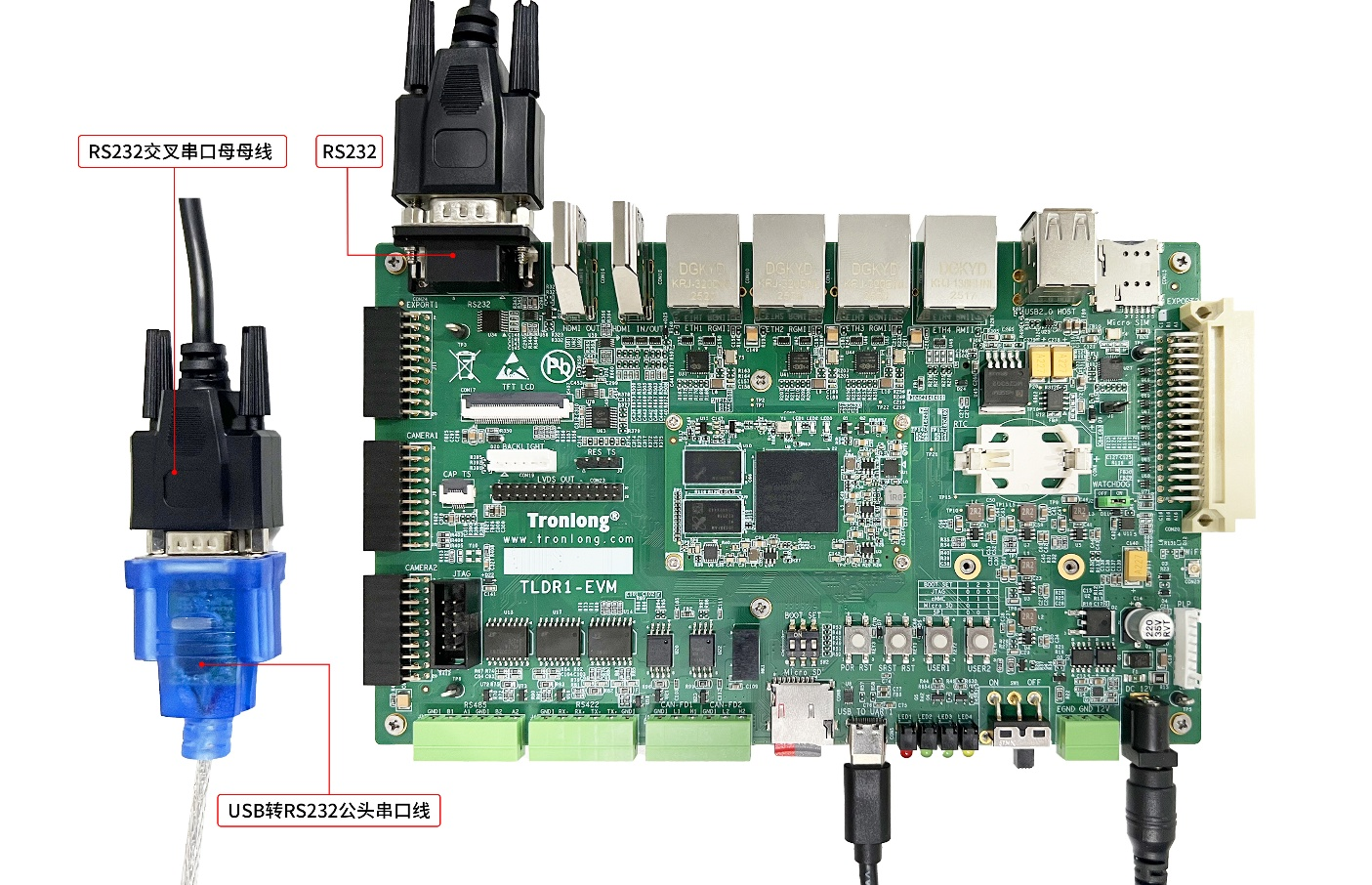

(1)RS232測試

請通過RS232交叉串口母線、USB轉RS232公頭串口線,將評估板的RS232調試串口連接至PC機的USB接口,如下圖所示。

圖 27

圖 27

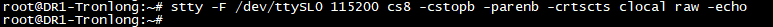

執(zhí)行如下命令,調整RS232串口通信參數。

Target# stty -F /dev/ttySL0 115200 cs8 -cstopb -parenb -crtscts clocal raw -echo

圖 28

圖 28

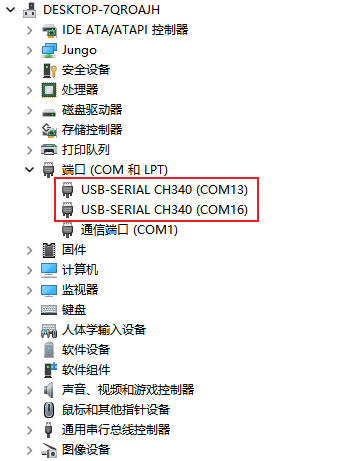

a)評估板接收

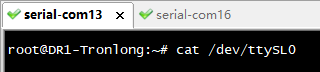

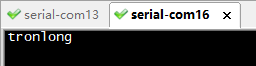

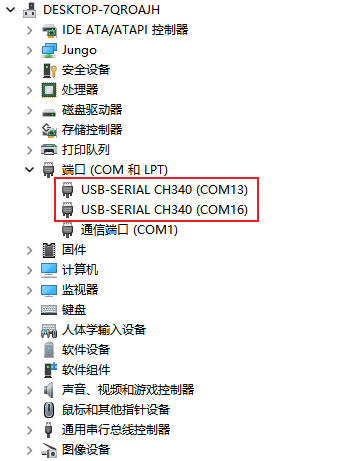

打開設備管理器,本次測試中調試串口USB TO UART1端口號為COM13,RS232串口的端口號為COM16,如下圖所示。

圖 29

圖 29

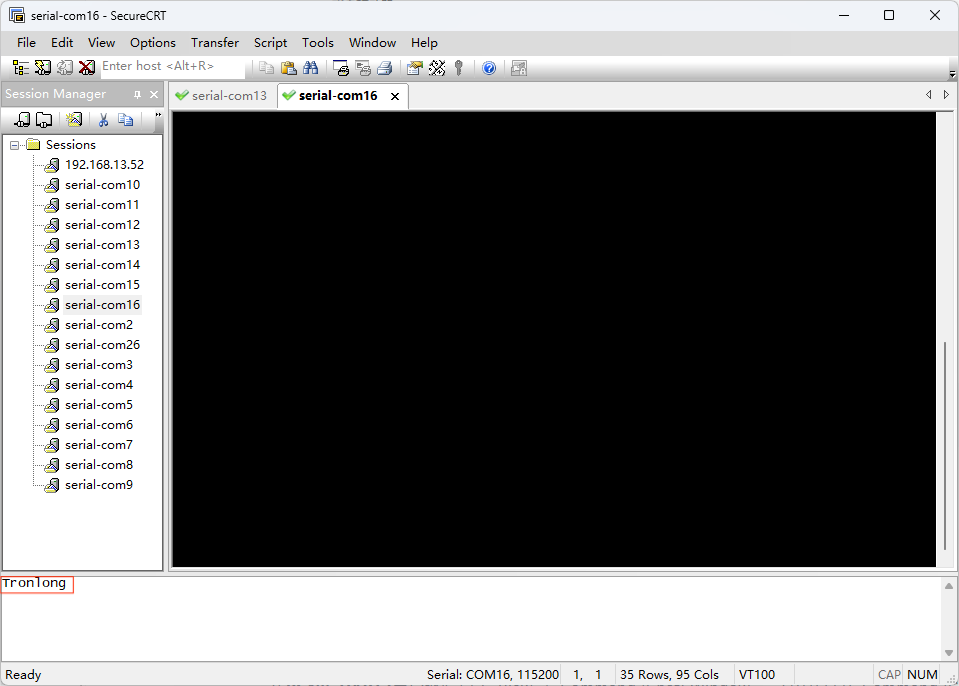

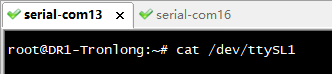

打開調試串口終端,COM16波特率設為115200,8N1,無校驗位。COM13波特率設為115200,8N1,無校驗位,并建立串口連接。評估板調試串口終端執(zhí)行如下命令,評估板等待接收上位機發(fā)送的數據。

Target# cat /dev/ttySL0

圖 30

圖 30

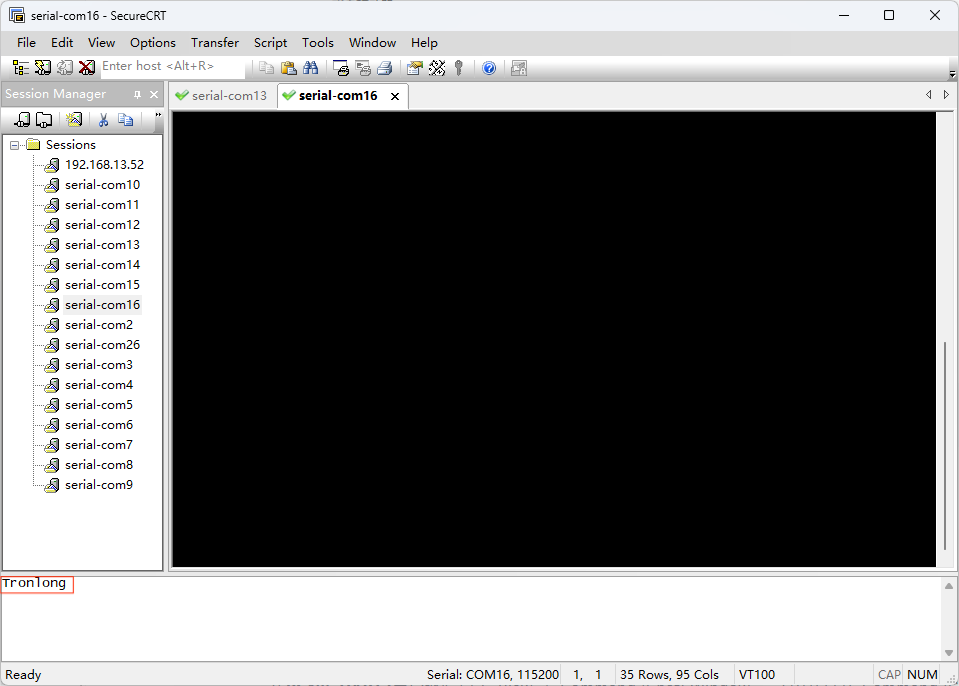

在RS232串口終端點擊"View -> Command (Chat) Window",選中并打開"Command (Chat) Window"窗口。

圖 31

圖 31

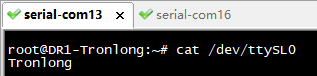

在窗口中輸入數據,例如"Tronlong",再按回車鍵。

圖 32

圖 32

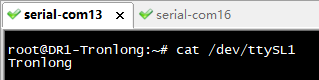

評估板調試串口終端將會打印接收到的數據。

圖 33

圖 33

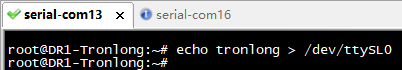

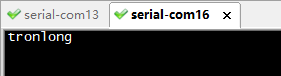

b)評估板發(fā)送

執(zhí)行如下命令,評估板通過RS232串口發(fā)送數據至上位機。

Target# echo tronlong > /dev/ttySL0

圖 34

圖 34

RS232串口終端將會打印接收到的數據,如下圖所示。

圖 35

圖 35

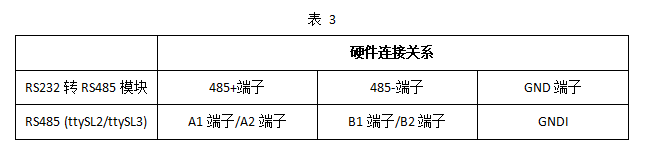

(2)RS485串口測試

使用RS232轉RS485模塊、USB轉RS232公頭串口線,將評估板RS485串口連接至PC機的USB接口,硬件連接如下圖所示。

RS232轉RS485模塊與評估板RS485串口硬件連接關系如下表所示。

圖 36

圖 36

本章節(jié)以RS485串口(設備節(jié)點為:ttySL2)為例進行演示。如需測試RS485另一個串口,請將設備節(jié)點修改為ttySL3。

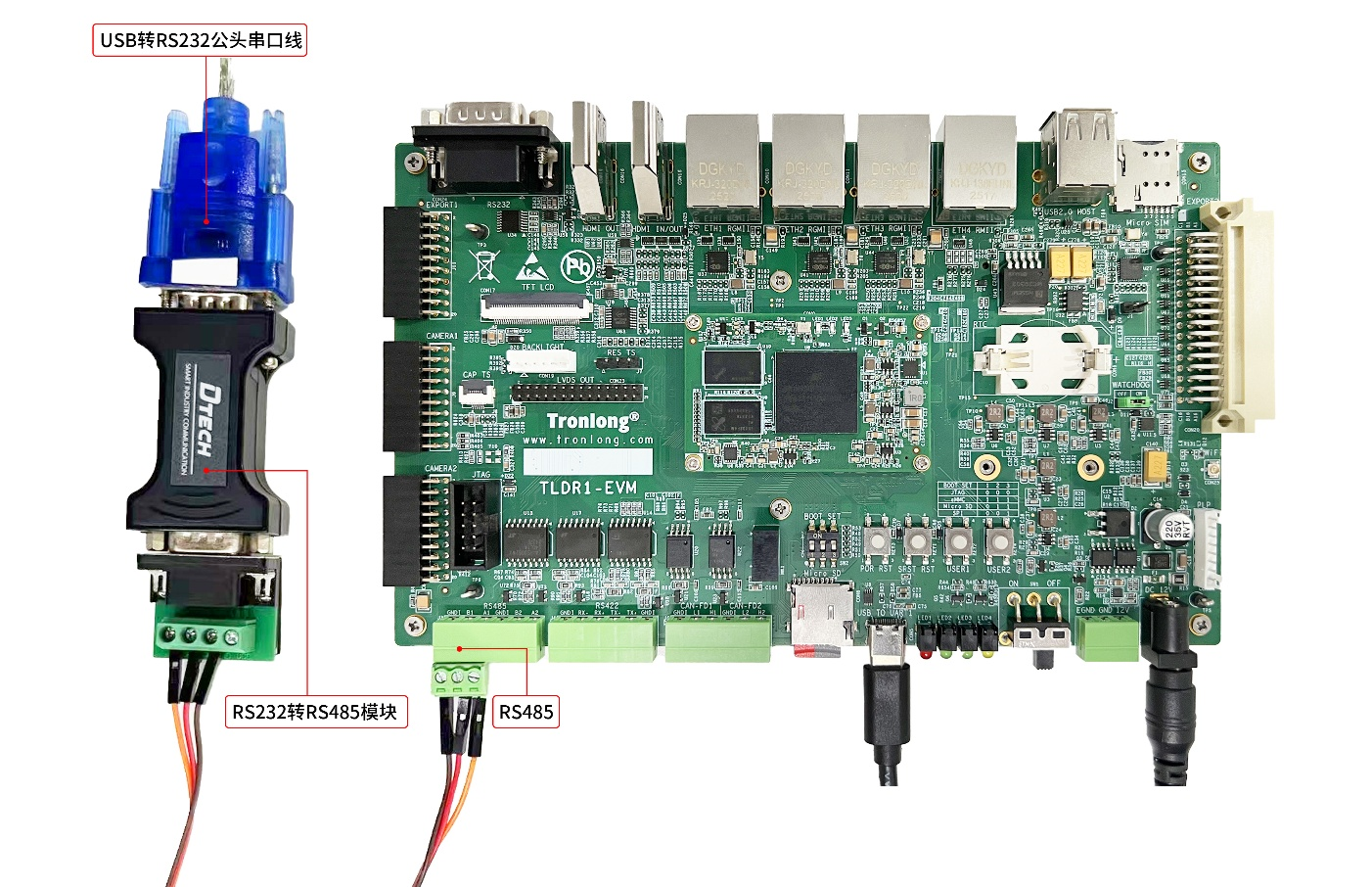

執(zhí)行如下命令,調整RS485串口通信參數。

Target# stty -F /dev/ttySL2 115200 cs8 -cstopb -parenb -crtscts clocal raw -echo

圖 37

圖 37

a)評估板接收

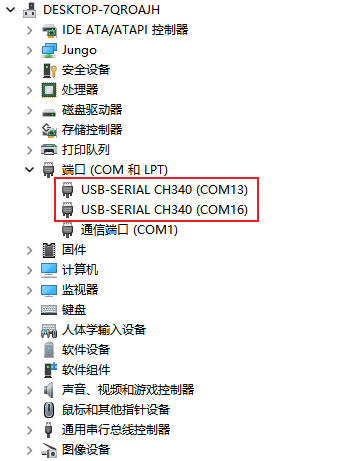

打開設備管理器,本次測試中調試串口USB TO UART1端口號為COM13,RS485串口的端口號為COM16,如下圖所示。

圖 38

圖 38

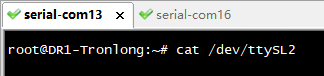

評估板調試串口終端執(zhí)行如下命令,評估板等待接收上位機發(fā)送的數據。

Target# cat /dev/ttySL2

圖 39

圖 39

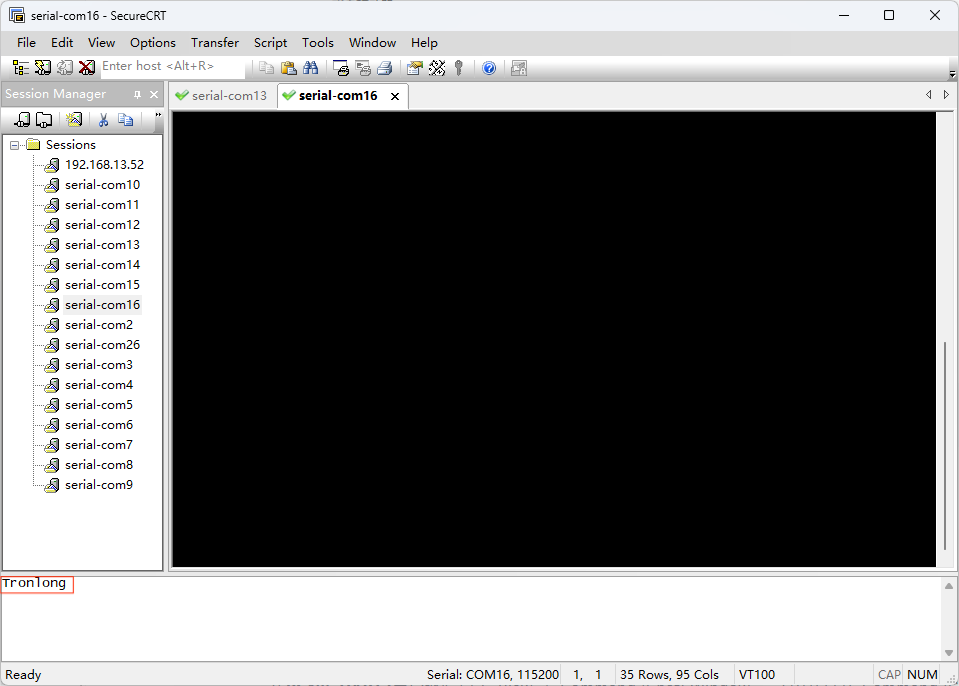

在RS485串口終端點擊"View -> Command (Chat) Window",選中并打開"Command (Chat) Window"窗口。

圖 40

圖 40

在窗口中輸入數據,例如"Tronlong",再按回車鍵。

圖 41

圖 41

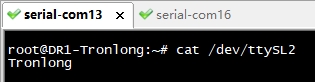

評估板調試串口終端將會打印接收到的數據。

圖?42

圖?42

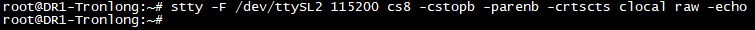

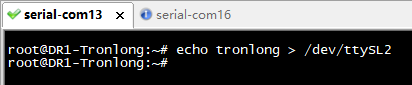

b)評估板發(fā)送

執(zhí)行如下命令,評估板通過RS485串口發(fā)送數據至上位機。

Target# echo tronlong > /dev/ttySL2

圖 43

圖 43

RS485 UART3串口終端將會打印接收到的數據,如下圖所示。

圖 44

圖 44

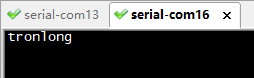

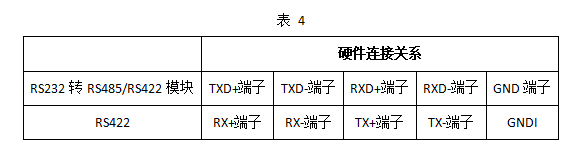

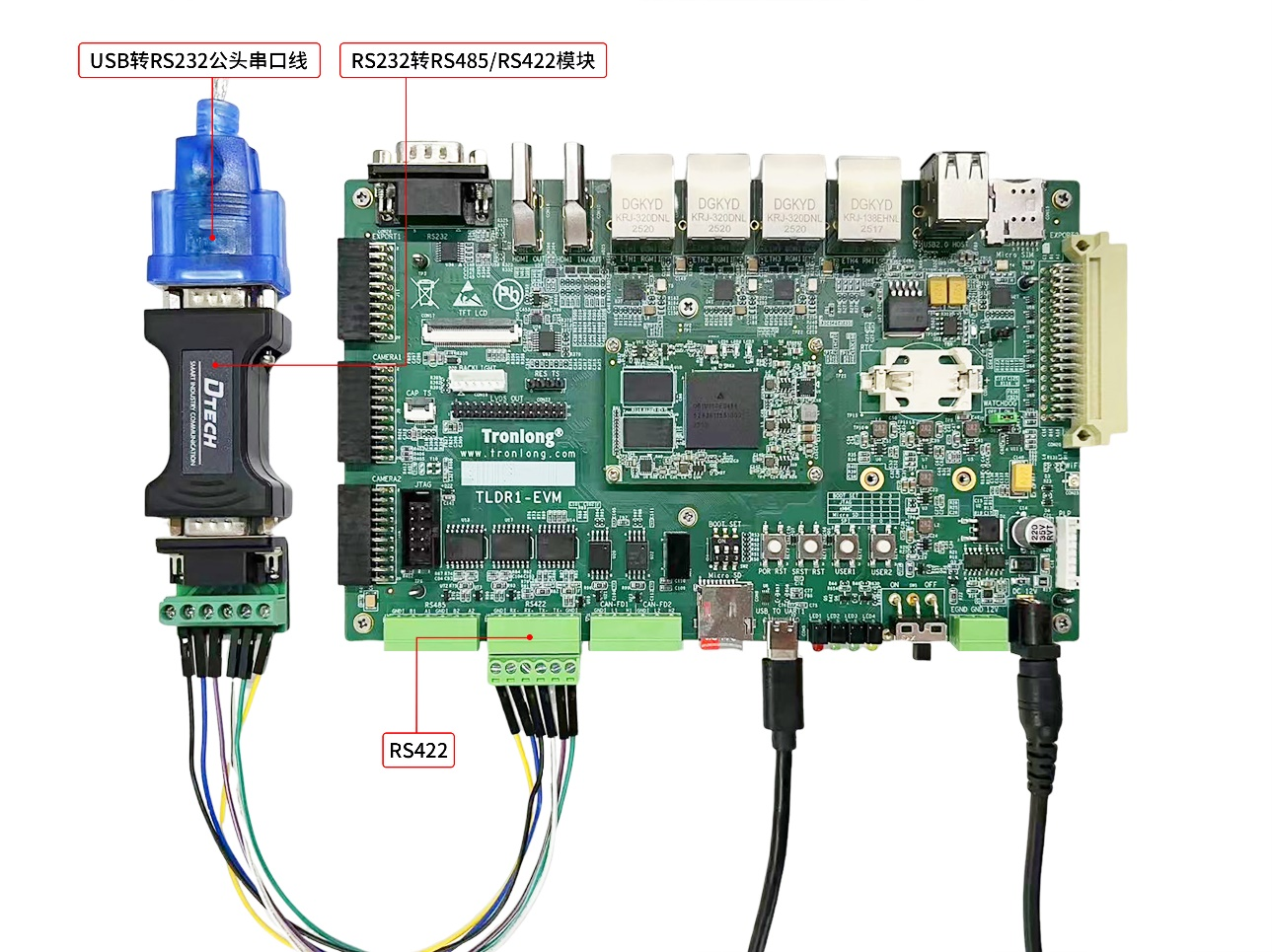

(3)RS422串口測試

使用RS232轉RS485/RS422模塊、USB轉RS232公頭串口線,將評估板RS422串口連接至PC機的USB接口,硬件連接如下圖所示。

RS232轉RS485/RS422模塊與評估板RS422串口硬件連接關系如下表所示。

圖 45

圖 45

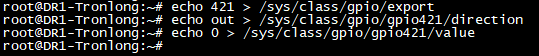

本章節(jié)以RS422串口(設備節(jié)點為:ttySL1)為例進行演示。執(zhí)行如下命令,配置RS422端口的RE_n管腳為低電平。

Target# echo 421 > /sys/class/gpio/export

Target# echo out > /sys/class/gpio/gpio421/direction

Target# echo 0 > /sys/class/gpio/gpio421/value

圖 46

圖 46

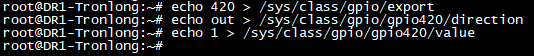

執(zhí)行如下命令,配置RS422端口的DE管腳為高電平。

Target# echo 420 > /sys/class/gpio/export

Target# echo out > /sys/class/gpio/gpio420/direction

Target# echo 1 > /sys/class/gpio/gpio420/value

圖 47

圖 47

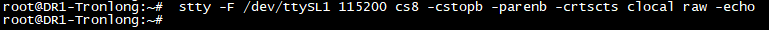

執(zhí)行如下命令,調整RS422串口通信參數。

Target# stty -F /dev/ttySL1 115200 cs8 -cstopb -parenb -crtscts clocal raw -echo

圖 48

圖 48

a)評估板接收

打開設備管理器,本次測試中調試串口USB TO UART1端口號為COM13,RS422串口的端口號為COM16,如下圖所示。

圖 49

圖 49

評估板調試串口終端執(zhí)行如下命令,評估板等待接收上位機發(fā)送的數據。

Target# cat /dev/ttySL1

圖 50

圖 50

在RS422串口終端點擊"View -> Command (Chat) Window",選中并打開"Command (Chat) Window"窗口。

圖 51

圖 51

在窗口中輸入數據,例如"Tronlong",再按回車鍵。

圖 52

圖 52

評估板調試串口終端將會打印接收到的數據。

圖?53

圖?53

b)評估板發(fā)送

執(zhí)行如下命令,評估板通過RS422串口發(fā)送數據至上位機。

Target# echo tronlong > /dev/ttySL1

圖 54

圖 54

RS422串口終端將會打印接收到的數據,如下圖所示。

圖 55

圖 55

由于篇幅過長等原因,部分內容均不逐一展示,如需獲取完整版詳細資料,請關注創(chuàng)龍科技微信公眾號或官網,或者評論區(qū)留言,感謝您的支持!

審核編輯 黃宇

-

核心板

+關注

關注

6文章

1409瀏覽量

32085

發(fā)布評論請先 登錄

ZYNQ PS + PL異構多核案例開發(fā)手冊之1axi_gpio_led_demo案例

DR1平臺Linux應用開發(fā)指南:含GDB調試、Python及MQTT實戰(zhàn)

FM20S用戶手冊-PS + PL異構多核案例開發(fā)手冊

復旦微PS+PL異構多核開發(fā)案例分享,基于FMQL20SM國產處理器平臺

米爾瑞芯微多核異構低功耗RK3506核心板重磅發(fā)布

ZYNQ PS + PL異構多核案例開發(fā)手冊之axi_timer_pwm_demo案例

Zynq-7000系列打得火熱,異構多核技術需求怎么解決

【資料分享】Zynq-7010/7020工業(yè)核心板規(guī)格書(雙核ARM Cortex-A9 + FPGA,主頻766MHz)

【資料分享】Xilinx Zynq-7010/7020工業(yè)核心板規(guī)格書(雙核ARM Cortex-A9 + FPGA,主頻766MHz)

創(chuàng)龍科技Zynq-7010/7020異構多核SoC工業(yè)級核心板-性能及參數資料

基于Xilinx Zynq-7010/20系列——PS+PL異構多核案例開發(fā)手冊

基于全志T113-i多核異構處理器的全國產嵌入式核心板簡介

DR1 評估板 PL 端 FPGA 開發(fā)完全指南:基礎案例與 ADC 采集模塊詳解(一)

DR1 系列評估板 PS 端裸機與 FreeRTOS 開發(fā)案例手冊

DR1 系列核心板 PS+PL 異構多核實戰(zhàn)案例手冊(二)

DR1 系列核心板 PS+PL 異構多核實戰(zhàn)案例手冊(二)

評論