前 言

本文為PS + PL端異構(gòu)多核案例開發(fā)的指引文檔,主要對(duì)PS + PL端開發(fā)案例進(jìn)行簡(jiǎn)要介紹。

開發(fā)環(huán)境

Windows開發(fā)環(huán)境:Windows10 64bit

開發(fā)工具:TD_5.9.1_DR1_2025.1_NL、FD_2025.1_SP1

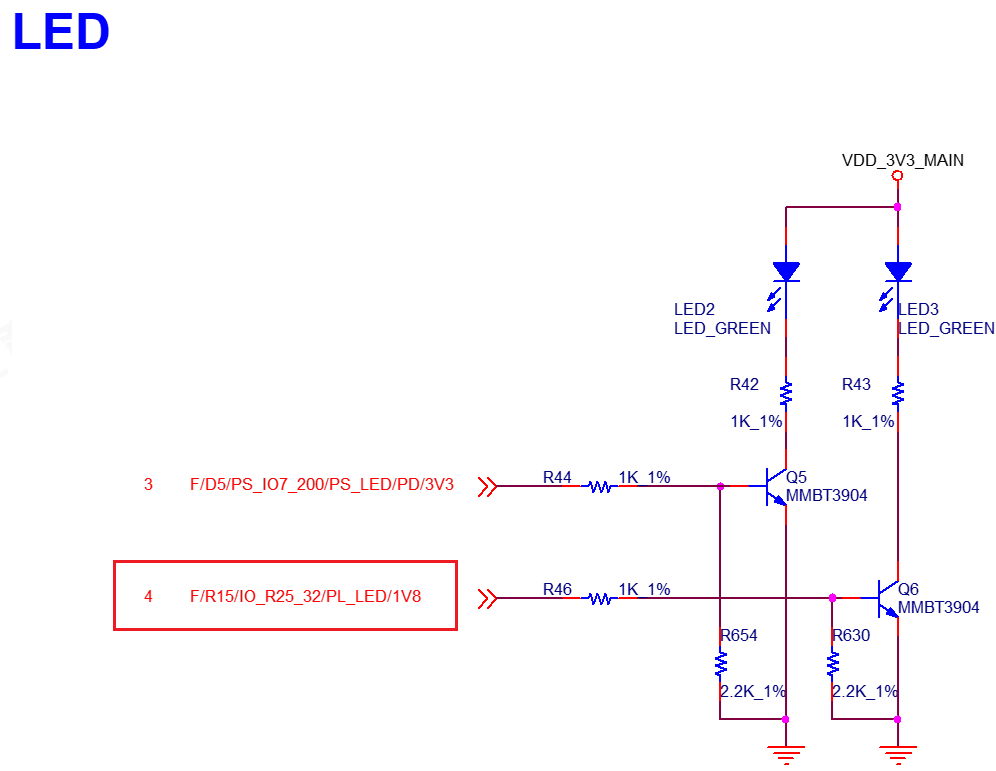

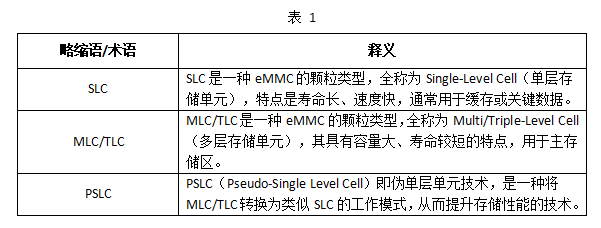

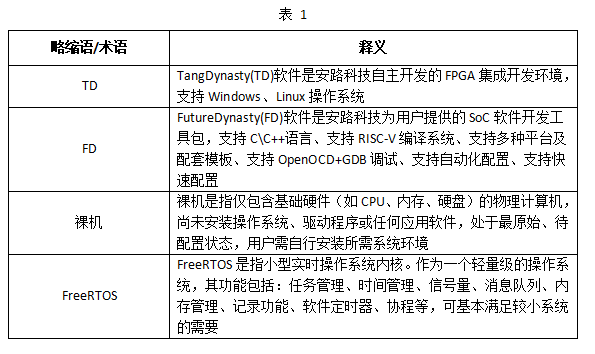

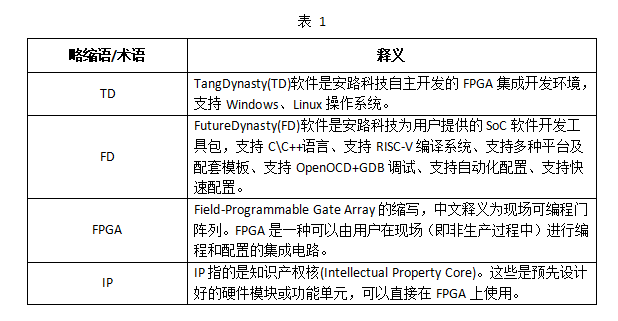

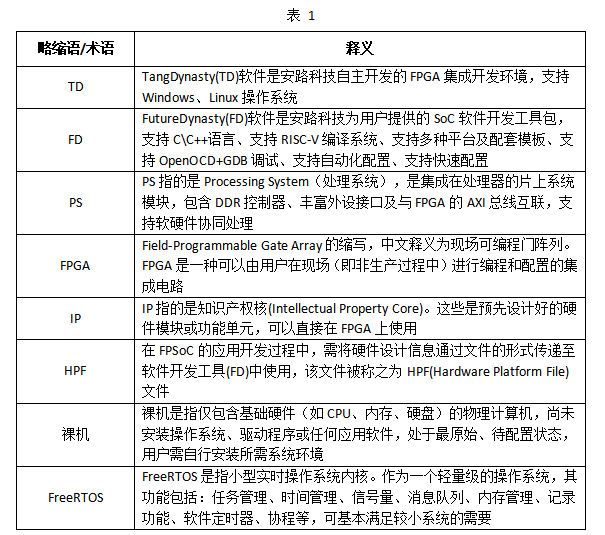

術(shù)語(yǔ)表

為便于閱讀,下表對(duì)文檔出現(xiàn)的關(guān)鍵術(shù)語(yǔ)進(jìn)行解釋;對(duì)于廣泛認(rèn)同釋義的術(shù)語(yǔ),在此不做注釋。

注意事項(xiàng)

(1)請(qǐng)先按照《開發(fā)環(huán)境搭建》文檔安裝TD、FD等軟件以及進(jìn)行JTAG驅(qū)動(dòng)安裝,使用下載器(廠家:安路科技,型號(hào):AL-LINK-FT-V1.0)連接評(píng)估板JTAG接口至PC端USB接口。

(2)在進(jìn)行本文操作前,請(qǐng)先參考《TD-FD工程編譯與加載》,熟悉工程編譯、鏡像加載等方法。

(3)案例于產(chǎn)品資料“4-軟件資料

DemoFPGA-demosAll-Programmable-SoC-demos”目錄下。案例目錄詳細(xì)說(shuō)明見下表:

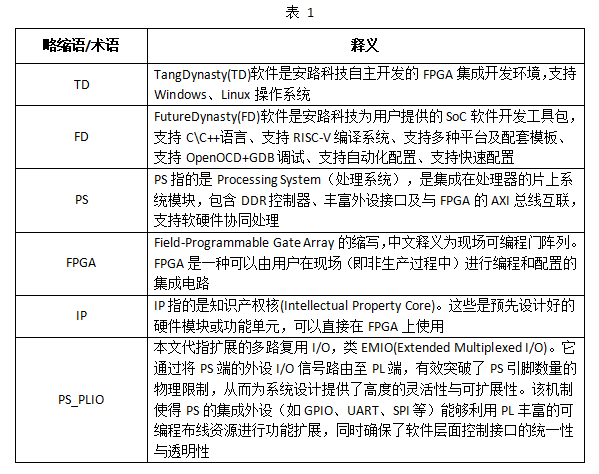

(4)查看案例的Design工程以及約束文件的方法如下,以axi_gpio_led案例進(jìn)行演示:

可在TD工程中雙擊"axi_gpio_led_bd"打開Design Integrator界面。

圖 1

圖 1

圖 2

圖 2

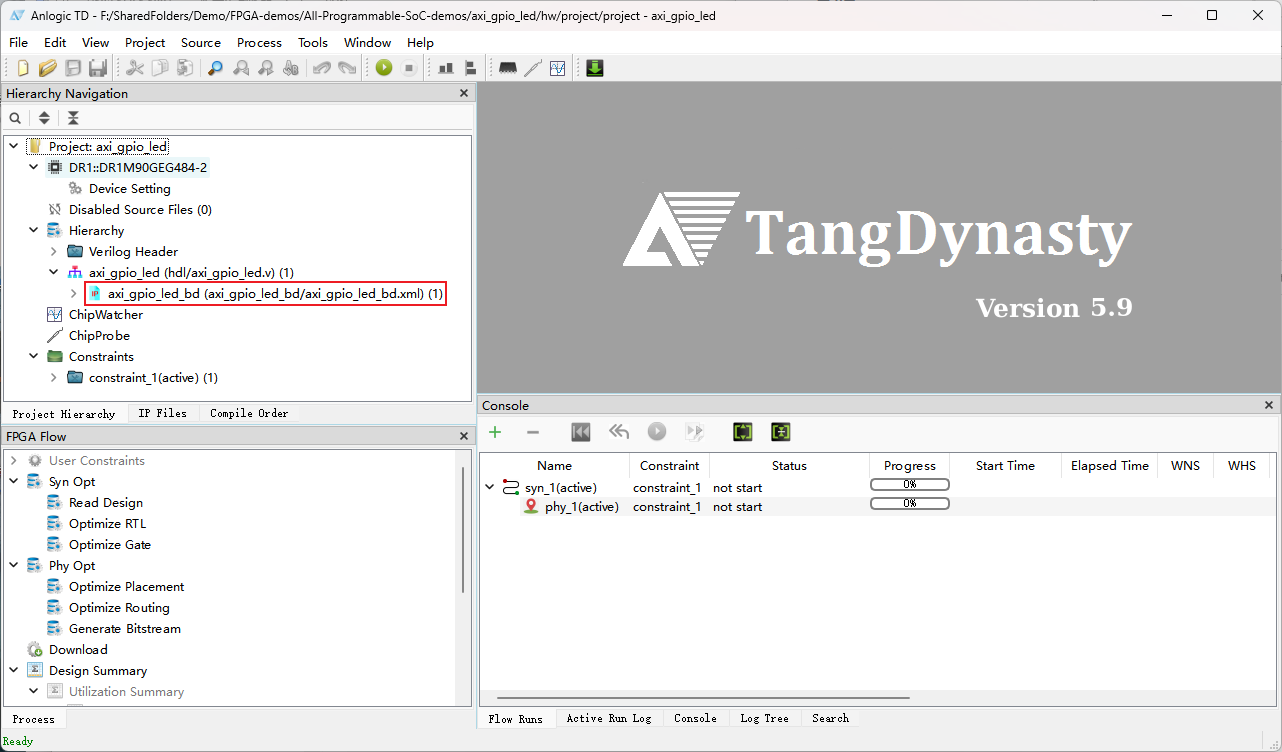

雙擊"axi_gpio_led_demo.adc"打開.adc約束文件。

圖 3

圖 3

1axi_gpio_led案例

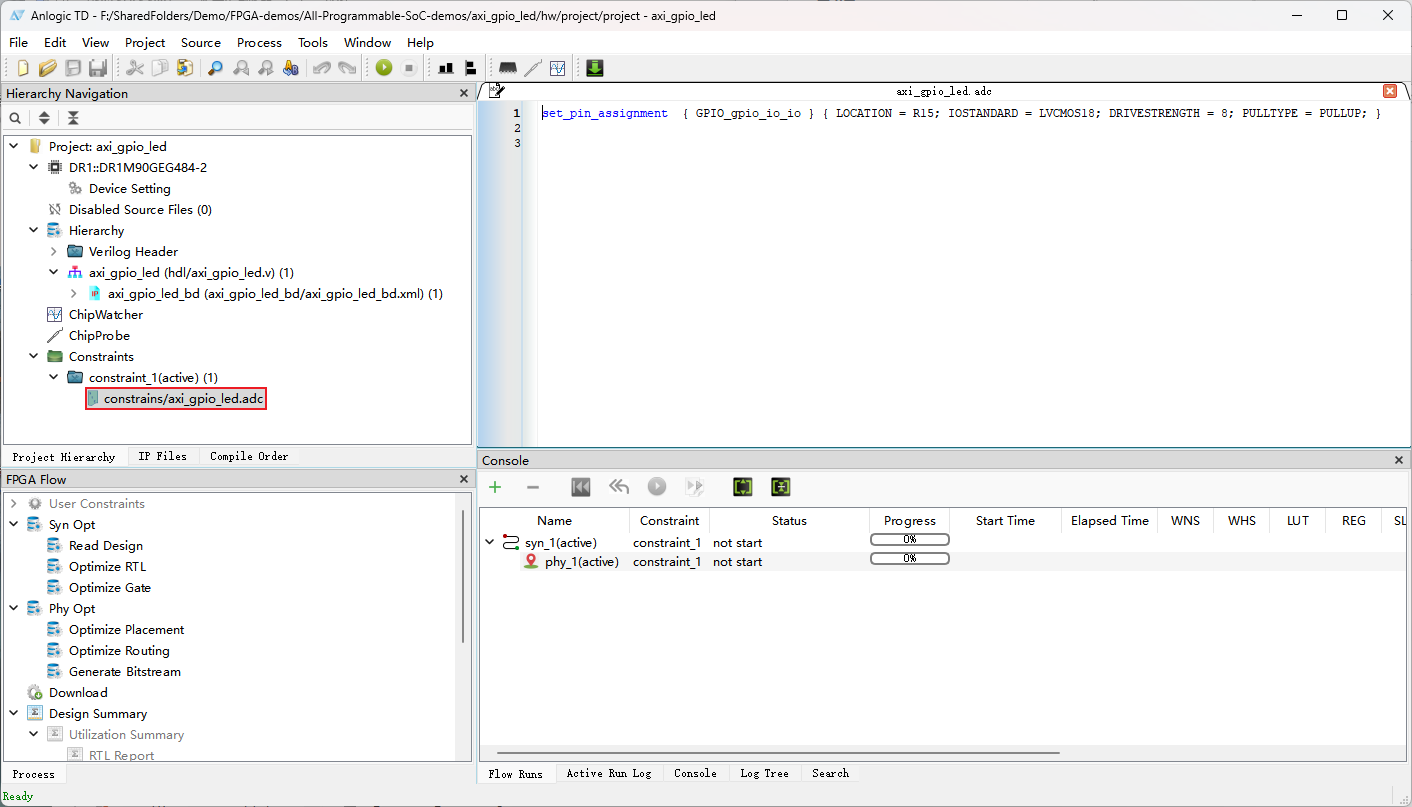

案例功能:PS端通過(guò)AXI4-Lite總線發(fā)送命令至PL端AXI GPIO IP核,IP核再根據(jù)命令控制評(píng)估底板PL端LED3的狀態(tài)。

圖 4

圖 4

工程管腳約束可查看工程文件"constrains"目錄下的.adc約束文件。

1.1 TD工程說(shuō)明

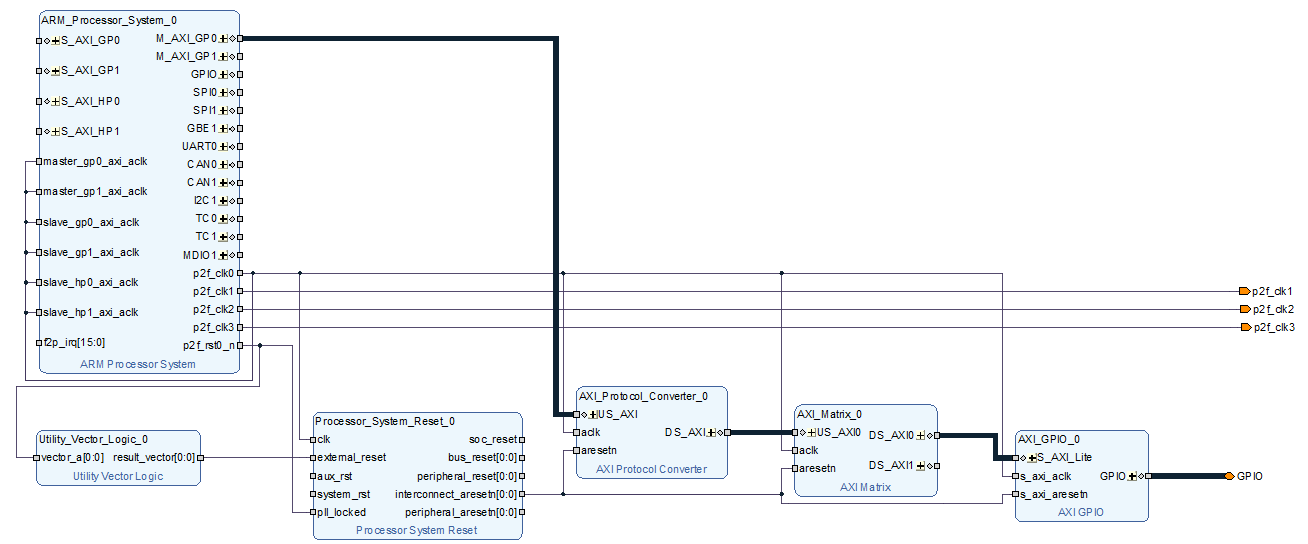

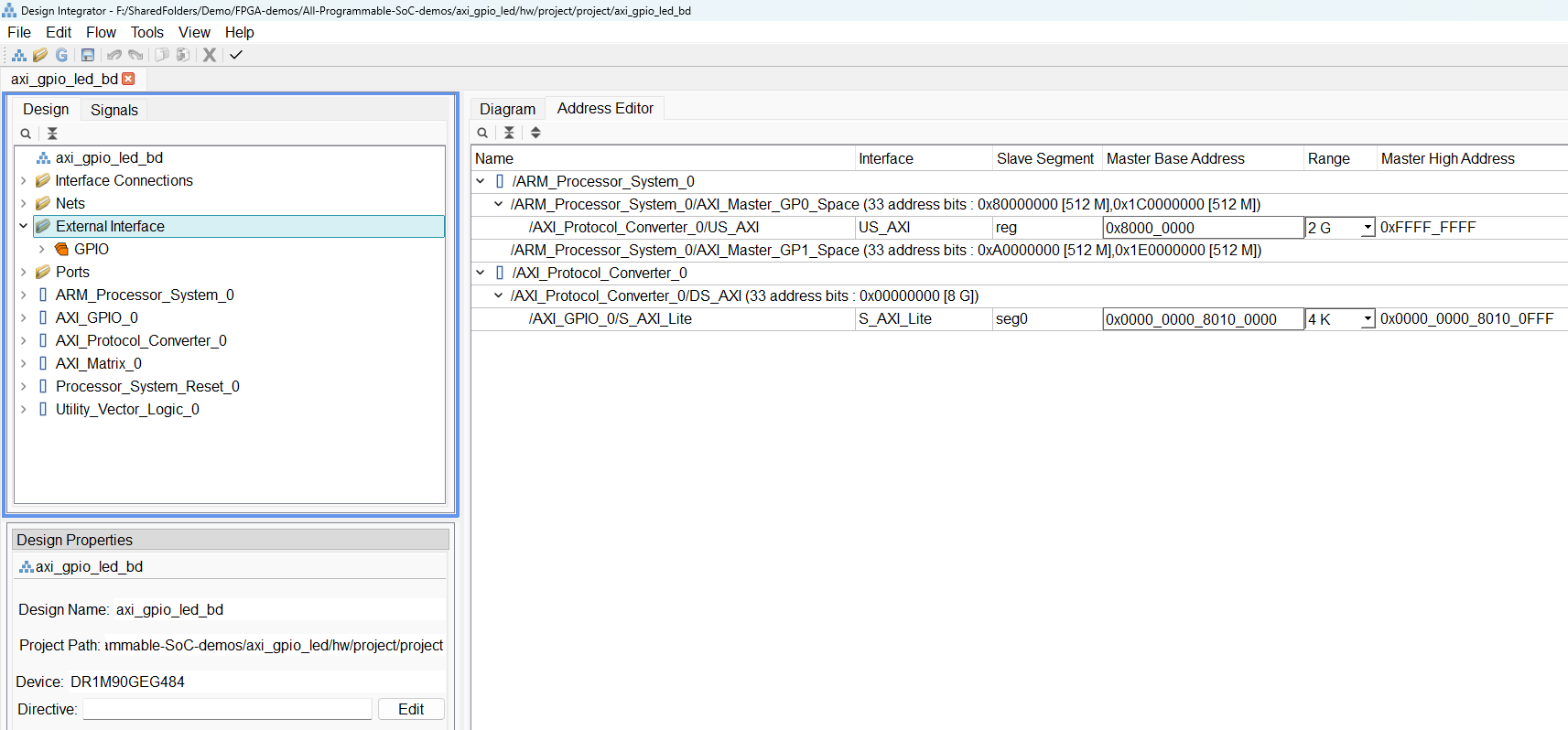

工程在PL端上使用AXI GPIO IP核,ARM Processor System IP核(PS端)通過(guò)AXI4-Lite總線可以控制底板的LED亮滅,Design Integrator工程和地址分配如下:

圖 5

圖 5

圖 6

圖 6

1.2 IP核簡(jiǎn)介

IP核開發(fā)相關(guān)資料可查閱產(chǎn)品資料“6-開發(fā)參考資料Anlogic官方參考文檔”目錄下文檔,IP核配置參數(shù)如下。

(1)ARM Processor System

ARM Processor System IP核心配置和FSBL工程一致,詳細(xì)配置可參考位于產(chǎn)品資料“4-軟件資料LinuxFSBLfsbl-[版本號(hào)]”目錄下的FSBL工程。

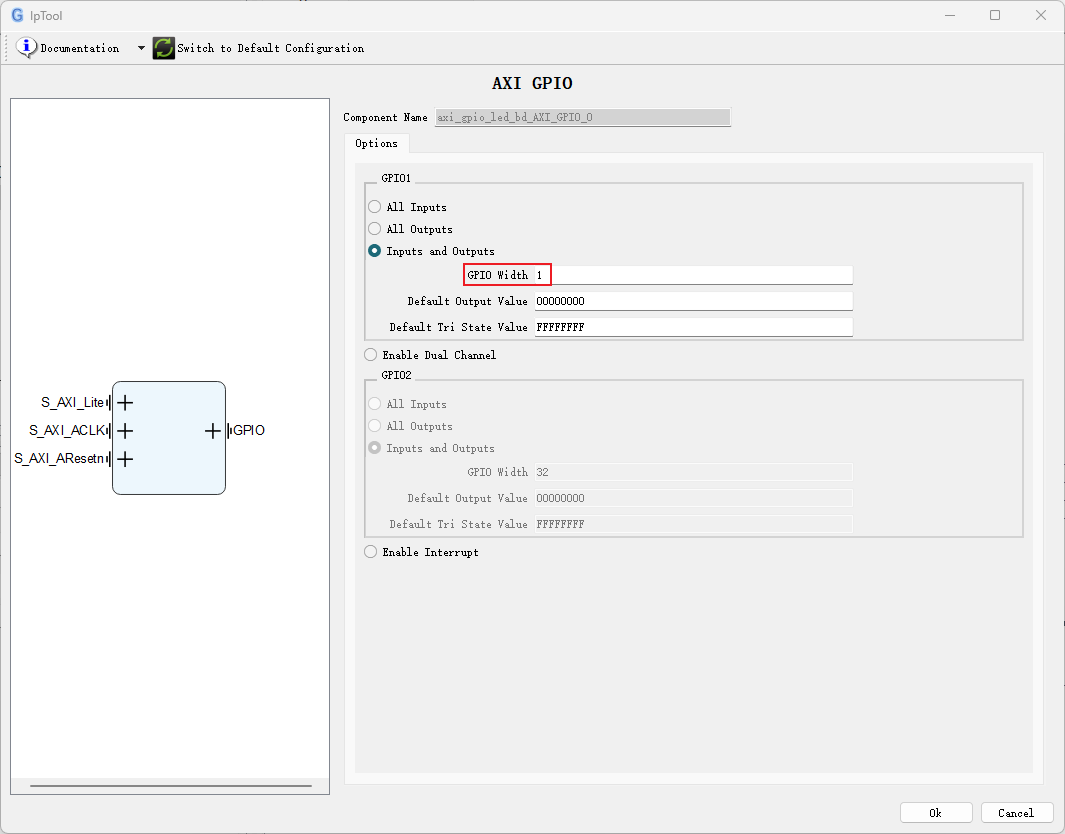

(2)AXI GPIO

圖 7

圖 7

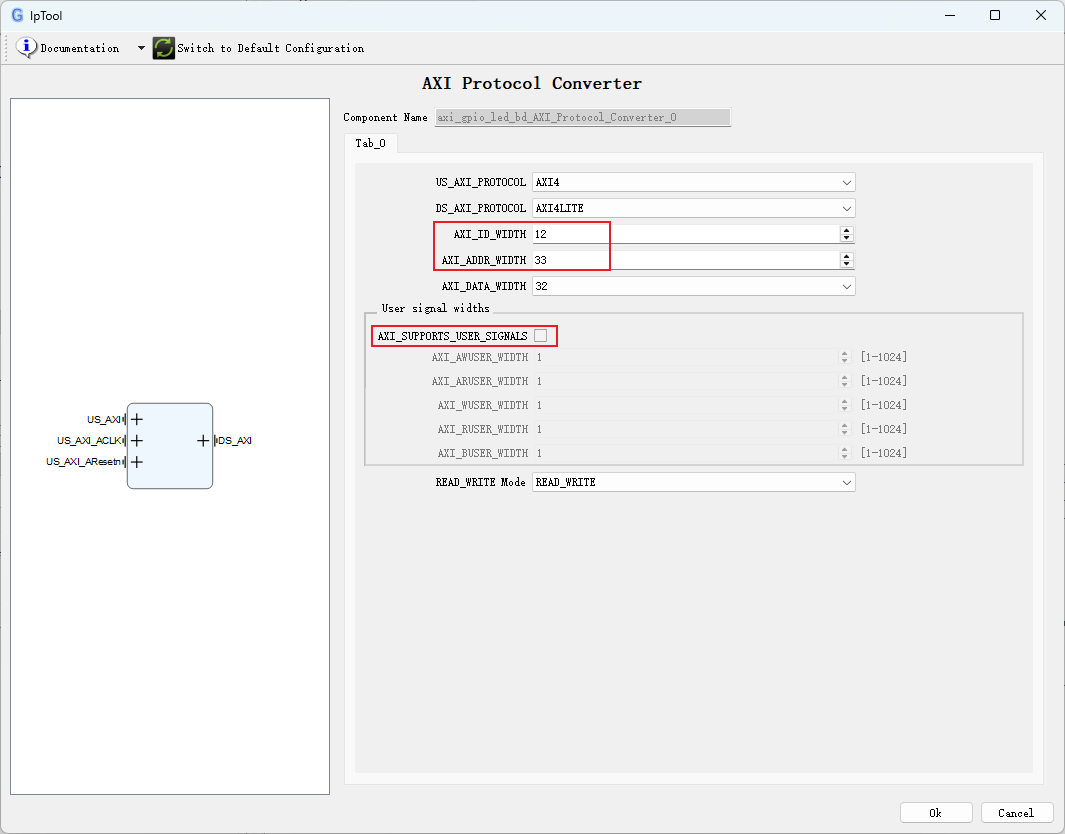

(3)AXIProtocolConverter

圖 8

圖 8

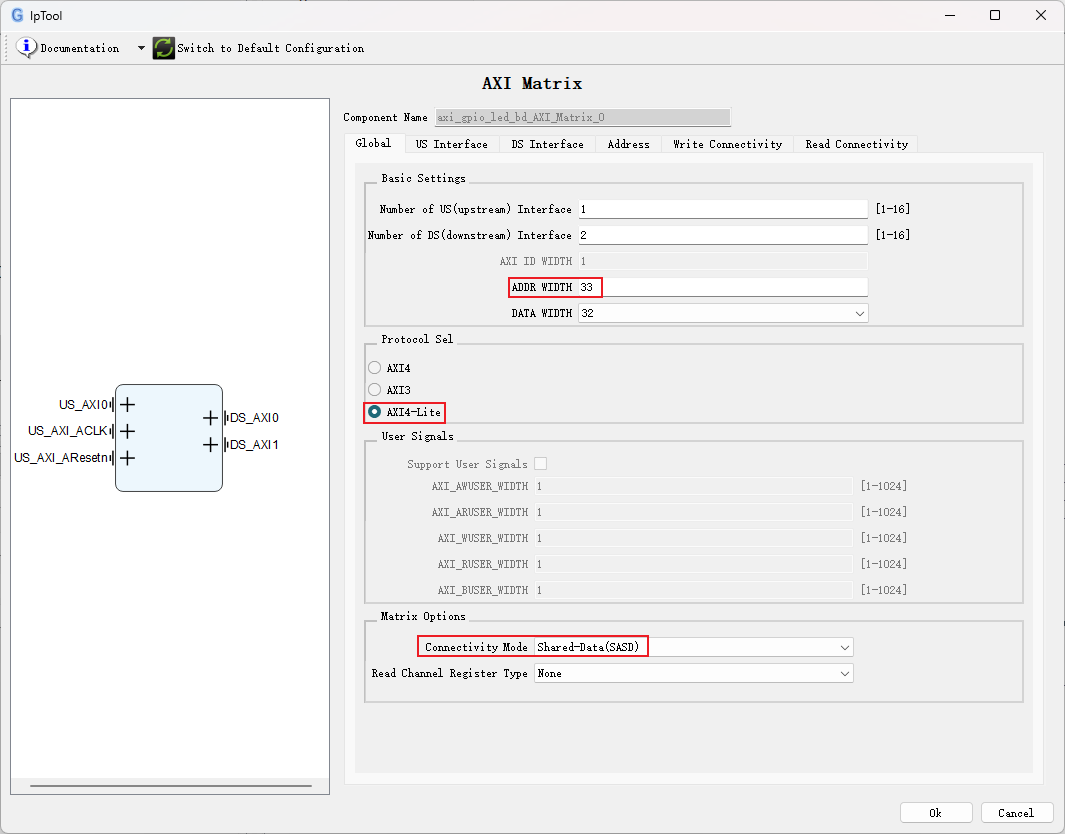

(4)AXIMatrix

圖 9

圖 9

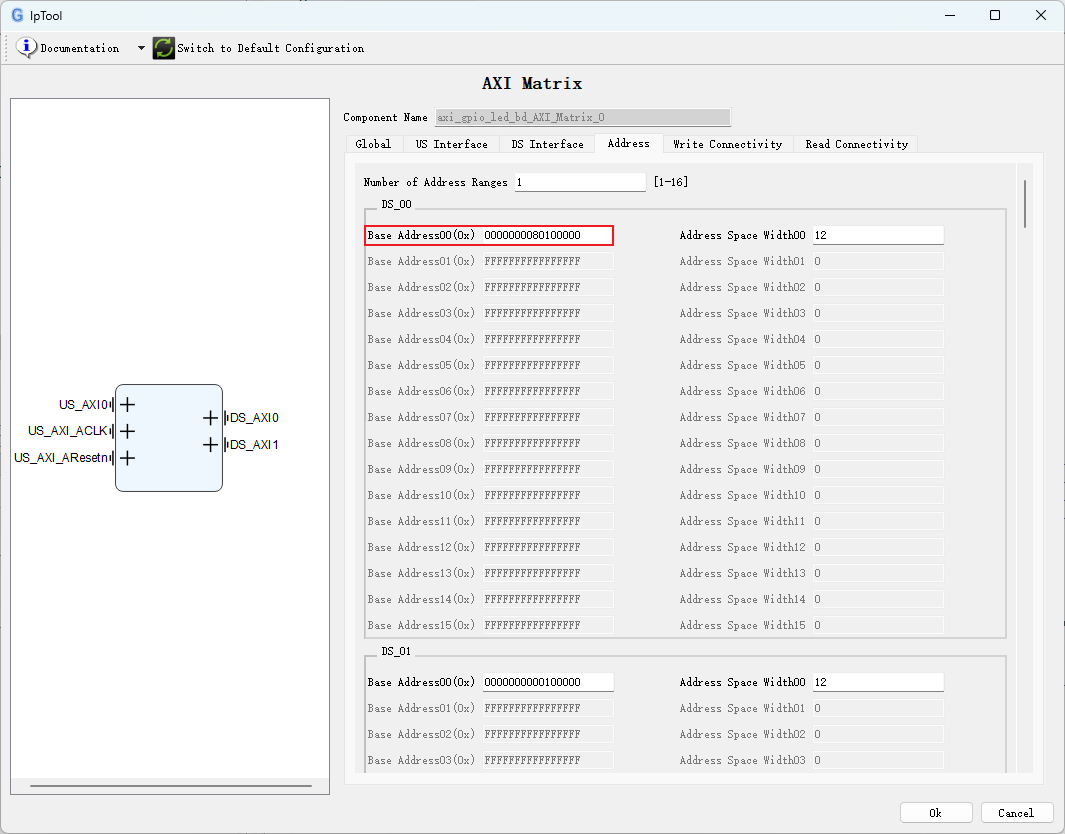

圖 10

圖 10

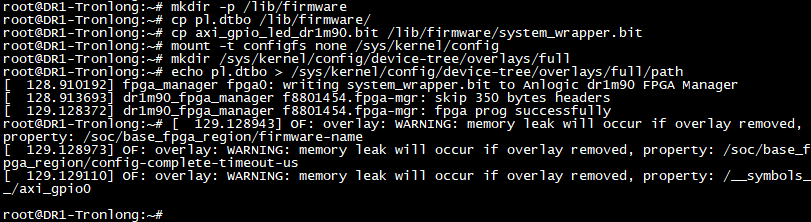

1.3 案例測(cè)試

將本案例的動(dòng)態(tài)設(shè)備樹鏡像文件pl.dtbo和PL端.bit鏡像文件拷貝至"/lib/firmware/"目錄下(若該目錄不存在,請(qǐng)新建),并將PL端可執(zhí)行文件重命名為system_wrapper.bit,然后執(zhí)行如下命令加載PL端鏡像。

Target# mkdir -p /lib/firmware

Target# cp pl.dtbo /lib/firmware/

Target# cp axi_gpio_led_dr1m90.bit /lib/firmware/system_wrapper.bit

Target# mount -t configfs none /sys/kernel/config

Target# mkdir /sys/kernel/config/device-tree/overlays/full //創(chuàng)建full目錄,可根據(jù)實(shí)際情況修改

Target# echo pl.dtbo > /sys/kernel/config/device-tree/overlays/full/path //dtbo文件名稱請(qǐng)根據(jù)實(shí)際情況修改

圖 11

圖 11

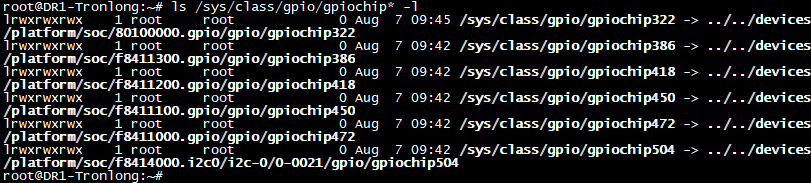

查看"/sys/class/gpio/"目錄下生成的gpiochip322節(jié)點(diǎn),地址為0x80100000,與axi_gpio_led案例給AXI GPIO IP分配的地址一致。

Target# ls /sys/class/gpio/gpiochip* -l

圖 12

圖 12

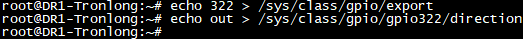

生成gpio322節(jié)點(diǎn),配置gpio322為output。

Target# echo 322 > /sys/class/gpio/export

Target# echo out > /sys/class/gpio/gpio322/direction

圖 13

圖 13

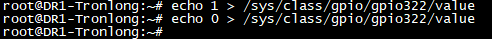

通過(guò)gpio322控制評(píng)估底板LED3亮滅。

Target# echo 1 > /sys/class/gpio/gpio322/value

Target# echo 0 > /sys/class/gpio/gpio322/value

圖 14

圖 14

審核編輯 黃宇

-

開發(fā)板

+關(guān)注

關(guān)注

26文章

6365瀏覽量

119939 -

核心板

+關(guān)注

關(guān)注

6文章

1410瀏覽量

32092

發(fā)布評(píng)論請(qǐng)先 登錄

DR1 系列評(píng)估板 eMMC 健康管理案例開發(fā)手冊(cè):信息查詢與壽命監(jiān)控

DR1 系列評(píng)估板 PS 端裸機(jī)與 FreeRTOS 開發(fā)案例手冊(cè)

DR1 系列核心板 PS+PL 異構(gòu)多核實(shí)戰(zhàn)案例手冊(cè)(二)

DR1 評(píng)估板 PL 端 FPGA 開發(fā)完全指南:基礎(chǔ)案例與 ADC 采集模塊詳解(一)

DR1M90 評(píng)估板 TD-FD 工程與 Linux 多場(chǎng)景應(yīng)用開發(fā)指南

DR1平臺(tái)Linux應(yīng)用開發(fā)指南:含GDB調(diào)試、Python及MQTT實(shí)戰(zhàn)

【玩轉(zhuǎn)多核異構(gòu)】T153核心板RISC-V核的實(shí)時(shí)性應(yīng)用解析

【米爾MYC-YM90X安路飛龍DR1開發(fā)板】HMI人機(jī)界面開發(fā)

重磅上新!Linux+AI多核異構(gòu)全志T527核心板/開發(fā)板,SX1262芯片升級(jí)款LoRa模塊

搭載ARM,NPU,F(xiàn)PGA三種核心的開發(fā)板—米爾安路DR1M90飛龍派

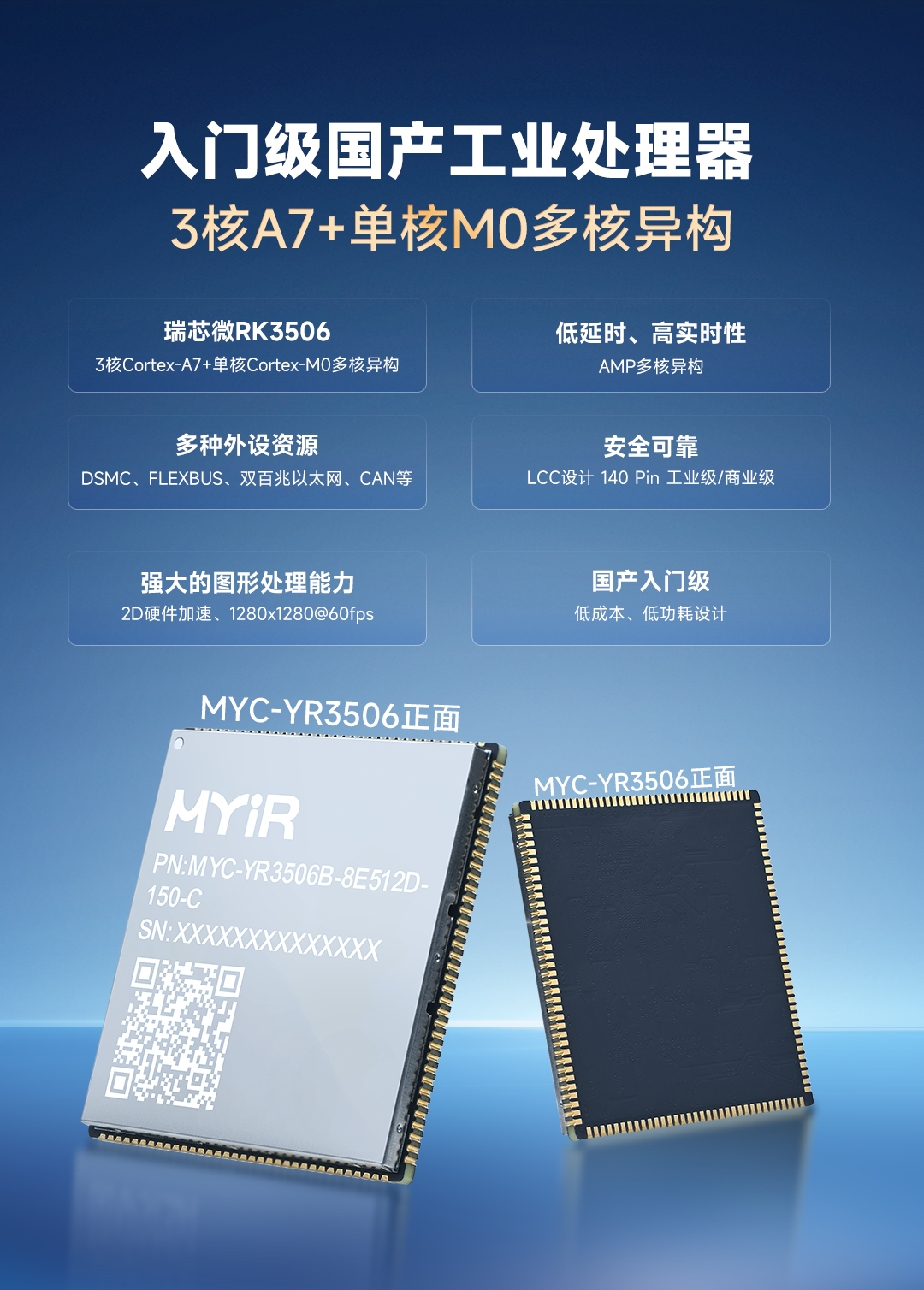

米爾瑞芯微多核異構(gòu)低功耗RK3506核心板重磅發(fā)布

3核A7+單核M0多核異構(gòu),米爾全新低功耗RK3506核心板發(fā)布

【米爾MYC-YM90X安路飛龍DR1開發(fā)板】安路科技 SALDRAGON開發(fā)板介紹

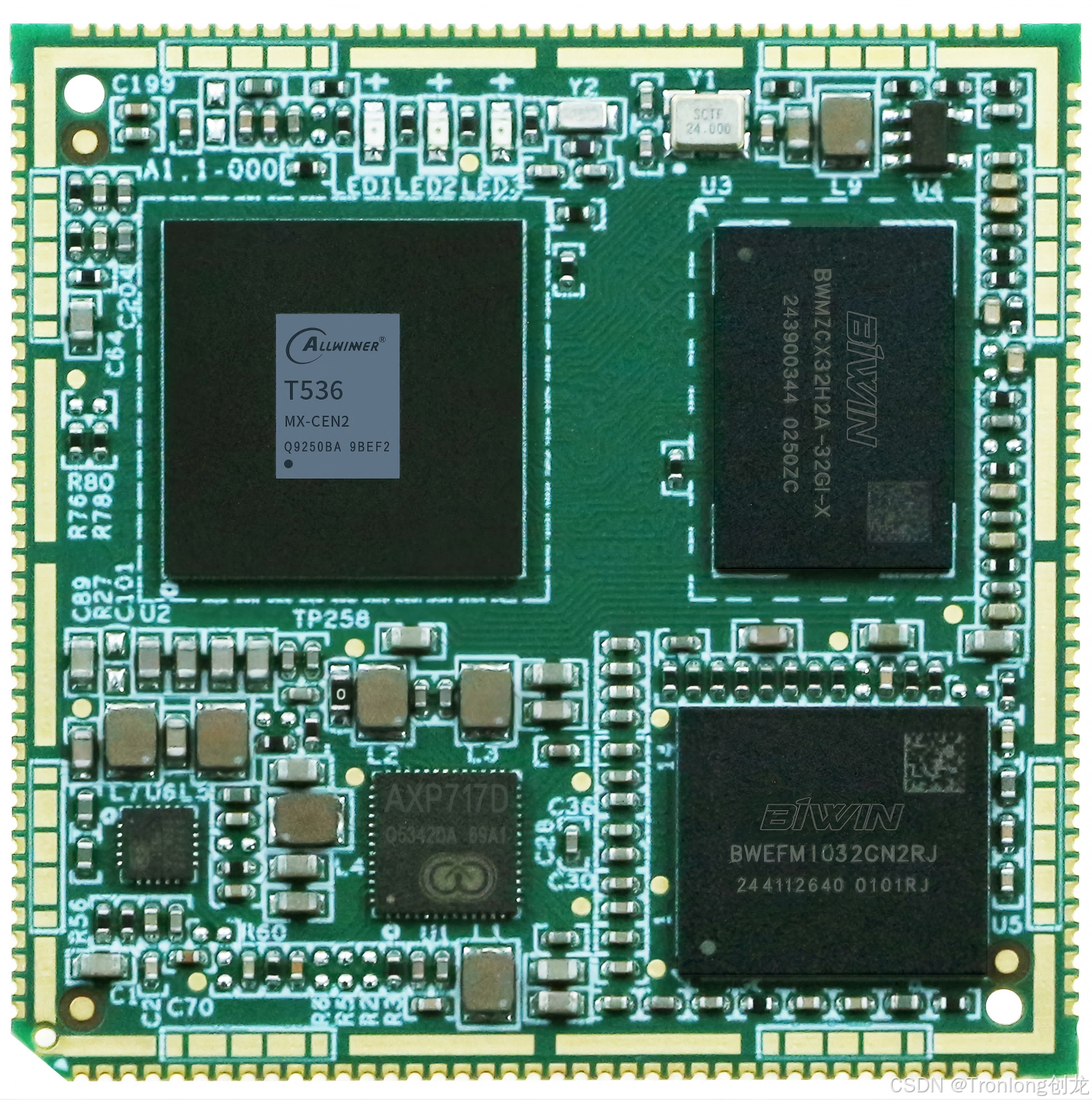

全志T536(異構(gòu)多核ARMCortex-A55+玄鐵E907 RISC-V)工業(yè)核心板說(shuō)明書

DR1 系列核心板 PS+PL 異構(gòu)多核實(shí)戰(zhàn)案例手冊(cè)(一)

DR1 系列核心板 PS+PL 異構(gòu)多核實(shí)戰(zhàn)案例手冊(cè)(一)

評(píng)論