作者:Hello,Panda

Zynq UltraScale+MPSoC是Xilinx推出的第二代多處理SoC系統(tǒng),在第一代Zynq-7000的基礎(chǔ)上做了全面升級(jí)。

一、概述

Zynq UltraScale+MPSoC系列器件共有四個(gè)大的系列,分別是CG系列、EG系列和EV系列,其中EG系列和EV系列提供汽車級(jí)和軍品級(jí)器件。

相較與上一代ZYNQ-7000產(chǎn)品,器件性能優(yōu)越性主要體現(xiàn)在:

a)PS性能顯著提升:64bit四核1.3GHz Cortex-A53 APU(CG系列是雙核);可運(yùn)行在獨(dú)立、鎖步模式的雙核533MHz Cortex-R5 RPU;

b)靜態(tài)存儲(chǔ):采用高達(dá)36Mb的高密度片上UltraRAM靜態(tài)存儲(chǔ)器,在通信等應(yīng)用中可完美取代片外SRAM;

c)高速互聯(lián):增強(qiáng)PS MIO性能,集成PCIe2.1x4、SATA3.0、DP1.2、USB3.0 等高速接口;PL高速收發(fā)器單通道速率達(dá)到32.75Gbps,集成了PCIExpress Gen 3 x16、150G Interlaken、100G Ethernet MAC/PCS等高速互聯(lián)資源;

d)電源管理:采用先進(jìn)的multi-domain,multi-island電源管理系統(tǒng),支持LPS子系統(tǒng)(符合ASIL-C和SIL3等標(biāo)準(zhǔn))和FPS子系統(tǒng)(符合ASIL-B和SIL2等標(biāo)準(zhǔn))兩類功耗模式工作;

e)高速數(shù)據(jù)轉(zhuǎn)換:RF系列集成增強(qiáng)的12bit/4.096GSPS RF數(shù)據(jù)直采ADC和14bit/6.554GSPS RF DAC;

f)視頻處理性能:EV系列集成H.265/264視頻Codec,可提供10位像素深度下4K/P60的編解碼性能;

g)增強(qiáng)的安全性能:支持4096bit RSA簽名(帶384bitSHA-3)和256bit AES認(rèn)證。

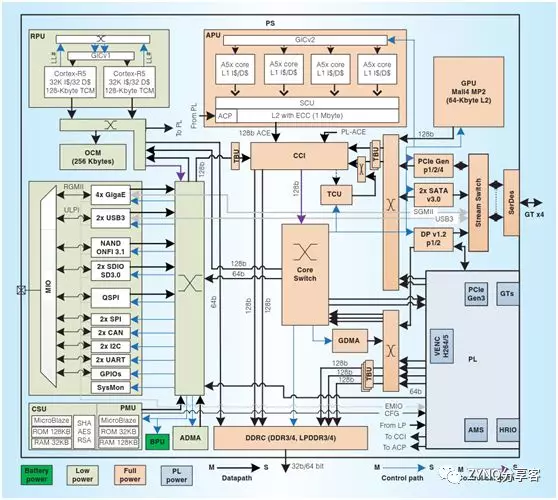

除此之外,器件的邏輯量、時(shí)鐘性能、DSP資源、DDR控制器帶寬、PS-PL交互帶寬等都得到了大幅度的提升,EV/EG系列還包括入門級(jí)Mali-400 GPU。當(dāng)然,價(jià)格上也有了質(zhì)的提升,便宜的也得數(shù)百美金,貴的嘛,高達(dá)數(shù)十萬(wàn)美金[見(jiàn)過(guò)國(guó)內(nèi)用的最便宜的RF系列的,單片價(jià)格一萬(wàn)美刀]。下圖1是Zynq UltraScale+ MPSoC系列器件的共有結(jié)構(gòu)框圖。

圖1 Zynq UltraScale+ MPSoC系列器件框圖

二、CG系列器件

CG系列器件APU為雙核A53,沒(méi)有Video Codec、GPU、只有16.3Gbps高速GTH收發(fā)器資源。

CG系列器件邏輯資源覆蓋103K~600K范圍,并且有不帶高速收發(fā)器和UltraRAM資源的Very Low Cost版本,封裝也有19×19mm A484和21×21mm A625的小尺寸封裝,是最有望能在一般應(yīng)用中能用得上、用得起的系列。

CG系列器件主要針對(duì)傳感處理系統(tǒng)、電機(jī)和控制系統(tǒng)、一般的音視頻系統(tǒng)、采集和互聯(lián)系統(tǒng)、存儲(chǔ)系統(tǒng)等領(lǐng)域。

三、EG系列器件

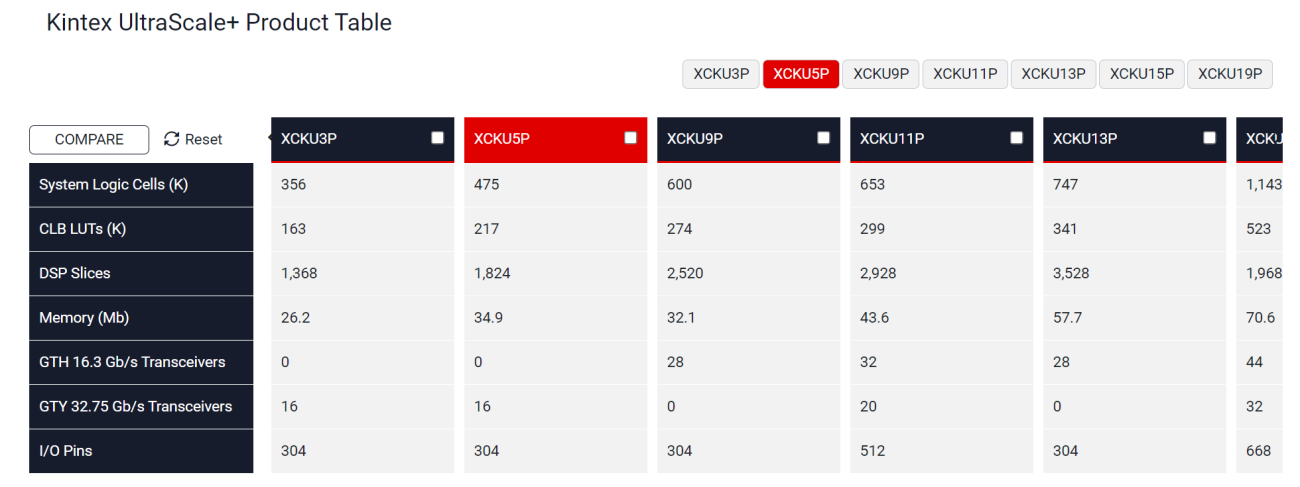

EG系列不含Video Codec,但是邏輯規(guī)模大、高速互聯(lián)資源強(qiáng)。該系列邏輯資源覆蓋103K~1143K,GTH、GTY、100G EMAC、150G Interlaken、PCIe Gen3 x16資源應(yīng)有盡有,Ultra RAM和DSP資源也特別豐富。

因此,EG系列的器件特別適合數(shù)據(jù)中心、云計(jì)算、AI、機(jī)器視覺(jué)、高性能醫(yī)療儀器等對(duì)計(jì)算能力要求高、互聯(lián)通信帶寬高時(shí)延小的的應(yīng)用領(lǐng)域。

四、EV系列器件

EV系列器件帶H.265/H.264 Codec硬核資源,只有三個(gè)型號(hào),分別是ZU4EV(192K)、ZU5EV(256K)和ZU7EV(504K),最小的封裝是23×23mm的C784,就目前來(lái)價(jià)格看,最便宜的約$400,一些高端視覺(jué)應(yīng)用中勉強(qiáng)可以接受。

該系列器件主要針對(duì)視覺(jué)領(lǐng)域的應(yīng)用,比如態(tài)勢(shì)感知(AR/全息等)、圖像檢測(cè)識(shí)別跟蹤等、汽車輔助駕駛(ADAS)等高性能視覺(jué)應(yīng)用。

五、RF系列器件

RF系列器件有ZU21/25/27/28/29DR 5個(gè)型號(hào)的器件,除ZU25DR外,其他型號(hào)的邏輯資源均為930K、Ultra RAM均為25Mb、DSP Slice均為4272個(gè),其他高速互聯(lián)資源應(yīng)有盡有,可以看成是EV系列去除GPU、增加RF ADC/DAC的版本。

RF系列器件的ADC有12bit/4.096GSPS RF-ADC w/DDC和12bit/2.058GSPS RF-ADC w/DDC兩個(gè)版本、14-bit/6.554GSPS RF-DAC w/DUC。ZU21/28DR還集成了SD-FEC。最大的目的是想要去掉中頻,實(shí)現(xiàn)射頻直采和直放。

從性能配置上看,該系列器件主要針對(duì)的是通信市場(chǎng),特別是5G市場(chǎng)。當(dāng)然,軍民用雷達(dá)、全球定位導(dǎo)航系統(tǒng)等也是通通可以用的。

該系列器件提供擴(kuò)展溫度級(jí)、工業(yè)級(jí)和軍品級(jí)器件,單片價(jià)格$10000以上,屬于禁運(yùn)清單產(chǎn)品。

編輯:hfy

-

收發(fā)器

+關(guān)注

關(guān)注

10文章

3833瀏覽量

111323 -

DDR

+關(guān)注

關(guān)注

11文章

759瀏覽量

69353 -

soc

+關(guān)注

關(guān)注

40文章

4595瀏覽量

229590 -

Xilinx

+關(guān)注

關(guān)注

73文章

2202瀏覽量

131519 -

Zynq

+關(guān)注

關(guān)注

10文章

631瀏覽量

49509

發(fā)布評(píng)論請(qǐng)先 登錄

第二代AMD Kintex UltraScale+ FPGA的亮點(diǎn)

【ALINX選型】AMD Kintex UltraScale+ 系列 FPGA 開(kāi)發(fā)板速選

如何在Zynq UltraScale+ MPSoC平臺(tái)上通過(guò)JTAG啟動(dòng)嵌入式Linux鏡像

如何在ZYNQ本地部署DeepSeek模型

AMD UltraScale架構(gòu):高性能FPGA與SoC的技術(shù)剖析

ALINX教程分享_Zynq UltraScale+ MPSoC PYNQ3.1.2移植

現(xiàn)已上市:AMD Spartan UltraScale+ FPGA SCU35 評(píng)估套件——面向所有開(kāi)發(fā)人員的經(jīng)濟(jì)實(shí)惠平臺(tái)

雙Zynq MPSoC PS側(cè)PCIe高速DMA互連解決方案

AMD Spartan UltraScale+ FPGA的優(yōu)勢(shì)和亮點(diǎn)

【VPX650 】青翼凌云科技基于 VPX 系統(tǒng)架構(gòu)的 VU13P FPGA+ZYNQ SOC 超寬帶信號(hào)處理平臺(tái)

fpga開(kāi)發(fā)板 璞致 Kintex UltraScale Plus PZ-KU3P 與 PZ-KU5P核心板與開(kāi)發(fā)板用戶手冊(cè)

璞致電子 UltraScale+ RFSoC 架構(gòu)下的軟件無(wú)線電旗艦開(kāi)發(fā)平臺(tái)

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 異構(gòu)架構(gòu)下的智能邊緣計(jì)算標(biāo)桿

AMD Spartan UltraScale+ FPGA 開(kāi)始量產(chǎn)出貨

Xilinx Ultrascale系列FPGA的時(shí)鐘資源與架構(gòu)解析

Xilinx ZYNQ UltraScale+四大系列概覽

Xilinx ZYNQ UltraScale+四大系列概覽

評(píng)論