由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結(jié)構(gòu)必須能實(shí)現(xiàn)板上的所有阻抗需求,包括內(nèi)層和外層、單端和差分線等。

2023-07-18 09:22:31 2160

2160

在設(shè)計(jì)電磁兼容性(EMC)表現(xiàn)優(yōu)異的 PCB 時(shí),疊層結(jié)構(gòu)的選擇是需要掌握的核心概念之一。

2025-07-15 10:25:03 6338

6338

電路板的疊層安排是對(duì)PCB的整個(gè)系統(tǒng)設(shè)計(jì)的基礎(chǔ)。疊層設(shè)計(jì)如有缺陷,將最終影響到整機(jī)的EMC性能。總的來(lái)說(shuō)疊層

2017-12-01 05:59:00 17662

17662 PCB疊層設(shè)計(jì),其實(shí)和做漢堡有類似的工藝。漢堡店會(huì)精心準(zhǔn)備每一層漢堡,就像PCB廠家的PCB板層疊在一起一樣。漢堡會(huì)有不同的大小和形狀,有各種各樣的配料,秘密醬汁覆蓋著我們自己的烤面包。就像我們?cè)?b class="flag-6" style="color: red">PCB上使用不同類型的金屬芯一樣,我們也會(huì)提供各種各樣的餡餅。

2022-09-02 17:17:57 9313

9313

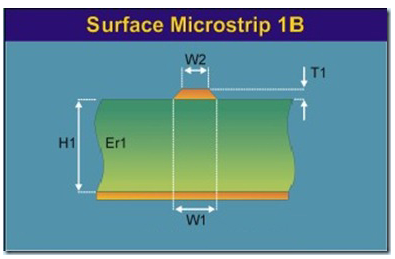

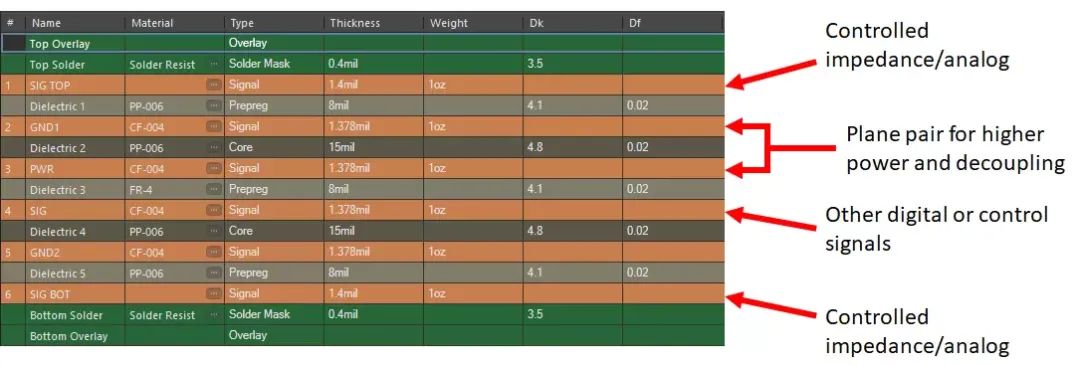

為了減少在高速信號(hào)傳輸過(guò)程中的反射現(xiàn)象,必須在信號(hào)源、接收端以及傳輸線上保持阻抗的匹配。單端信號(hào)線的具體阻抗取決于它的線寬尺寸以及與參考平面之間的相對(duì)位置。特定阻抗要求的差分對(duì)間的線寬/線距則取決于選擇的PCB疊層結(jié)構(gòu)。

2023-07-12 09:10:21 3085

3085

決于選擇的PCB疊層結(jié)構(gòu)。由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結(jié)構(gòu)必須能實(shí)現(xiàn)板上的所有阻抗需求,包括內(nèi)層和外層、單端和差分

2023-07-31 10:18:02 1567

1567

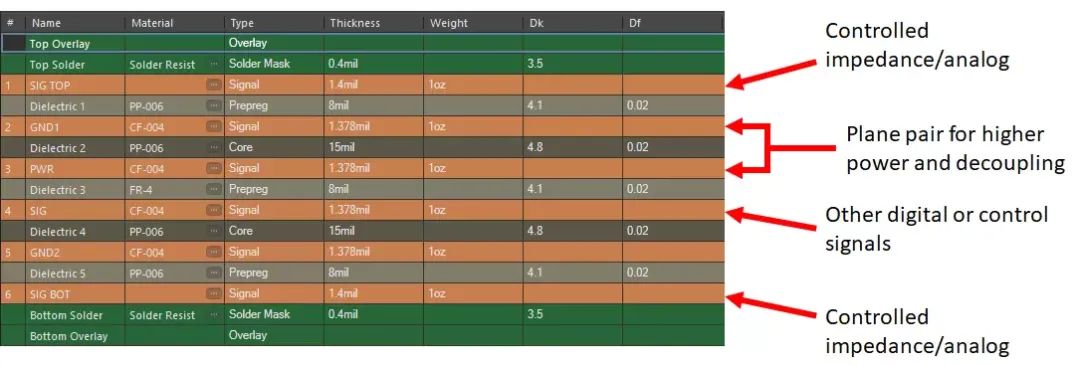

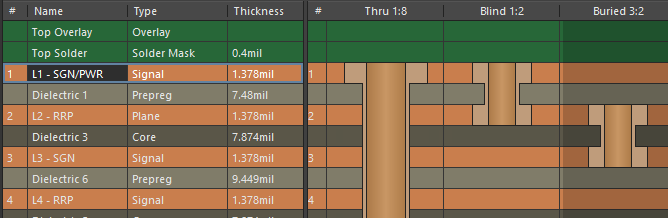

只有使用正確的PCB疊層進(jìn)行構(gòu)建,高速設(shè)計(jì)才能成功運(yùn)行。您的疊層必須正確布置電源和接地層,為信號(hào)分配足夠的層,并且所有材料組和銅選擇均能以適當(dāng)?shù)囊?guī)模和成本制造。如果設(shè)計(jì)人員能夠獲得正確的疊層,那么在確保信號(hào)完整性的情況下布線就會(huì)容易得多,并且可以抑制或防止許多更簡(jiǎn)單的EMI問(wèn)題。

2023-08-04 10:47:16 1240

1240

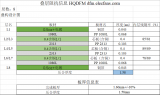

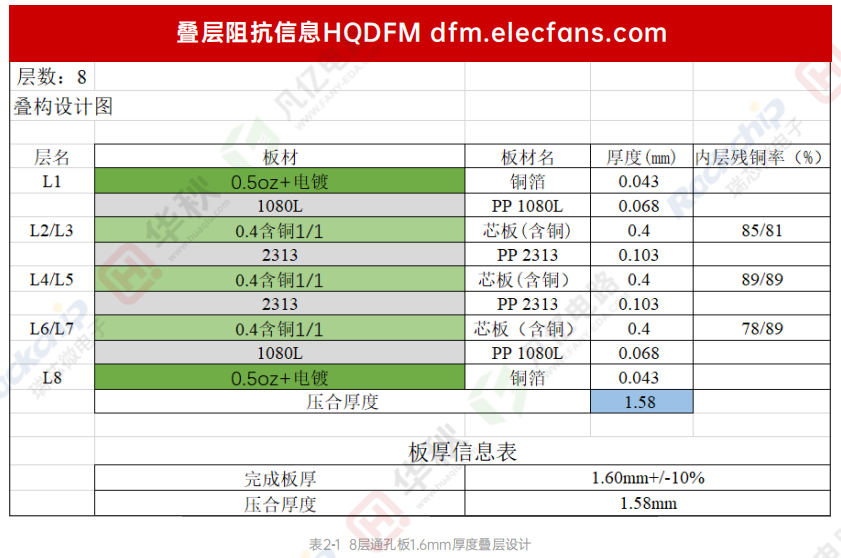

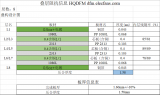

分享,《RK3588 PCB設(shè)計(jì)指導(dǎo)白皮書》其中章節(jié)——RK3588 PCB推薦疊層及阻抗設(shè)計(jì)。(文末附《RK3588 PCB設(shè)計(jì)指導(dǎo)白皮書》下載入口)

2023-08-10 09:32:51 1817

1817

層中看到的所有元素,但最終制造商將處理該決定,以努力在可用材料與加工能力和產(chǎn)量之間取得平衡。 疊層描述的不僅僅是PCB的基本結(jié)構(gòu);疊層中內(nèi)置了許多其他設(shè)計(jì)考慮因素,這些因素由您的核心材料和介電材料的材料特性定義。為確保您的

2023-09-15 09:41:34 1669

1669

4層PCB上的空間用完后,就該升級(jí)到6層電路板了。額外的層可以為更多的信號(hào)、額外的平面對(duì)或?qū)w的混合提供空間。如何使用這些額外的層并不重要,重要的是如何在PCB疊層中排列它們,以及如何在6層PCB上

2023-10-16 15:24:34 4129

4129

每次PCB設(shè)計(jì)最讓你頭疼的是什么?是密密麻麻的走線?還是讓人抓狂的EMI問(wèn)題?問(wèn)題的根源可能藏在你看不見(jiàn)的地方——PCB疊層結(jié)構(gòu)。當(dāng)你的設(shè)計(jì)從實(shí)驗(yàn)室小批量轉(zhuǎn)到批量生產(chǎn)時(shí),是否遇到過(guò)信號(hào)完整性突然惡化

2025-06-25 07:36:24 2570

2570

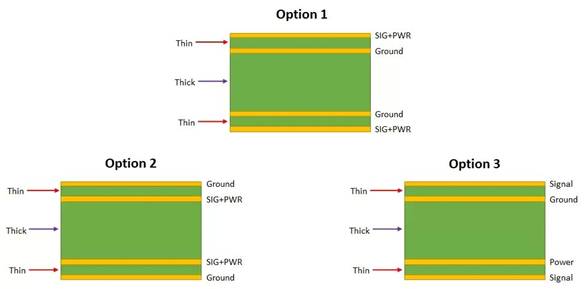

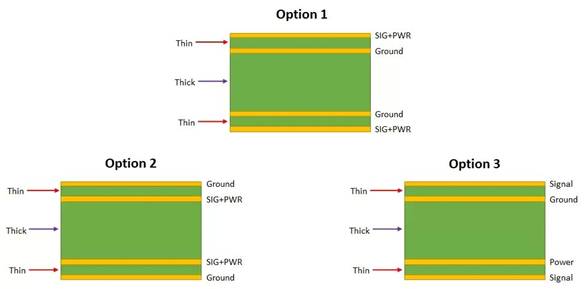

4.3.3 實(shí)驗(yàn)設(shè)計(jì)3:4層PCB 本章將考慮4層PCB疊層的幾種不同變體。這些變化中最簡(jiǎn)單的是基于實(shí)驗(yàn)設(shè)計(jì)2層疊層(第4.3.2節(jié)),外加兩個(gè)額外的內(nèi)部信號(hào)層。假設(shè)附加層主要由許多較薄的信號(hào)

2023-04-20 17:10:43

了信號(hào)線的特征阻抗,也可有效地減少串?dāng)_。所以,對(duì)于某些高端的高速電路設(shè)計(jì),已經(jīng)明確規(guī)定一定要使用6層(或以上的)的疊層方案,如Intel對(duì)PC133內(nèi)存模塊PCB的要求。這主要就是考慮到多層板在電氣

2016-05-17 22:04:05

本帖最后由 lee_st 于 2017-10-31 08:48 編輯

PCB疊層設(shè)計(jì)及阻抗計(jì)算

2017-10-21 20:44:57

PCB疊層設(shè)計(jì)及阻抗計(jì)算

2017-09-28 15:13:07

PCB疊層設(shè)計(jì)及阻抗計(jì)算

2016-06-02 17:13:08

到的電源優(yōu)先鋪整塊銅皮;易受干擾的、高速的、沿跳變的優(yōu)選走內(nèi)層等等。 下表給出了多層板層疊結(jié)構(gòu)的參考方案,供參考。 PCB設(shè)計(jì)之疊層結(jié)構(gòu)改善案例(From金百澤科技) 問(wèn)題點(diǎn) 產(chǎn)品有8組網(wǎng)口與光口,測(cè)試

2018-09-18 15:12:16

至目標(biāo)厚度

設(shè)計(jì)完成關(guān)鍵步驟:用工具驗(yàn)證疊層

疊層設(shè)計(jì)完成后,如何驗(yàn)證?傳統(tǒng)方法依賴工程師經(jīng)驗(yàn),現(xiàn)在 華秋DFM軟件提供了一站式解決方案 。

1、阻抗神器

結(jié)合各種生產(chǎn)因素,自動(dòng)計(jì)算或反算阻抗,確保

2025-06-24 20:09:53

是電路板設(shè)計(jì)的一個(gè)重要指標(biāo),特別是在高頻電 路的PCB設(shè)計(jì)中,必須考慮導(dǎo)線的特性阻抗和器件或信號(hào)所要求的特性阻抗是否一致,是否匹配。這就涉及到兩個(gè)概念:阻抗控制與阻抗匹配,本文重點(diǎn)討論阻抗控制和疊層設(shè)計(jì)的問(wèn)題。

2019-05-30 07:18:53

PCB板阻抗設(shè)計(jì):阻抗線有無(wú)參考層阻抗如何變化?生產(chǎn)PCB時(shí)少轉(zhuǎn)彎的阻抗線的阻抗更容易控制穩(wěn)定性?

2023-04-10 17:03:31

PCB線路板疊層設(shè)計(jì)要注意哪些問(wèn)題呢?

2021-03-29 08:12:19

PCB設(shè)計(jì)中疊層算阻抗時(shí)需注意哪些事項(xiàng)?

2019-05-16 11:06:01

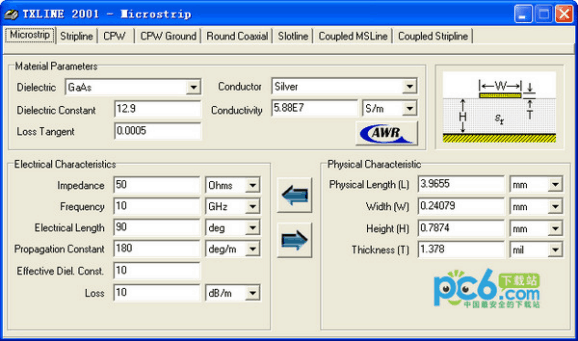

在高速PCB設(shè)計(jì)流程里,疊層設(shè)計(jì)和阻抗計(jì)算是登頂?shù)牡谝惶荨?b class="flag-6" style="color: red">阻抗計(jì)算方法很成熟,不同軟件的計(jì)算差別不大,相對(duì)而言比較繁瑣,阻抗計(jì)算和工藝制程之間的一些"權(quán)衡的藝術(shù)",主要是為了達(dá)到

2018-01-22 14:41:32

% ,如其他默認(rèn)的參數(shù)需要調(diào)整,可以在參數(shù)配置里面填寫修改,保存即可。

二、計(jì)算阻抗匹配介質(zhì)厚度壓合圖

1、硬板疊層圖

1) 華秋DFM軟件可以 自動(dòng)生成疊層圖 ,也可以手動(dòng)填寫層數(shù)、板厚、銅厚等,用疊層圖

2023-09-13 11:03:22

為此困擾,這里推薦一款可以一鍵智能計(jì)算阻抗自動(dòng)疊層的工具: 華秋DFM軟件 ,使用其阻抗計(jì)算功能,可以高效輕松反算和計(jì)算所需阻抗和線寬線距等。

2023-12-25 13:46:25

為此困擾,這里推薦一款可以一鍵智能計(jì)算阻抗自動(dòng)疊層的工具: 華秋DFM軟件 ,使用其阻抗計(jì)算功能,可以高效輕松反算和計(jì)算所需阻抗和線寬線距等。

2023-12-25 13:48:49

影響因素則與特性阻抗相同。

7、共面阻抗

阻抗線距導(dǎo)體的間距與阻抗成正比,間距越大,阻抗越大,其它影響因素則與特性阻抗相同。

阻抗計(jì)算神器驗(yàn)證影響因素

1、疊層圖制作

這里推薦一款免費(fèi)的國(guó)產(chǎn)工具:華

2023-05-04 16:43:04

您還在為阻抗設(shè)計(jì)頭疼嗎?這里有齊全的阻抗參數(shù)及疊層結(jié)構(gòu)。有它您無(wú)需再去仿真,我們已將其一一列出,如 90ohm線寬線距為7/6mil 或 5/4mil ,結(jié)合布線空間選擇對(duì)應(yīng)的線寬線距。

2020-06-10 20:54:11

多層板疊層設(shè)計(jì)規(guī)則,單層、雙層PCB板的疊層,推薦設(shè)計(jì)方式,設(shè)計(jì)方案講解。

2021-03-29 11:58:10

`非常經(jīng)典的PCB阻抗設(shè)計(jì)教程資料,詳細(xì)介紹了阻抗參數(shù)計(jì)算、多層面板設(shè)計(jì)步驟與思路,值得一看。`

2021-03-29 14:14:04

常見(jiàn)的PCB疊層結(jié)構(gòu),四層板、六層板、八層板十層板疊層設(shè)計(jì)及注意事項(xiàng)。

2021-03-29 11:49:35

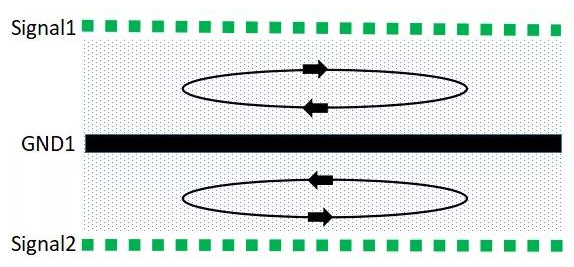

阻抗的電流返回路徑最重要的就是合理規(guī)劃這些參考平面的設(shè)計(jì)。圖1所示為一種典型多層PCB疊層配置。圖1 一種典型多層PCB疊層配置回復(fù)帖子查看資料下載鏈接:[hide][/hide]

2021-08-04 10:18:25

的眾多變量。本文將討論如何確定哪些PCB疊層信息需要了解的方式方法。回復(fù)帖子查看資料下載鏈接:[hide][/hide]

2021-08-04 10:13:17

本文主要介紹多層PCB設(shè)計(jì)疊層的基礎(chǔ)知識(shí),包括疊層結(jié)構(gòu)的排布一般原則,常用的疊層結(jié)構(gòu),疊層結(jié)構(gòu)的改善案例分析。回復(fù)帖子查看資料下載鏈接:[hide][/hide]

2021-08-04 10:06:58

,其余影響因素則與特性阻抗相同。

共面阻抗

阻抗線距導(dǎo)體的間距與阻抗成正比,間距越大,阻抗越大,其它影響因素則與特性阻抗相同。

阻抗計(jì)算神器驗(yàn)證影響因素

疊層圖制作

這里推薦一款免費(fèi)的國(guó)產(chǎn)工具:華秋

2023-04-28 11:01:02

則與特性阻抗相同。

共面阻抗

阻抗線距導(dǎo)體的間距與阻抗成正比,間距越大,阻抗越大,其它影響因素則與特性阻抗相同。

阻抗計(jì)算神器驗(yàn)證影響因素

疊層圖制作

這里推薦一款免費(fèi)的國(guó)產(chǎn)工具:華秋DFM軟件

2023-04-28 11:12:07

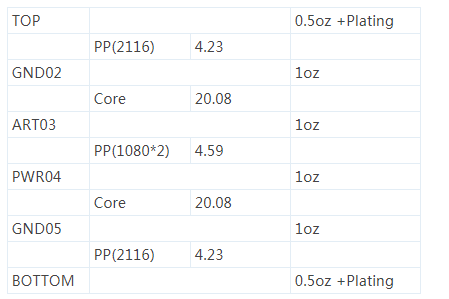

PCB設(shè)計(jì)中層疊結(jié)構(gòu)的設(shè)計(jì)建議:1、PCB疊層方式推薦為Foil疊法2、盡可能減少PP片和CORE型號(hào)及種類在同一層疊中的使用(每層介質(zhì)不超過(guò)3張PP疊層)3、兩層之間PP介質(zhì)厚度不要超過(guò)21MIL

2017-01-16 11:40:35

聽(tīng)說(shuō)多級(jí)阻抗PCB有獨(dú)特的計(jì)算方法?一起來(lái)看看吧

2023-04-14 15:50:20

多層PCB如何定義疊層呢?

2023-04-11 14:53:59

搞定疊層,你的PCB設(shè)計(jì)也可以很高級(jí)

2020-12-28 06:44:43

電路板的疊層設(shè)計(jì)是對(duì)PCB的整個(gè)系統(tǒng)設(shè)計(jì)的基礎(chǔ),疊層設(shè)計(jì)若有缺陷,將最終影響到整機(jī)的EMC性能。疊層設(shè)計(jì)是一個(gè)復(fù)雜的,嚴(yán)謹(jǐn)過(guò)程,當(dāng)然,設(shè)計(jì)開(kāi)發(fā),沒(méi)必要從零開(kāi)始經(jīng)過(guò)一系列的復(fù)雜計(jì)算和仿真,來(lái)確定設(shè)計(jì)方案是否合適,僅需要總結(jié)前人的經(jīng)驗(yàn),選擇合適系統(tǒng)的疊層方案。

2021-11-12 07:59:58

工作,其他7組光口通信正常。1、問(wèn)題點(diǎn)確認(rèn)根據(jù)客戶端提供的信息,確認(rèn)為L(zhǎng)6層光口8與芯片8之間的兩條差分阻抗線調(diào)試不通;2、客戶提供的疊構(gòu)與設(shè)計(jì)要求改善措施 影響阻抗信號(hào)因素分析: 線路圖分析:客戶

2019-05-29 08:11:41

,可以在參數(shù)配置里面填寫修改,保存即可。

計(jì)算阻抗匹配介質(zhì)厚度壓合圖

硬板疊層圖

1、華秋DFM軟件可以 自動(dòng)生成疊層圖 ,也可以手動(dòng)填寫層數(shù)、板厚、銅厚等,用疊層圖的介質(zhì)厚度匹配阻抗。

2、如需調(diào)整疊

2023-09-15 14:12:46

信號(hào)線(高速信號(hào))數(shù)量不多,區(qū)域集中,也可以使用這個(gè)層疊方案,局部高速信號(hào)區(qū)域?qū)?yīng)的相鄰層鋪地銅,做成局部3層布線(L1&L4&L6)。疊層如下(阻抗計(jì)算從略,大家可以自己算算,后面

2019-05-30 07:20:55

信號(hào)線(高速信號(hào))數(shù)量不多,區(qū)域集中,也可以使用這個(gè)層疊方案,局部高速信號(hào)區(qū)域?qū)?yīng)的相鄰層鋪地銅,做成局部3層布線(L1&L4&L6)。疊層如下(阻抗計(jì)算從略,大家可以自己算算,后面

2022-03-07 16:04:23

關(guān)鍵信號(hào)線(高速信號(hào))數(shù)量不多,區(qū)域集中,也可以使用這個(gè)層疊方案,局部高速信號(hào)區(qū)域?qū)?yīng)的相鄰層鋪地銅,做成局部3層布線(L1&L4&L6)。疊層如下(阻抗計(jì)算從略,大家可以自己算算,后面

2019-05-29 07:26:53

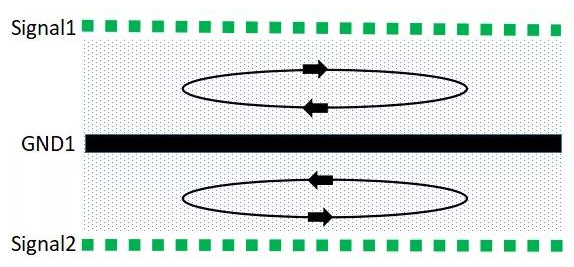

的低阻抗的電流返回路徑最重要的就是合理規(guī)劃這些參考平面的設(shè)計(jì)。圖1所示為一種典型多層PCB疊層配置。 信號(hào)層大部分位于這些金屬實(shí)體參考平面層之間,構(gòu)成對(duì)稱帶狀線或是非對(duì)稱帶狀線。此外,板子的上、下兩個(gè)

2018-11-27 15:14:59

高速PCB設(shè)計(jì)的疊層問(wèn)題

2009-05-16 20:51:30

而言就是降低了成本;另一方面,合拼的PCB板,如采用相對(duì)一致的疊層結(jié)構(gòu),在壓合工序可提高產(chǎn)品質(zhì)量。

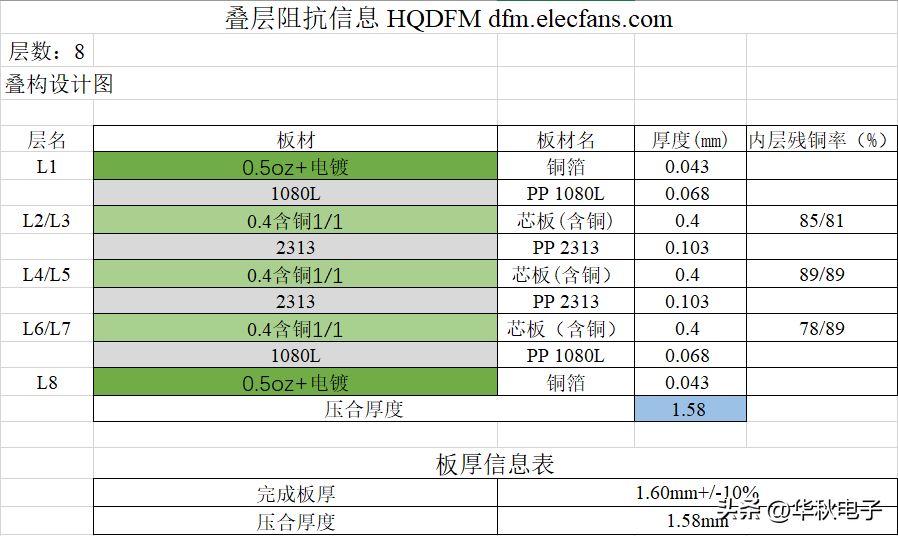

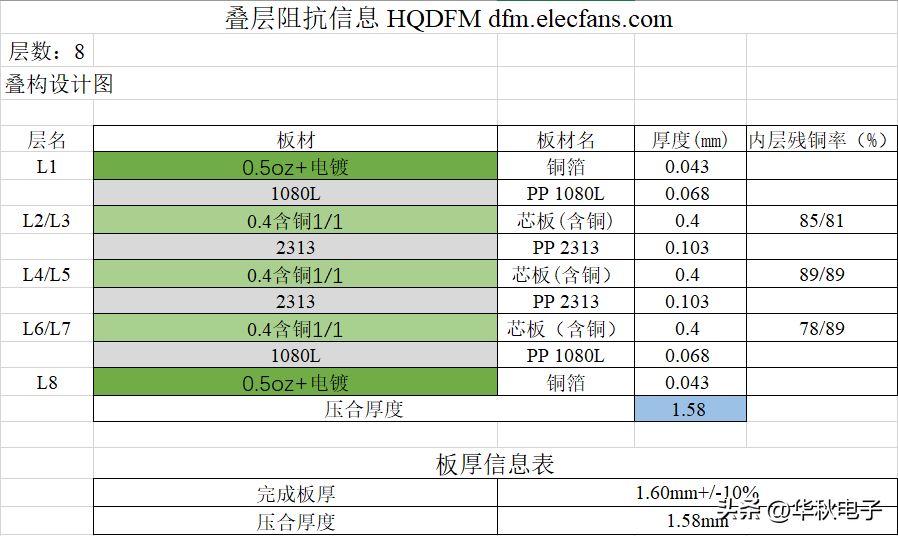

下圖是華秋推薦疊層結(jié)構(gòu)其中之一,更多的疊層設(shè)計(jì)可參考華秋DFM阻抗計(jì)算,也可參考華秋PCB官網(wǎng)推薦疊層

2023-05-26 11:30:36

高速PCB設(shè)計(jì)的疊層問(wèn)題

2009-05-16 20:06:45 0

0 使用polar 工具計(jì)算阻抗!以一個(gè)四層板為例,四層板的一般疊層為 top gnd02 power03 bottom從四層板的疊層來(lái)看是由兩個(gè)信號(hào)層加平面層組成。詳細(xì)計(jì)算步驟如

2010-04-05 06:47:27 44

44 【珍藏版】PCB阻抗設(shè)計(jì)與疊層方案,感興趣的小伙伴們可以看看。

2016-07-26 11:11:00 0

0 在高速PCB設(shè)計(jì)流程里,疊層設(shè)計(jì)和阻抗計(jì)算是登頂?shù)牡谝惶荨O旅嫖覀兛偨Y(jié)了一些設(shè)計(jì)疊層算阻抗是的注意事項(xiàng),幫助大家提高計(jì)算效率。

2018-01-22 14:00:07 6385

6385

我們都知道,電路板的疊層安排是對(duì)PCB的整個(gè)系統(tǒng)設(shè)計(jì)的基礎(chǔ)。疊層設(shè)計(jì)如有缺陷,將最終影響到整機(jī)的emc性能。那么下面就和咱一起來(lái)看看到底如何才看懂疊層文件吧~

2018-10-27 07:58:00 5925

5925 我們都知道,電路板的疊層安排是對(duì)PCB的整個(gè)系統(tǒng)設(shè)計(jì)的基礎(chǔ)。疊層設(shè)計(jì)如有缺陷,將最終影響到整機(jī)的emc性能。那么下面就和咱一起來(lái)看看到底如何才看懂疊層文件吧~

2018-10-27 09:56:02 13305

13305

在高速PCB設(shè)計(jì)流程里,疊層設(shè)計(jì)和阻抗計(jì)算是登頂?shù)牡谝惶荨?b class="flag-6" style="color: red">阻抗計(jì)算方法很成熟,不同軟件的計(jì)算差別不大,相對(duì)而言比較繁瑣,阻抗計(jì)算和工藝制程之間的一些"權(quán)衡的藝術(shù)",主要是為了達(dá)到我們阻抗管控目的的同時(shí),也能保證工藝加工的方便,以及盡量降低加工成本。

2018-12-01 10:56:49 4150

4150 做pcb設(shè)計(jì)過(guò)程中,在走線之前,一般我們會(huì)對(duì)自己要進(jìn)行設(shè)計(jì)的項(xiàng)目進(jìn)行疊層,根據(jù)厚度、基材、層數(shù)等信息進(jìn)行計(jì)算阻抗,計(jì)算完后一般可得到如下內(nèi)容。

2019-03-16 09:04:03 9434

9434

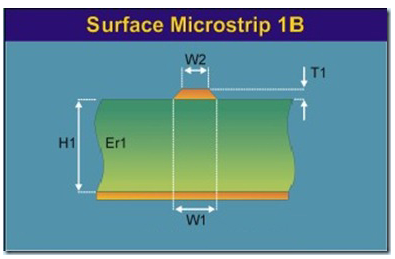

PCB跡線的阻抗將由其感應(yīng)和電容性電感、電阻和電導(dǎo)系數(shù)確定。影響PCB走線的阻抗的因素主要有: 銅線的寬度、銅線的厚度、介質(zhì)的介電常數(shù)、介質(zhì)的厚度、焊盤的厚度、地線的路徑、走線周邊的走線等。PCB阻抗的范圍是 25 至120 歐姆。

2019-08-08 15:23:43 5235

5235

我的第一塊PCB遠(yuǎn)離高速數(shù)字設(shè)備。它只是單層PCB上的放大器電路,控制阻抗甚至不是事后的想法。一旦我開(kāi)始研究需要高采樣率的電光系統(tǒng),控制阻抗始終是一個(gè)關(guān)鍵的設(shè)計(jì)問(wèn)題。電路板上的受控阻抗是PCB布局問(wèn)題,我在處理PCB一段時(shí)間后感覺(jué)不太舒服。

2019-07-25 09:13:38 2686

2686 阻抗控制PCB 在高頻應(yīng)用中,信號(hào)不會(huì)因?yàn)樗鼈冊(cè)?b class="flag-6" style="color: red">PCB中的路徑而降級(jí)。 在PCB設(shè)計(jì)中通過(guò)疊層計(jì)算阻抗控制時(shí)需要注意的四個(gè)問(wèn)題 在高速PCB設(shè)計(jì)過(guò)程中,堆棧設(shè)計(jì)和阻抗計(jì)算是邁向頂端的第一步。阻抗

2019-07-29 14:02:17 3541

3541

如何設(shè)計(jì)4層PCB板疊層?

2019-07-31 10:49:44 19768

19768 對(duì)于兩層板來(lái)說(shuō),由于板層數(shù)量少,已經(jīng)不存在疊層的問(wèn)題。

2020-03-12 16:41:39 2594

2594 PCB的疊層設(shè)計(jì)不是層的簡(jiǎn)單堆疊,其中地層的安排是關(guān)鍵,它與信號(hào)的安排和走向有密切的關(guān)系。

2019-08-21 11:45:18 2170

2170 PCB的疊層設(shè)計(jì)通常是在考慮各方面的因素后折中決定的。高速數(shù)字電路和射須電路通常采用多層板設(shè)計(jì)。

2019-08-23 16:45:21 1198

1198 PCB疊層EMC規(guī)劃與設(shè)計(jì)思路的核心就是合理規(guī)劃信號(hào)回流路徑,盡可能減小信號(hào)從單板鏡像層的回流面積,使得磁通對(duì)消或最小化。

2020-01-22 17:12:00 1283

1283

硬件工程師應(yīng)該掌握的PCB疊層設(shè)計(jì)內(nèi)容

2020-01-10 14:17:12 3760

3760 示例講解: 一、單面PCB板和雙面PCB板的疊層 對(duì)于兩層板來(lái)說(shuō),由于板層數(shù)量少,已經(jīng)不存在疊層的問(wèn)題。控制EMI輻射主要從布線和布局來(lái)考慮; 單層板和雙層板的電磁兼容問(wèn)題越來(lái)越突出。造成這種現(xiàn)象的主要原因就是因是信號(hào)回路面積過(guò)大,不僅產(chǎn)生

2020-04-13 09:34:57 3623

3623 在PCB設(shè)計(jì)中,對(duì)于消費(fèi)類電子或者一些對(duì)成本要求比較高的PCB板,為了成本的降低,多采用6層板設(shè)計(jì),而器件布局空間上也是比較緊張的,這就對(duì)疊層的分配和信號(hào)規(guī)劃有了較高的要求。

2020-05-12 16:19:07 6252

6252 靈活性的優(yōu)點(diǎn),但也存在缺點(diǎn)。充分了解優(yōu)缺點(diǎn)將有助于我們確定何時(shí)使用此技術(shù)。然后我們看一下如何優(yōu)化剛?cè)?b class="flag-6" style="color: red">疊層設(shè)計(jì)。 剛?cè)?b class="flag-6" style="color: red">疊層 PCB :優(yōu)點(diǎn)和缺點(diǎn) 剛?cè)崾?PCB 的三種常見(jiàn)分類之一。另外兩個(gè)是剛性的(大多數(shù)板都是剛性的),并且是彎曲的,

2020-09-16 20:46:57 2756

2756 特性阻抗,體現(xiàn)在PCB板上,主要是通過(guò)疊層、線寬、線距。在PCB版圖布局完成以后,我們要對(duì)PCB板進(jìn)行層疊設(shè)計(jì)。

2020-09-19 10:47:33 10061

10061

: 一、單面 PCB 板和雙面 PCB 板的疊層 對(duì)于兩層板來(lái)說(shuō),由于板層數(shù)量少,已經(jīng)不存在疊層的問(wèn)題。控制 EMI 輻射主要從布線和布局來(lái)考慮; 單層板和雙層板的電磁兼容問(wèn)題越來(lái)越突出。造成這種現(xiàn)象的主要原因就是因是信號(hào)回路面積過(guò)大,不僅產(chǎn)生了較

2020-10-30 14:13:20 3412

3412 PCB 線路板疊層設(shè)計(jì)要注意哪些問(wèn)題呢?下面就讓專業(yè)工程師來(lái)告訴你。 做疊層設(shè)計(jì)時(shí),一定要遵從兩個(gè)規(guī)矩: 1. 每個(gè)走線層都必須有一個(gè)鄰近的參考層(電源或地層); 2. 鄰近的主電源層和地層要保持

2022-12-08 10:27:50 1595

1595 、單面 PCB 板和雙面 PCB 板的疊層 對(duì)于兩層板來(lái)說(shuō),由于板層數(shù)量少,已經(jīng)不存在疊層的問(wèn)題。控制 EMI 輻射主要從布線和布局來(lái)考慮; 單層板和雙層板的電磁兼容問(wèn)題越來(lái)越突出。造成這種現(xiàn)象的主要原因就是因是信號(hào)回路面積過(guò)大,不僅產(chǎn)生了較強(qiáng)的電

2020-10-30 15:09:22 1768

1768 的疊層操作方法我們都已經(jīng)懂了,無(wú)非就是看長(zhǎng)度吃飯。長(zhǎng)度決定我們要的板材級(jí)別,然后PP盡量選好的,也就是盡量不要選單張106或者1080(不要再問(wèn)高速先生為什么了哈,我們會(huì)生氣的)。然后選好PP/core的厚度之后就把對(duì)應(yīng)阻抗的線寬/線距算出來(lái),

2021-03-26 11:48:20 4557

4557 射頻板設(shè)計(jì)PCB疊層時(shí),推薦使用四層板結(jié)構(gòu),層設(shè)置架構(gòu)如下 【Top layer】射頻IC和元件、射頻傳輸線、天線、去耦電容和其他信號(hào)線, 【Layer 2】地平面 【Layer 3】電源平面

2021-03-05 11:03:39 4474

4474 如今,電子產(chǎn)品日益緊湊的趨勢(shì)要求多層印刷電路板的三維設(shè)計(jì)。但是,層堆疊提出了與此設(shè)計(jì)觀點(diǎn)相關(guān)的新問(wèn)題。其中一個(gè)問(wèn)題就是為項(xiàng)目獲取高質(zhì)量的疊層構(gòu)建。 隨著生產(chǎn)越來(lái)越多的由多層組成的復(fù)雜印刷電路,PCB

2020-11-03 10:33:28 5559

5559 八層板通常使用下面三種疊層方式 。 第一種疊層方式: 第一層:元件面、微帶走線層? 第二層:內(nèi)部微帶走線層,較好

2020-12-03 10:33:18 8178

8178 為了很好地對(duì)PCB進(jìn)行阻抗控制,首先要了解PCB的結(jié)構(gòu)。

2021-03-22 14:30:38 0

0 電路板的疊層設(shè)計(jì)是對(duì)PCB的整個(gè)系統(tǒng)設(shè)計(jì)的基礎(chǔ),疊層設(shè)計(jì)若有缺陷,將最終影響到整機(jī)的EMC性能。疊層設(shè)計(jì)是一個(gè)復(fù)雜的,嚴(yán)謹(jǐn)過(guò)程,當(dāng)然,設(shè)計(jì)開(kāi)發(fā),沒(méi)必要從零開(kāi)始經(jīng)過(guò)一系列的復(fù)雜計(jì)算和仿真,來(lái)確定設(shè)計(jì)方案是否合適,僅需要總結(jié)前人的經(jīng)驗(yàn),選擇合適系統(tǒng)的疊層方案。

2021-11-07 10:51:03 73

73 PCB設(shè)計(jì)時(shí)線寬是多少呢?小北帶你利用SI9000在計(jì)算阻抗,及12層PCB板的疊層結(jié)構(gòu)

2022-05-29 22:10:46 41966

41966

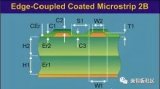

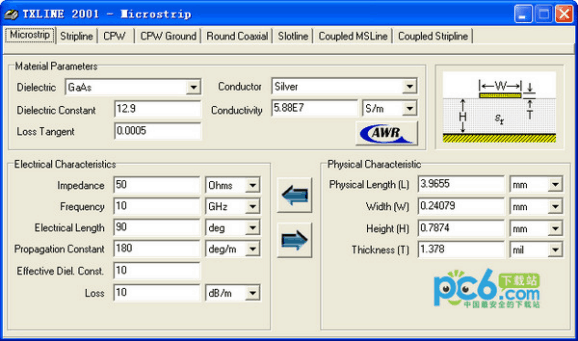

在 STM32 無(wú)線系列產(chǎn)品的 PCB 設(shè)計(jì)中,需要對(duì)射頻部分電路進(jìn)行阻抗控制,良好的阻抗控制可以減少信號(hào)衰減、反射和 EMC 輻射。本篇 LAT 主要介紹印制電路板(PCB)上射頻走線阻抗仿真計(jì)算

2022-06-16 16:36:21 8874

8874 選擇板層、板厚、內(nèi)層銅厚、阻抗層、參考層并輸入阻抗值、線距(差分阻抗)、線到銅的距離(共面阻抗),點(diǎn)計(jì)算,可自動(dòng)計(jì)算出線寬及疊構(gòu)方案。

2022-09-16 09:23:08 4038

4038 大家在進(jìn)行PCB設(shè)計(jì)的時(shí)候都是需要對(duì)我們的板子選擇疊層方案的,一個(gè)好的層疊方案能使我們的信號(hào)質(zhì)量變好,板子性能也會(huì)更穩(wěn)定等等,大家可能或多或少的接觸過(guò)多層板,也就是兩層往上的板子,那么大家在做六層板

2022-12-15 07:40:07 2508

2508 決于選擇的PCB疊層結(jié)構(gòu)。 由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結(jié)構(gòu)必須能實(shí)現(xiàn)板上的所有阻抗需求,包括內(nèi)層和外層、單端和差分線等。 PCB疊層設(shè)計(jì) “ ?層的定義設(shè)計(jì)原則? 1、主芯片相臨層

2023-07-19 07:45:02 1806

1806 在設(shè)計(jì)2層PCB時(shí),實(shí)際上不需要考慮PCB在工廠的結(jié)構(gòu)問(wèn)題。但是,當(dāng)電路板上的層數(shù)為四層或更多時(shí),PCB的堆疊是一個(gè)重要因素。

2023-07-19 16:19:13 3407

3407

由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結(jié)構(gòu)必須能實(shí)現(xiàn)板上的所有阻抗需求,包括內(nèi)層和外層、單端和差分線等。

2023-07-20 09:20:21 1350

1350

決于選擇的PCB疊層結(jié)構(gòu)。 由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結(jié)構(gòu)必須能實(shí)現(xiàn)板上的所有阻抗需求,包括內(nèi)層和外層、單端和差分線等。 PCB疊層設(shè)計(jì) “ ?層的定義設(shè)計(jì)原則? 1、主芯片相臨層

2023-07-27 18:15:06 1307

1307

決于選擇的PCB疊層結(jié)構(gòu)。 由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結(jié)構(gòu)必須能實(shí)現(xiàn)板上的所有阻抗需求,包括內(nèi)層和外層、單端和差分線等。 PCB疊層設(shè)計(jì) “ 層的定義設(shè)計(jì)原則 1、主芯片相臨層為地

2023-07-31 10:15:02 1374

1374

決于選擇的PCB疊層結(jié)構(gòu)。由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結(jié)構(gòu)必須能實(shí)現(xiàn)板上的所有阻抗需求,包括內(nèi)層和外層、單端和差分線等。 一、PCB疊層設(shè)計(jì) 層的定義設(shè)計(jì)原則: 1)主芯片相臨層

2023-08-01 07:45:01 3865

3865

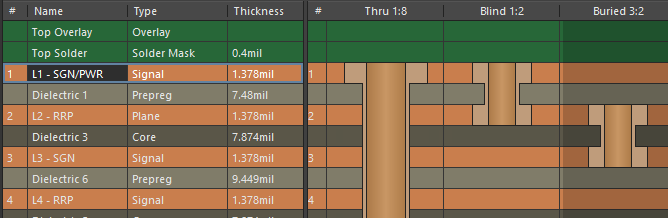

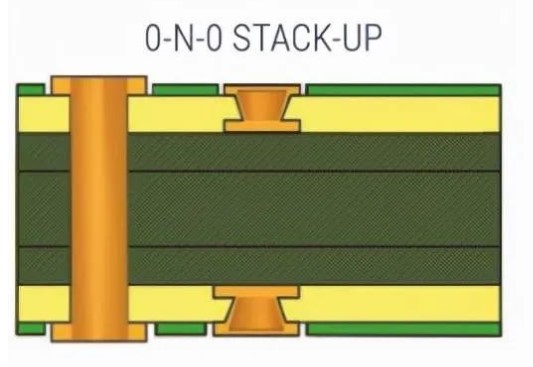

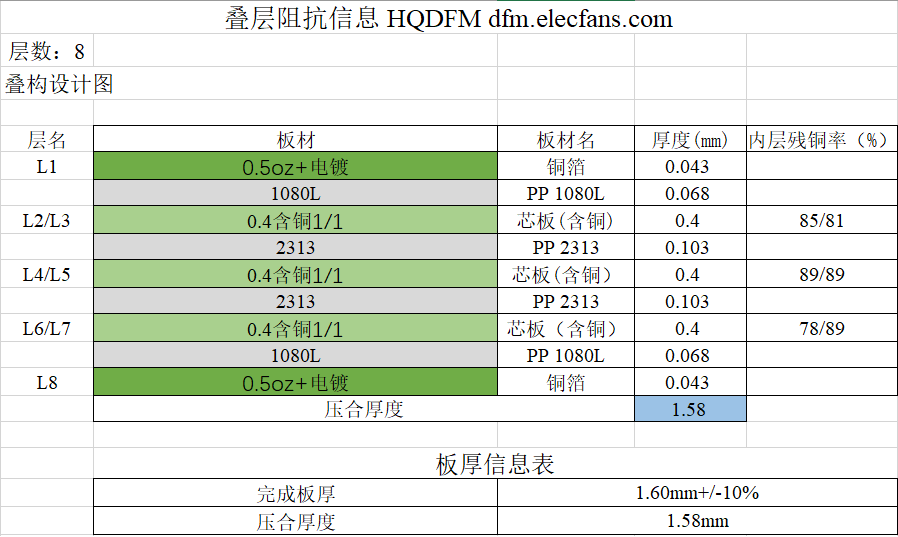

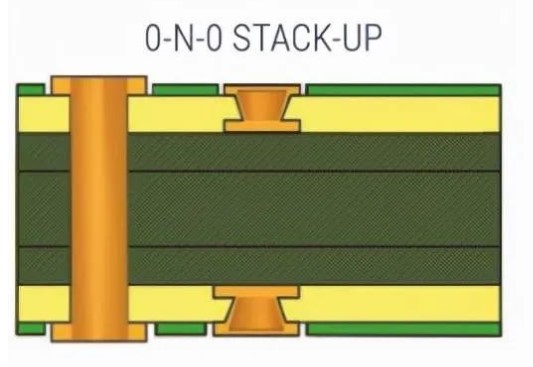

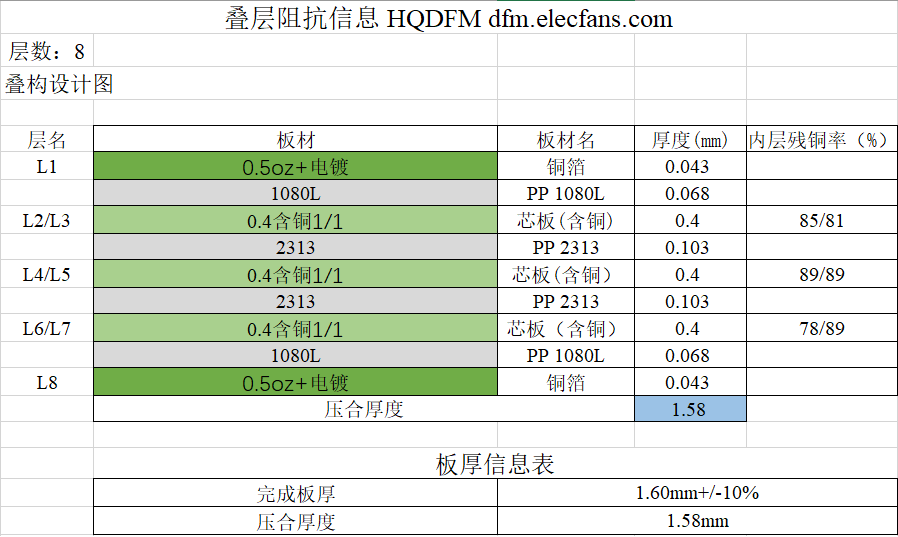

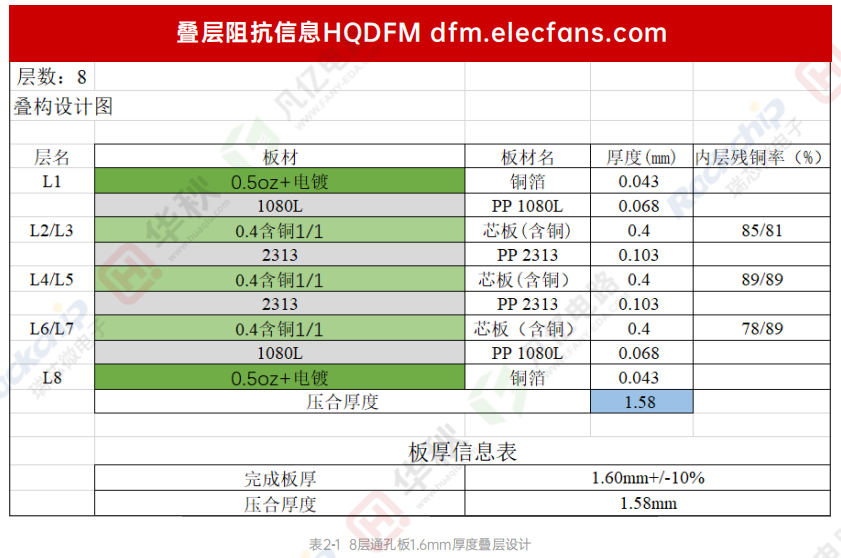

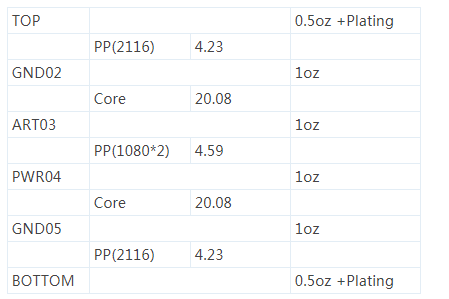

8層通孔板1.6mm厚度疊層與阻抗設(shè)計(jì) ? ? 在8層通孔板疊層設(shè)計(jì)中,頂層信號(hào) L1 的參考平面為 L2,底層信號(hào) L8 的參考平面為 L7。 建議層疊為

2023-08-21 17:16:58 4978

4978

只有使用正確的PCB疊層進(jìn)行構(gòu)建,高速設(shè)計(jì)才能成功運(yùn)行。您的疊層必須正確布置電源和接地層,為信號(hào)分配足夠的層,并且所有材料組和銅選擇均能以適當(dāng)?shù)囊?guī)模和成本制造。如果設(shè)計(jì)人員能夠獲得正確的疊層,那么在

2023-10-05 16:12:00 1785

1785

隨著高速電路的不斷涌現(xiàn),PCB板的復(fù)雜度也越來(lái)越高,為了避免電氣因素的干擾,信號(hào)層和電源層必須分離,所以就牽涉到多層PCB的設(shè)計(jì),即疊層結(jié)構(gòu)設(shè)計(jì)。——PCB疊層結(jié)構(gòu)設(shè)計(jì)10大通用原則——多層板常用的疊層結(jié)構(gòu)講解——多層板制造:如何做好疊層與阻抗匹配?

2022-09-30 12:03:38 114

114 高速PCB設(shè)計(jì)的疊層問(wèn)題

2022-12-30 09:22:17 43

43 今天畫了幾張多層PCB電路板內(nèi)部結(jié)構(gòu)圖,用立體圖形展示各種疊層結(jié)構(gòu)的PCB圖內(nèi)部架構(gòu)。

2024-01-02 10:10:54 2145

2145

良好的PCB疊層設(shè)計(jì)能夠?yàn)楦咚傩盘?hào)回流提供完整的路徑,縮小信號(hào)環(huán)路面積,降低信號(hào)耦合靜電放電噪聲干擾的能力。良好的PCB疊層設(shè)計(jì)可以降低參考地平面寄生電感,減小靜電放電時(shí)高頻電流流過(guò)地平面時(shí)所產(chǎn)生的地電位差。

2024-01-19 10:00:47 1006

1006

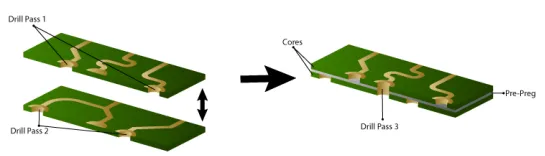

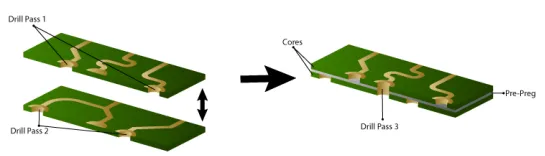

1.PCB疊層結(jié)構(gòu)與阻抗計(jì)算1.1.Core和PPPCB由Core和Prepreg(半固化片)組成。Core是覆銅板(通常是FR4—玻璃纖維&環(huán)氧基樹(shù)脂),Core的上下表面之間填充的是固態(tài)

2024-01-25 17:15:52 22863

22863

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論