為了減少在高速信號傳輸過程中的反射現象,必須在信號源、接收端以及傳輸線上保持阻抗的匹配。單端信號線的具體阻抗取決于它的線寬尺寸以及與參考平面之間的相對位置。特定阻抗要求的差分對間的線寬/線距則取決于選擇的PCB疊層結構。

由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結構必須能實現板上的所有阻抗需求,包括內層和外層、單端和差分線等。

PCB疊層設計

“

層的定義設計原則

1、主芯片相臨層為地平面,提供器件面布線參考平面;

2、所有信號層盡可能與地平面相鄰;

3、盡量避免兩信號層直接相鄰;

4、主電源盡可能與其對應地相鄰;

5、原則上應該采用對稱結構設計,對稱的含義包括:介質層厚度及種類、銅箔厚度、圖形分布類型(大銅箔層、線路層)的對稱。

“

PCB的層定義推薦方案

具體的PCB層設置時,要對以上原則進行靈活掌握,根據實際的需求,確定層的排布,切忌生搬硬套。以下給出常見的層排布推薦方案,供參考。在層設置時,若有相鄰布線層,可通過增大相鄰布線層的間距,來降低層間串擾。對于跨分割的情況,確保關鍵信號必須有相對完整的參考地平面或提供必要的橋接措施。

本文以RK3588方案的PCB設計為例,其10層1階,10層2階,8層通孔等PCB疊層結構的相關介紹,給客戶在疊層結構的選擇和評估上提供幫助。如果選擇其他類型的疊層結構,請根據PCB廠商給出的規格,重新計算阻抗。

本文使用華秋DFM軟件的阻抗計算功能,為大家展開相關疊層和阻抗設計的案例講解。這是一款國內免費的PCB可制造性和PCBA裝配分析軟件,幫助設計工程師在生產前檢查出可制造性問題,且能夠滿足工程師需要的多種使用場景。

華秋DFM軟件下載地址(復制到電腦瀏覽器打開):

https://dfm.elecfans.com/uploads/software/promoter/hqdfm_DFMGZH.zip

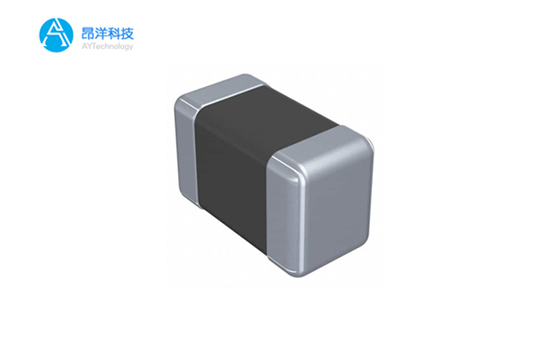

8層通孔板1.6mm厚度疊層設計

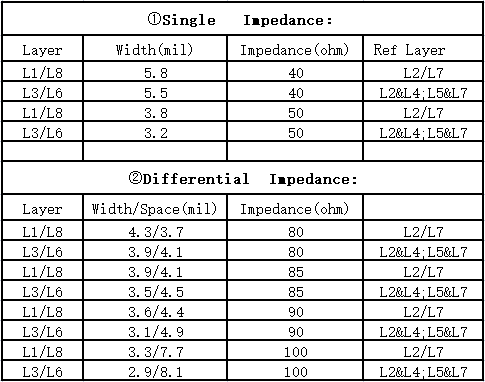

在8層通孔板疊層設計中,頂層信號L1的參考平面為L2,底層信號L8的參考平面為L7。建議層疊為TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基銅厚度建議全部采用 1oZ,厚度為1.6mm,其疊層設計如下圖所示。

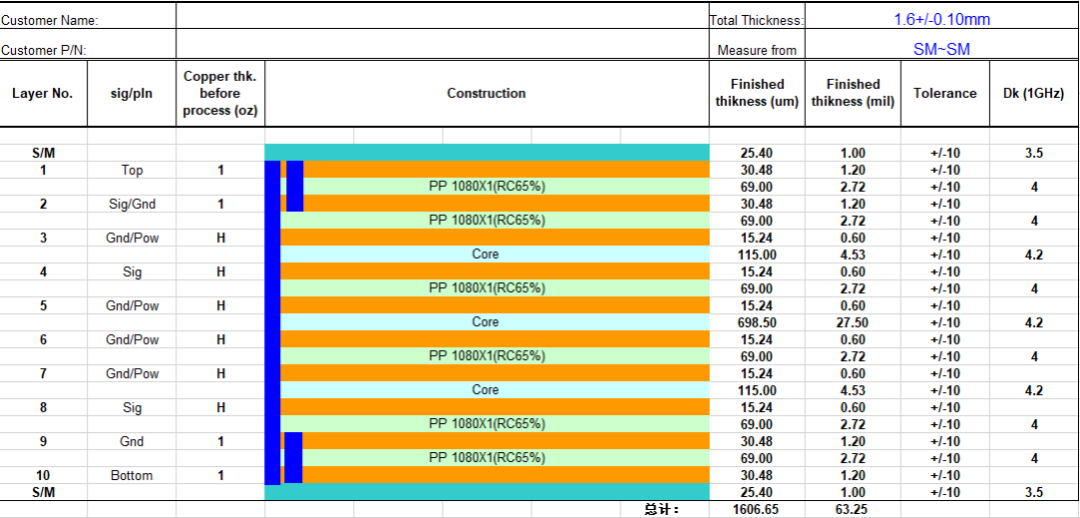

8層通孔板1.6mm厚度阻抗設計

“

外層單端50歐姆阻抗設計

使用華秋DFM工具,選擇外層單端阻抗模型,輸入對應參數,計算出對應線寬為3.8mil,L1與L8層是對稱設計,故L1層與L8層50歐姆單端走線為3.8mil,如下圖所示。

“

外層差分100歐姆阻抗設計

使用華秋DFM工具,選擇外層單端阻抗模型,輸入對應參數,計算出對應線寬/間距為3.3/7.7mil,L1與L8層是對稱設計,故L1層與L8層100歐姆差分走線為3.3/7.7mil,如下圖所示。

“

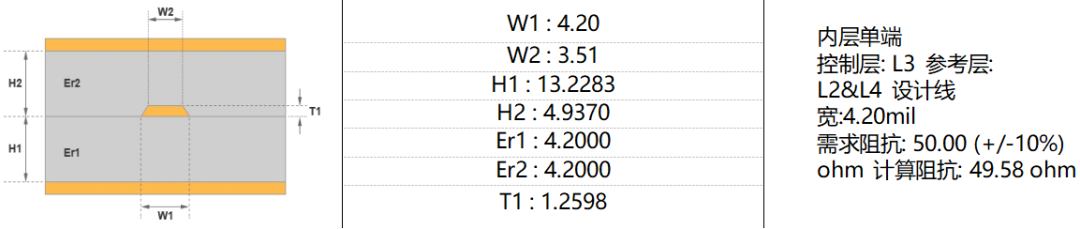

內層單端50歐姆阻抗設計

使用華秋DFM工具,選擇外層單端阻抗模型,輸入對應參數,計算出對應線寬為4.2mil,L3與L6層是對稱設計,故L3層與L6層50歐姆單端走線為4.2mil,如下圖所示。

“

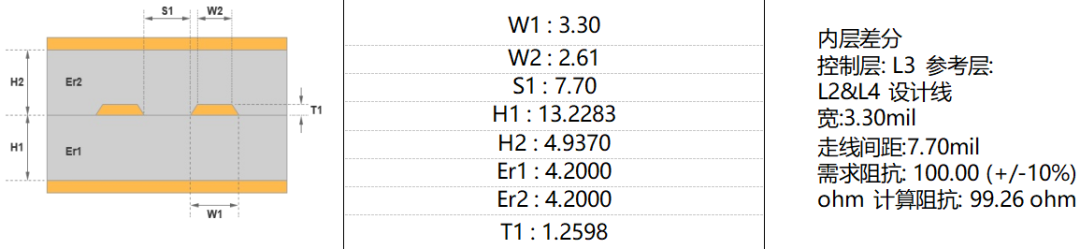

內層差分100歐姆阻抗設計

使用華秋DFM工具,選擇外層單端阻抗模型,輸入對應參數,計算出對應線寬/間距為3.3/7.7mil,L3與L6層是對稱設計,故L3層與L6層100歐姆差分走線為3.3/7.7mil,如下圖所示。

“

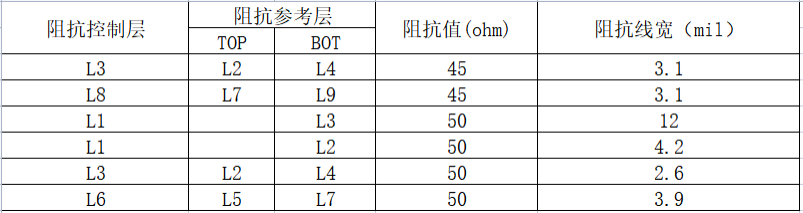

總體阻抗走線線寬

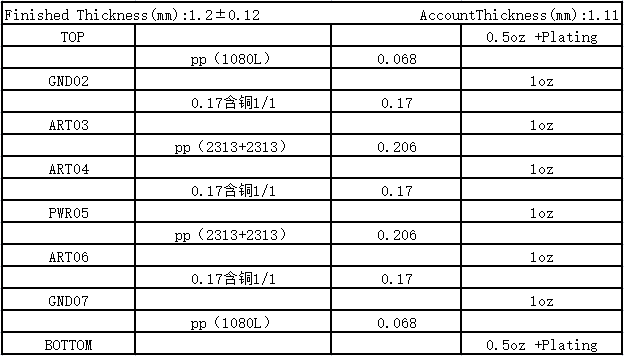

8層通孔板1.2mm厚度疊層設計

在8層通孔板疊層設計中,頂層信號L1的參考平面為L2,底層信號L8的參考平面為L7。建議層疊為TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基銅厚度建議全部采用 1oZ,厚度為1.2mm,詳細的疊層設計如下表所示。

8層通孔板1.2mm厚度阻抗設計

按照疊層設計參數,使用華秋DFM軟件進行阻抗計算,計算方法與上述8層1.6MM通孔一致,不一一截圖,計算出的阻抗線寬線距如下表所示。

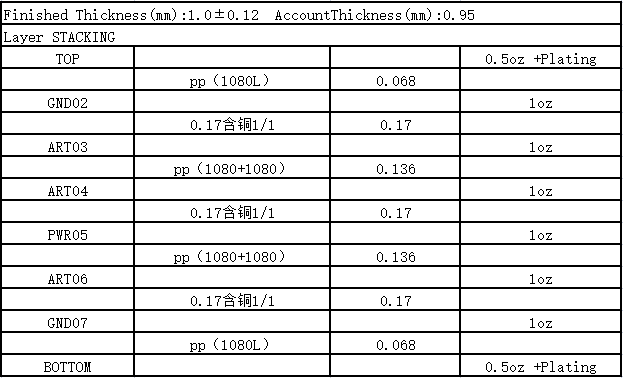

8層通孔板1.0mm厚度疊層設計

在8層通孔板疊層設計中,頂層信號L1的參考平面為L2,底層信號L8的參考平面為L7。建議層疊為TOP-Gnd-Signal-Power-Gnd-Signal-Gnd-Bottom,基銅厚度建議全部采用 1oZ,厚度為1.0mm,詳細的疊層設計如下表所示。

8層通孔板1.0mm厚度阻抗設計

按照疊層設計參數,使用華秋DFM軟件進行阻抗計算,計算方法與上述8層1.6MM通孔一致,不一一截圖,計算出的阻抗線寬線距如下表所示。

10層1階HDI板1.6mm厚度疊層設計

在10層1階板疊層設計中,頂層信號L1的參考平面為L2,底層信號L10的參考平面為L9。建議層疊為TOP-Signal/Gnd-Gnd/Power-Signal-Gnd/Power-Gnd/Power-Gnd/Power-Signal-Gnd-Bottom,其中L1,L2,L9,L10,建議采用1oZ,其它內層采用HoZ。如下圖所示為1.6mm板厚的參考疊層。

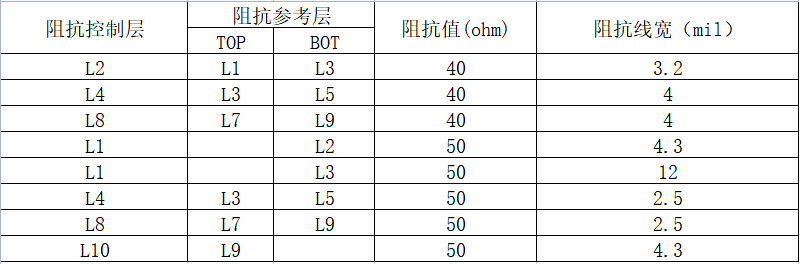

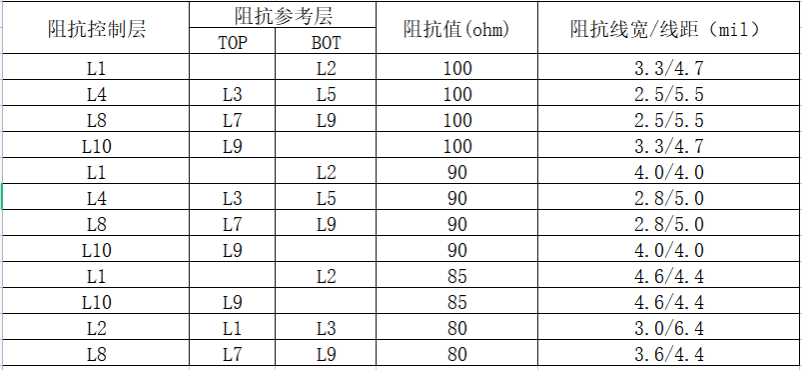

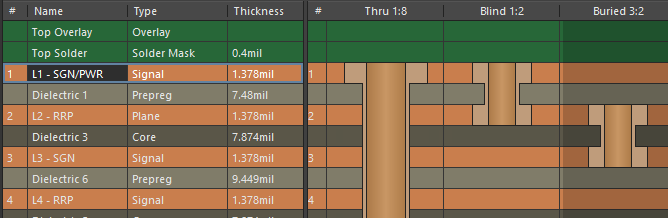

10層1階HDI板1.6mm厚度阻抗設計

按照疊層設計參數,使用華秋dfm軟件進行阻抗計算,計算方法與上述8層通孔一致,不一一截圖,計算出的單端阻抗線寬線距、差分阻抗線寬線距如下圖所示。

10層2階HDI板1.6mm厚度疊層設計

在10層2階板疊層設計中,頂層信號L1的參考平面為L2,底層信號L10的參考平面為L9。建議層疊為TOP-Gnd-Signal-Gnd-Power-Signal/Pow -Gnd-Signal-Gnd-Bottom,其中L1,L2,L3,L8,L9,L10,建議采用1oZ,其它內層采用HoZ。下圖為1.6mm板厚的參考疊層。

10層2階HDI板1.6mm厚度阻抗設計

按照疊層設計參數,使用華秋dfm軟件進行阻抗計算,計算方法與上述8層通孔一致,不一一截圖,計算出的單端阻抗線寬線距、差分阻抗線寬線距如下圖所示。

華秋DFM軟件下載地址(復制到電腦瀏覽器打開):

https://dfm.elecfans.com/uploads/software/promoter/hqdfm_hqsc.zip

專屬福利

上方鏈接下載還可享多層板首單立減50元

每月1次4層板免費打樣

并領取多張無門檻“元器件+打板+貼片”優惠券

原文標題:一文輕松搞定PCB疊層和阻抗設計

文章出處:【微信公眾號:華秋商城】歡迎添加關注!文章轉載請注明出處。

-

華秋商城

+關注

關注

8文章

119瀏覽量

8582

原文標題:一文輕松搞定PCB疊層和阻抗設計

文章出處:【微信號:華強芯城,微信公眾號:華秋商城】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PCB加工中的“流膠”到底是怎么影響阻抗的?

疊層固態電容:小型化封裝,釋放PCB更多空間

疊層固態電容的性能優勢

貼片電感代理-疊層電感的實際應用

一文輕松搞定PCB疊層和阻抗設計

一文輕松搞定PCB疊層和阻抗設計

評論