大家在進行PCB設計的時候都是需要對我們的板子選擇疊層方案的,一個好的層疊方案能使我們的信號質量變好,板子性能也會更穩定等等,大家可能或多或少的接觸過多層板,也就是兩層往上的板子,那么大家在做六層板的時候是否有聽過“假八層”的說法,“假八層”是什么意思呢?他到底是六層還是八層呢?我們在搞清楚這個問題之前需要先了解一下以下兩個知識點。

01 PCB的疊層知識

我們的PCB板通常是有芯板,銅箔,半固化片(又稱PP片)以及阻焊油組成的。

芯板:由銅箔、固態樹脂材料和玻璃纖維組成,制作PCB的基礎材料,具有一定的硬度及厚度,并且兩個表層都有銅箔。

半固化片(PP片):主要由樹脂和增強材料組成,增強材料又分為玻纖布、紙基、復合材料等幾種類型,而制作多層印制板所使用的半固化片(黏結片)大多是采用玻纖布做增強材料。

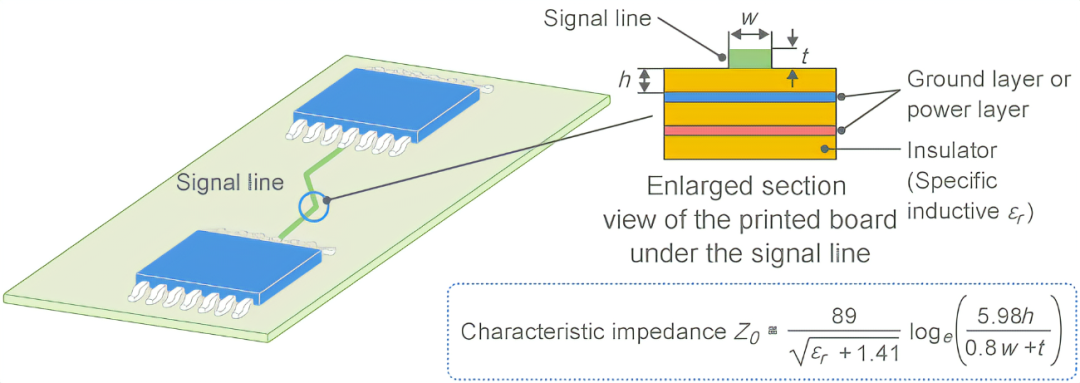

02 PCB的阻抗基礎知識

我們簡單了解完我們的板子組成之后,下面還需要了解一個知識點,那就是“阻抗”。隨著信號傳送速度迅猛的提高和高頻電路的廣泛應用,對印刷電路板也提出了更高的要求。印刷電路板提供的電路性能必須能夠使信號在傳輸過程中不發生反射現象,信號保持完整,降低傳輸損耗,起到匹配阻抗的作用,這樣才能得到完整、可靠、精確、無干擾、噪音的傳輸信號。阻抗匹配在高頻設計中是很重要的,阻抗匹配與否關系到信號的質量優劣 。而阻抗匹配的目的主要在于傳輸線上所有高頻的微波信號皆能到達負載點,不會有信號反射回源點。

通常影響我們阻抗的因素主要有板材,介電常數,銅厚,阻焊油,線寬等等,如果是差分線那么差分線之間的距離也會影響阻抗。一般介質厚度,差分線之間的間距和阻抗成正比關系,銅厚,線寬和阻抗成反比關系,一般阻焊油刷上去也會減小我們的阻抗值。

我們知道這些知識之后就可以進入主題了,什么是“假八層”:

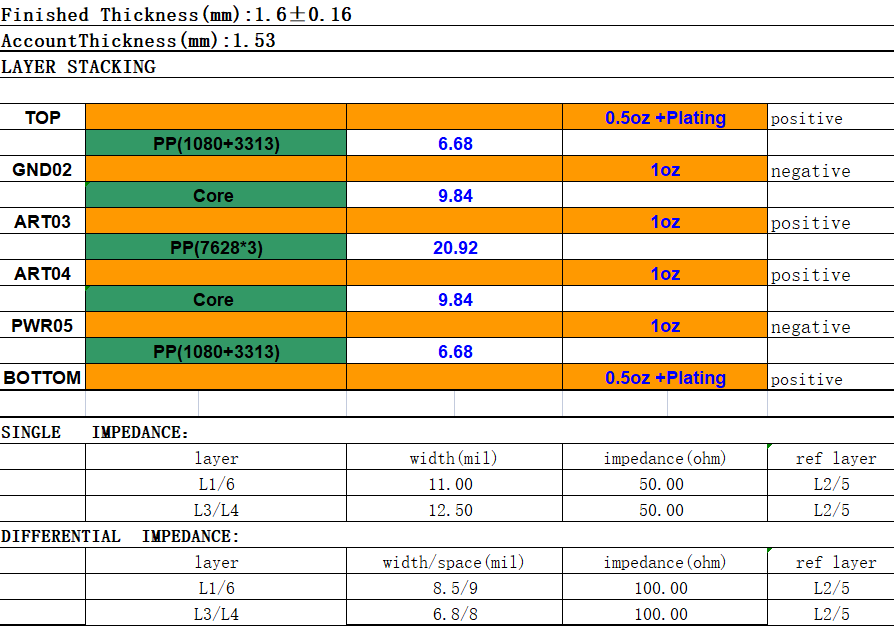

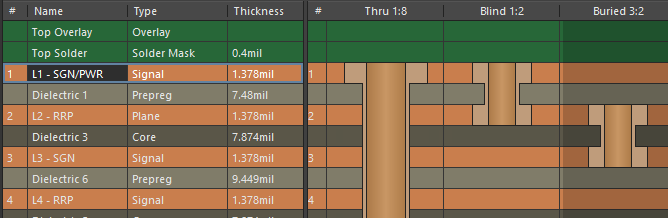

上圖所示是一個1.6mm板厚六層板的疊層,他內部有兩個芯板,一二層與五六層的pp片厚度為6.68mil,core厚度是9.84mil,芯板與芯板之間有三張pp片因此厚度達到了20.92mil,我們用此疊層設計PCB,如果我們板子上面有很多阻抗線的情況下這個時候我們經過計算會發現表底層需要控50om單端的情況下線寬是11mil,100om差分其線寬線距為8.5mil/9mil,而內層50om單端線寬達到了12.50mil,差分線寬線距為6.8mil/8mil,

這個線寬大小無疑增大了我們的設計難度,甚至很有可能設計不出來,所以我們可以通過更改疊層的方法實現降低線寬和滿足阻抗的要求,從上面介紹的阻抗知識當中我們了解到介質厚度和阻抗值成正比關系,所以我們如果要減小表層的線寬則可以通過減少表層與第二層之間的pp片數量以及選用更薄的pp片類型來減小介質厚度,此時介質厚度減小,阻抗值也會隨之小,那么這時可以減小線寬來達到我們的目標阻抗值,由于疊層的對稱性所以底層也是通過此方法減小線寬。

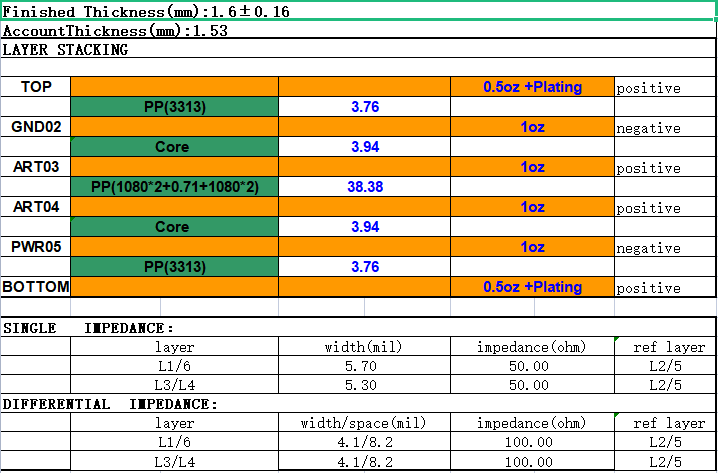

第三層是參考第二層和第五層的,其中第三層離第二層GND平面比較近,第五層離第三層比較遠,我們主要是參考第二層GND平面,受第二層的影響多一點,所以我們可以通過更改芯板的類型減小core的值,介質厚度減小了,第三層的相同線寬的情況下阻抗值越小,那么我們要達到目標阻抗值也是一樣減小線寬就可以了,這樣內層也實現了減小線寬和滿足阻抗的要求了,第四層也是如此,但是這個時候我們會發現,一二層和五六層之間的pp片都變薄了,芯板也變薄了,這個時候要達到目標板厚就只能在芯板與芯板之間增加厚度了,我們可以增加pp片的數量來達到增厚的目的,但是我們不能一直增加pp片的數量,一般最多只能用三張pp片,數量過多的情況下在板子壓合的時候板子會出現滑片的風險,我們上面已經介紹了芯板和pp片的組成 ,都含有樹脂和玻璃纖維,但是芯板的兩側有各有一塊銅箔,我們可以在芯板與芯板之間再加一塊“芯板”來滿足我們的板厚要求,但是這塊“芯板”我們是把兩側的銅箔是去掉的。新的疊層如下圖所示

(假八層)

這時我們發現表底層的50om單端線寬是5.7mil,100om差分線寬線距為4.1mil/8.2mil,內層50om阻抗單端線寬5.3mil,100om差分間距為4.1mil/8.2mil

這個線寬對常規設計來說一般都是可以滿足的,那么我們可以對比一下這兩個疊層,你會發現他們之間的差異就是core是變薄了,然后一二層和五六層的pp片也變薄了,芯板和芯板之間多了一個兩側不帶銅箔的芯板,那么一般這種疊層我們稱之為“假八層”。

了解完他們之間的不同后那么我們也可以總結一下他們之間的優缺點:

1、在需要阻抗的情況下,我們采用假八層的設計可以減小我們的設計線寬,從而滿足我們的設計要求。

2、在六層板疊層第三層和第四層走線的情況下采用假八層的設計可以減小第三層和第四層之間的串擾,因為第三層和第四層是相鄰層,都要走線的話,兩層之間太薄的情況下會產生串擾,影響信號質量,所以我們假八層的設計加大了這兩者的距離,串擾會相對來說會比較小,但是我們也需要注意的是,有相鄰布線層的情況下,我們要采用”垂直布線”,即走線一層走水平的,另一層走垂直的。

3、由于材料的增加從而導致我們的成本也會相應的提高,假八層是比六層貴的,但是比八層便宜。

以上就是本次要介紹的知識點了,相信大家在閱讀完成之后對什么是假八層也有一個基本概念了。

聲明: 本文凡億教育原創文章,轉載請注明來源!投稿/招聘/廣告/課程合作/資源置換請加微信:13237418207 ?分享點贊在看“三連”支持!

點擊“閱讀原文”查看更多干貨文章

?分享點贊在看“三連”支持!

點擊“閱讀原文”查看更多干貨文章

原文標題:PCB疊層當中的“假八層”是什么意思呢?

文章出處:【微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

-

pcb

+關注

關注

4404文章

23877瀏覽量

424241

原文標題:PCB疊層當中的“假八層”是什么意思呢?

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

西門子PCB疊層設計工具Z-planner Enterprise 2510版本的新增功能

疊層固態電容:小型化封裝,釋放PCB更多空間

晶科能源再度實現鈣鈦礦/TOPCon疊層電池轉換效率突破

疊層固態電容的性能優勢

貼片電感代理-疊層電感的實際應用

PCB疊層設計避坑指南

PCB疊層設計避坑指南

捷多邦專家解讀:如何選擇最優PCB疊層方案?

效率超30%!雙面鈣鈦礦/晶硅疊層電池的IBC光柵設計與性能優化

PCB疊層當中的“假八層”是什么意思呢?

PCB疊層當中的“假八層”是什么意思呢?

評論