信號完整性基本上是阻抗匹配的問題。而影響阻抗匹配的因素有信號源的架構和輸出阻抗(output impedance),走線的特性阻抗,負載端的特性,走線的拓樸(topology)架構等。解決的方式是靠端接(termination)與調整走線的拓樸。

2022-09-15 17:05:05 1949

1949 今天給大家分享的是PCB信號完整性、9個影響PCB信號完整性因素、提高PCB信號完整性規則。

2023-06-30 09:11:22 2397

2397

核心要點受控阻抗布線通過匹配走線阻抗來防止信號失真,從而保持信號完整性。高速PCB設計中,元件與走線的阻抗匹配至關重要。PCB材料的選擇(如低損耗層壓板)對減少信號衰減起關鍵作用。受控阻抗布線

2025-04-25 20:16:07 1101

1101

在您努力想要穩定板上的各種信號時, 信號完整性 問題會帶來一些麻煩。IBIS 模型是解決這些問題的一種簡單方法。您可以利用 IBIS 模型提取出一些重要的變量,用于進行信號完整性計

2012-05-08 09:45:59 2244

2244

、仿真軟件優劣等概況;概述后面諸講的各種基本概念。同時,簡要介紹相關技術資料、國內外最新科研成果、國內出版的原版譯著情況等。第二講 信號/互連線帶寬與時頻域阻抗 介紹信號完整性的研究對象——上升邊

2010-12-16 10:03:11

電阻的放置 高速PCB信號完整性仿真分析 信號完整性的電路板設計準則 基于信號完整性分析的高速數字PCB的設計方法 LVDS(低電壓差分信號)原理分析 阻抗匹配與史密斯(Smith)圓圖:基本原理

2008-12-25 09:49:59

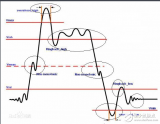

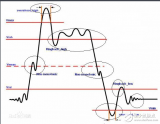

確定該電路具有較好的信號完整性。反之,當信號不能正常響應時,就出現了信號完整性問題。 高速PCB的信號完整性問題主要包括信號反射、串擾、信號延遲和時序錯誤。 · 反射:信號在傳輸線上傳輸時,當高速

2018-11-27 15:22:34

上導線的特性阻抗是電路設計的一個重要指標,特別是在高頻電路的PCB設計中,必須考慮導線的特性阻抗和器件或信號所要求的特性阻抗是否一致,是否匹配。因此,在PCB設計的可靠性設計中有兩個概念是必須注意

2018-09-18 15:50:04

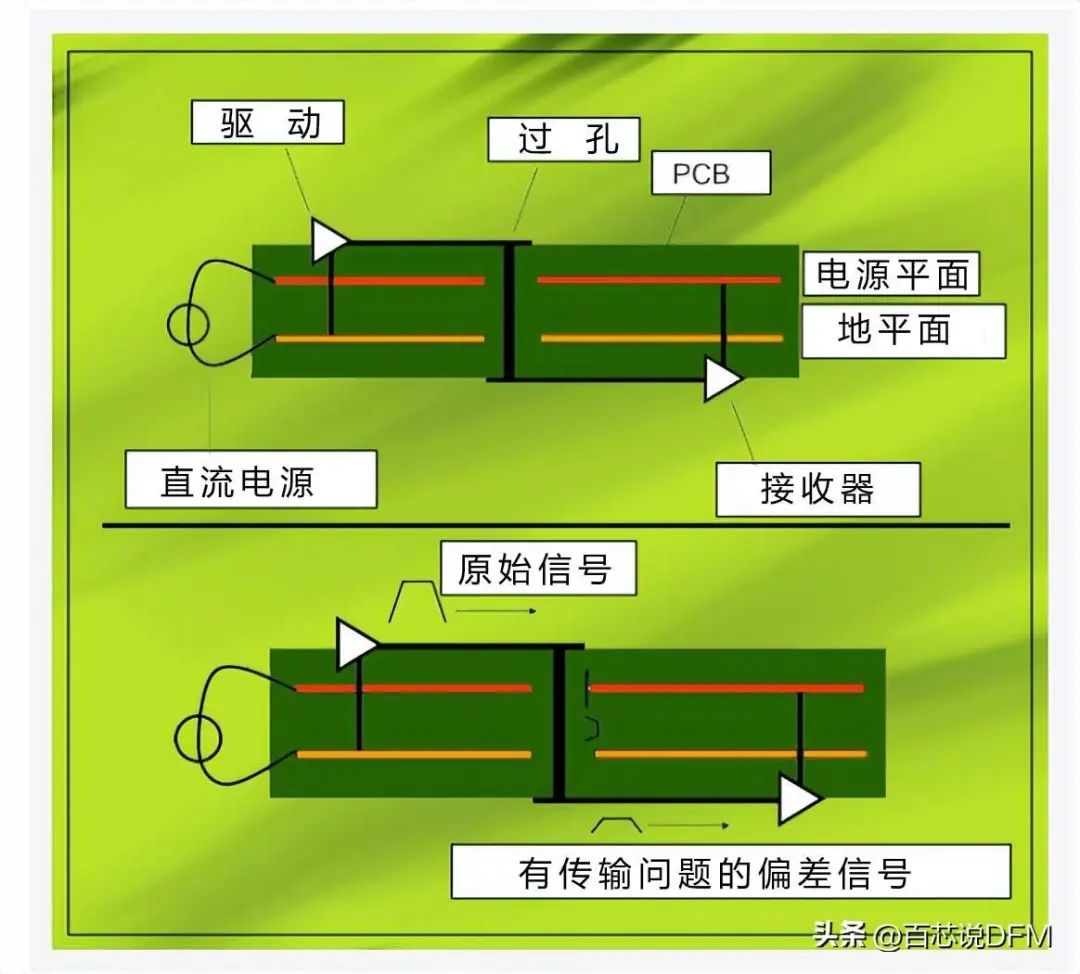

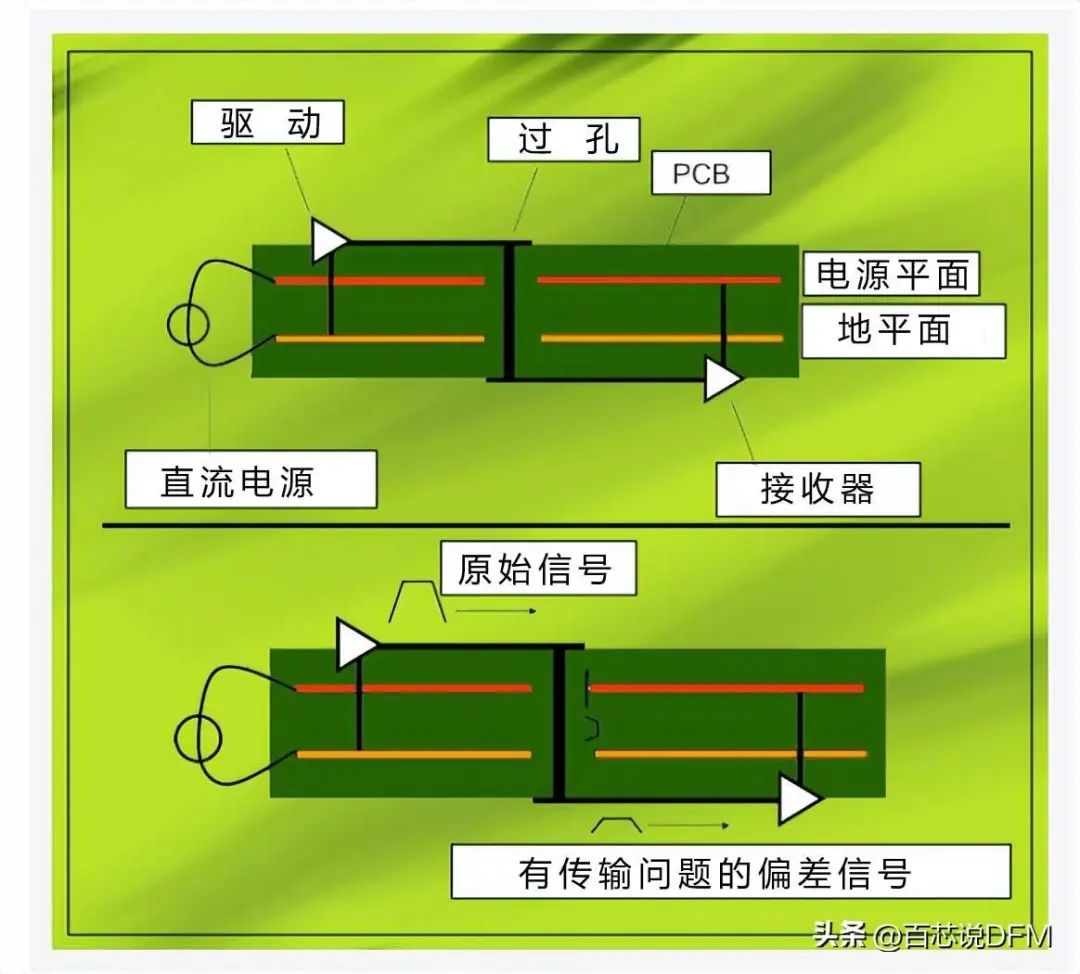

元件(Driver) 所發出的信號,將通過PCB傳輸線到達接收元件 (Receiver)。信號在印制板的信號線中傳輸時,其特性阻抗值Z0 必須 與頭尾元件的“電子阻抗”能夠匹配,信號中的“能量”才會

2018-09-14 16:21:15

本文具體分析了PCB板的特性阻抗和特性阻抗的控制辦法。

2021-04-25 07:27:35

在高速設計中,可控阻抗板和線路的特性阻抗問題困擾著許多中國工程師。本文通過簡單而且直觀的方法介紹了特性阻抗的基本性質、計算和測量方法。在高速設計中,可控阻抗板和線路的特性阻抗是最重要和最普遍

2017-10-12 13:19:56

在高速設計中,可控阻抗板和線路的特性阻抗問題困擾著許多中國工程師。深圳捷多邦科技有限公司的工程師通過本文簡單而且直觀的方法介紹了特性阻抗的基本性質、計算和測量方法。 在高速設計中,可控阻抗板

2018-09-12 15:38:58

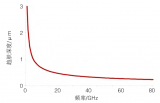

計算走線的阻抗特性。阻抗將會影響信號線上接收器中的波形形狀。最基本的信號完整性分析包括設置電路板疊層(包括適當的介電層厚度),以及查找正確的走線寬度,以實現一定的走線目標阻抗。與過孔相比,對走線進行建模

2019-06-17 10:23:53

,信號傳播路徑中阻抗發生變化的點,其電壓不再是原來傳輸的電壓。這種反射電壓會改變信號的波形,從而可能會引起信號完整性問題。這種感性的認識對研究信號完整性及設計電路板非常重要,必須在頭腦中建立起這個概念。

2019-05-31 07:48:31

工藝中用相反圖形來表示;通孔用來進行不同層之間的物理連接。目前的制造工藝中,芯片、封裝以及PCB板大多都是在類似結構上實現的。 版圖完整性設計的目標在于為系統提供足夠好的信號通路以及電源傳遞網絡。電流密度

2015-01-07 11:33:53

就變得重要了,通常將這種情況稱為高頻領域或高速領域。這些術語意味著在那些互連線對信號不再透明的產品或系統中,如果不小心就會出現一種或多種信號完整性問題。

從廣義上講,信號完整性指的是在高速產品中由互連線引起的所有問題。它主要研究互連線與數字償號的電壓電流波形相互作用時其電氣特性參數如何影響產品的性能。

2023-09-28 08:18:07

信號完整性的定義信號完整性包含哪些內容

2021-03-04 06:09:35

本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

2021-01-25 06:51:11

或高速脈沖信號的電壓),測量出反射回來的電壓變化,然后通過PC計算并輸出特性阻抗值Z0來。計算公式: Z0 =Z參V線/(V參-V線)5.3AOI對特性阻抗值的控制5.4由于導線制造的完整性(尺寸偏差

2018-02-08 08:29:08

很小的差異導致高速系統設計的失敗; 在電子產品向高密和高速電路設計方向發展的今天,解決一系列信號完整性的問題,成為當前每一個電子設計者所必須面對的問題。業界通常會采用在PCB制板前期,通過信號完整性

2015-12-28 22:25:04

機輸出線是51PIN的線,液晶模組的連接座是60PIN的,需要有個轉接板,把51PIN信號連接到60pin上,現在要做這個轉接板。在設計之前我有個問題不太確定,我知道51PIN傳輸線特性阻抗是100Ω,那

2018-12-16 16:55:27

`編輯推薦本書全面論述了信號完整性與電源完整性問題。主要講述信號完整性分析及物理設計概論,6類信號完整性問題的實質含義,物理互連設計對信號完整性的影響,電容、電感、電阻和電導的特性分析,求解信號

2017-08-08 18:03:31

`` 本帖最后由 lzr858585 于 2021-4-6 11:11 編輯

本書主要介紹信號完整性和物理設計概論,帶寬、電感和特性阻抗的實質,電阻電容電感和阻抗的相關分析。解決SI完整性問題的四個實用技術手段,物理互連設計對信號的影響,數學推導背后邏輯,改進信號完整性的推薦設計準則等。``

2021-04-06 11:10:15

基于優化多層印制板,改進信號完整性的設計,主要通過調整疊層設計中的各層導線寬度、基板厚度、填充層厚度和絕緣材料厚度,4個維度參數,從而改變信號傳輸路徑特性阻抗的方法,有具體應用實例。

2021-04-06 11:15:43

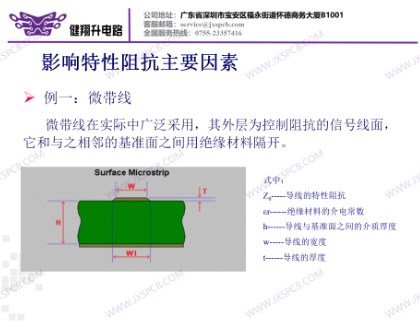

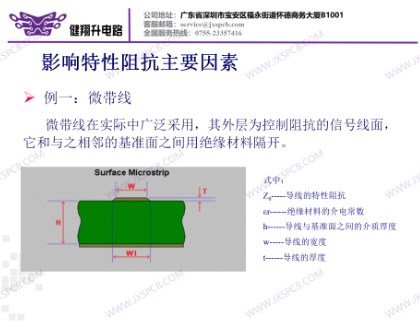

傳輸路徑上的特性阻抗發生變化,信號就會在阻抗不連續的結點產生反射。影響特性阻抗的因素有:介電常數、介質厚度、線寬、銅箔厚度。現象類比:運輸線的糟糕路況(類似傳輸線里的特性阻抗)會影響運輸車隊的速度,路

2019-06-03 08:14:49

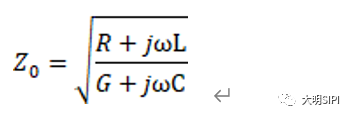

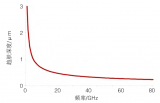

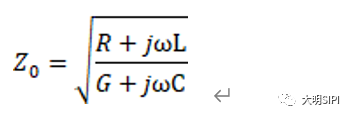

影響傳輸線電路中信號完整性的一個主要因素 如果沒有特殊說明,一般用特性阻抗來統稱傳輸線阻抗簡單的來說,傳輸線阻抗可以用上面的公式來說明,但如果往深里說,我們就要分析信號在傳輸線中的行為,Eric

2015-01-23 11:56:02

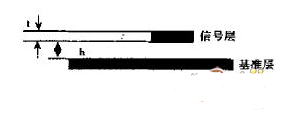

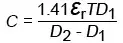

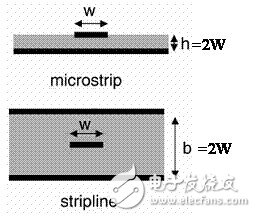

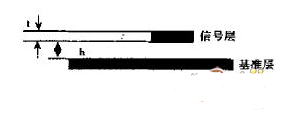

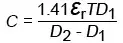

,信號線路和返回線路在幾何尺寸上不同高頻情況下單端傳輸線的特性阻抗(也就是通常所說的單端阻抗)為:其中:L為單位長度傳輸線的固有電感,C為單位長度傳輸線的固有電容。單端傳輸線特性阻抗與傳輸線尺寸、介質層

2009-09-28 14:48:47

何為信號完整性:信號完整性(Signal Integrity,簡稱SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一因素導致的,而是板級設計中多種因素共同引起的。當電路中信號能以要求的時序

2021-12-30 08:15:58

(differential impedance)的值, 此值是設計差分對的重要參數。 需要平行也是因為要保持差分阻抗的一致性。 若兩線忽遠忽近, 差分阻抗就會不一致, 就會影響信號完整性(signal

2019-06-03 07:19:49

本文是關于在印刷電路板 (PCB) 開發階段使用數字輸入/輸出緩沖信息規范 (IBIS) 模擬模型的文章。本文將介紹如何使用一個 IBIS 模型來提取一些重要的變量,用于信號完整性計算和確定 PCB

2011-09-13 09:28:36

在能量上的傳輸。3、特性阻抗控制(Z0 )上述此種“訊號”傳輸時所受到的阻力,另稱為“特性阻 抗”,代表符號為Z0。所以,PCB導線上單解決“通”、“斷”和“短路”的問題還 不夠,還要控制

2015-04-10 20:52:45

本文介紹了一種基于信號完整性計算機分析的高速數字信號PCB板的設計方法。在這種設計方法中,首先將對所有的高速數字信號建立起PCB板級的信號傳輸模型,然后通過對信號完整性的計算分析來尋找設計的解

2018-08-29 16:28:48

本文介紹了一種基于信號完整性計算機分析的高速數字信號PCB板的設計方法。在這種設計方法中,首先將對所有的高速數字信號建立起PCB板級的信號傳輸模型,然后通過對信號完整性的計算分析來尋找設計的解

2008-06-14 09:14:27

、電磁噪聲分析等,以避免設計的盲目性,降低設計成本。這里著重介紹如何利用Protel 99軟件對所設計之PCB 進行預先的信號分析,使得設計的電路更加切實可行。 信號完整性的有關概念 電磁干擾 電磁

2018-08-27 16:13:55

市場需求的推動作用,而電路板制造商可能是唯一的需方市場。確保信號完整性的PCB設計方法:通過總結影響信號完整性的因素,在PCB設計過程較好地確保信號完整性,可以從以下幾個方面來考慮。(1)電路設計上的考慮

2018-07-31 17:12:43

問題:如何解決PCB技術在高速設計中的特性阻抗問題?

2019-09-06 09:48:13

高速數字PCB設計信號完整性解決方法

2021-03-29 08:12:25

影響PCB特性阻抗的因素:介質厚度H、銅的厚度T、走線的寬度W、走線的間距、疊層選取的材質的介電常數Er、阻焊的厚度。 一般來說,介質厚度、線距越大阻抗值越大;介電常數、銅厚、線寬、阻焊厚度

2020-09-07 17:54:12

影響印刷電路板PCB的特性阻抗因素及對策摘要:本文給出了印刷電路板PCB特性阻抗的定義,分析了影響特性阻抗的因素及的構造,參數對特性阻抗精度的影響最后給出了一些對策。關鍵詞:印刷電路板, 特性阻抗,精度

2009-05-16 21:42:20

信號傳輸過程中不發生反射現象,信號保持完整,降低傳輸損耗,起到匹配阻抗的作用,這樣才能得到完整、可靠、精確,無干擾、噪音的傳輸信號。本文就實際中常用的表面微帶線結構多層板的特性阻抗控制的問題進行討論。1

2018-08-29 16:28:55

在高速設計中,可控阻抗板和線路的特性阻抗問題困擾著許多中國工程師。本文通過簡單而且直觀的方法介紹了特性阻抗的基本性質、計算和測量方法。 在高速設計中,可控阻抗板和線路的特性阻抗是最重要和最普遍

2012-06-02 10:08:56

有這樣一種錯誤認識,認為速率不高的PCB不用考慮信號完整性問題,可以隨便設計。盡管有時候PCB也會出問題,但并不認為是信號完整性的事。信號完整性和信號速率其實沒多大關系。舉一個例子,如果PCB板上有

2016-12-07 10:08:27

不是地,信號總是將最近的平面當作它的返回路徑,分析過孔引入的SSN。介紹導線空間延伸的概念。介紹輸入阻抗、瞬態阻抗、特性阻抗的不同用途. 第五講 反射及其消除:分析各種互連感性、容性突變下的多種反射

2010-11-09 14:21:09

在高速PCB電路板的設計和制造過程中,工程師需要從布線、元件設置等方面入手,以確保這一PCB板具有良好的信號傳輸完整性。在今天的文章中,我們將會為各位新人工程師們介紹PCB信號完整性設計中常

2018-11-27 09:57:50

高速信號的電源完整性分析在電路設計中,設計好一個高質量的高速PCB板,應該從信號完整性(SI——Signal Integrity)和電源完整性 (PI——Power Integrity )兩個方面來

2012-08-02 22:18:58

影響印刷電路板(PCB板)的特性阻抗因素及對策:本文給出了印刷電路板PCB特性阻抗的定義,分析了影響特性阻抗的因素及PCB的構造參數對特性阻抗精度的影響,最后給出了一些對

2009-03-25 15:39:37 0

0 本文介紹了一種基于信號完整性計算機分析的高速數字信號 PCB板的設計方法。在這種設計方法中,首先將對所有的高速數字信號建立起PCB板級的信號傳輸模型,然后通過對信號完

2009-04-25 16:49:13 37

37 針對高速數字電路印刷電路板的板級信號完整性, 分析了IBIS 模型在板級信號完整性分析中的作用。利用ADS 仿真軟件, 采用電磁仿真建模和電路瞬態仿真測試了某個實際電路版

2010-08-23 17:18:04 39

39 什么是特性阻抗,什么叫特性阻抗

特征阻抗(也有人稱特性阻抗),它是在甚高頻、超高頻范圍內的概念,它不是

2009-05-24 23:05:57 5681

5681 千兆位設備PCB的信號完整性設計

本文主要討論在千兆位數據傳輸中需考慮的信號完整性設計問題,同時介紹應用PCB設計工具解

2009-11-18 08:59:52 630

630 本文結合特性阻抗板生產工藝要求,主要講述了在設計特性阻抗板時需要注意的參數,并對PolarSi8000 多電介質控制阻抗設計系統進行了簡單介紹。

2011-06-24 15:37:09 0

0 在高速設計中,可控阻抗板和線路的特性阻抗問題困擾著許多中國工程師。本文通過簡單而且直觀的方法介紹了特性阻抗的基本性質、計算和測量方法。

2011-09-30 14:17:17 1602

1602 在pcb layout中必須要考慮SI差的信號完整性不是由某一因素導致的,而是由板級設計中多種因素共同引起的

2011-11-21 13:57:34 7607

7607 在您努力想要穩定板上的各種信號時,信號完整性問題會帶來一些麻煩。IBIS 模型是解決這些問題的一種簡單方法。您可以利用 IBIS 模型提取出一些重要的變量,用于進行信號完整性計算

2012-01-14 12:58:55 1585

1585

本書全面論述了信號完整性問題。主要講述了信號完整性和物理設計概論,帶寬、電感和特性阻抗的實質含義,電阻、電容、電感和阻抗的相關分析,解決信號完整性問題的四個實用技術手段,物理互連設計對信號完整性

2015-11-10 17:36:24 0

0 影響印刷電路板(PCB)的特性阻抗因素及對策

2017-01-10 21:35:22 0

0 高速PCB電路板的基本理論和信號完整性設計

2017-09-18 09:20:22 25

25 信號完整性是指信號在傳輸路徑上的質量,由于路徑的特性對信號造成的失真。數字電路剛出現的時候,由于傳輸信號速率很低,在電路分析時采用低頻和直流的方法就可以。

2017-11-03 15:52:36 88456

88456

描述了高速PCB電路板信號完整性設計方法。 介紹了信號完整性基本理論, 重點討論了如何采用高速PCB設計方法保證高速數采模塊的信號完整性

2017-11-08 16:55:13 0

0 信號完整性(Signal Integrity Signal Integrity,簡稱SI SI)是指在信號線上的信號質量。差的信號完整性不是由某一單一 因素導致的,而是板級設計中多種因素共同

2017-11-16 13:24:51 0

0 基于信號完整性分析的PCB設計流程如圖所示。 主要包含以下步驟: 圖基于信號完整性分析的高速PCB設計流程 (1)因為整個設計流程是基于信號完整性分析的,所以在進行PCB設計之前,必須建立或獲取高速

2017-12-04 10:46:30 0

0 信號完整性是關系到電路板電氣性能的首要問題,主要影響電路的射頻應用和高速數字信號應用。與電路材料相關的一些特性能夠提高信號完整性。

2018-02-05 17:32:03 1598

1598 本文首先介紹了PCB信號完整性的問題,其次闡述了PCB信號完整性的步驟,最后介紹了如何確保PCB設計信號完整性的方法。

2018-05-23 15:08:32 11792

11792 本文著重介紹了特性阻抗的概念,另外還介紹了特性阻抗類比說明和特性阻抗測量方法及測量單位。

2018-08-21 18:01:25 12582

12582 在基于信號完整性計算機分析的PCB設計方法中,最為核心的部分就是pcb板級信號完整性模型的建立,這是與傳統的設計方法的區別之處。SI模型的正確性將決定設計的正確性,而SI模型的可建立性則決定了這種設計方法的可行性。

2019-06-24 15:22:49 5816

5816 本文給出了印刷電路板PCB特性阻抗的定義分析了影響特性阻抗的因素及PCB的構造參數對特性阻抗精度的影響最后給出了一些對策。

2019-10-25 14:28:40 7

7 傳輸線造成的信號邊沿退化等問題。信號完整性問題不僅會造成電路功能錯誤,也會造成各種電磁兼容問題。在高速 PCB 設計過程中,為了能夠使 PCB 一次設計成功的同時又能確保板級輻射發射不超標,板級信號完整性仿真分析已經成為一種重要

2019-11-04 08:00:00 0

0 信號完整性 涉及高速 PCB 布局指南的主要問題是信號完整性。長期以來, PCB 單元的信號完整性損失一直是一個令人擔憂的問題,因此在制造,銷售或購買印刷電路板時,請務必牢記信號完整性 PCB 布局

2020-09-21 21:22:51 3169

3169 )要充分考慮接插組裝電子元器件,接插后充分考慮導電率能和信號傳送性能等問題,因此便會規定特性阻抗越低越好,電阻要小于每平方厘米1TImes;10-6以下。 2、PCB線路板在生產制造過程中要歷經沉銅、電鍍錫(或化學鍍,或熱噴錫)、接插件焊錫等生產

2020-11-24 14:03:41 2775

2775 不能簡單地視為電連接的函數,而是必須仔細考慮過孔對信號完整性的影響。通孔表現為傳輸線上阻抗不連續的斷點,導致信號反射。然而,通孔帶來的問題更多地集中在寄生電容和寄生電感上。過孔寄生電容對電路的影響主要是延長信號的上升時間并降低電

2020-09-27 22:16:52 3628

3628 在PCB板上的布局、高速信號線的布線等因素,都會引起信號完整性的問題,對于PCB布局來說,信號完整性需要提供不影響信號時序或電壓的電路板布局,而對電路布線來說,信號完整性則要求提供端接元件、布局策略和布線信息。 PCB上信號速度高、端接元件的布局不正確或高

2022-11-17 11:46:28 1645

1645 在 PCB 設計階段要注意阻抗控制,這一點很重要。阻抗控制涉及為 PCB 上的走線和傳輸線指定所需的阻抗。這對于高速信號尤其重要,并且可能會受到您的影響。基材,銅線寬度和布線。即使在布置好電路板并

2020-10-09 21:12:57 2063

2063 地視為電連接的函數,而是必須仔細考慮過孔對信號完整性的影響。通孔表現為傳輸線上阻抗不連續的斷點,導致信號反射。 然而,通孔帶來的問題更多地集中在寄生電容和寄生電感上。過孔寄生電容對電路的影響主要是延長信號的上升時間并降低電路

2020-10-25 09:34:10 3595

3595 地視為電連接的函數,而是必須仔細考慮過孔對信號完整性的影響。通孔表現為傳輸線上阻抗不連續的斷點,導致信號反射。 然而,通孔帶來的問題更多地集中在寄生電容和寄生電感上。過孔寄生電容對電路的影響主要是延長信號的上升時間并降低電路

2020-10-25 09:33:30 2388

2388 本文主要介紹信號完整性是什么,信號完整性包括哪些內容,什么時候需要注意信號完整性問題?

2021-01-20 14:22:53 2345

2345

PCB特性阻抗計算工具軟件下載

2021-06-22 09:40:50 200

200 高速電路信號完整性分析與設計 —阻抗控制

2022-02-10 16:36:42 0

0 本文首先介紹了PCB信號完整性的問題,其次闡述了PCB信號完整性的步驟,最后介紹了如何確保PCB設計信號完整性的方法。

2022-12-22 11:53:39 1449

1449 特性阻抗(Impedance) 什么是電纜的特性阻抗?傳輸線受導體的結構影響,而有一高頻信號的阻值,單位為Ohm。

2023-01-09 09:57:13 4508

4508 PCB產品的信號完整性由PCB原材料和PCB設計產品兩部分來提升。PCB材料的電性能可以通過測試介質層的介電常數、介質損耗以及導體銅箔粗糙度值來衡量;PCB產品的電性能主要通過測試阻抗和插入損耗(傳輸損耗

2023-04-27 10:32:55 2855

2855

信號完整性分析是基于傳輸線理論的,研究信號完整性必須從認識傳輸線開始,而傳輸線中最基本的概念就是阻抗和反射。

2023-06-14 15:40:58 11574

11574

印刷電路板提供的電路性能必須能夠使信號傳輸過程中不發生反射現象,信號保持完整,降低傳輸損耗,起到匹配阻抗的作用,這樣才能得到完整、可靠、,無干擾、噪音的傳輸信號。本文就實際中常用的表面微帶線結構多層板的特性阻抗控制的問題進行討論。

2023-08-17 14:19:44 1783

1783

pcb信號完整性詳解 隨著電子領域技術日新月異的發展,高速電路已經成為了電路設計的重要領域之一。在高速電路中,信號完整性顯得尤為重要。在設計PCB電路時,信號完整性是一個必須考慮的因素。那么

2023-09-08 11:46:58 2269

2269 通孔的阻抗控制對PCB信號完整性會觸發什么樣的影響?

2023-10-17 11:56:11 1312

1312

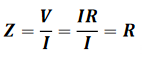

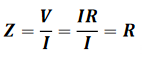

我們把阻抗定義為電壓和電流之比,通常用大寫字母Z表示。Z = V/I。在信號完整性扮演重要角色的高速數字系統中,信號是指變化的電壓或變化的電流。

2023-09-21 16:45:54 1627

1627

有許多種不同的類型,包括雙絞線、同軸電纜、光纖等。傳輸線的長度和特性阻抗對于傳輸信號的質量有著決定性的影響。 什么是信號完整性分析? 信號完整性分析是一種用于評估電路板或集成電路等系統中信號的傳輸和控制的技術。

2023-10-23 10:34:34 1559

1559 PCB電流與信號完整性設計

2022-12-30 09:20:34 51

51 影響印刷電路板(PCB)的特性阻抗因素及對策

2022-12-30 09:21:38 4

4 pcb板阻抗控制是指什么?pcb怎么做阻抗? PCB板阻抗控制是指在PCB(印刷電路板)設計和制造過程中,通過優化電氣特性和信號完整性,確保設計滿足特定的阻抗要求。在高速數字和模擬電路中,阻抗控制

2024-01-17 16:38:04 5037

5037 PCB特性阻抗-影響特性阻抗因素V3.0 圖文說明 ? ? ? ? ? 審核編輯 黃宇

2024-06-03 15:41:11 1089

1089

電子發燒友網站提供《信號完整性與電源完整性-差分對的特性.pdf》資料免費下載

2024-08-12 14:28:39 1

1 電子發燒友網站提供《高速PCB的信號完整性、電源完整性和電磁兼容性研究.pdf》資料免費下載

2024-09-19 17:37:43 1

1 高速PCB信號完整性設計與分析

2024-09-21 11:51:47 4

4 高速高密度PCB信號完整性與電源完整性研究

2024-09-25 14:43:20 5

5 完整性至關重要。首先是反射現象,當信號在傳輸線上傳播遇到阻抗不連續點時,就會發生反射。例如,信號從驅動芯片的輸出阻抗傳輸到傳輸線的特性阻抗,再到接收芯片的輸入阻抗,這些不同的阻抗可能導致信號部分能量反射回去,從而影響信號

2024-11-05 13:48:28 1078

1078 在高速電路設計和信號傳輸領域,特性阻抗(Characteristic Impedance)是一個至關重要的概念。它描述了信號在傳輸線上傳輸的行為和特性,對于確保信號完整性、減少信號反射和提高系統性能具有關鍵作用。本文將深入探討特性阻抗的定義、意義以及計算公式,為工程師提供全面的理解。

2025-01-29 14:28:00 6369

6369 ,作為影響信號傳輸質量的關鍵因素之一,是高質量電路板設計不可或缺的技術。 什么是PCB阻抗控制? PCB(Printed Circuit Board)阻抗控制,是指在電路板設計過程中,通過調節布線、材料等參數,控制傳輸線的特性阻抗,以保證信號的完整性。所謂特性阻抗,是

2025-04-18 09:07:47 823

823 本文要點PCB走線和IC走線中的阻抗控制主要著眼于預防反射。防止互連路徑上發生反射,可確保功率傳輸至負載,同時避免其他信號完整性問題。使用集成場求解器的PCB設計軟件可以評估阻抗匹配并提取互連網

2025-09-05 15:19:30 5017

5017

?。如果PCB上線條的厚度和寬度不變,并且走線和返回平面間距離不變,那么信號感受到的瞬態阻抗就不變,傳輸線是均勻的。對于均勻傳輸線,恒定的瞬態阻抗說明了傳輸線的特性,稱為特性阻抗。

?。如果PCB上線條的厚度和寬度不變,并且走線和返回平面間距離不變,那么信號感受到的瞬態阻抗就不變,傳輸線是均勻的。對于均勻傳輸線,恒定的瞬態阻抗說明了傳輸線的特性,稱為特性阻抗。 ?。

?。

電子發燒友App

電子發燒友App

評論