在高速PCB設計中,DDR模塊是絕對繞不過去的一關。無論你用的是DDR、DDR2還是DDR3,只要設計不規范,后果就是——信號反射、時序混亂、系統頻繁死機。

2025-04-29 13:51:03 2492

2492

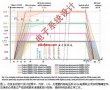

本文主要使用了Cadence公司的時域分析工具對DDR3設計進行量化分析,介紹了影響信號完整性的主要因素對DDR3進行時序分析,通過分析結果進行改進及優化設計,提升信號質量使其可靠性和安全性大大提高。##時序分析。##PCB設計。

2014-07-24 11:11:21 6350

6350

和?x16 配置中均可提供高達?2133Mbps 的數據傳輸速率,并可與1.5V DDR3實現100%兼容。目前,華邦的?DRAM 產品布局包括1Gb-4Gb DDR3、128Mb-2Gb DDR2

2022-04-20 16:04:03 3594

3594

導讀:DDR5協議發布已經有一段時間了,其中的變化還是比較大的,地址信號采取了ODT的端接形式,本篇文章為大家仿真一下DDR5地址信號。同時,我也推薦大家關注我在仿真秀原創的精品課《DDR3/4/5系列信號完整性仿真24講》,讓你清楚掌握DDR協議和仿真關鍵技術要點。

2022-12-01 10:24:03 2805

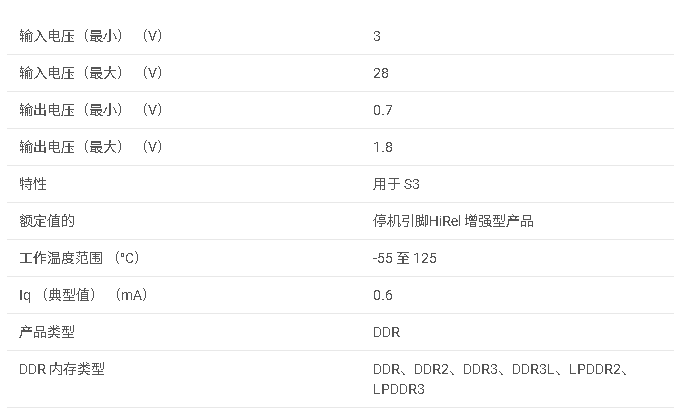

2805 DDR內存1代已經淡出市場,直接學習DDR3 SDRAM感覺有點跳躍;如下是DDR1、DDR2以及DDR3之間的對比。

2023-04-04 17:08:47 5108

5108

DDR5已經開始商用,但是有的產品還才開始使用DDR4。本文分享一些DDR4的測試內容。DDR4 和前代的 DDR3 相比, 它的速度大幅提升,最高可以達到 3200Mb/s,這樣高速的信號,對信號完整性的要求就更加嚴格,JESD79‐4 規范也對 DDR4 信號的測量提出了一些要求。

2024-01-08 09:18:24 4649

4649

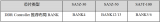

DDR內存控制器是一個高度集成的組件,支持多種DDR內存類型(DDR2、DDR3、DDR3L、LPDDR2),并通過精心設計的架構來優化內存訪問效率。

2025-03-05 13:47:40 3578

3578

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代產品,相較于DDR2,DDR3有更高的運行性能與更低的電壓。

2025-04-10 09:42:53 3932

3932

DDR2 DDR3 dimm接口封裝文件,金手指接口

2017-12-03 22:22:02

了極大的挑戰。 本文主要使用了Cadence公司的時域分析工具對DDR3設計進行量化分析,介紹了影響信號完整性的主要因素對DDR3進行時序分析,通過分析結果進行改進及優化設計,提升信號質量使其可靠性

2014-12-15 14:17:46

DDR3(double-data-rate three synchronous dynamic random accessmemory)是應用在計算機及電子產品領域的一種高帶寬并行數據總線。DDR3 在 DDR2

2019-05-22 08:36:26

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之處?

2021-03-12 06:22:08

[size=14.3999996185303px]我有個ARM的板子,DDR2和NAND的數據線是復用的,這樣PCB走線的時候,除了原來DDR2高速信號走線阻抗和等長以外,還需要特別注意什么嗎。NAND的線長是不是不算入DDR2總的線長中。

2016-10-10 17:09:28

DR2與DDR有哪些區別?DDR3與DDR2的區別是什么?

2021-10-26 06:15:07

大家好,我們可以在這里討論使用DDR2 / DDR3內存與FIFO(我的好奇心)的差異/優點/缺點。以上來自于谷歌翻譯以下為原文Hi All, Can we discuss here

2019-02-14 06:14:38

不同的標準外,還應該能夠提供動態的OCT和可變擺率,以此來管理信號的上升和下降時間。結論DDR3在未來即將超越DDR2的使用,高端FPGA提供的低成本、高效能、高密度和良好的信號完整性方案必須滿足JEDEC讀寫均衡要求。來源:EDN CHINA

2019-04-22 07:00:08

hyperlynx Sigrity信號完整性仿真之高速理論視頻教程Allegro 平板電腦DDR3 PCB設計視頻教程鏈接:https://pan.baidu.com/s/1P1elXupWFQ8KNh-u7QhCDg 密碼:fc5q

2018-08-25 15:54:28

SDRAM 相連的是BANK35 的 IO,DDR3 的硬件設計需要嚴格考慮信號完整性,我們在電路設計和 PCB設計的時候已經充分考慮了匹配電阻/終端電阻,走線阻抗控制,走線等長控制,保證DDR3 高速

2021-07-30 11:23:45

DDR3的頻率就是外頻的8倍 133=1066DDR2和DDR3的區別內存相對于DDR2內存,其實只是規格上的提高,并沒有真正的全面換代的新架構。DDR3接觸針腳數目同。DDR2皆為240pin。但是

2014-12-30 14:35:58

DDR3的頻率就是外頻的8倍 133=1066DDR2和DDR3的區別內存相對于DDR2內存,其實只是規格上的提高,并沒有真正的全面換代的新架構。DDR3接觸針腳數目同。DDR2皆為240pin。但是

2014-12-30 14:36:44

本文章主要涉及到對DDR2和DDR3在設計印制線路板(PCB)時,考慮信號完整性和電源完整性的設計事項,這些是具有相當大的挑戰性的。文章重點是討論在盡可能少的PCB層數,特別是4層板的情況下的相關

2019-07-30 07:00:00

并不會注意一些數字上的差異,如DDR3和DDr2,或許大多數人都會追求時髦選擇DDR3,但是你真的了解DDR2與DDR3的區別嗎?作為消費者,其實我們可主宰自己的命運,用知識的武器捍衛自己的選擇。下面

2011-12-13 11:29:47

本手冊以 DDR3 器件為例講解硬件設計方法,包括 FPGA I/O 分配、原理圖設計、電源網絡設計、PCB 走線、參考平面設計、仿真等,旨在協助用戶快速完成信號完整性好、低功耗、低噪聲的高速存儲

2022-09-29 06:15:25

如何進行兼顧電源影響的DDR4信號完整性仿真

2021-01-08 07:53:31

本人菜鳥初學者一個,求大神幫忙設計一個ddr2,ddr3供電電源,查了很多資料,自己也嘗試著設計了一下,但是發現問題很多,只能求助各位了,能幫我設計的本人必有酬謝,200元話費。。。。。 求會的大神直接聯系我qq447420097

2014-03-25 23:02:56

DDR,DDR2,DDR3,DDR4,LPDDR區別文所有權歸作者Aircity所有1什么是DDRDDR是Double Data Rate的縮寫,即“雙比特翻轉”。DDR是一種技術,中國大陸工程師

2021-09-14 09:04:30

針對DDR2-800和DDR3的PCB信號完整性設計

2012-12-29 19:12:39

信號完整性和時序分析的模式變化:簡單的接口分析經驗法則在分析現代高速接口(如DDR2、PCI Express和SATA-II)時非常不合適。隨著新興標準(如DDR3 和5-10 Gbps串行接口)逐漸普及,

2010-04-27 08:25:54 70

70 本文介紹了DDR3 SDRAM 的基本特點和主要操作時序,給出了一種基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的設計方法。詳述了控制器基本結構和設計思想,分析了各模塊功能與設計注意事項,并

2010-07-30 17:13:55 30

30 不只計算機存儲器系統一直需要更大、更快、功率更低、物理尺寸更小的存儲器,嵌入式系統應用也有類似的要求。本應用指南介紹了邏輯分析儀在檢驗DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 81

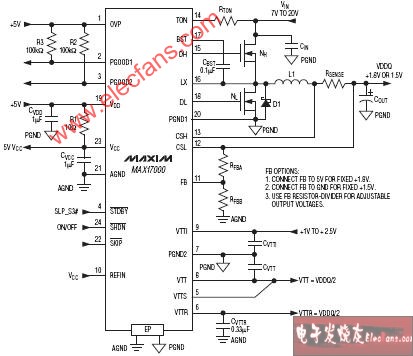

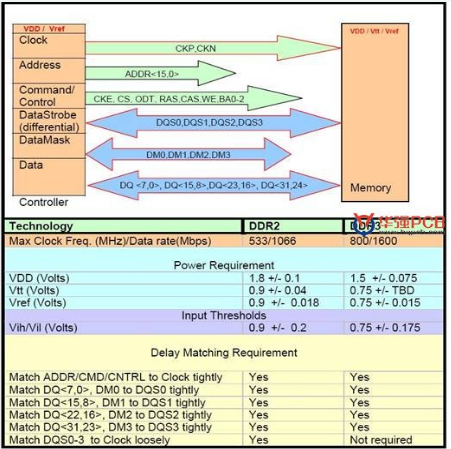

81 MAX17000 完備的DDR2和DDR3電源管理方案

MAX17000 概述

MAX17000脈寬調制

2009-01-22 12:59:21 1311

1311

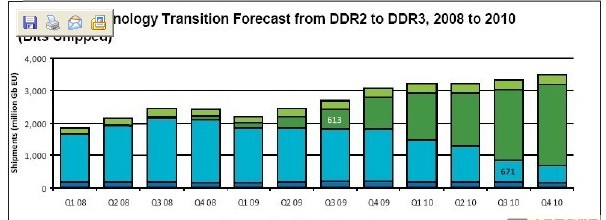

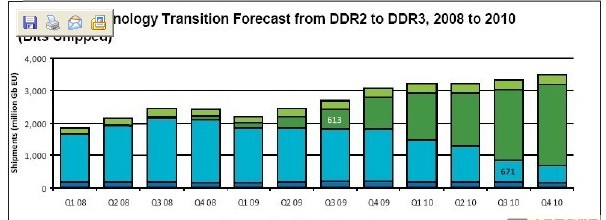

DDR3將是2010年最有前景市場

2009 年即將結束,DDR2 作為DRAM 市場之王的日子同樣所剩無幾。速度更快且功耗更低的DDR3 幾年前就已經問世,iSuppli 公司認為,它即將成為世

2009-12-15 10:28:14 1003

1003

什么是DDR2 SDRAM

DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設備工程聯合委員會)進行開發的新生代內存技

2009-12-17 11:17:59 935

935 DDR2的定義:

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設備工程聯合委員會)進行開發的新生代內存技術標準,它與上一代DDR內存技術標準最大的不

2009-12-17 16:26:19 1134

1134 DDR2傳輸標準

DDR2可以看作是DDR技術標準的一種升級和擴展:DDR的核心頻率與時鐘頻率相等,但數據頻率為時鐘頻率的兩倍,也就是說在一個時鐘周期內必須傳輸兩次

2009-12-25 14:12:57 563

563 臺灣DRAM廠商大舉轉產DDR3

2010年PC主流內存標準從DDR2向DDR3的轉換正在逐步成為現實。據臺灣媒體報道,由于下游廠商的DDR2訂單量近期出現急劇下滑,多家臺系DRAM芯片

2010-01-18 09:25:13 795

795 DDR2乏人問津 DRAM廠搶轉產能

DDR2和DDR3 1月上旬合約價走勢迥異,DDR2合約價大跌,DDR3卻大漲,凸顯世代交替已提前來臨,將加速DDR2需求急速降溫,快速轉移到DDR3身上,

2010-01-18 16:04:44 1317

1317 廠商采取搭售策略 挽回DDR2銷售頹勢

全球DRAM市場正加速進行世代交替,DDR3芯片因缺貨使得價格持續上漲,DDR2價格卻嚴重下跌,且累積庫存越來越多,近期韓系DRAM大

2010-01-20 09:24:18 912

912 DDR2芯片價格有望在下半年超過DDR3

報道,威剛主席Simon Chen今天表示,隨著DRAM制造商把重點放在DDR3芯片生產上,DDR2芯片的出貨量將開始減少,其價格有望在今年下半

2010-02-05 09:56:18 1177

1177 DDR2,DDR2是什么意思

DDR2(Double Data Rate 2) SDRAM是由JEDEC(電子設備工程聯合委員會)進行開發的新生代內存技術標準,它與上一代DDR內

2010-03-24 16:06:36 1644

1644 金士頓:DDR2/DDR3價格可能會繼續上漲

據報道,存儲大廠金士頓亞太地區副總裁Scott Chen近日表示,雖然1Gb DDR2/DDR3的芯片價格已經超過了3美元大關,

2010-04-09 09:11:05 904

904 Quamtum-SI DDR3仿真解析

Automated DDR3 Analysis

2010-04-29 09:00:11 4760

4760

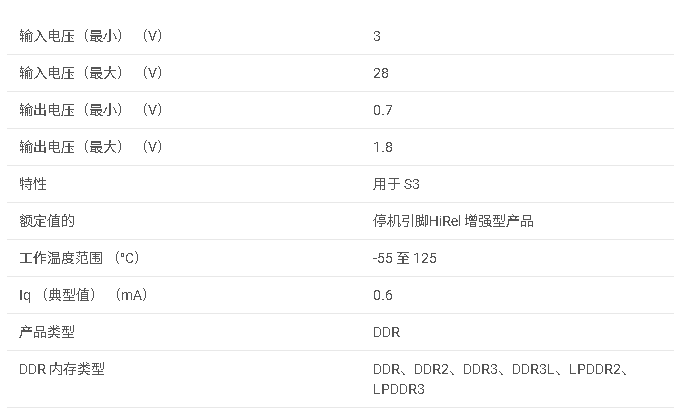

MAX17000A脈寬調制(PWM)控制器為筆記本電腦的DDR、DDR2、DDR3存儲器提供完整的電源方案。該器件集成了一路降壓控制器、一路可

2010-11-25 09:26:24 909

909

從那時起,采用DDR2、甚至最新的DDR3 SDRAM的新設計讓DDR SDRAM技術黯然失色。DDR內存主要以IC或模塊的形式出現。如今,DDR4雛形初現。但是在我們利用這些新技術前,設計人員必須了解如何

2011-07-11 11:17:14 6408

6408

本文章主要涉及到對 DDR2 和DDR3 在設計印制線路板(PCB)時,考慮信號完整性和電源完整性的設計事項,這些是具有相當大的挑戰性的。文章重點是討論在盡可能少的PCB 層數,特別是4 層板

2011-07-12 17:31:10 0

0 SDRAM, DDR, DDR2, DDR3 是RAM 技術發展的不同階段, 對于嵌入式系統來說, SDRAM 常用在低端, 對速率要求不高的場合, 而在DDR/DDR2/DDR3 中,目前基本上已經以DDR2 為主導,相信不久DDR3 將全面取代

2012-01-16 14:53:01 0

0 ) requirements of Printed Circuit Boards (PCBs) containing Double Data Rate 2 (DDR2) memories. The emphasis is on low layer count PCBs, typically 4-6

2012-01-16 16:31:19 259

259 總結了DDR和DDR2,DDR3三者的區別,對于初學者有很大的幫助

2015-11-10 17:05:37 36

36 針對DDR2-800和DDR3的PCB信號完整性設計

2016-02-23 11:37:23 0

0 Xilinx FPGA工程例子源碼:DDR2 Controller

2016-06-07 11:44:14 24

24 針對DDR2-800和DDR3的PCB信號完整性設計,要認證看

2016-12-16 21:23:41 0

0 本文首先列出了DDR2布線中面臨的困難,接著系統的講述了DDR2電路板設計的具體方法,最后給出個人對本次電路設計的一些思考。

2017-09-19 11:27:21 22

22 DDR4提供比DDR3/ DDR2更低的供電電壓1.2V以及更高的帶寬,DDR4的傳輸速率目前可達2133~3200MT/s。DDR4 新增了4 個Bank Group 數據組的設計,各個Bank

2017-11-07 10:48:51 55968

55968

雖然新一代電腦/智能手機用上了DDR4內存,但以往的產品大多還是用的DDR3內存,因此DDR3依舊是主流,DDR4今后將逐漸取代DDR3,成為新的主流,下面我們再來看看DDR4和DDR3內存都有哪些區別。相比上一代DDR3,新一代DDR4內存主要有以下幾項核心改變:

2017-11-08 15:42:23 32470

32470 SDRAM):DDR4提供比DDR3/ DDR2更低的供電電壓1.2V以及更高的帶寬,DDR4的傳輸速率目前可達2133~3200 MT/s。

2017-11-17 13:15:49 28010

28010 針對采用DDR3接口來設計的新一代閃存固態盤(SSD)需要完成與內存控制器進行通信與交互的特點,提出了基于現場可編程門陣列( FPGA)的DDR3協議解析邏輯方案。首先,介紹了DDR3內存工作原理

2017-12-05 09:34:44 10

10 本文章主要涉及到對DDR2和DDR3在設計印制線路板(PCB)時,考慮信號完整性和電源完整性的設計事項,這些是具有相當大的挑戰性的。文章重點是討論在盡可能少的PCB層數,特別是4層板的情況下的相關技術,其中一些設計方法在以前已經成熟的使用過。

2018-02-06 18:47:57 3382

3382

本節提供了DDR2接口作為一個PCB設計和制造的時間規范規范。設計規則限制PCB軌跡長度、PCB跟蹤歪斜、信號完整性、串擾,信號定時。這些規則,之后,在一個可靠的DDR2內存系統的結果而不需要對于一

2018-04-18 14:26:10 4

4 本節提供了DDR2接口作為一個PCB設計和制造的時間規范規范。設計規則限制PCB軌跡長度、PCB跟蹤歪斜、信號完整性、串擾,信號定時。這些規則,之后,在一個可靠的DDR2內存系統的結果而不需要

2018-04-18 16:45:17 8

8 性能和成本達到最佳收益的選擇,就是在布線方面,DDR3需要注意的問題比DDR2就略多。這里對AM335x關于DDR3的軟硬件設計資源以及這些注意事項做一個簡單匯總

2018-04-24 16:08:20 18

18 DDR3內存已經被廣泛地使用,專業的PCB設計工程師會不可避免地會使用它來設計電路板。本文為您提出了一些關于DDR3信號正確扇出和走線的建議,這些建議同樣也適用于高密度、緊湊型的電路板設計。

2018-06-16 07:17:00 10446

10446

突發長度,由于DDR3的預期為8bit,所以突發傳輸周期(BL,Burst Length)也固定位8,而對于DDR2和早期的DDR架構的系統,BL=4也是常用的,DDR3為此增加了一個

2018-06-21 09:20:54 16120

16120

針對 DDR2高速電路中存在的信號完整性問題進行了分析,提出了PCB設計要點。并以單個DDR2存儲器與控制器間的 PCB設計為例,對如何在減少仿真工作的情況下成功完成一個可用的設計進行了論述。

2019-03-04 08:00:00 0

0 DDR3內存與DDR2內存相似包含控制器和存儲器2個部分,都采用源同步時序,即選通信號(時鐘)不是獨立的時鐘源發送,而是由驅動芯片發送。它比DR2有更高的數據傳輸率,最高可達1866Mbps;DDR3還采用8位預取技術,明顯提高了存儲帶寬;其工作電壓為1.5V,保證相同頻率下功耗更低。

2019-06-25 15:49:23 2336

2336 DDR3 SDRAM是DDR3的全稱,它針對Intel新型芯片的一代內存技術(但目前主要用于顯卡內存),頻率在800M以上。DDR3是在DDR2基礎上采用的新型設計,與DDR2 SDRAM相比具有功耗和發熱量較小、工作頻率更高、降低顯卡整體成本、通用性好的優勢。

2019-10-29 08:00:00 0

0 本文檔的主要內容詳細介紹的是DDR和DDR2與DDR3的設計資料總結包括了:一、DDR的布線分析與設計,二、DDR電路的信號完整性,三、DDR Layout Guide,四、DDR設計建議,六、DDR design checklist,七、DDR信號完整性

2020-05-29 08:00:00 0

0 注意事項。 信號完整性問題和印刷電路板 頻率 在低頻下,您應該不會遇到信號完整性方面的任何重大問題。但是,隨著信號速度的提高,您會獲得更高的頻率,這會影響系統的模擬和數字屬性。在較高的頻率下,您可能會遇到反射,地面反彈,串擾和振鈴

2020-09-21 21:22:51 3169

3169 用于 DDR 電源及終端的高效率、雙通道、±3A同步降壓型穩壓器符合 DDR / DDR2 / DDR3 標準

2021-03-19 08:44:50 13

13 15V、雙通道 3A 單片同步降壓型穩壓器為 DDR1、DDR2 或 DDR3 存儲器供電

2021-03-20 15:29:10 6

6 用于 DDR 終端的高效率 ±6A 開關穩壓器符合 DDR / DDR2 / DDR3 標準

2021-03-21 05:20:16 4

4 本文章主要涉及到對DDR2和DDR3在PCB設計時,考慮信號完整性和電源完整性的設計事項,這些是具有相當大的挑戰性的。 文章重點是討論在盡可能少的PCB層數,特別是4層板的情況下的相關技術,其中

2021-03-25 14:26:01 5336

5336

EE-387:將DDR3/DDR2/LPDDR內存連接到ADSP-SC5xx/ADSP-215xx處理器

2021-04-20 15:44:56 2

2 引言:本文我們介紹FPGA外設DDR2/DDR3硬件設計相關內容,包括PCB板層數估計,信號端接、信號完整性及時序考慮等問題。 1.介紹 Artix-7和Spartan-7器件有各種各樣的軟件包

2021-08-26 10:12:21 4890

4890

DDR4電路板設計與信號完整性驗證挑戰

2021-09-29 17:50:07 14

14 DDR,DDR2,DDR3,DDR4,LPDDR區別作者:AirCity 2019.12.17Aircity007@sina.com 本文所有權歸作者Aircity所有1 什么是DDRDDR

2021-11-10 09:51:03 163

163 本手冊以 DDR3 器件為例講解硬件設計方法,包括 FPGA I/O 分配、原

理圖設計、電源網絡設計、PCB 走線、參考平面設計、仿真等,旨在協助用

戶快速完成信號完整性好、低功耗、低噪聲的高速存儲方案的硬件設計。

2022-09-15 10:31:36 15

15 的讀取寫入是按時鐘同步的;所謂動態,是指DDR3中的數據掉電無法保存,且需要周期性的刷新,才能保持數據;所謂隨機存取,即可以隨機操作任一地址的數據;所謂double-data-rate,即時鐘的上升沿

2022-12-21 18:30:05 5150

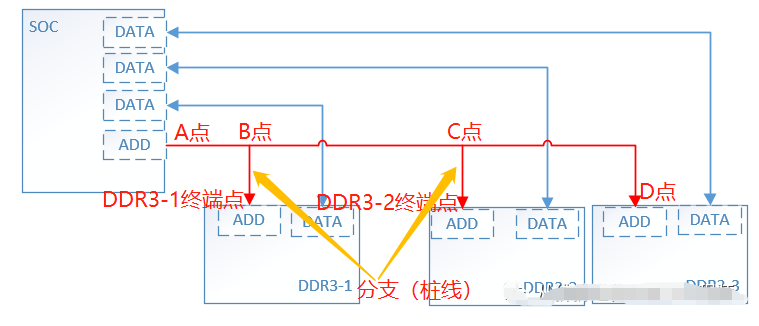

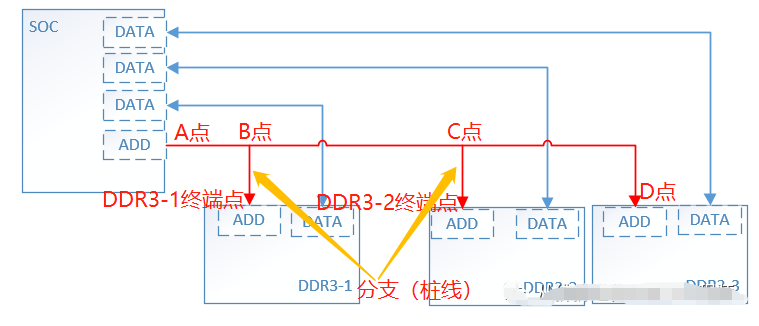

5150 有些設計中可能是三個或者更多芯片在同一個信號鏈路上,按照flyby拓撲結構布局。如下圖是一顆SOC和3顆DDR3的PCB布局設計。因為三顆DDR3的ADD是共用一組來自SOC的信號線,因此只有ADD

2023-04-15 16:07:50 2094

2094

電子發燒友網站提供《PI2DDR3212和PI3DDR4212在DDR3/DDR4中應用.pdf》資料免費下載

2023-07-24 09:50:47 3

3 DDR3是2007年推出的,預計2022年DDR3的市場份額將降至8%或以下。但原理都是一樣的,DDR3的讀寫分離作為DDR最基本也是最常用的部分,本文主要闡述DDR3讀寫分離的方法。

2023-10-18 16:03:56 1889

1889

電子發燒友網站提供《DDR2與DDR的區別.doc》資料免費下載

2024-03-07 14:58:52 0

0 電子發燒友網站提供《完整的DDR、DDR2和DDR3內存電源解決方案同步降壓控制器數據表.pdf》資料免費下載

2024-03-13 10:16:45 1

1 電子發燒友網站提供《具有同步降壓控制器、2A LDO和緩沖基準的TPS51916完整DDR2、DDR3、DDR3L和DDR4存儲器電源解決方案數據表.pdf》資料免費下載

2024-03-13 11:24:34 0

0 電子發燒友網站提供《具有同步降壓控制器、2A LDO和緩沖基準的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4內存電源解決方案數據表.pdf》資料免費下載

2024-03-13 11:13:44 0

0 電子發燒友網站提供《完整的DDR2、DDR3和DDR3L內存電源解決方案同步降壓控制器TPS51216數據表.pdf》資料免費下載

2024-03-13 13:58:12 0

0 電子發燒友網站提供《適用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF緩沖基準的TPS51206 2A峰值灌電流/拉電流DDR終端穩壓器數據表.pdf》資料免費下載

2024-03-13 13:53:03 1

1 電子發燒友網站提供《具有同步降壓控制器、2A LDO和緩沖基準的完整DDR2、DDR3和DDR3L存儲器電源解決方案TPS51216-EP數據表.pdf》資料免費下載

2024-03-26 11:19:21 0

0 電子發燒友網站提供《全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數據表.pdf》資料免費下載

2024-04-09 09:51:21 9

9 電子發燒友網站提供《完整DDR,DDR2,DDR3 和LPDDR3 存儲器電源解決方案同步降壓控制器數據表.pdf》資料免費下載

2024-04-09 09:49:32 0

0 電子發燒友網站提供《在DSP上實現DDR2 PCB布局布線.pdf》資料免費下載

2024-10-15 09:16:49 3

3 通常在800MHz到2133MHz之間,最新的技術可以達到8400MHz,但并非普遍標準。其帶寬相比DDR2提高了近30%。 DDR4 :速度通常在2133MHz到4266MHz之間,傳輸速率比DDR3

2024-11-29 15:08:28 19722

19722 最后一期我們主要介紹智多晶DDR Controller使用時的注意事項。

2025-01-24 11:14:14 1480

1480

TPS51216-EP 以最低的總成本和最小的空間為 DDR2、DDR3 和 DDR3L 內存系統提供完整的電源。它將同步降壓穩壓控制器 (VDDQ) 與 2A 灌/拉跟蹤 LDO (VTT) 和緩

2025-04-26 11:12:30 681

681

TPS51116為 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、DDR3L、LPDDR3 和 DDR4 內存系統提供完整的電源。它將同步降壓控制器與 3A 灌電流/拉

2025-04-29 16:38:02 1034

1034

? ? ? 本文講述了使用Altium designer設計SOC和DDR等高速PCB時候,如何設計信號線等長。DDR信號線分成兩大部分。一是數據線部分,二是地址線、控制信號線部分。本文著重詳細

2025-07-28 16:33:12 4

4

電子發燒友App

電子發燒友App

評論