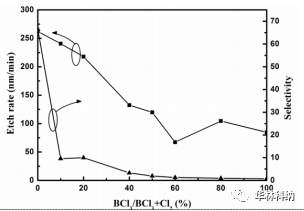

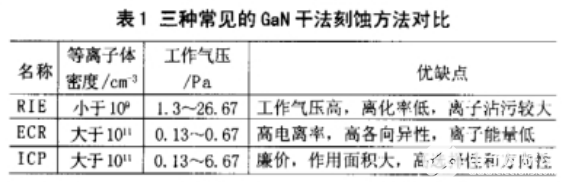

氮化鎵作為一種寬帶隙半導體,已被用于制造發(fā)光二極管和激光二極管等光電器件。最近已經(jīng)開發(fā)了幾種用于氮化鎵基材料的不同干蝕刻技術。電感耦合等離子體刻蝕因其優(yōu)越的等離子體均勻性和強可控性而備受關注。本研究

2022-04-26 14:07:28 2863

2863

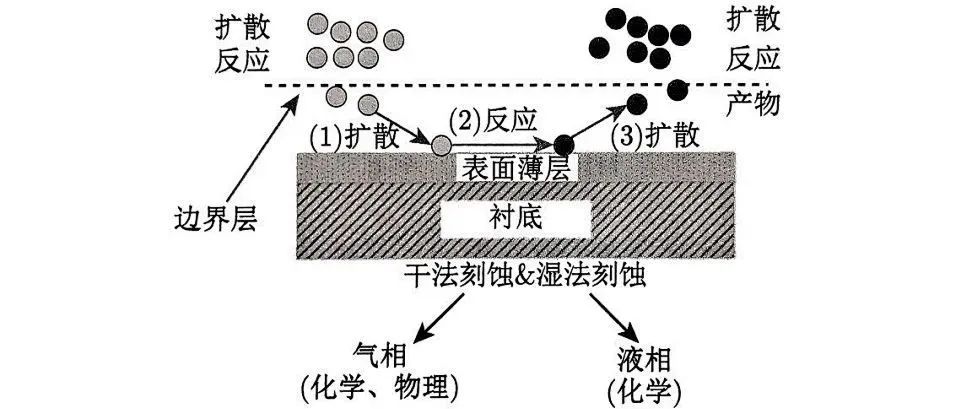

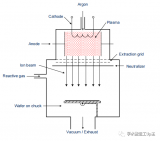

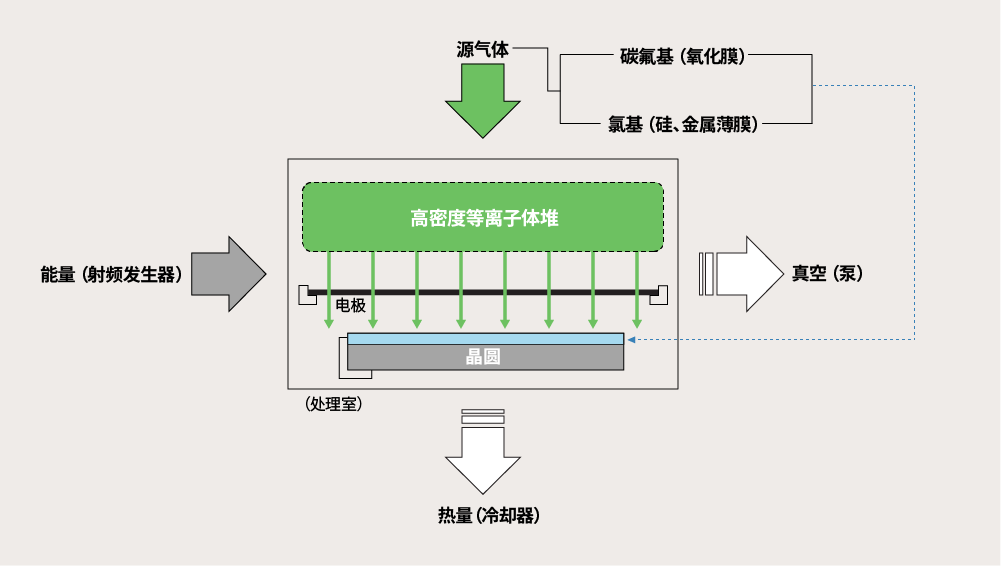

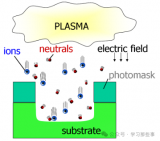

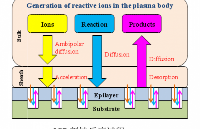

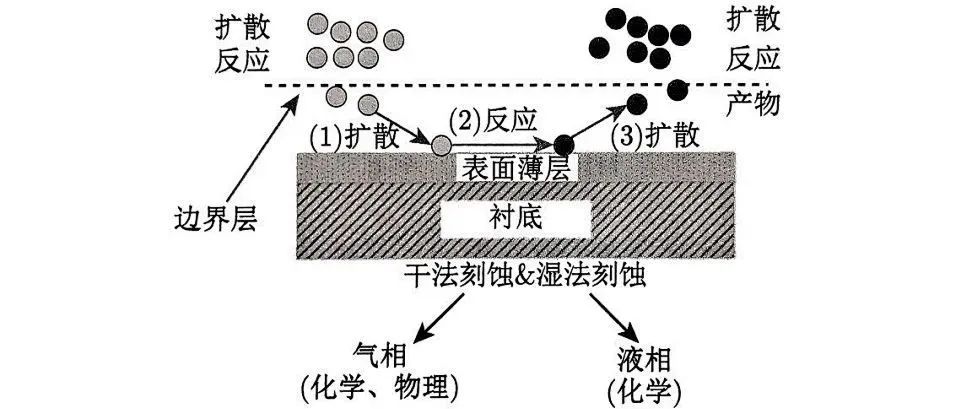

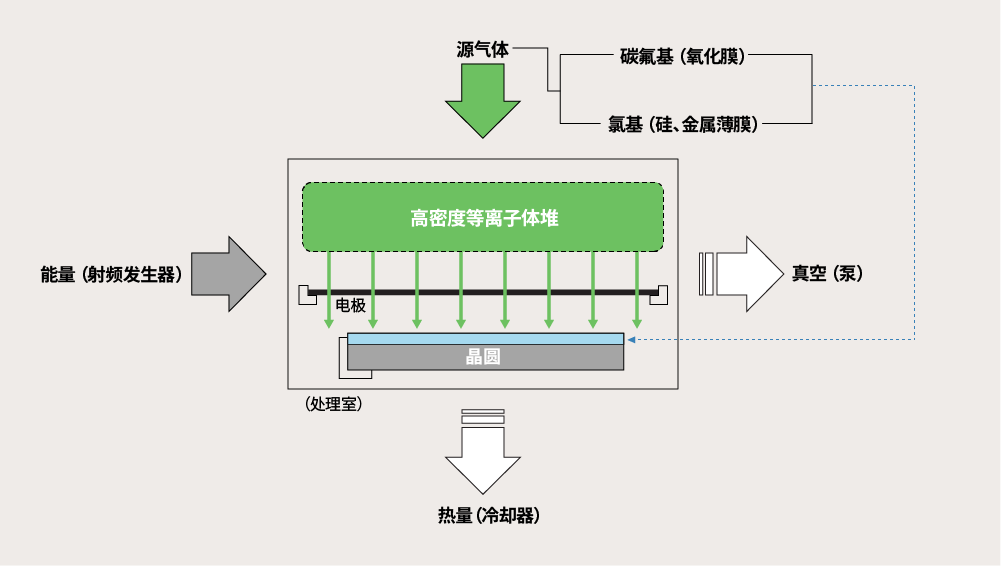

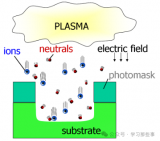

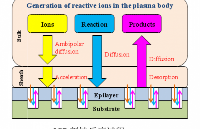

等離子體工藝廣泛應用于半導體制造中。比如,IC制造中的所有圖形化刻蝕均為等離子體刻蝕或干法刻蝕,等離子體增強式化學氣相沉積(PECVD)和高密度等離子體化學氣相沉積 (HDP CVD)廣泛用于電介質(zhì)

2022-11-15 09:57:31 5641

5641 在干法蝕刻中,氣體受高頻(主要為 13.56 MHz 或 2.45 GHz)激發(fā)。在 1 到 100 Pa 的壓力下,其平均自由程為幾毫米到幾厘米。

2023-06-20 09:49:16 15106

15106

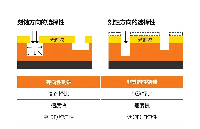

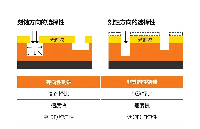

濕法刻蝕由于精度較差,只適用于很粗糙的制程,但它還是有優(yōu)點的,比如價格便宜,適合批量處理,酸槽里可以一次浸泡25張硅片,所以有些高校和實驗室,還在用濕法做器件,芯片廠里也會用濕法刻蝕來顯露表面缺陷(defect),腐蝕背面多晶硅。

2023-08-28 09:47:44 5856

5856

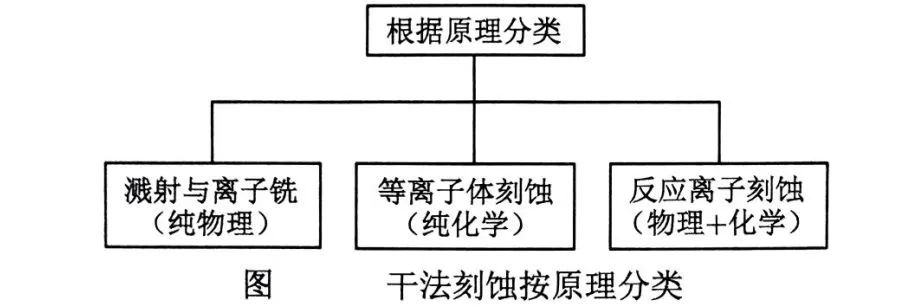

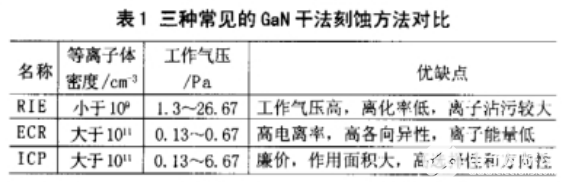

。常見的干法刻蝕設備有反應離子刻蝕機(RIE)、電感耦合等離子體刻蝕機(ICP)、磁性中性線等離子體刻蝕機(NLD)、離子束刻蝕機(IBE),本文目的對各刻蝕設備的結(jié)構(gòu)進行剖析,以及分析技術的優(yōu)缺點。

2024-01-20 10:24:56 16124

16124

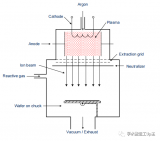

在半導體加工工藝中,常聽到的兩個詞就是光刻(Lithography)和刻蝕(Etching),它們像倆兄弟一樣,一前一后的出現(xiàn),有著千絲萬縷的聯(lián)系,這一節(jié)介紹半導體刻蝕工藝。

2024-01-26 10:01:58 5925

5925

干法刻蝕技術作為半導體制造的核心工藝模塊,通過等離子體與材料表面的相互作用實現(xiàn)精準刻蝕,其技術特性與工藝優(yōu)勢深刻影響著先進制程的演進方向。

2025-05-28 17:01:18 3199

3199

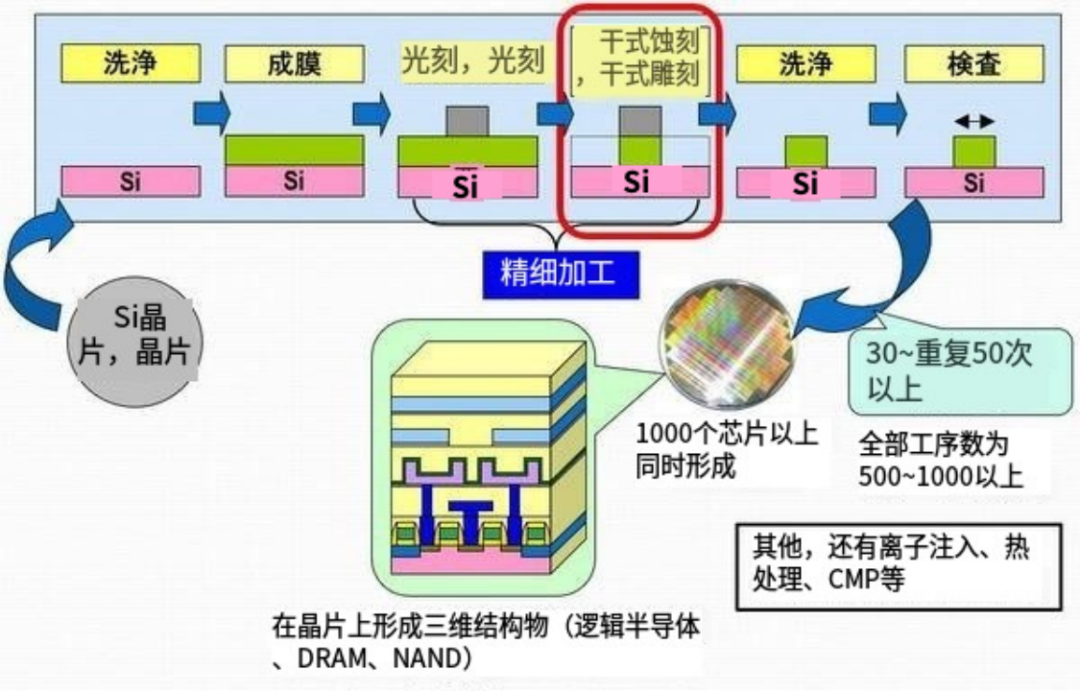

過程中需要經(jīng)歷材料制備、掩膜、光刻、刻蝕、清洗、摻雜、機械研磨等多個工序,其中以光刻流程最為關鍵,***是半導體芯片制造中最精密復雜、難度最高、價格最昂貴的設備,是整個制造流程工藝先進程度的重要指標

2019-06-14 16:43:28 30334

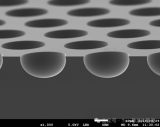

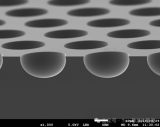

30334 隨著ALD厚度的增加,SiN /基底界面處的孔形狀從方形變?yōu)閳A形,并且逐漸變小。在足夠的ALD厚度下,菱形孔的尖端可視度有限,這會導致較低的刻蝕速率且刻蝕保持圓形。

2021-11-15 14:34:30 2317

2317

所需晶圓加工設備研發(fā)與銷售為主的技術驅(qū)動型半導體設備公司,主要產(chǎn)品包括干法去膠設備、快速熱處理設備、干法刻蝕設備等,主要應用于邏輯芯片、閃存芯片、DRAM芯片三大主流應用領域。 截至2021年6月底,屹唐半導體產(chǎn)品全球累計裝機數(shù)量已超過3800臺

2023-02-25 01:09:00 26672

26672 的成熟程度也間接決定了產(chǎn)品的良率和吞吐量。 ? 這每一道工序中,都有所需的對應設備,比如光刻所需的EUV、DUV光刻機,刻蝕所需的干法、濕法刻蝕機,以及化學、物理氣相沉積所需的CVD、PVD設備等等。光刻機作為半導體制造的核心

2023-07-30 03:24:48 3585

3585

濕法刻蝕作為半導體制造領域的元老級技術,其發(fā)展歷程與集成電路的微型化進程緊密交織。盡管在先進制程中因線寬控制瓶頸逐步被干法工藝取代,但憑借獨特的工藝優(yōu)勢,濕法刻蝕仍在特定場景中占據(jù)不可替代的地位。

2025-05-28 16:42:54 4247

4247

鋁、干法刻蝕鈦、干法刻蝕氮化鈦等)20、 等離子去膠21、 DRIE (硅深槽刻蝕)、ICP、TSV22、 濕法刻蝕23、 膜厚測量24、 納米、微米臺階測量25、 電阻、方阻、電阻率測量等26、 半導體

2015-01-07 16:15:47

半導體光刻蝕工藝

2021-02-05 09:41:23

本人小白,最近公司想上半導體器件的塑封生產(chǎn)線,主要是小型貼片器件封裝,例如sot系列。設備也不需要面面俱到,能進行小規(guī)模正常生產(chǎn)就行。哪位大神能告知所需設備的信息,以及這些設備的國內(nèi)外生產(chǎn)廠家,在此先行感謝!

2022-01-22 12:26:47

半導體失效分析項目介紹,主要包括點針工作站(Probe Station)、反應離子刻蝕(RIE)、微漏電偵測系統(tǒng)(EMMI)、X-Ray檢測,缺陷切割觀察系統(tǒng)(FIB系統(tǒng))等檢測試驗。

2020-11-26 13:58:28

哪位大神可以詳細介紹一下半導體式光纖溫度傳感器的建模、仿真與實驗

2021-04-07 06:42:55

半導體景氣關鍵指標北美半導體設備制造商接單出貨比(B/B值),8月雖站上五個月來新高達1.06,但國際半導體設備材料協(xié)會(SEMI)預警未來幾個月將下滑,國際一線半導體設備大廠營運首當其沖。 B

2015-11-27 17:53:59

蘇州晶淼半導體設備有限公司致力于向客戶提供濕法制程刻蝕設備、清洗設備、高端PP/PVC通風柜/廚、CDS化學品集中供液系統(tǒng)等一站式解決方案。我們的產(chǎn)品廣泛應用與微電子、半導體、光伏、光通信、LED等

2016-09-06 13:53:08

功率半導體的熱管理對于元件運行的可靠性和使用壽命至關重要。本設計實例介紹的愛普科斯(EPCOS)負溫度系數(shù)(NTC)和正溫度系數(shù)(PTC)熱敏電阻系列,可以幫助客戶可靠地監(jiān)測半導體元件的溫度。

2020-08-19 06:50:50

在制造半導體器件時,為什么先將導電性能介于導體和絕緣體之間的硅或鍺制成本征半導體,使之導電性極差,然后再用擴散工藝在本征半導體中摻入雜質(zhì)形成N型半導體或P型半導體改善其導電性?

2012-07-11 20:23:15

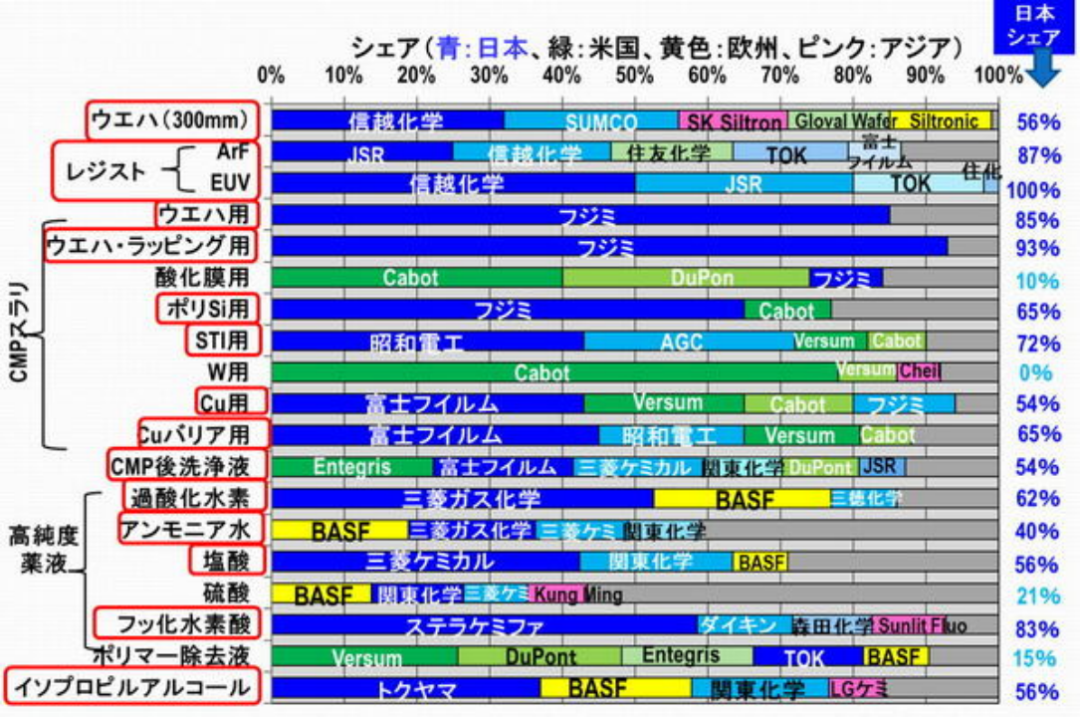

以及降低成本。由于半導體制造的工藝性涉及多個行業(yè),專門從事供應的行業(yè)發(fā)展起來以提供硅片制造需要的化學材料和設備。眾多高技術公司于20世紀60年代成立:1968年,成立英特爾公司。1969年,成立AMD。20

2020-09-02 18:02:47

過程與機臺,以提高良率和總體設備效能。而統(tǒng)計過程控制(Statistical Process Control,SPC)是目前國內(nèi)外發(fā)展APC最常用的一種技術,本文將主要論述SPC在半導體晶圓制造

2018-08-29 10:28:14

表面的預處理 治療2.2 GaN襯底的CMP處理2.3 GaN襯底的ICP干法刻蝕2.4 表面處理后的表面和次表面評估3. 結(jié)果和討論3.1 GaN襯底的CMP處理3.2 GaN襯底的ICP干法刻蝕

2021-07-07 10:26:01

是工廠的排氣系統(tǒng);半導體制造和檢驗過程中使用多種藥液和氣體,也會產(chǎn)生大量的污水和有害氣體,如圖1-1所示,污水處理設施、廢液儲存罐、廢氣處理設施也是半導體工廠的標配。

通過閱讀此章了解了半導體工廠建設所需要的條件和設備,對生產(chǎn)環(huán)境的要求。

2024-12-29 17:52:51

保留半導體電路圖。這一步驟需要借助液體、氣體或等離子體等物質(zhì),通過濕法刻蝕或干法刻蝕等方法,精確去除選定的多余部分。

薄膜沉積將含有特定分子或原子單元的薄膜材料,通過一系列技術手段,如化學氣相沉積

2024-12-30 18:15:45

還提到了占用空間比較大的居然是停車場。

然后介紹了擴擴散工藝,提到了無塵室是半導體工廠的心臟。

接著介紹了晶圓檢驗工藝

接著介紹了封裝和檢驗工藝

屬于后道工序制造

然后介紹了

2024-12-16 22:47:55

新加坡知名半導體晶圓代工廠招聘資深刻蝕工藝工程師和刻蝕設備主管!此職位為內(nèi)部推薦,深刻蝕工藝工程師需要有LAM 8寸機臺poly刻蝕經(jīng)驗。刻蝕設備主管需要熟悉LAM8寸機臺。待遇優(yōu)厚。有興趣的朋友可以將簡歷發(fā)到我的郵箱sternice81@gmail.com,我會轉(zhuǎn)發(fā)給HR。

2017-04-29 14:23:25

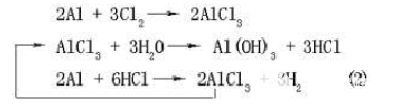

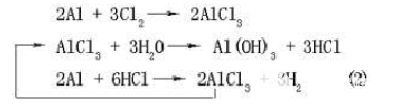

蒸發(fā),所以刻蝕要在一個裝有冷卻蓋的密封回流容器中進行。主要問題是光刻膠層經(jīng)不起刻蝕劑的溫度和高刻蝕速率。因此,需要一層二氧化硅或其他材料來阻擋刻蝕劑。這兩個因素已導致對于氮化硅使用干法刻蝕技術。蒸汽刻蝕

2018-12-21 13:49:20

1、GaAs半導體材料可以分為元素半導體和化合物半導體兩大類,元素半導體指硅、鍺單一元素形成的半導體,化合物指砷化鎵、磷化銦等化合物形成的半導體。砷化鎵的電子遷移速率比硅高5.7 倍,非常適合

2019-07-29 07:16:49

想問一下,半導體設備需要用到溫度傳感器的有那些設備,比如探針臺有沒有用到,具體要求是那些,

2024-03-08 17:04:59

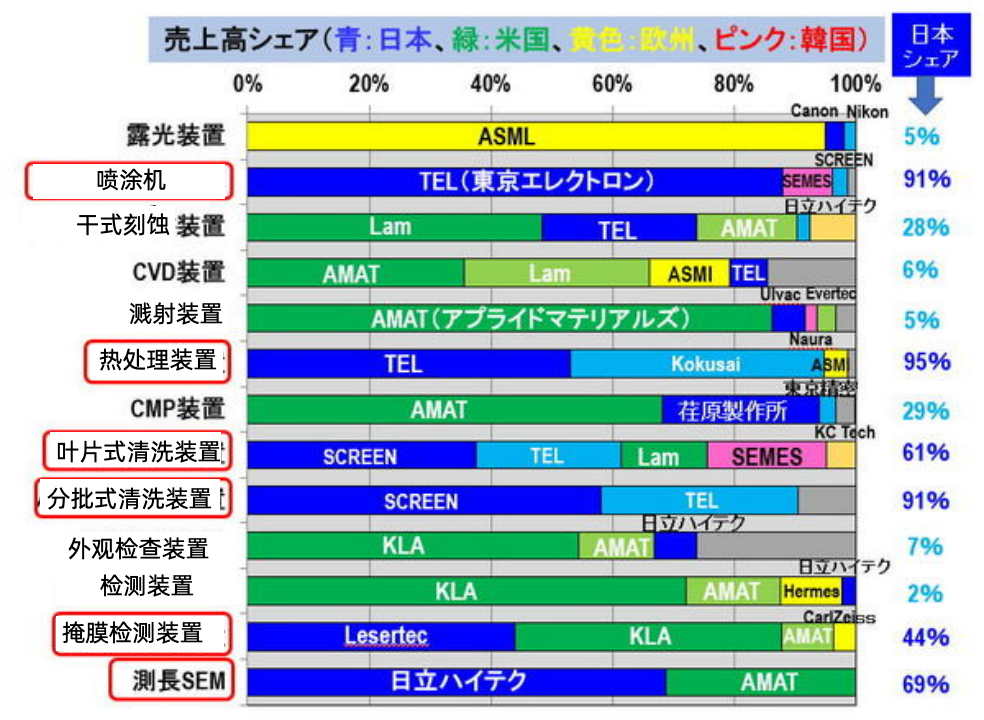

芯片是未來眾多高技術產(chǎn)業(yè)的食糧,芯片設計制造技術成為世界主要大國競爭的最重要領域之一。而芯片生產(chǎn)設備又為芯片大規(guī)模制造提供制造基礎,因此更是整個半導體芯片產(chǎn)業(yè)金字塔頂端的尖尖。下面是小編帶領大家

2018-09-03 09:31:49

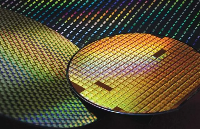

今日分享晶圓制造過程中的工藝及運用到的半導體設備。晶圓制造過程中有幾大重要的步驟:氧化、沉積、光刻、刻蝕、離子注入/擴散等。這幾個主要步驟都需要若干種半導體設備,滿足不同的需要。設備中應用較為廣泛

2018-10-15 15:11:22

基于半導體制冷片的高精度溫度控制系統(tǒng),總結(jié)的太棒了

2021-05-08 06:20:22

如何實現(xiàn)基于STM32的半導體制冷片(TEC)溫度控制系統(tǒng)設計?

2021-12-23 06:07:59

{:1:}想了解半導體制造相關知識

2012-02-12 11:15:05

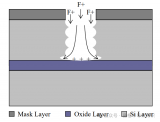

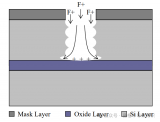

形成電路,而“濕法”刻蝕(使用化學浴)主要用于清潔晶圓。 干法刻蝕是半導體制造中最常用的工藝之一。 開始刻蝕前,晶圓上會涂上一層光刻膠或硬掩膜(通常是氧化物或氮化物),然后在光刻時將電路圖形曝光在晶圓

2017-10-09 19:41:52

。 第1章 半導體產(chǎn)業(yè)介紹 第2章 半導體材料特性 第3章 器件技術 第4章 硅和硅片制備 第5章 半導體制造中的化學品 第6章 硅片制造中的沾污控制 第7章 測量學和缺陷檢查 第8章 工藝腔內(nèi)的氣體控制

2025-04-15 13:52:11

蘇州晶淼有限公司專業(yè)制作半導體設備、LED清洗腐蝕設備、硅片清洗、酸洗設備等王經(jīng)理***/13771786452

2016-07-20 11:58:26

面表達能力,可以使用英語或日語或者韓語進行溝通者佳;4. 優(yōu)先考慮具有3年及以上干法刻蝕經(jīng)驗工藝工程師;5. 熟悉TFT原理及制造工藝流程;6. 有設備評估經(jīng)驗者優(yōu)先,有設備安裝調(diào)試經(jīng)驗者優(yōu)先。四、實驗

2017-02-04 10:04:52

、具有半導體器件工藝開發(fā)工作經(jīng)歷,3年以上工作經(jīng)驗,4、具有良好的團隊合作精神和進取精神三、半導體刻蝕工藝工程師職責描述:1、 獨立負責干法、濕法刻蝕工藝,進行刻蝕工藝菜單的調(diào)試; 2、優(yōu)化干法刻蝕、濕法

2016-10-26 17:05:04

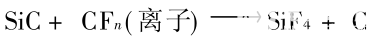

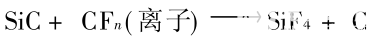

最近需要用到干法刻蝕技術去刻蝕碳化硅,采用的是ICP系列設備,刻蝕氣體使用的是SF6+O2,碳化硅上面沒有做任何掩膜,就是為了去除SiC表面損傷層達到表面改性的效果。但是實際刻蝕過程中總是會在碳化硅

2022-08-31 16:29:50

畢業(yè)設計的要求是用單片機設計一個溫度測量電路,通過測量得到的溫度去控制半導體片的電流方向,從而達到控制兩面的溫度!這個要怎么做,求大神

2020-03-25 00:26:51

Microstructures在SEMICON China期間推出了干法刻蝕模塊與氧化物釋放技術,該技術為MEMS器件設計師提供了更多的生產(chǎn)選擇,同時帶來了寬泛的制造工藝窗口,從而使良率得到了提升。麥|斯

2013-11-04 11:51:00

一、設備概述高溫磷酸刻蝕設備是半導體制造中用于各向異性刻蝕的關鍵設備,通過高溫磷酸溶液與半導體材料(如硅片、氮化硅膜)的化學反應,實現(xiàn)精準的材料去除。其核心優(yōu)勢在于納米級刻蝕精度和均勻

2025-06-06 14:38:13

釋放MEMS機械結(jié)構(gòu)的干法刻蝕技術

濕法刻蝕是MEMS 器件去除犧牲材料的傳統(tǒng)工藝,總部位于蘇格蘭的Point 35 Microstructures在SEMICON C

2009-11-18 09:17:32 1341

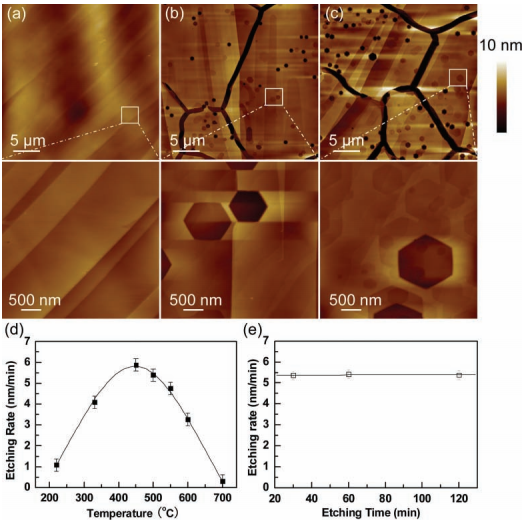

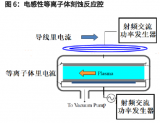

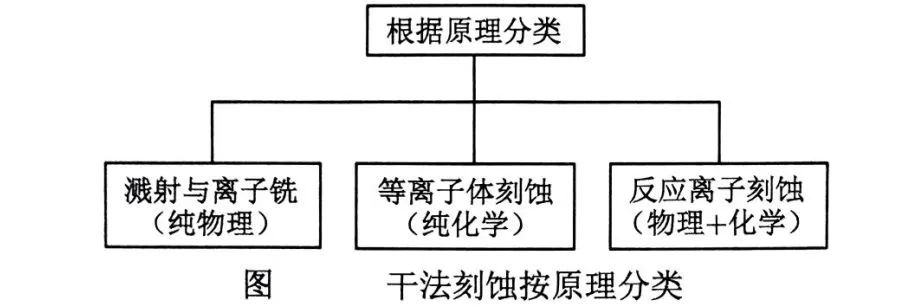

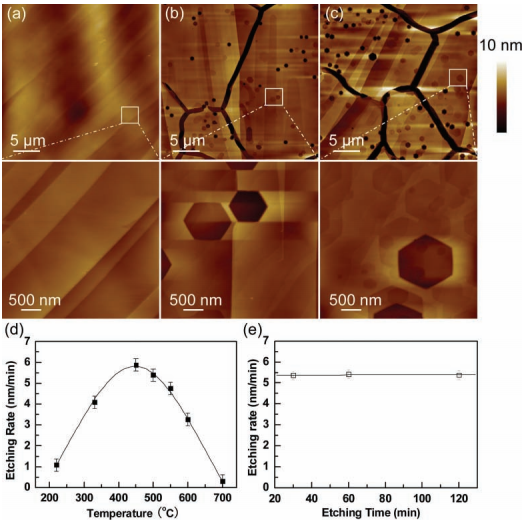

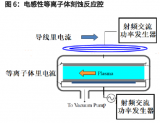

1341 干法刻蝕原理

刻蝕作用:去除邊緣PN結(jié),防止上下短路。干法刻蝕原理:利用高頻輝光放電反應,使CF4氣體激活成活性粒子,這些活性

2010-07-18 11:28:20 6853

6853 熟悉微電子工藝設備的人都知道,射頻源(RFGENERATER)是半導體工藝不可缺少的設備,其主要應用于等離子體干法刻蝕設備。其原理是刻蝕氣體(主要是F基和C1基的氣體)通過氣體流量控制

2016-05-27 15:17:07 2282

2282

半導體制造刻蝕設備調(diào)度算法的研究_賈小恒

2017-03-19 11:28:16 2

2 目前市場上,一臺新的干法刻蝕設備使用的射頻源售價大概在1萬美金左右,而維修一臺射頻源的費用一般也要1萬元人民幣以上,可見其費用相當昂貴。本著節(jié)約成木的原則,本單位對在使用中出現(xiàn)故障的射頻源進行自主

2018-06-08 09:19:00 9541

9541

日前,《日本經(jīng)濟新聞》報道,當?shù)貢r間4月3日,半導體制造設備業(yè)界團體、國際半導體設備與材料協(xié)會(SEMI)宣布,中國半導體后道工序使用的封裝設備和材料的市場規(guī)模2017年同比增長23.4%,達到

2018-04-16 13:34:00 948

948 半導體設備和材料處于產(chǎn)業(yè)鏈的上游,是推動技術進步的關鍵環(huán)節(jié)。半導體設備和材料應用于集成電路、LED等多個領域,其中以集成電路的占比和技術難度最高。 01IC制造工藝流程及其所需設備和材料 半導體產(chǎn)品

2018-10-13 18:28:01 5731

5731 反刻是在想要把某一層膜的總的厚度減小時采用的(如當平坦化硅片表面時需要減小形貌特征)。光刻膠是另一個剝離的例子。總的來說,有圖形刻蝕和無圖形刻蝕工藝條件能夠采用干法刻蝕或濕法腐蝕技術來實現(xiàn)。為了復制硅片表面材料上的掩膜圖形,刻蝕必須滿足一些特殊的要求。

2018-12-14 16:05:27 72478

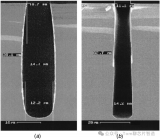

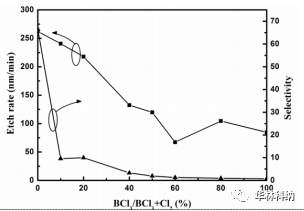

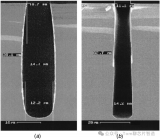

72478 形貌。在優(yōu)化后的刻蝕工藝條件下GaN材料刻蝕速率達到340nm/min,側(cè)墻傾斜度大于8O。且刻蝕表均方根粗糙度小于3nm。對引起干法刻蝕損傷的因索進行了討論,并介紹了幾種減小刻蝕損傷的方法。 氮化鎵(GaN

2020-12-29 14:39:29 4598

4598

在集成電路的制造過程中,刻蝕就是利用化學或物理方法有選擇性地從硅片表面去除不需要的材料的過程。從工藝上區(qū)分,刻蝕可以分為濕法刻蝕和干法刻蝕。前者的主要特點是各向同性刻蝕;后者是利用等離子體來進行

2020-12-29 14:42:58 11752

11752

摘要:簡述了在SiC材料半導體器件制造工藝中,對SiC材料采用干法刻蝕工藝的必要性.總結(jié)了近年來SiC干法刻蝕技術的工藝發(fā)展狀況. 半導體器件已廣泛應用于各種場合,近年來其應用領域已拓展至許多

2020-12-30 10:30:11 10663

10663

半導體制造是人類迄今為止掌握的工業(yè)技術難度最高的生產(chǎn)環(huán)節(jié),是先進制造領域皇冠上的一顆鉆石。隨著半導體技術不斷發(fā)展,芯片線寬尺寸不斷減小,制造工序逐漸復雜。目前國際上7 nm制程已進入產(chǎn)業(yè)化階段,需要

2021-11-17 16:31:45 4322

4322 我們?nèi)A林科納研究了一種干法各向異性刻蝕石墨和石墨烯的方法,能夠通過調(diào)整蝕刻參數(shù),如等離子體強度、溫度和持續(xù)時間,從邊緣控制蝕刻,蝕刻過程歸因于碳原子的氫化和揮發(fā),蝕刻動力學與甲烷形成一致,這種簡單、干凈、可控且可擴展的技術與現(xiàn)有的半導體處理技術兼容。

2022-05-19 17:06:46 3260

3260

刻蝕室半導體IC制造中的至關重要的一道工藝,一般有干法刻蝕和濕法刻蝕兩種,干法刻蝕和濕法刻蝕一個顯著的區(qū)別是各向異性,更適合用于對形貌要求較高的工藝步驟。

2022-06-13 14:43:31 6

6 在 MEMS 制造工藝中,常用的干法刻蝕包括反應離子刻蝕 (Reactive lon Etching, RIE)、深反應離子刻蝕(Deep Reactive lon Etching, DRIE) 和XerF2各向同性蝕刻。

2022-10-10 10:12:15 6878

6878 干法刻蝕工藝流程為,將刻蝕氣體注入真空反應室,待壓力穩(wěn)定后,利用射頻輝光放電產(chǎn)生等離子體;受高速電子撞擊后分解產(chǎn)生自由基,并擴散到圓片表面被吸附。

2022-11-10 09:54:19 9999

9999 濕法刻蝕是集成電路制造工藝最早采用的技術之一。雖然由于受其刻蝕的各向同性的限制,使得大部分的濕法刻蝕工藝被具有各向異性的干法刻蝕替代,但是它在尺寸較大的非關鍵層清洗中依然發(fā)揮著重要的作用。

2022-11-11 09:34:18 19992

19992 目前制作硅通孔的主要手段有濕法刻蝕,激光加工和干法刻蝕(深反應離子刻蝕, DRIE )三種。

2022-12-07 11:26:20 736

736 刻蝕是移除晶圓表面材料,達到IC設計要求的一種工藝過程。刻蝕有兩種:一種為圖形 化刻蝕,這種刻蝕能將指定區(qū)域的材料去除,如將光刻膠或光刻版上的圖形轉(zhuǎn)移到襯底薄膜 上

2023-02-01 09:09:35 4217

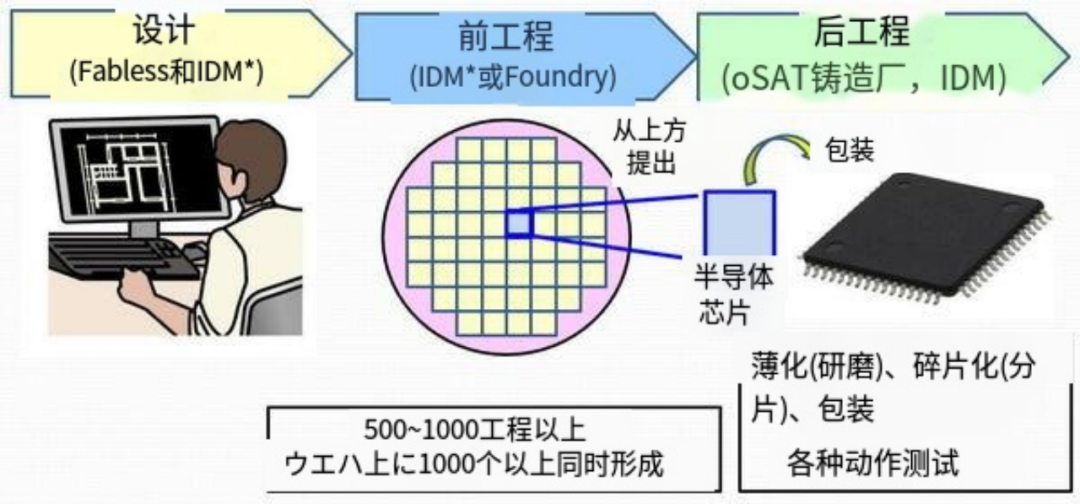

4217 半導體產(chǎn)品的制造過程主要包括前道晶圓制造和后道封裝測試,隨著先進封裝技術的浸透,呈現(xiàn)了介于晶圓制造和封裝之間的加工環(huán)節(jié),稱為中道)。半導體產(chǎn)品的加工工序多,在制造過程中需求大量的半導體設備。在這里

2023-03-27 09:43:57 1644

1644

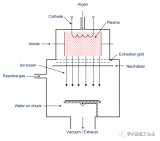

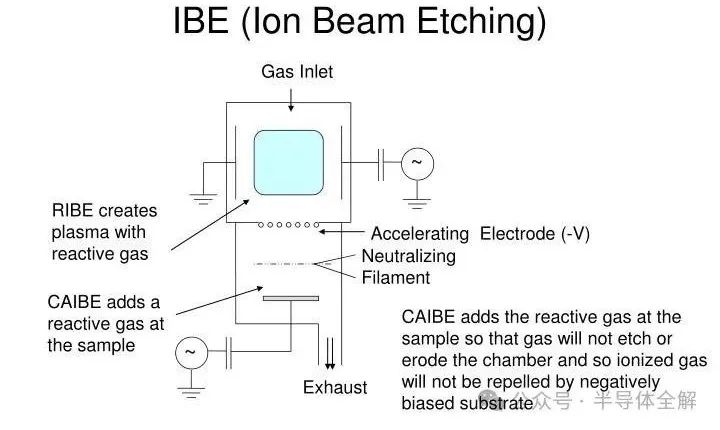

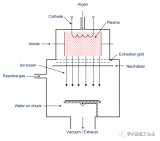

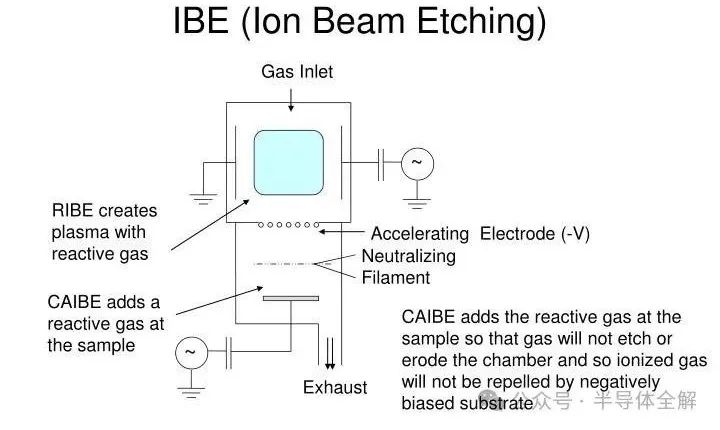

離子束蝕刻 (Ion beam etch) 是一種物理干法蝕刻工藝。由此,氬離子以約1至3keV的離子束輻射到表面上。由于離子的能量,它們會撞擊表面的材料。晶圓垂直或傾斜入離子束,蝕刻過程是絕對

2023-06-20 09:48:56 9250

9250

Dimension, CD)小型化(2D視角),刻蝕工藝從濕法刻蝕轉(zhuǎn)為干法刻蝕,因此所需的設備和工藝更加復雜。由于積極采用3D單元堆疊方法,刻蝕工藝的核心性能指數(shù)出現(xiàn)波動,從而刻蝕工藝與光刻工藝成為半導體制造的重要工藝流程之一。

2023-06-26 09:20:10 3193

3193

在半導體制造過程中,每個半導體元件的產(chǎn)品都需要經(jīng)過數(shù)百道工序。這些工序包括前道工藝和后道工藝,前道工藝是整個制造過程中最為重要的部分,它關系到半導體芯片的基本結(jié)構(gòu)和特性的形成,涉及晶圓制造、沉積、光刻、刻蝕等步驟,技術難點多,操作復雜。

2023-07-11 11:25:55 6657

6657

第一種是間歇式刻蝕方法(BOSCH),即多次交替循環(huán)刻蝕和淀積工藝,刻蝕工藝使用的是SF6氣體,淀積工藝使用的是C4F8氣體

2023-07-14 09:54:46 9786

9786

半導體工程裝備、北方華創(chuàng)的主要品種是刻蝕、薄膜、清洗、熱處理、晶體生長等核心技術裝備,廣泛應用邏輯部件,存儲半導體零部件、先進封裝、第三代半導體照明、微機電系統(tǒng)、新型顯示、新能源,襯底材料制造等工藝過程。

2023-09-18 09:47:19 1627

1627 9月17日,北方華創(chuàng)在投資者互動平臺表示,公司前期已經(jīng)發(fā)布了首臺國產(chǎn)12英寸CCP晶邊干法刻蝕設備研發(fā)成功有關信息,目前已在客戶端實現(xiàn)量產(chǎn),其優(yōu)秀的工藝均勻性、穩(wěn)定性贏得客戶高度評價。

2023-09-20 10:09:49 2728

2728 在半導體制造中,刻蝕工序是必不可少的環(huán)節(jié)。而刻蝕又可以分為干法刻蝕與濕法刻蝕,這兩種技術各有優(yōu)勢,也各有一定的局限性,理解它們之間的差異是至關重要的。

2023-09-26 18:21:00 10327

10327

據(jù)工信部網(wǎng)站11月16日消息,工信部公開征集了《半導體設備 集成電路制造用干法刻蝕設備測試方法》等196個行業(yè)標準、1個行業(yè)標準外文版、38個推薦性國家標準計劃項目的意見。

2023-11-16 17:04:49 1972

1972

刻蝕可以分為濕法刻蝕和干法刻蝕。濕法刻蝕各向異性較差,側(cè)壁容易產(chǎn)生橫向刻蝕造成刻蝕偏差,通常用于工藝尺寸較大的應用,或用于干法刻蝕后清洗殘留物等。

2024-04-12 11:41:56 8872

8872

今天我們要一起揭開一個隱藏在現(xiàn)代電子設備背后的高科技秘密——干法刻蝕工藝。這不僅是一場對微觀世界的深入探秘,更是一次對半導體芯片制造藝術的奇妙之旅。

2024-08-26 10:13:57 4403

4403

主要介紹幾種常用于工業(yè)制備的刻蝕技術,其中包括離子束刻蝕(IBE)、反應離子刻蝕(RIE)、以及后來基于高密度等離子體反應離子的電子回旋共振等離子體刻蝕(ECR)和電感耦合等離子體刻蝕(ICP)。

2024-10-18 15:20:41 3338

3338

本文介紹了為什么干法刻蝕又叫低溫等離子體刻蝕。 什么是低溫等離子體刻蝕,除了低溫難道還有高溫嗎?等離子體的溫度?? ? 等離子體是物質(zhì)的第四態(tài),并不是只有半導體制造或工業(yè)領域中才會有等離子體

2024-11-16 12:53:53 1560

1560

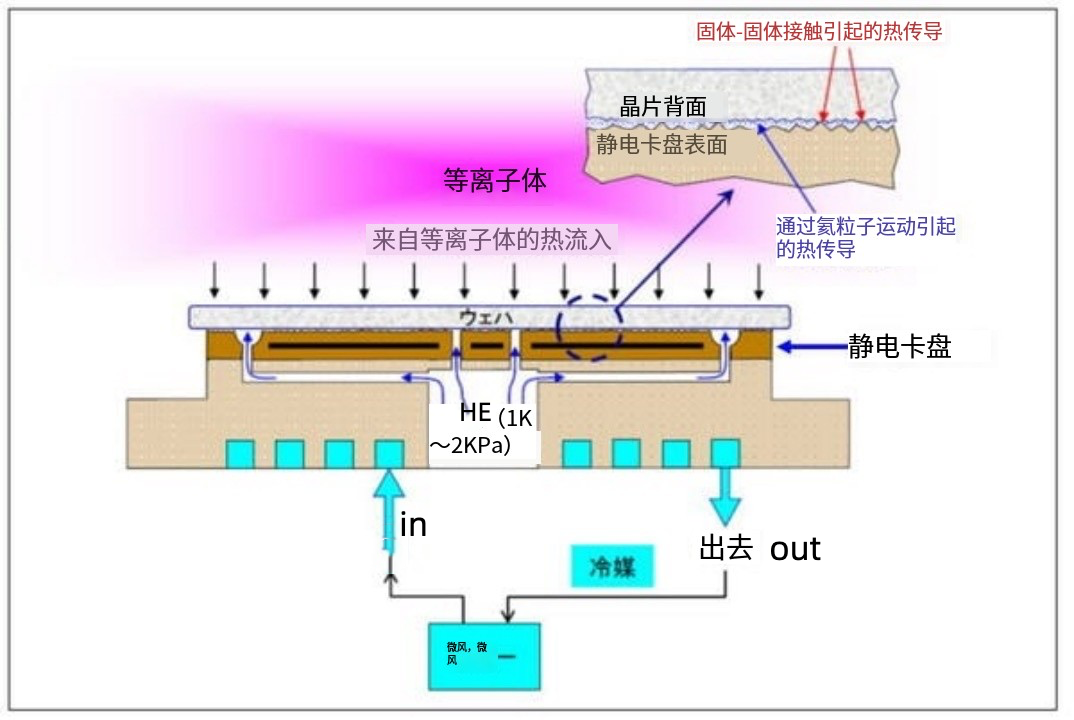

? ? ? 本文介紹了干法刻蝕工藝的不同參數(shù)。 干法刻蝕中可以調(diào)節(jié)的工藝參數(shù)有哪些?各有什么作用? 1,溫度:晶圓表面溫度,溫度梯度 晶圓表面溫度:控制刻蝕表面的化學反應速率和產(chǎn)物的揮發(fā)性 溫度

2024-12-02 09:56:43 2897

2897 本文介紹晶圓表面溫度對干法刻蝕的影響 表面溫度對干法刻蝕的影響主要包括:聚合物沉積,選擇性,光刻膠流動、產(chǎn)物揮發(fā)性與刻蝕速率,表面形貌等。 ? 聚合物沉積?:工藝過程中產(chǎn)生的聚合物會在表面沉積

2024-12-03 10:48:31 1982

1982

本文介紹了干法刻蝕側(cè)壁彎曲的原因及解決方法。 什么是側(cè)壁彎曲? 如上圖,是典型的干法刻蝕時,側(cè)壁彎曲的樣子,側(cè)壁為凹形或凸形結(jié)構(gòu)。而正常的側(cè)壁幾乎是垂直的,角度接近 90°。 ?什么原因?qū)е铝藗?cè)壁

2024-12-03 11:00:01 1609

1609

本文簡單介紹了芯片制造過程中的兩種刻蝕方法 ? 刻蝕(Etch)是芯片制造過程中相當重要的步驟。 刻蝕主要分為干刻蝕和濕法刻蝕。 ①干法刻蝕 利用等離子體將不要的材料去除。 ②濕法刻蝕 利用腐蝕性

2024-12-06 11:13:58 3353

3353

我們的主題,來給大家講講:半導體濕法刻蝕設備加熱器到底有什么用?作為核心部件的加熱器相信大家懂的,為了更容易讓大家明白與了解。我們總結(jié)了以下幾點內(nèi)容: 保持恒定刻蝕溫度:在半導體集成電路制造的槽式濕法刻蝕過

2024-12-13 14:00:31 1610

1610 在芯片制造過程中的各工藝站點,有很多不同的工藝名稱用于除去晶圓上多余材料,如“清洗”、“刻蝕”、“研磨”等。如果說“清洗”工藝是把晶圓上多余的臟污、particle、上一站點殘留物去除掉,“刻蝕

2024-12-16 15:03:06 2431

2431

離子轟擊的不均勻性 干法刻蝕通常是物理作用和化學作用相結(jié)合的過程,其中離子轟擊是重要的物理刻蝕手段。在刻蝕過程中,離子的入射角和能量分布可能不均勻. 如果離子入射角在側(cè)壁的不同位置存在差異,那么

2024-12-17 11:13:12 1469

1469

什么是刻蝕?刻蝕是指通過物理或化學方法對材料進行選擇性的去除,從而實現(xiàn)設計的結(jié)構(gòu)圖形的一種技術。蝕刻是半導體制造及微納加工工藝中相當重要的步驟,自1948年發(fā)明晶體管到現(xiàn)在,在微電子學和半導體領域

2024-12-20 16:03:16 1651

1651

)與半導體材料發(fā)生化學反應,形成可溶性產(chǎn)物。這些產(chǎn)物隨后被溶解在刻蝕液中,從而實現(xiàn)材料的去除。 刻蝕速率的控制:刻蝕速率由反應動力學和溶液中反應物質(zhì)的濃度決定。通過控制刻蝕劑的成分、濃度和溫度,可以精確控制刻蝕速率

2025-01-02 13:49:32 1181

1181 碳化硅(SiC)作為一種高性能材料,在大功率器件、高溫器件和發(fā)光二極管等領域有著廣泛的應用。其中,基于等離子體的干法蝕刻在SiC的圖案化及電子器件制造中起到了關鍵作用,本文將介紹干法刻蝕的概念、碳硅

2025-01-22 10:59:23 2668

2668

刻蝕工藝的核心機理與重要性 刻蝕工藝是半導體圖案化過程中的關鍵環(huán)節(jié),與光刻機和薄膜沉積設備并稱為半導體制造的三大核心設備。刻蝕的主要作用是將光刻膠上的圖形轉(zhuǎn)移到功能膜層,具體而言,是通過物理及化學

2025-04-27 10:42:45 2203

2203

半導體BOE(Buffered Oxide Etchant,緩沖氧化物蝕刻液)刻蝕技術是半導體制造中用于去除晶圓表面氧化層的關鍵工藝,尤其在微結(jié)構(gòu)加工、硅基發(fā)光器件制作及氮化硅/二氧化硅刻蝕中廣

2025-04-28 17:17:25 5516

5516 ICP(Inductively Coupled Plasma,電感耦合等離子體)刻蝕技術是半導體制造中的一種關鍵干法刻蝕工藝,廣泛應用于先進集成電路、MEMS器件和光電子器件的加工。以下是關于ICP

2025-05-06 10:33:06 3902

3902 在MEMS制造工藝中,干法刻蝕是通過等離子體、離子束等氣態(tài)物質(zhì)對薄膜材料或襯底進行刻蝕的工藝,其評價參數(shù)直接影響器件的結(jié)構(gòu)精度和性能。那么干法刻蝕有哪些評價參數(shù)呢?

2025-07-07 11:21:57 1625

1625

在MEMS中,玻璃因具有良好的絕緣性、透光性、化學穩(wěn)定性及可鍵合性(如與硅陽極鍵合),常被用作襯底、封裝結(jié)構(gòu)或微流體通道基板。玻璃刻蝕是制備這些微結(jié)構(gòu)的核心工藝,需根據(jù)精度要求、結(jié)構(gòu)尺寸及玻璃類型選擇合適的方法,玻璃刻蝕主要分為濕法腐蝕和干法刻蝕兩大類。

2025-07-18 15:18:01 1491

1491 在半導體制造中,溝槽刻蝕工藝的臺階高度直接影響器件性能。臺階儀作為接觸式表面形貌測量核心設備,通過精準監(jiān)測溝槽刻蝕形成的臺階參數(shù)(如臺階高度、表面粗糙度),為工藝優(yōu)化提供數(shù)據(jù)支撐。Flexfilm費

2025-08-01 18:02:17 845

845

濕法刻蝕SC2工藝在半導體制造及相關領域中具有廣泛的應用,以下是其主要應用場景和優(yōu)勢:材料選擇性去除與表面平整化功能描述:通過精確控制化學溶液的組成,能夠?qū)崿F(xiàn)對特定材料的選擇性去除。例如,它能

2025-08-06 11:19:18 1198

1198

電子發(fā)燒友App

電子發(fā)燒友App

評論