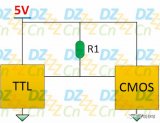

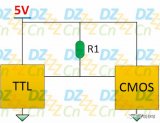

在 同樣5V電源電壓情況下,COMS電路可以直接驅動TTL,因為CMOS的輸出高電平大于2.0V,輸出低電平小于0.8V。

2017-09-20 10:04:53 35780

35780

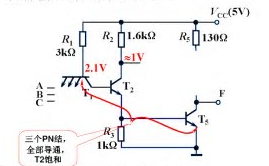

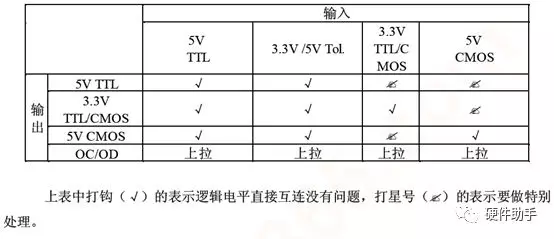

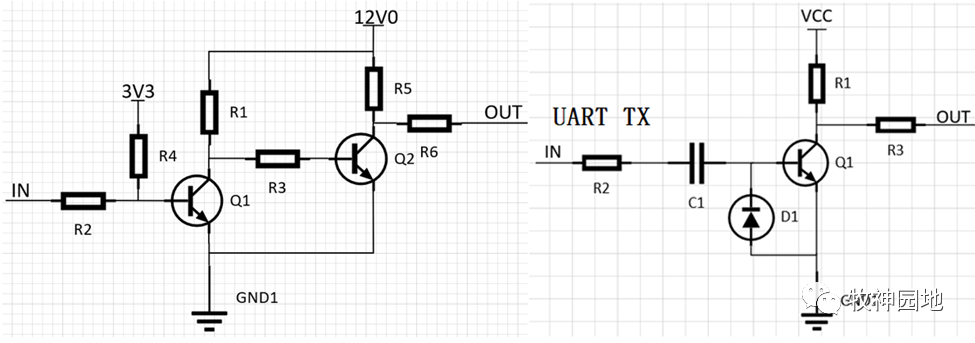

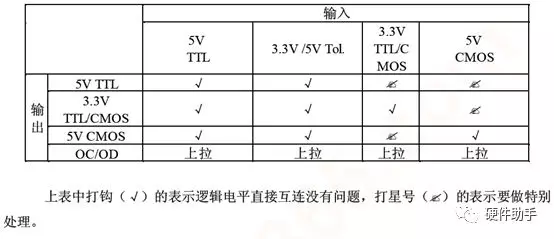

本篇主要介紹TTL/CMOS電平的互連、OC/OD的互連,其余單端邏輯電平的互連可參考相關器件規范、電平規范。 1、TTL/CMOS互連 常用的TTL和CMOS電平主要是5V TTL、5V CMOS

2020-12-23 14:15:12 8784

8784

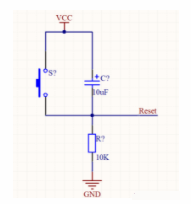

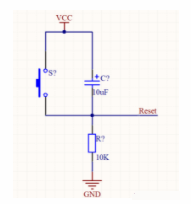

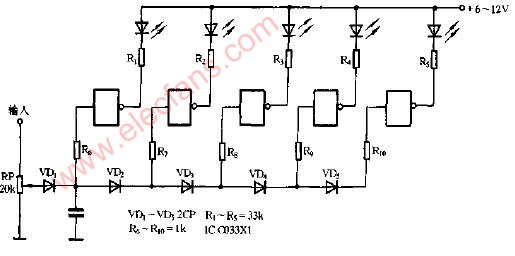

單片機復位電路分為兩種類型:低電平復位和高電平復位。

2022-08-05 15:45:28 32149

32149

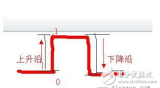

高電平和低電平是數字電路中經常會出現的專業名詞,它們所表面的意思就是電路上有和無,兩者之間沒有中間值,在不同的電路上,電壓的具體值也是各不相同的。如果用簡單的語言表達它們的意思就是開和關,平時

2023-05-26 10:17:30 67552

67552

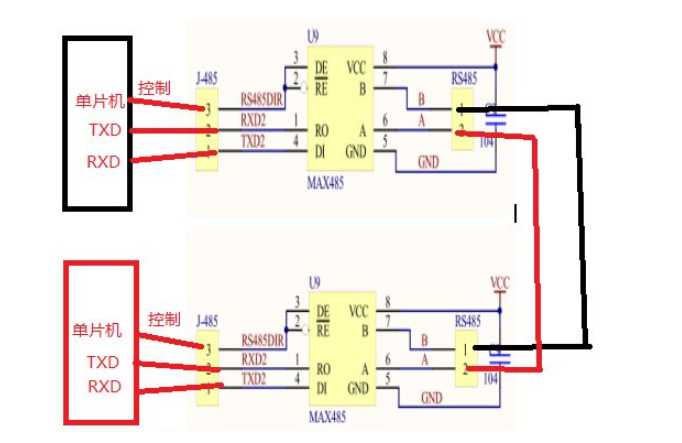

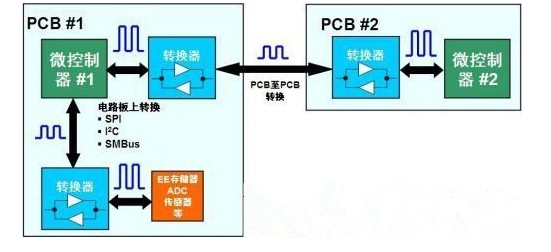

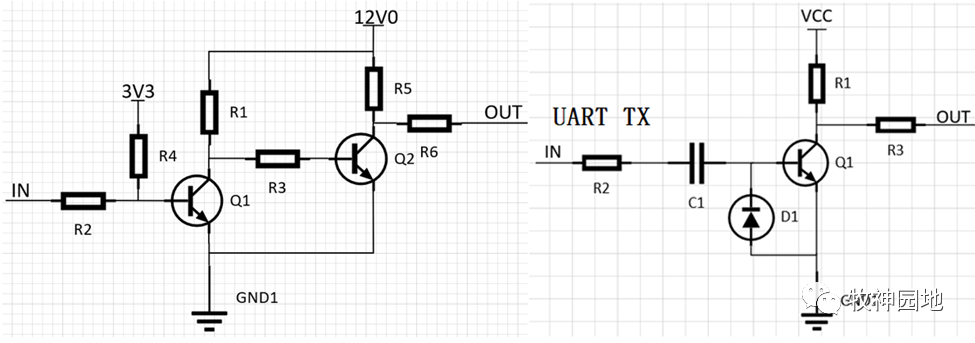

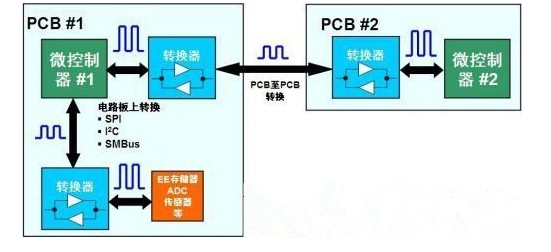

單端邏輯電平的匹配是我們平時在硬件設計中最經常碰到的,我們在《TTL&CMOS電平》章節中已經對TTL和COMS電平的匹配設計做了一些分析,一般3.3V LVTTL和LVCMOS是可以直接相互驅動的。但是其它不同邏輯電平之間呢?舉個栗子,3.3V邏輯電平和1.8V邏輯電平之間呢?

2023-06-25 14:52:24 4577

4577

CMOS電平和TTL電平對比分析為什么引入OC門?什么是OC、OD?

2021-04-20 06:53:21

1.TTL電平: 輸出高電平>2.4V,輸出低電平=2.0V,輸入低電平

2016-09-23 14:11:11

1.TTL電平: 輸出高電平>2.4V,輸出低電平=2.0V,輸入低電平

2016-09-25 10:13:14

CMOS和TTL通過電阻接電源,要如何判斷接入高電平還是低電平?

2023-04-25 09:27:35

DDC112的數字接口和控制(包括:TEST、CONV、CLK、DCLK、/DVALID、/DXMIT、DOUT等)的信號電平時CMOS電平?

2025-01-24 06:32:28

STM8的引腳要怎么才能輸出CMOS電平

2023-10-11 08:20:58

什么是TTL電平,什么是CMOS電平,他們的區別(一)TTL高電平3.6~5V,低電平0V~2.4V CMOS電平Vcc可達到12V ...

2022-01-25 06:19:09

指示出什么顏色代表什么區域,謝謝了!舉例,VIHX線往上方邊界Vcc看,中間包含的藍色和條紋帶都能被認為是高電平。是可靠電平。左邊2個是ttl邏輯電路不同供電電壓時情況;右邊2個是cmos邏輯電路

2008-07-21 10:22:44

“TTL電平”最常用于有關電專業,如:電路、數字電路、微機原理與接口技術、單片機等課程中都有所涉及。在數字電路中只有兩種電平(高和低)高電平+5V、低電平0V。同樣運用比較廣泛的還有CMOS電平

2018-01-17 14:52:47

TTL與CMOS電平詳解超級有用

2014-03-12 00:03:46

stm32F407VET6,如何判斷支持CMOS和TTL電平的IO口的的電平閾值,手冊說的是所有IO口都支持CMOS和TTL電平,且不需要軟件配置,

在標明IO口高低電平閾值特別說明了TTL

2024-04-16 08:24:56

,輸出在0.5V以下為低電平,輸入在2V以上為高電平,在0.8V以下為低電平。因此,CMOS電路與TTL電路就有一個電平轉換的問題,使兩者電平域值能匹配TTL電平與CMOS電平的區別:(一)TTL高電平

2016-09-27 16:26:31

什么是TTL電平?什么是CMOS電平?開漏形式的電路有什么特點?

2021-09-28 07:56:38

高電平低電平主要應用于數字電路。體現在電路上就是只有‘有’和‘無’,沒有中間值,這個有在不同電路上的電壓值不相同。如果是5V供電的數字電路,高電平就是5V,或接近5V。低電平就是‘無’,就是0V或

2018-08-28 14:59:04

。

早期的器件多是TTL電平,如早先的54系列和74系列。現在的大部分器件使用的工藝都是CMOS工藝。

輸出電平:高電平Uoh >=2.4v,低電平Uol <= 0.4v

2025-12-03 08:10:03

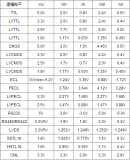

硬件研發工程師設計時肯定離不開電平這個概念,目前有多種電平定義,今天我就常用的電平做了下總結,和大家分享下現在常用的電平標準有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL

2011-05-11 08:02:01

看TTP224B手冊的時候看到這樣一句話。直接輸出模式, CMOS 輸出低電平有效到底是指低電平時才能有效輸出,還是指輸出端輸出低電平?

2020-10-18 15:39:26

TTL 驅動 3.3V CMOS可以直接驅動。

2、3.3V/5V TTL 驅動 5V CMOS 高電平輸出大于2.4V,如果落在2.4V至3.5V之間,CMOS電路不能檢測到高電平,需要進行電平轉換。

純分享貼,有需要可以直接下載附件獲取完整資料!

(如果內容有幫助可以關注、點贊、評論支持一下哦~)

2025-03-22 15:21:36

,輸出電壓低于VSS+0.5V(VSS為數字地)為邏輯 0。CMOS電路輸出高電平約為 0.9Vcc,而輸出低電平約為 0.1Vcc.當輸入電壓高于VDD-1.5V時為邏輯 1,輸入電壓

2019-03-22 07:00:00

CMOS電平和TTL電平的區別

2021-04-06 09:52:03

當Vccio=3. 3V時, 對于輸入腳, 它兼容TTL, CMOS電平;對輸出腳, 它是否也兼容TTL和CMOS電平?對CMOS電平, 是否需要用OpenDrain 加上下拉電阻來實現?

2019-09-03 05:55:08

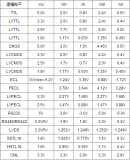

是從5V CMOS邏輯電平關注移植過來的,所以它的Vih、Vil和Voh、Vol與工作電壓有關,其值如上圖所示。LVCMOS邏輯電平定義的工作電壓范圍是2.7-3.6V。 5V的CMOS邏輯器件工作于

2009-04-12 12:03:33

。LVCMOS邏輯電平標準是從5V CMOS邏輯電平關注移植過來的,所以它的Vih、Vil和Voh、Vol與工作電壓有關,其值如上圖所示。LVCMOS邏輯電平定義的工作電壓范圍是2.7-3.6V。5V

2008-06-24 09:38:52

TTL電平與CMOS電平的區別

1,TTL電平:

輸出高電平>2.4V,輸出低電平<0.4V。在室溫下,一般輸出高電平是3.5V,輸出低電

2007-10-10 12:26:19 8910

8910 TTL電平 CMOS電平推挽輸出

TTL——Transistor-Transistor Logic HTTL——High-speed TTL LTTL——Low-power TTL STTL——Schottky TTL LSTTL——Low-power Schottky TTL

2007-12-05 09:35:31 3329

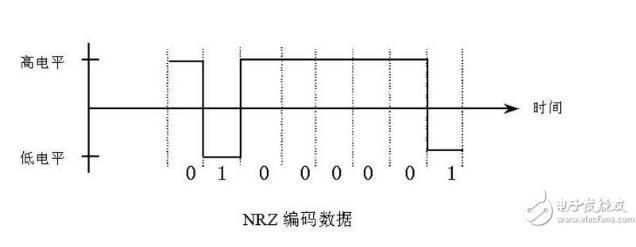

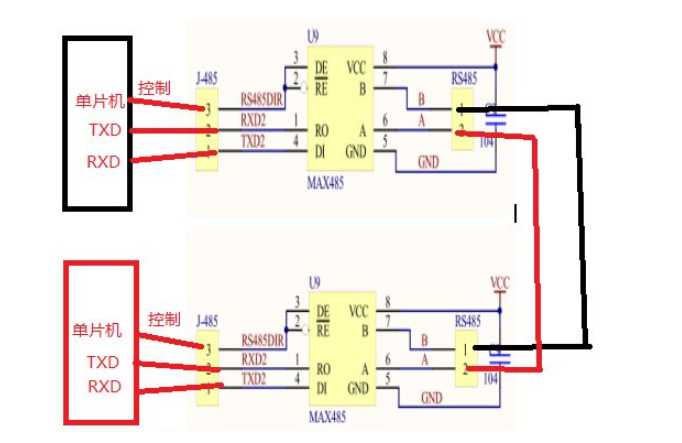

3329 電平標準:現在常用的電平標準有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,還有一些速

2008-07-21 10:25:08 3066

3066

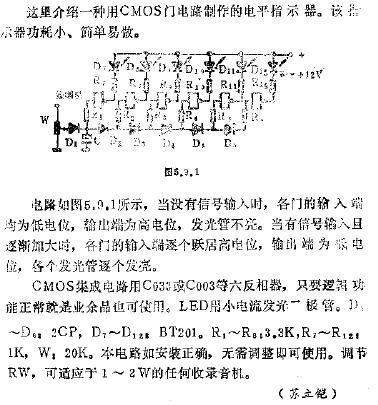

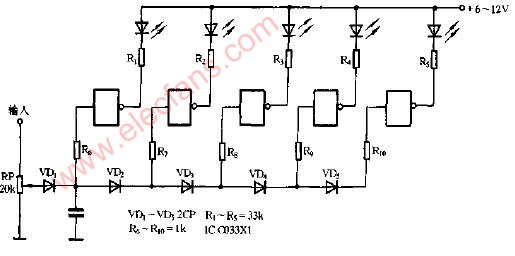

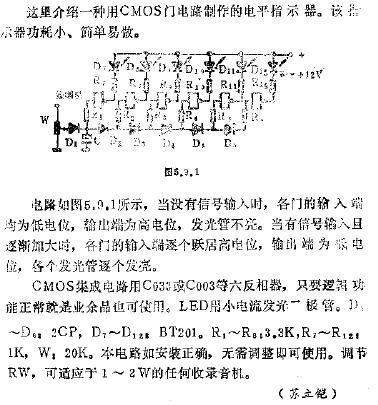

用CMOS集成電路制作的電平指示器

2009-04-20 11:37:05 790

790

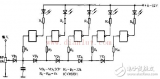

CMOS集成電路電平指示電路圖

2009-05-08 15:57:02 993

993

TTL和CMOS電平基礎知識

TTL電平: 輸出高電平 > 2.4V 輸出低電平 <

2009-11-28 11:28:33 1458

1458 車載功放的高電平輸入 高電平輸入是指車載功放可以直接從車載主機接收原本輸出至車載揚聲器的信

2010-01-04 11:11:59 7611

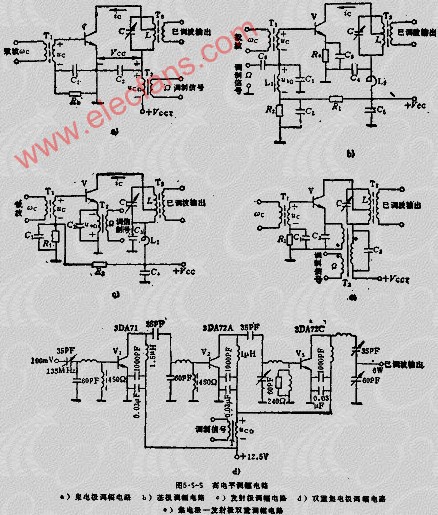

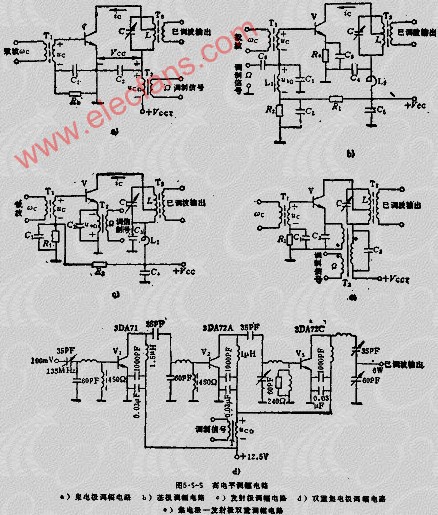

7611 調幅電路工作原理--高電平調幅電路

調幅的方法按電平的高低可區分為高電平調制和低電平調制,前者是直接產生滿足發射機輸出功率要

2010-05-25 15:50:49 19490

19490

CMOS 電路是電壓控制器件,輸入電阻極大,對于干擾信號十分敏感,因此不用的輸入端不應開路,接到地或者電源上。 CMOS 電路的優點是噪聲容限較寬,靜態功耗很小。TTL 電平輸出高電

2011-08-08 16:02:01 182

182 在電路設計時,最容易忽視也最容易造成錯誤的問題,詳細介紹TTL電平和CMO電平之間怎么轉換

2016-01-13 10:23:26 8

8 高電平輸出光控電路原理圖都是值得參考的設計。

2016-05-11 17:00:47 28

28 數字信號才是0和1 。凡是輸入與 5V TTL 電平兼容的 5V CMOS 器件都可以用作 3.3V→5V 電平轉換,這是由于 3.3V CMOS 的電平剛好和5V TTL電平兼容(巧合),而 CMOS 的輸出電平總是接近電源電平的。

2017-08-26 16:52:00 9729

9729

介紹常用的幾種邏輯電平,然后給出其與光模塊的接口電路。 TTL 電路的電平就叫 TTL 電平,CMOS 電路的電平就叫 CMOS 電平。 TTL 集成電路的全名是晶體管-晶體管邏輯集成電路(Transistor-Transistor Logic),標準 TTL 輸入高電平最小 2V,輸出高電平

2017-11-06 16:50:08 100

100 UolUoh2.4V,Uol0.4V 2.輸入高電平和輸入低電平Uih2.0V,Uil0.8V 二.CMOS CMOS電路是電壓控制器件,輸入電阻極大,對于干擾信號十分敏感,因此不用的輸入端不應開路,接到

2017-11-08 12:59:13 0

0 數字電路中,把電壓的高低用邏輯電平來表示。邏輯電平包括高電平和低電平這兩種。不同的元器件形成的數字電路,電壓對應的邏輯電平也不同。在TTL門電路中,把大于3.5伏的電壓規定為邏輯高電平,用數字1表示

2017-11-14 10:37:26 302062

302062

TTL電平最常用于有關電專業,如:電路、數字電路、微機原理與接口技術、單片機等課程中都有所涉及。在數字電路中只有兩種電平(高和低)高電平+5V、低電平0V.同樣運用比較廣泛的還有CMOS電平、232

2017-11-15 14:34:49 6

6 ,其引腳基本上是CMOS結構,因此輸入電壓范圍是:高電平不低于0.7VCC,低電平不高于0.3VCC。 但在介紹電平轉換電路之前,我們需要先來了解以下幾點: 1.解決電平轉換問題,最根本的就是要解決電平的兼容問題,而電平兼容原則有兩條:①VOH》VIH ②VO

2017-11-28 10:14:40 18

18 輸入高電平門限Vih:保證邏輯門的輸入為高電平時所允許的最小輸入高電平,當輸入電平高于Vih時,則認為輸入電平為高電平;

2018-03-10 09:47:49 13998

13998

本文開始闡述了電平信號什么意思以及電平信號的產生,其次對TTL電平的相關定義進行了介紹,最后闡述了電平信號和脈沖信號區別以及闡述了電平和電壓的區別。

2018-03-13 10:02:07 71765

71765

TTL、CMOS電平和OC門知識大全

2018-07-15 10:33:00 9500

9500 LS、HC 二者高電平低電平定義不同,HC高電平規定為0.7倍電源電壓,低電平規定為0.3倍電源電壓。

2018-08-02 16:52:25 81332

81332 (AHCT與TTL電平兼容)

FCT——FACT擴展系列,與TTL電平兼容

FACT——Fairchild Advanced CMOS Technology,其

?

1,TTL電平:

???輸出高電平>2.4V,輸出低電平=2.0V,輸入低電平

2018-09-20 18:26:45 9456

9456 CMOS電平:CMOS電路輸出高電平為3V~12V,低電平輸出接近0V 計算機的MAX232電平:高電平為-5V到-12V,低電平為+5V到+12V,為負電壓電平

2019-09-09 17:26:00 2

2 晶體管組成了TTL集成電路,TTL大多采用5V電路。用二進制來進行表示的話, 5V正好等于邏輯上的“1”, 0V等于邏輯上的“0”,因此, TTL電平在電路中得以被大星應用。而在此領域中,同樣被大量應用的還有CMOS電平。除了邏輯電平范圍的不同,TTL電平和CMOS電平之間還有哪些不同呢?

2019-08-19 14:20:23 31103

31103 1.CMOS電平:

‘1’邏輯電平電壓接近于電源電壓,‘0’邏輯電平接近于0V。噪聲容限很大

2.TTL電平:

輸出高電平》2.4V,輸出低電平《0.4V。在室溫下,一般輸出高電平是3.5V

2019-09-14 10:52:00 7026

7026

本文檔的主要內容詳細介紹的是TTL和CMOS電平的區別詳細資料說明。

2020-06-05 17:10:31 27

27 在門電路輸入端串聯10K電阻后再輸入低電平,輸入端出呈現的是高電平而不是低電平。因為由TTL門電路的輸入端負載特性可知,只有在輸入端接的串聯電阻小于910歐時,它輸入來的低電平信號才能被門電路識別出來,串聯電阻再大的話輸入端就一直呈現高電平。這個一定要注意。COMS門電路就不用考慮這些了。

2020-08-05 10:41:30 19901

19901

由于晶體管-晶體管邏輯(TTL)和互補金屬氧化物半導體(CMOS)是邏輯電路中的標準電平,因傳統邏輯電平轉換方法中,TTL-CMOS輸入轉換很常見。這種轉換方法簡單,成本低,主要用于低電平至高電平

2020-08-12 16:16:57 3858

3858

由于實現方式簡單,CMOS電平時鐘被廣泛使用(通常頻率在200MHz以內)。但實際應用中由于電源軌的限制經常需要將CMOS信號的電平進行轉化,比方將3.3V轉換成1.8V,或1.8V轉換成1.2V。在此給出一種簡單的轉換電路和計算。

2020-09-08 09:41:29 5071

5071

本篇主要介紹TTL/CMOS電平的互連、OC/OD的互連,其余單端邏輯電平的互連可參考相關器件規范、電平規范。

2021-01-06 17:40:22 20

20 邏輯輸出的高電平最小值VOHMIN(2.4V)卻低于CMOS邏輯輸入高電平的最小值VIHMIN(0.7×VCC=3.5V),換言之,CMOS邏輯可能不能夠識別TTL邏輯高電平(注意“可能”這兩個字)。

2021-01-20 17:14:12 6234

6234

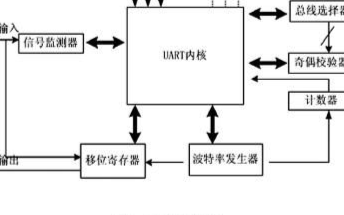

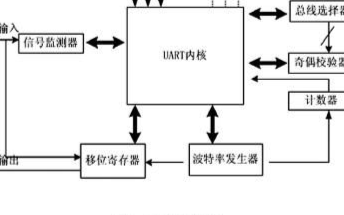

實現RS-232電平和TTL/CMOS電平轉換可以用接口芯片來實現,實現數據的串行到并行轉換用的是UART,它們是實現串行通信必不可少的兩個部分。

2021-03-26 14:19:59 5774

5774

電子發燒友網為你提供什么是TTL電平、CMOS電平?都有哪些區別?資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-29 08:41:19 21

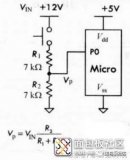

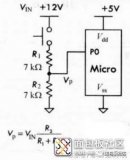

21 可靠的邏輯高電平I/O電路(輸入) 微控制器I/O端口線能承受的最大電壓不超過5V(不同微控制器有所區別),否則有可能燒壞I/O端口。本電路中,即使使用較大的電源電壓,分壓網絡也會送一個安全的(5V

2021-08-16 14:52:33 9694

9694

TTL,CMOS都屬于數字電路。TTL電流控制器件輸出高電平>2.4V輸出低電平<0.4VCMOS電壓控制器件輸出高電平>2.4V輸出低電平<0.4V

2021-11-26 18:51:08 10

10 的平臺,給老司機交流的平臺。所有文章來源于項目實戰,屬于原創。一、電平規范1、名稱解釋Uoh -> 輸出高電平,Uol -> 輸出低電平;Uih -> 輸入高電平,Uil -&g...

2021-11-30 20:21:12 6

6 什么是TTL電平,什么是CMOS電平,他們的區別

2021-11-30 20:51:06 40

40 初學51單片機,可能不太理解復位電路,復位電路有高電平和低電平兩種,C51是高電平復位,現在一般的MCU都是低電平復位。

2021-12-08 11:51:04 15

15 電平轉換也可以叫電壓轉換,它可以解決器件接口中的電平兼容問題。

2022-02-02 17:59:00 2912

2912 單片機最小系統,即單片機能正常工作的最簡單的電路。復位電路是單片機最小系統的組成部分之一。對于不同單片機,復位方式有高電平復位和低電平復位,從而相對應地就有兩種復位電路,高電平和低電平復位電路,本文

2022-01-17 12:38:52 15

15 什么是ttl電平

TTL電平信號被利用的最多是因為通常數據表示采用二進制規定,+5V等價于邏輯"1",0V等價于邏輯"0",這被稱做TTL(晶體管-晶體管邏輯電平)信號系統,這是計算機處理器控制

2022-02-11 15:12:28 14

14 請注意LS和CMOS之間的高電平的不兼容性。

2022-03-11 10:28:15 1788

1788 TTL器件輸出低電平要小于0.8V,高電平要大于2.4V。輸入,低于1.2V就認為是0,高于2.0就認為是1。于是TTL電平的輸入低電平的噪聲容限就只有(0.8-0)/2=0.4V,高電平的噪聲容限為(5-2.4)/2=1.3V。

2022-08-22 10:10:50 13114

13114 什么是TTL電平、CMOS電平、RS232電平?它們有什么區別呢?一般說來,CMOS電平比TTL電平有著更高的噪聲容限。

2023-02-07 14:58:26 6932

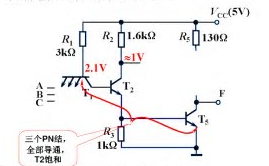

6932 推挽輸出是低電平還是高電平? 推挽輸出器是一種常見的輸出方式。它由負和正三項組成,其中,負電平被連接到PNP晶體管,而正電平被連接到NPN晶體管。當給定輸入信號時,晶體管被開啟或關閉,電流流過負極

2023-08-31 10:26:31 4337

4337 讀取某一個上拉電平信號,它可能輸出是低電平,可能是高電平,可能是方波,并且這個方波不知道頻率何占空比,那么如何來通過程序來判斷呢?高電平和低電平都好說,利用HAL庫讀取即可,如下

2023-11-07 08:00:52 5708

5708

金屬氧化物半導體)技術利用了兩種類型的晶體管:NMOS(負極性金屬氧化物半導體)晶體管和PMOS(正極性金屬氧化物半導體)晶體管。NMOS晶體管只有有源端施加高電平時才能導通,而PMOS晶體管只有有源端施加低電平時才能導通。這種互補配置使得CMOS電路能夠實

2024-01-09 11:25:51 7488

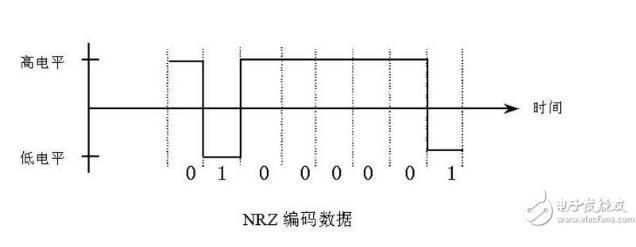

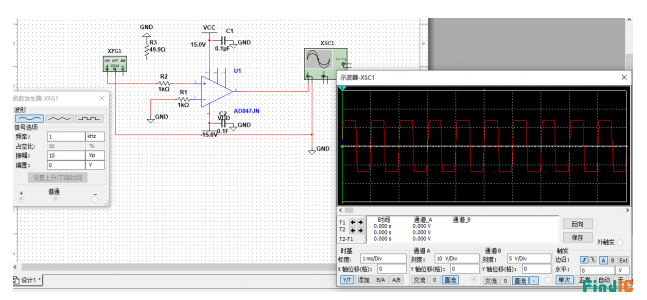

7488 能夠看到,當一個正弦波信號經過比較器出來以后,就成為了一個方波信號(PWM信號)。從廣義的角度上來說,PWM信號是模擬信號,可以所所有的信號都是模擬的,數字信號是我們將其所謂的高電平定義為 1 ,低電平定義為 0 。

2024-02-15 10:41:00 1254

1254

STM32單片機以兼容CMOS與TTL電平。 首先,我們先了解一下CMOS和TTL電平的特性。CMOS和TTL是兩種常見的邏輯電平標準。CMOS電平一般定義為0V至VDD之間的電壓范圍,其中VDD

2024-02-02 13:57:47 6060

6060 )是常用的數字電路家族,兩者都有自己的特點和應用范圍。在介紹如何轉換CMOS電平和TTL電平之前,我們先來了解一下它們的定義和特點。 CMOS電平: CMOS電平是一種用于數字電路傳輸的電壓標準。常見

2024-02-22 11:10:52 5619

5619 半導體)管道組成。在CMOS電路中,輸入信號的高和低電平取決于輸入信號的電壓和電路中的配置。 對于CMOS門電路來說,判斷輸出電平的關鍵是輸入電壓。在理想的情況下,當輸入電壓為高電平時,輸出為低電平;當輸入電壓為低電平時,輸出電平為高電平。這是因為CMOS電路的輸入管道是一個開關,當輸入電壓為高

2024-02-22 11:12:34 7094

7094 在數字電子學中,高電平和低電平是兩種基本的信號狀態,它們分別代表二進制數字1和0。這兩種電平狀態在數字電路設計、通信和計算機系統中扮演著至關重要的角色。 高電平和低電平的定義 高電平(High

2024-07-23 11:25:49 14441

14441 芯片引腳懸空時的電平狀態(高電平或低電平)并不是一個固定答案,它取決于多個因素,包括芯片類型、生產廠家、引腳特性以及周圍電路環境等。 首先,從邏輯門電路的角度來看,當引腳懸空時,其電平狀態可能會

2024-08-28 09:55:16 6261

6261 CMOS(互補金屬氧化物半導體)電平接口,作為電子電路設計中的一種重要接口類型,其獨特的半導體特性和廣泛的應用場景使得我們對其并不陌生。下面將為大家介紹CMOS電平接口。 在正常情況下,CMOS電平

2024-09-30 17:03:41 1422

1422 (黃色插頭)。這些連接器通常用于連接家庭影院系統、音響設備、游戲機和其他多媒體設備。 關于RCA輸出是低電平還是高電平,這實際上是一個關于信號電平的問題。在電子學中,電平通常指的是信號的電壓大小。低電平和高電平是相對的術語,它們描述了信號

2024-10-17 11:01:50 3879

3879 在現代電子系統中,數字電路扮演著至關重要的角色。這些電路處理的是二進制信號,即由邏輯“1”和邏輯“0”組成的信號。這些邏輯狀態通常通過電壓水平來表示,其中高電平代表邏輯“1”,低電平代表邏輯“0

2024-10-17 14:56:42 11416

11416 (Bipolar Junction Transistor, BJT)的,它定義了邏輯“0”和邏輯“1”的電壓范圍。在TTL電路中,邏輯“0”通常對應于0V到0.8V的電壓范圍,而邏輯“1”則對應于2V到5V。這種電平標準使得TTL電路在電壓變化時能夠提供清晰的邏輯狀態區分。 CMOS電平標準則是基于金屬氧化

2025-01-16 09:43:59 2847

2847 逐漸成熟,并成為數字電路設計中的一個標準。 TTL電平標準的定義 TTL電平標準定義了數字信號的高低電平電壓范圍。在TTL電平標準中,高電平(邏輯1)通常定義為2.7V至5V,而低電平(邏輯0)則定義為0V至0.8V。這些電壓范圍確保了數字信號的清晰區

2025-01-16 09:46:44 3507

3507 德州儀器(Texas Instruments)在20世紀50年代末開發。TTL電平以其簡單、可靠和成本效益高而聞名,盡管隨著技術的發展,它已經被一些更新的標準所取代,但在某些應用中仍然廣泛使用。 TTL電平的特點 電壓范圍 :TTL電平定義了兩個電壓范圍來表示邏輯

2025-01-16 10:21:08 2016

2016 在電子工程領域,信號電平的轉換是一個常見的需求,尤其是在不同技術標準之間。TTL(晶體管-晶體管邏輯)電平和高電平信號是兩種不同的電平標準,它們在電壓水平和應用場景上有所不同。 TTL電平的定義

2025-01-16 10:28:42 1598

1598

電子發燒友App

電子發燒友App

評論