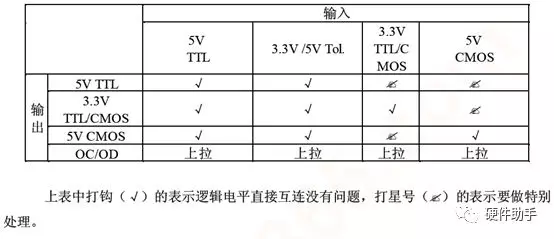

本篇主要介紹TTL/CMOS電平的互連、OC/OD的互連,其余單端邏輯電平的互連可參考相關器件規范、電平規范。

1、TTL/CMOS互連

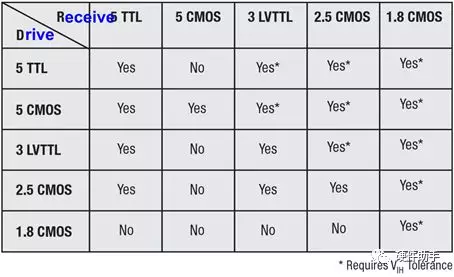

常用的TTL和CMOS電平主要是5V TTL、5V CMOS、3.3VTTL、3.3V CMOS、3.3V/5V Tol(輸入時3.3V邏輯電平,但是可以接受5V的信號輸入)等,隨著處理器電壓越來越低,現在1.8V CMOS等低電壓的邏輯電平也越來越普及了。

針對各種單端邏輯電平,只要上一級的輸出電壓不滿足下一級的輸入電壓,就不能直接進行互連,后續會專門介紹邏輯電平的轉換。

|

5V TTL門作驅動源 |

驅動3.3V TTL/CMOS |

通過LVC/LVT系列器件(為TTL/CMOS邏輯電平輸入,LVTTL邏輯電平輸出)進行轉換。 |

|

驅動5V CMOS |

上拉5V電阻,或使用AHCT系列器件(為5VTTL輸入、5VCMOS輸出)進行轉換。 |

|

|

5V CMOS門作驅動源 |

驅動3.3V TTL/CMOS |

通過LVC/LVT器件(輸入是TTL/CMOS邏輯電平,輸出是LVTTL邏輯電平)進行轉換。 |

|

3.3V TTL/CMOS門作驅動源 |

驅動5V CMOS |

使用AHCT系列器件(為5V TTL輸入、5VCMOS輸出)進行轉換(3.3V TTL電平(LVTTL)與5V TTL電平可以互連)。 |

|

驅動2.5V CMOS |

使用LV、LVC、AVC、ALVT系列器件來進行3.3VTTL/CMOS邏輯電平到2.5V CMOS邏輯電平的轉換。 |

|

|

2.5V CMOS門作驅動源 |

驅動3.3V TTL/CMOS |

使用雙軌器件SN74LVCC3245A來進行2.5V邏輯電平到3.3V邏輯電平的轉換。 |

***上表中的所有互連方式都可以通過外部MOS管等分離器件搭建。

2、OC/OD互連

針對OC/OD邏輯門,為了保證輸出高電平的值,必須進行外部上拉處理,上拉電阻的選取可以參考相關總線的標準,也可以參考《I2C Bus Pull up Resistor Calculation》、《Choosing an Appropriate Pull-up/Pull-down Resistor for Open Drain Outputs》等文章。相同電壓的OC/OD邏輯電平可以直接互連,不同電壓的OC/OD需要進行電平轉換,可以采用獨立的MOS管搭建,也可以采用專門的OC/OD總線轉換芯片實現(專用芯片的節本架構也是基于MOS管的,只是多了外圍電路以及一些輔助的功能電路)。下面就針對采用MOS管進行OC/OD電平轉換進行介紹,使用專用芯片進行轉換的方式后續再介紹。

針對上述電路分析如下:

a、3.3V→5V轉換過程:

- 3.3V端輸出低電平時(0V),MOS管導通,5V端輸出是低電平(0V);

- 3.3V端輸出高電平時(3.3V),MOS管截止,5V端輸出是高電平(5V上拉);

- 3.3V端輸出高阻時(OC/OD),MOS管截止,5V端輸出是高電平(5V上拉)。

b、5V→3.3V轉換過程:

- 5V端輸出低電平時(0V),MOS管內的寄生二極管導通,從而使MOS管導通,3.3V端輸出是低電平(0V);

- 5V端輸出高電平時(5V),MOS管截止,3.3V端輸出是高電平(3.3V上拉);

- 5V端輸出高阻時(OC/OD),MOS管截止,3.3V端輸出是高電平(3.3V上拉)。

以上就是針對TTL/CMOS,OC/OD邏輯電平的互連介紹,后續會針對專門的邏輯電平轉換進行介紹。

編輯:hfy

-

CMOS

+關注

關注

58文章

6224瀏覽量

243251 -

TTL

+關注

關注

7文章

557瀏覽量

74949 -

邏輯電平

+關注

關注

0文章

205瀏覽量

15141 -

寄生二極管

+關注

關注

0文章

49瀏覽量

3526

發布評論請先 登錄

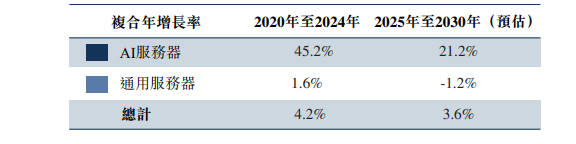

從內存接口到PCIe/CXL、以太網及光互連,高速互連芯片市場分析

單片機TTL和CMOS電平知識

淺談DDR的邏輯電平標準

MDD 邏輯IC的邏輯電平不兼容問題與解決方案

TTL光模塊電平標準是什么

光模塊TTL電平是什么?

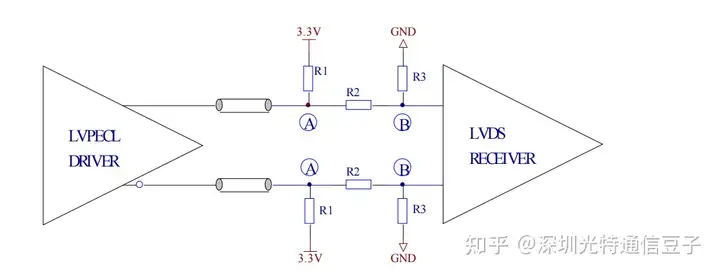

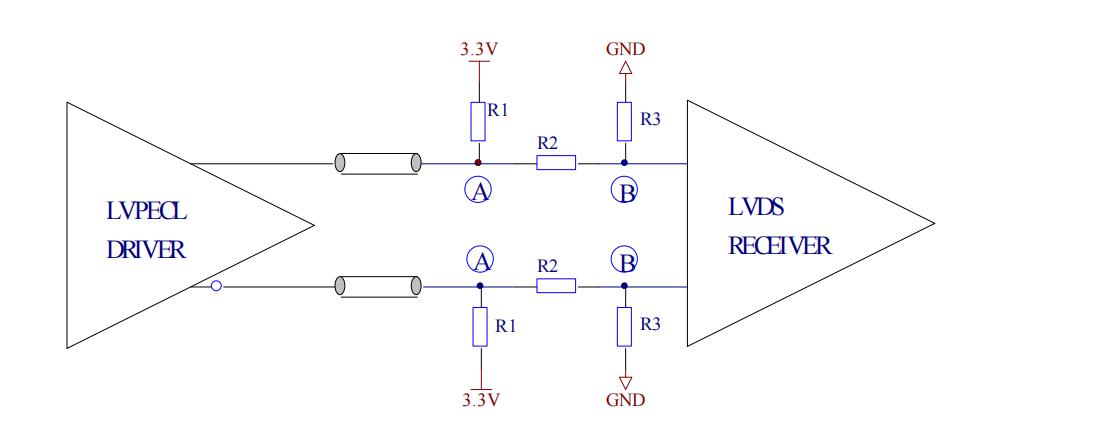

LVPECL 與 LVDS 及 PECL 與 LVDS 的互連技術解析

LVPECL與LVDS電平互連:直流與交流耦合設計指南

TTL/LVTTL:供電電源、電平標準及使用注意事項

XSR芯片間互連技術的定義和優勢

互連層RC延遲的降低方法

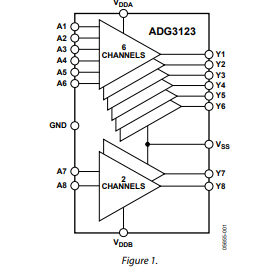

ADG3123 8通道CMOS邏輯轉高壓電平轉換器技術手冊

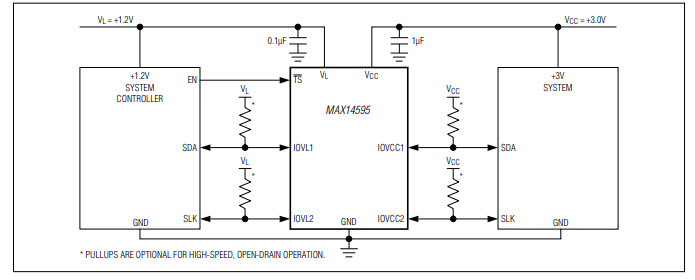

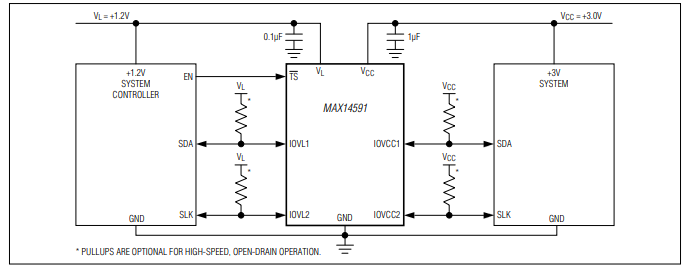

MAX14595高速、漏極開路邏輯電平轉換器技術手冊

邏輯電平TTL/CMOS電平的互連、OC/OD的互連規范

邏輯電平TTL/CMOS電平的互連、OC/OD的互連規范

評論