推挽輸出是低電平還是高電平

推挽輸出器是一種常見的輸出方式。它由負和正三項組成,其中,負電平被連接到PNP晶體管,而正電平被連接到NPN晶體管。當給定輸入信號時,晶體管被開啟或關閉,電流流過負極和正極之間的負載,該負載可以是電燈、電機、電子設備等。那么,推挽輸出是低電平還是高電平呢?這取決于使用情況和輸入信號。

首先,我們需要了解推挽輸出的基本工作原理。當給定輸入信號時,晶體管會被打開或關閉,取決于信號的極性。如果輸入信號是高電平信號,那么NPN晶體管將被打開,而PNP晶體管將被關閉,因此,負載將連接到地線,同時輸出將保持低電平狀態。反之,如果輸入信號是低電平信號,那么PNP晶體管將被打開,而NPN晶體管將被關閉,因此,負載將連接到正極,同時輸出將保持高電平狀態。

在實踐中,推挽輸出通常用于數字信號的放大和反相信號的生成。例如,在數字電路中,經常使用推挽輸出作為緩沖器或放大器,以增加信號的帶寬和減少失真。在音頻電路中,推挽輸出通常被用于放大音頻信號,因為它可以提供大量功率,同時保持音質的高保真度。

此外,推挽輸出還可以用于直流電機控制。在這種應用中,推挽輸出器被用來反轉直流電機的轉向,并改變其轉速。例如,如果您想將電機的轉向從順時針旋轉變為逆時針旋轉,那么您可以通過改變輸入信號的極性來實現。當電機開始運轉時,它消耗的電流會產生一定的電磁場,該電磁場帶有磁極性,可以改變磁力的方向和大小,從而實現電機的轉向和調速。

總而言之,推挽輸出是一種非常實用的輸出方式,可以用于各種不同的應用。它可以提供高效、可靠的電源輸出,同時可以幫助您控制電機、放大信號和反相信號,讓您的電子設備更加高效、靈活和可靠。因此,如果您需要推挽輸出器的幫助,我們建議您選擇高質量、可靠的設備,并確保您正確地理解和使用推挽輸出器的基本原則和操作。

-

PNP晶體管

+關注

關注

0文章

33瀏覽量

12716 -

低電平

+關注

關注

1文章

238瀏覽量

13987 -

輸出器

+關注

關注

0文章

11瀏覽量

8137 -

高電平

+關注

關注

6文章

225瀏覽量

22820 -

推挽輸出

+關注

關注

0文章

89瀏覽量

6882

發布評論請先 登錄

一個MOSFET電平轉換電路原理

請問為什么M0519引腳的某些部分在配置為GPIO功能后無法將輸出控制到高電平或低電平狀態?

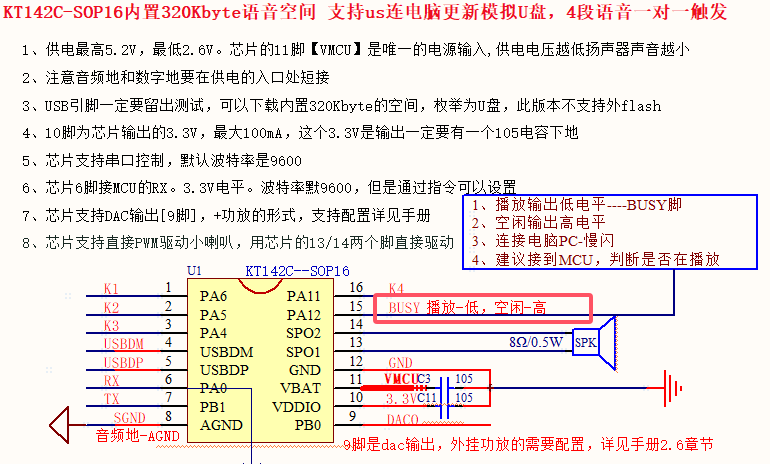

為什么 KT142C 芯片 BUSY 腳空閑高電平僅 0.2V?附低功耗模式配置指南

電平轉換電路設計原理和常見問題及解決辦法

DS1232LPS-2+T&R,在什么情況下,5腳RST會一直輸出高電平?

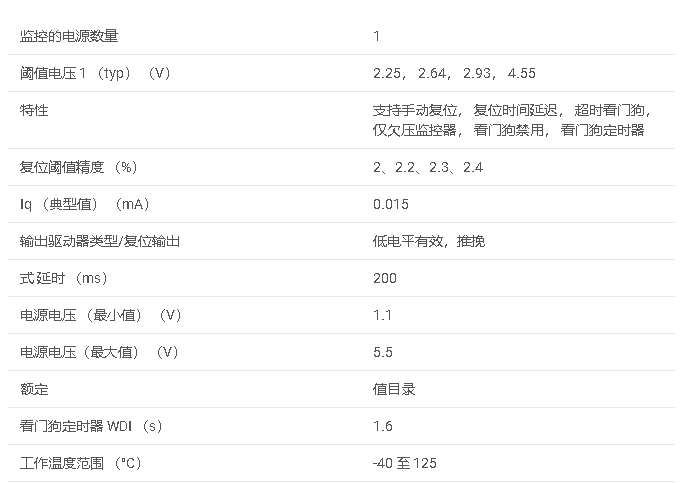

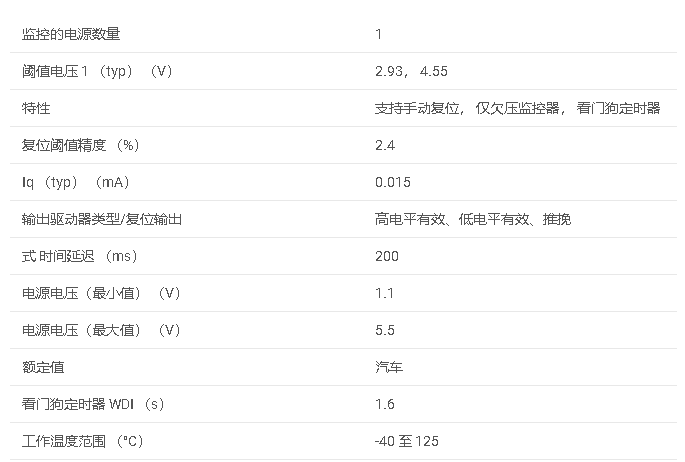

TPS3823 低電平,推挽式,電壓監控器(復位IC),帶1.6秒看門狗和手動復位數據手冊

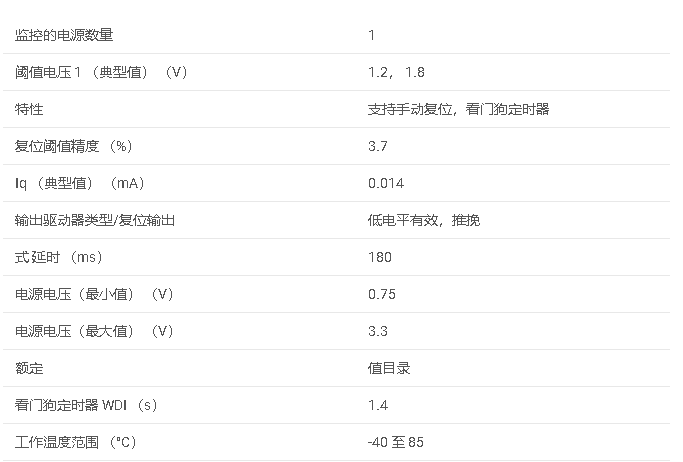

TPS3123 低電平,推挽式,電源電壓監控器,帶看門狗定時器和手動復位數據手冊

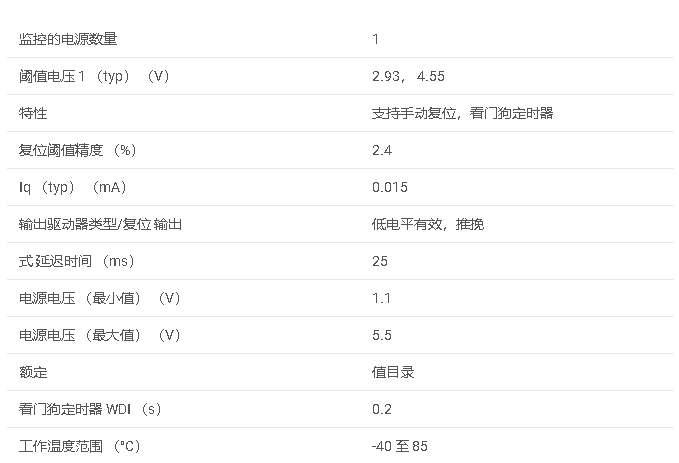

TPS3820 低電平,推挽式,電壓監控器(復位IC),帶0.2秒看門狗和手動復位數據手冊

TPS3824-Q1 高電平和低電平有效,汽車電壓監控器(復位IC)帶看門狗和手動復位技術手冊

推挽輸出是低電平還是高電平?

推挽輸出是低電平還是高電平?

評論