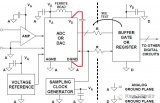

今天我們將討論同等重要并相關的主題:如何通過電源去耦來保持電源進入集成電路(IC)的各點的低阻抗。

2017-08-28 16:52:51 2185

2185

模數轉換器的電源去耦問題解析

盡管高速ADC給電源帶來的總負載是穩定的,但需要電流以ADC采樣速率和此頻率的諧波快速跳變。由于

2011-01-01 12:30:11 1240

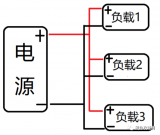

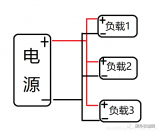

1240 電子電路中常用的電源就是以上兩種,這兩種各有優缺點,使用場合也有差別,并且每種都可繼續細分為多種子類,這已經超出了本篇電源去耦的范疇。從上面簡單的介紹中我們可以看出這兩種實際的電源都是有局限性的。

2018-05-29 08:34:45 14268

14268

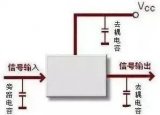

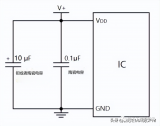

去耦(decoupling)電容也稱退耦電容,一般都安置在元件附近的電源處,用來濾除高頻噪聲,使電壓穩定干凈,保證元件的正常工作。

2022-10-24 10:46:49 5566

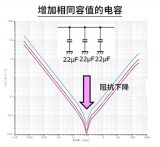

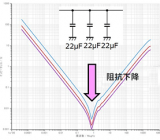

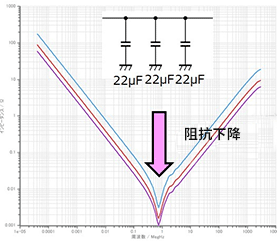

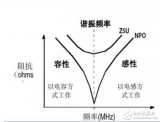

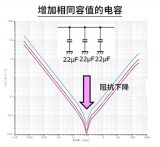

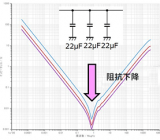

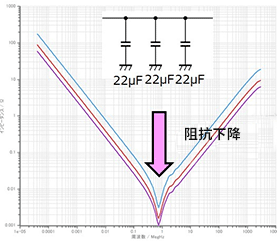

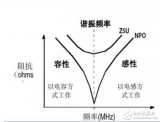

5566 去耦電容的有效使用方法之一是用多個(而非1個)電容進行去耦。使用多個電容時,使用相同容值的電容時和交織使用不同容值的電容時,效果是不同的。

2023-08-02 12:34:43 870

870

去耦電容有效使用方法分為兩種: 使用多個去耦電容 使用多個去耦電容時,使用相同容值的電容時和交織使用不同容值的電容時,效果是不同的。 ①使用多個容值相同的電容時 當增加容值相同的電容后,阻抗在整個

2023-08-07 09:43:14 2055

2055

使用多個去耦電容時,使用相同容值的電容時和交織使用不同容值的電容時,效果是不同的。

2023-08-23 16:44:42 1651

1651

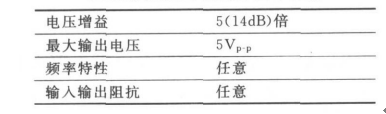

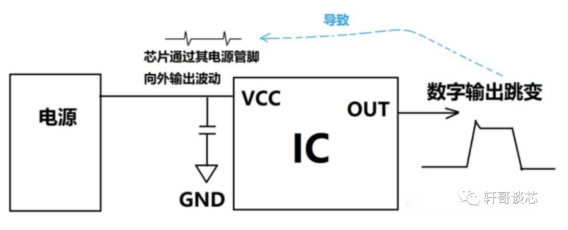

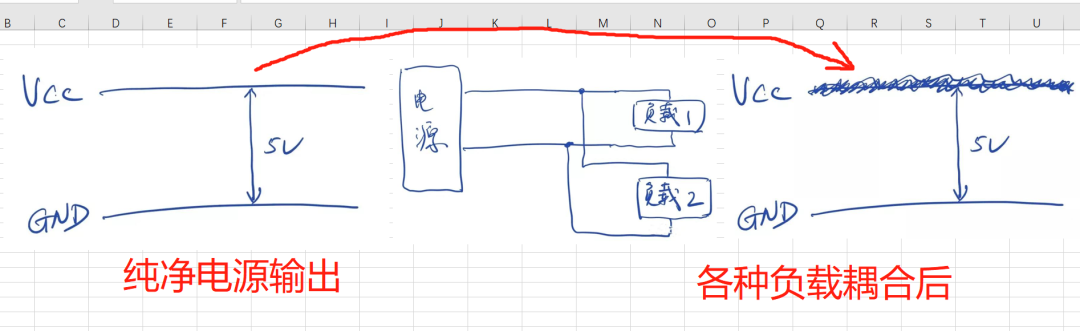

從電源上看,沒有去耦電容的時候如左側的波形,加上了去耦電容之后變成了右側的樣子,供電電壓的波形變得干凈了,我們稱該電容的作用是去掉了耦和在干凈的DC上的噪聲,所以該電容被稱之為去耦電容。

2024-03-27 14:08:48 7133

7133

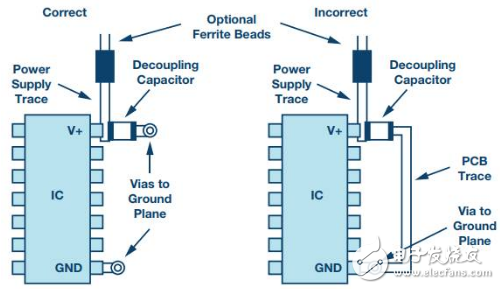

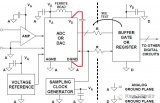

何謂正確去耦?有何必要性? 如果電源引腳上存在紋波和/或噪聲,大多數IC都會有某種類型的性能下降。數字IC的噪聲裕量會降低,時鐘抖動則可能增加。對于高性能數字IC,例如微處理器和FPGA,電源額定容

2018-12-05 09:21:51

在做高速電路設計的時候,為什么要有那么多去耦電容?到底什么是去耦?到底需要多大的去耦電容呢?為什么是很多個小電容并聯而不是用一個大電容(值是一樣大的啊)?為什么說小電容要靠近電源管腳而大電容可以

2019-05-07 06:22:23

去耦陶瓷電容在電源和地引腳的作用是什么?

2023-04-21 18:07:13

電源去耦電容為何要接近IC電源引腳?是什么原因呢?

2023-04-21 17:36:30

電源去耦的原因是什么實際電路常用的電源器件實際電源與理想電源的差距是什么

2021-03-17 07:22:40

2019.7.6 電源去耦設計原因:在直流電源回路中,負載的變化會引起電源噪聲。例如在數字電路中,當電路從一個狀態轉變為另一種狀態時,就會在電源線上產生一個很大的尖峰電流,形成瞬變的噪聲電壓。配置去

2021-12-31 08:05:14

為什么要重視電源噪聲問題?電源噪聲是如何產生的?電源系統去耦如何設計?

2021-03-11 07:01:30

什么是電源退耦?電源退耦是如何去完成的?

2021-07-19 06:28:32

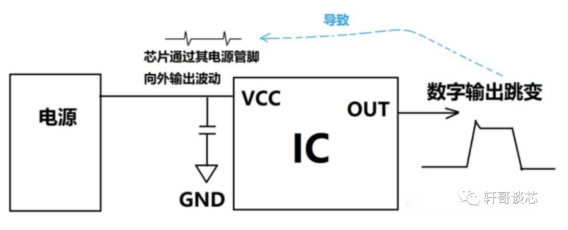

1.耦合機理及去耦需求集成電路芯片都有電源引腳,有的甚至有多個電源電壓和模擬數字混合電源。無論電源引腳數量如何,每路電源都有其允許范圍,包括推薦工作范圍和最大絕對值。為防止芯片損壞、保持正常工作

2021-11-17 07:42:53

手冊中可能沒有給出實際的PSRR,數據轉換器和其他混合信號IC的性能也會隨著電源上的噪聲而降低。電源噪聲也會以多種方式影響數字電路,包括降低邏輯電平噪聲容限,由于時鐘抖動而產生時序錯誤。適當的局部去耦

2018-10-19 10:49:11

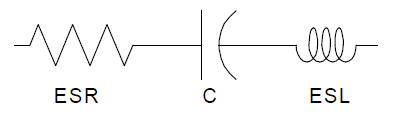

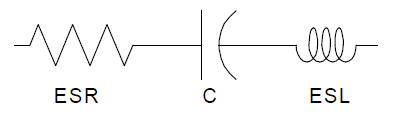

自諧振頻率高于最高目標頻率的電容,可確保有用值符合需要。薄膜型電容一般使用繞線,增加了電感,因此不適合電源去耦應用。此類型更常用于音頻應用,此時需要極低電容和電壓系數。圖3. 去耦對AD8000

2018-10-19 10:58:00

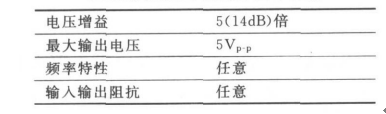

淺談電源去耦系列第一篇,希望從定性的角度談談自己對電源去耦的理解。希望大家支持,不足之處也請各位多多指正。淺談電源去耦——電源去耦的原因理想的電源:“理想的電源”的電壓是穩定不變的,沒有任何噪聲

2019-02-28 06:30:00

請問電源去耦和電源濾波是一回事嗎?

2023-04-21 17:42:23

IntroductionManufacturing test engineersoften face the challenge of testingmultiple UUT’s (Units

2010-07-22 14:57:43 6

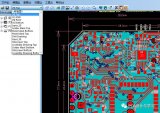

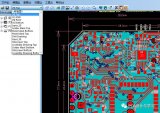

6 工程師們在設計PCB電源分配系統的時候,首先把整個設計分成四個部分:電源(電池、轉換器或者整流器)、PCB、電路板去耦電容和芯片去耦電容。本文將

2007-10-16 12:49:34 910

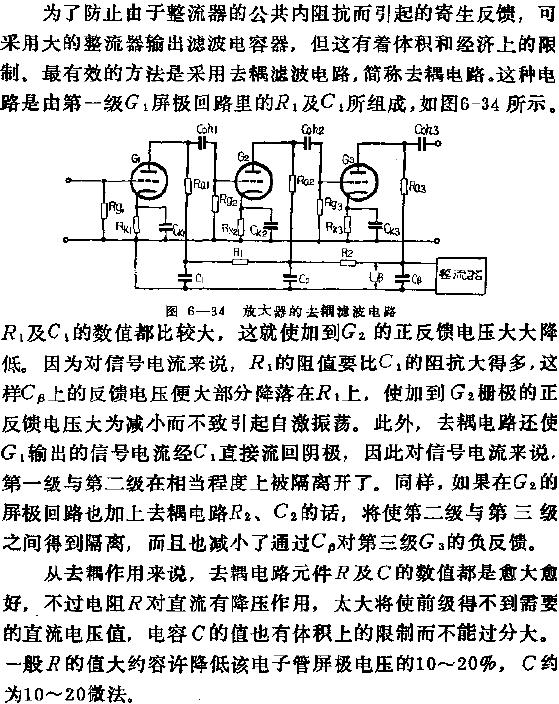

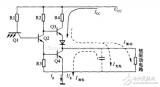

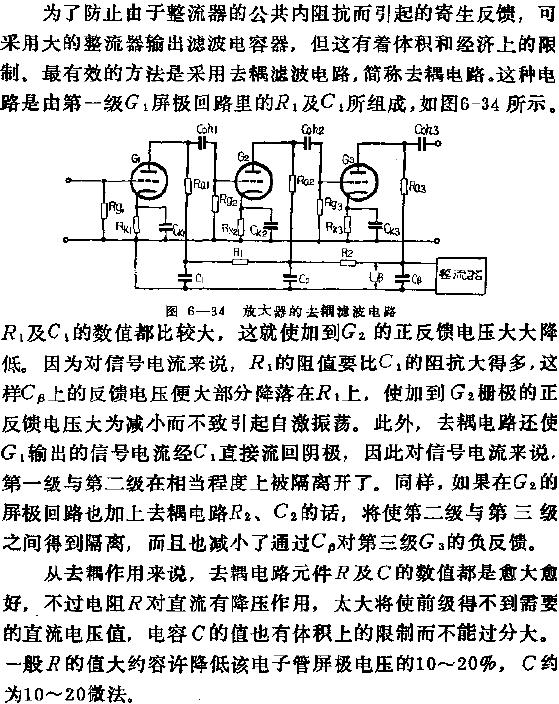

910 放大器的去耦濾波電路

2009-01-12 16:14:05 2464

2464

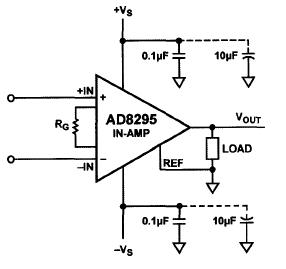

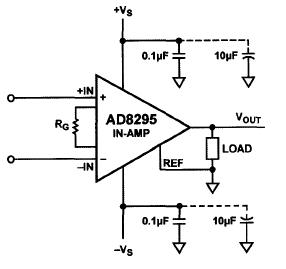

AD8295電源去耦電路及REF與輸出對地連接電路圖

2009-08-09 22:12:02 2427

2427

每個集成運放的電源引線,一般都應采用去耦旁路措施,即從電源引線端到地跨接一個高性能的電容,為此電子發燒友為您提供了運放電源去耦旁路圖!

2011-06-27 09:58:42 4515

4515

數字IC電源靜噪和去耦應用手冊,各類電容器和EMI 靜噪濾波器用于電源與數字IC 的連接。通過形成去耦電路充當濾波器,在連接IC 電源端子和配電網(PDN)的連接處,功率完整性(PI)

2011-11-21 16:00:20 128

128 電容去耦的一個重要問題是電容的去耦半徑。大多數資料中都會提到電容擺放要盡量靠近芯片,多數資料都是從減小回路電感的角度來談這個擺放距離問題。確實,減小電感是一個重要

2011-11-28 18:06:04 2944

2944 耦電容器的作用你知道嗎?在眾多電路設計的應用中都會用到去耦電容器,但設計者也往往嫌麻煩而省略了去耦電容器的使用。

2014-09-16 10:51:52 2204

2204 數字IC電源靜噪與去耦應用手冊

2017-01-14 12:39:33 10

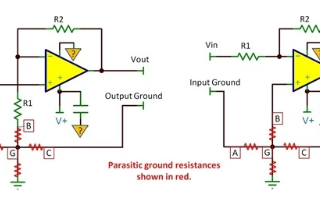

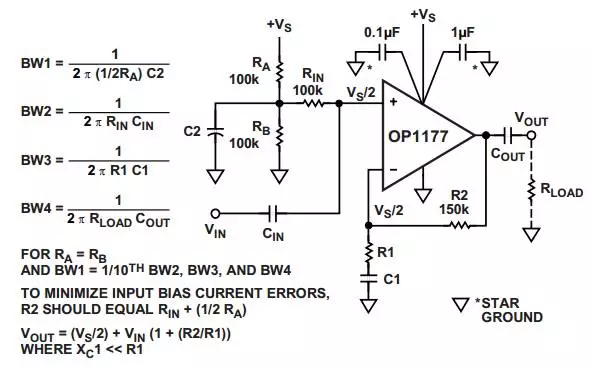

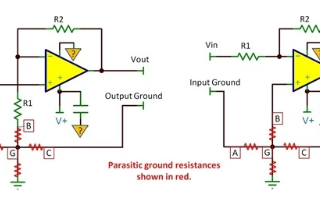

10 翻譯: TI信號鏈工程師 Michael Huang (黃翔) 以前談到電源去耦,我警告過糟糕的去耦會增加放大器的失真。一位讀者問了一個有趣的問題,去耦電容的接地腳應該在哪里接地才能消除這個問題呢?這個問題升級到關于正確接地的技術。

2017-04-08 07:42:11 7092

7092

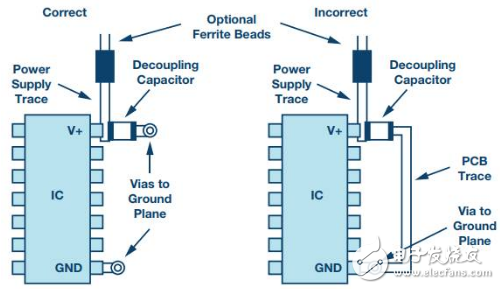

去耦電容與器件非常接近,因此電流路徑的電感很小。在暫態過程中,該電容器可在非常短的時間內向器件提供超大量的電流。未采用去耦電容的器件無法提供暫態電流,因此放大器的內部節點會下垂(通常稱為干擾)。無去耦電容的器件其內部電源干擾會導致器件工作不連續,原因是內部節點未獲得正確的偏置。

2017-09-21 10:41:54 2

2 電容去耦的一個重要問題是電容的去耦半徑。大多數資料中都會提到電容擺放要盡量靠近芯片,多數資料都是從減小回路電感的角度來談這個擺放距離問題。確實,減小電感是一個重要原因,但是還有一個重要的原因大多數

2017-11-12 10:53:40 7402

7402

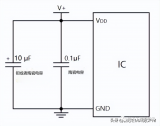

利用去耦電容濾除電路板上電源的高頻噪聲是工程中常用的方法。好的高頻去耦電容電路可去除高達1GHz的高頻成分。設計印制電路板的時,每個集成電路的電源和地之間都要加一個去耦電容。通常,瓷介電容和多層瓷介電容的高頻特性較好。

2017-11-12 11:24:47 13107

13107

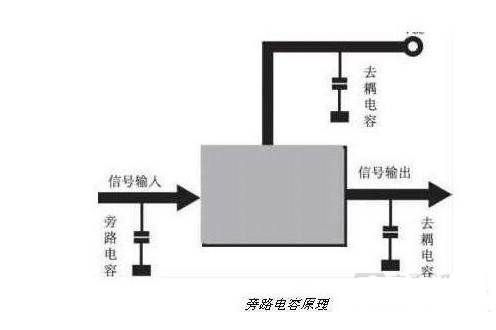

去耦電容是電路中裝設在元件的電源端的電容,此電容可以提供較穩定的電源,同時也可以降低元件耦合到電源端的噪聲,間接可以減少其他元件受此元件噪聲的影響。在電子電路中,去耦電容和旁路電容都是起到抗干擾的作用。

2017-11-27 16:35:50 3875

3875

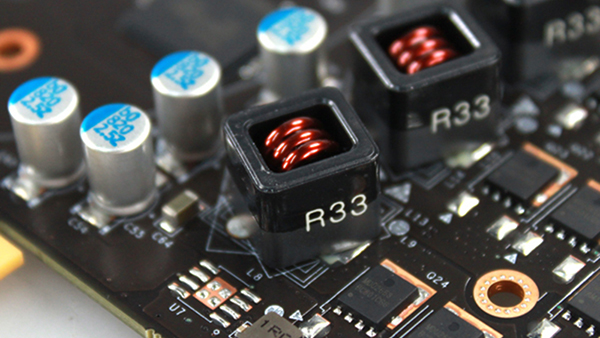

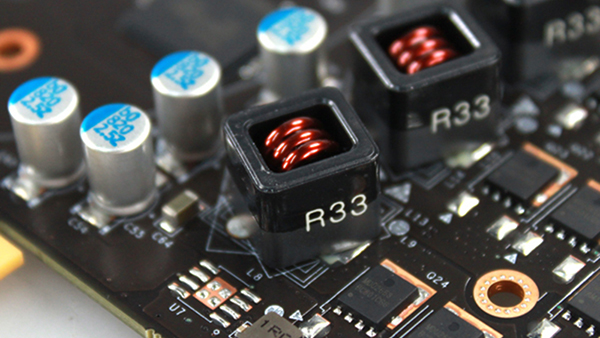

去耦電容的容值計算和布局布線有源器件在開關時產生的高頻開關噪聲將沿著電源線傳播。去耦電容的主要功能就是提供一個局部的直流電源給有源器件,以減少開關噪聲在板上的傳播,和將噪聲引導到地。

去耦電容

2018-01-19 16:23:19 1094

1094

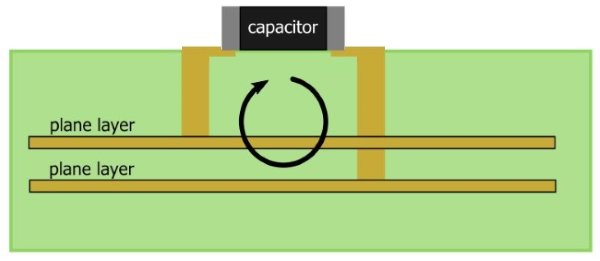

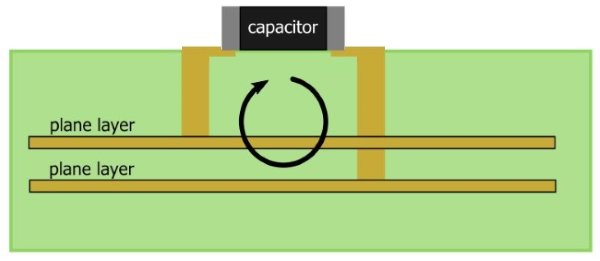

多層板設計板級去耦時,為了達到最好的板級去耦效果,一般在做疊層設計時把電源層和地層設計成相鄰的層。相鄰的層降低了電源?地平面的分布阻抗。從平板電容的角度來分析,由電容計算公式C=εs/4πkd可以

2018-04-18 14:34:26 6284

6284

SOIC的去耦局部的高頻濾波器可以優化小小效果,去耦電容 可以減小回路電感經驗法則

2019-02-27 16:03:57 5686

5686

去耦電容是電路中裝設在元件的電源端的電容,此電容可以提供較穩定的電源,同時也可以降低元件耦合到電源端的噪聲,間接可以減少其他元件受此元件噪聲的影響。去耦電容和旁路電容都是起到抗干擾的作用,電容所處

2019-08-09 17:33:00 5

5 去耦電容是電路中裝設在元件的電源端的電容,此電容可以提供較穩定的電源,同時也可以降低元件耦合到電源端的噪聲,間接可以減少其他元件受此元件噪聲的影響。

2019-07-03 14:37:43 10389

10389 在上一篇文章中,我們探討了是否連接電容器的問題通過走線或通過一對過孔將電容去耦到IC電源引腳。我們看到通孔技術是優越的,因為它降低了電感,當我們試圖確保去耦電容在50-100 MHz的頻率下有效時,電感是我們必須克服的主要障礙。高達數百兆赫。

2019-09-15 15:12:00 5165

5165

由于去耦電容器在高頻時的阻抗將會減小到其自諧振頻率,因而可以有效地除去信號線中的高頻噪聲,同時相對于低頻來說,對能量沒有影響,所以可在每一個集成電路的電源地腳之間加一個大小合適的去耦電容器。

2019-10-17 10:15:09 20966

20966

以前談到電源去耦,我警告過糟糕的去耦會增加放大器的失真。一位讀者問了一個有趣的問題,去耦電容的接地腳應該在哪里接地才能消除這個問題呢?

2020-07-14 14:23:29 1816

1816

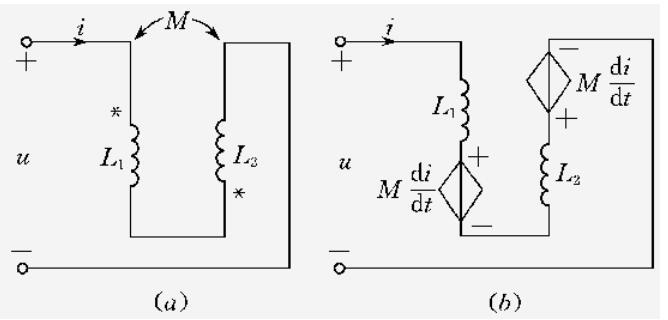

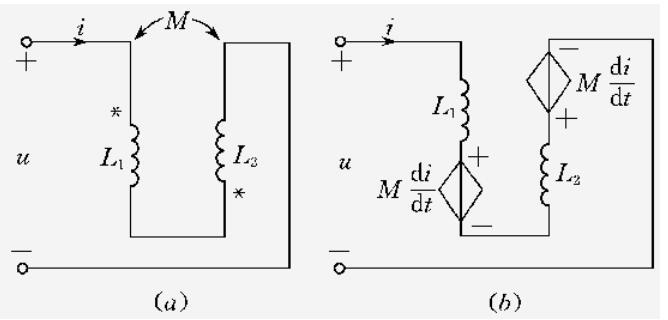

本文主要闡述了耦合電感去耦等效方法。

2020-08-13 10:11:37 84253

84253

另外,變化的電流經過PDS的互連線的阻抗時引起電壓降,這個就是“軌道塌陷”。有了這個理論基礎之后,我們就可以明確去耦的目的,去耦電容的目的就是為了盡量減小這兩種作用對電壓的影響。

2020-08-27 17:49:27 7251

7251

淺談電源去耦系列第一篇,希望從定性的角度談談自己對電源去耦的理解。也是Andrew的第一篇博文,希望大家支持,不足之處也請各位多多指正淺談電源去耦——電源去耦的原因

2020-09-14 08:00:00 1

1 去耦電容是電路中裝設在元件的電源端的電容,此電容可以提供較穩定的電源,同時也可以降低元件耦合到電源端的噪聲,間接可以減少對其他元件的噪聲影響。 市場上去耦電容有很多類型,但每種電容的電氣特性、極性

2020-12-03 11:25:53 5343

5343 。這是因為提供給組件的電壓遠遠不夠理想。與理論上描述的完美水平線不同,即使您擁有最干凈的電源,實際應用中的電壓讀數也會波動。 去耦起到儲能器的作用,并以兩種方式穩定電壓。當電壓增加到額定值以上時,去耦電容器會吸收

2020-12-23 16:46:46 4677

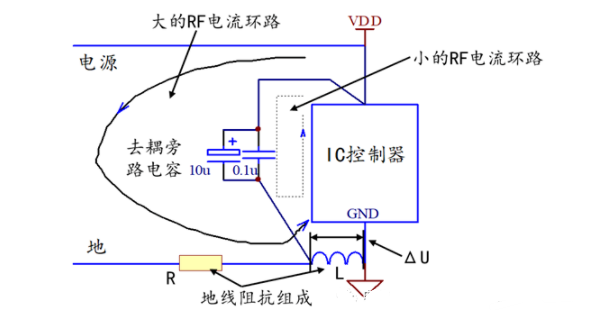

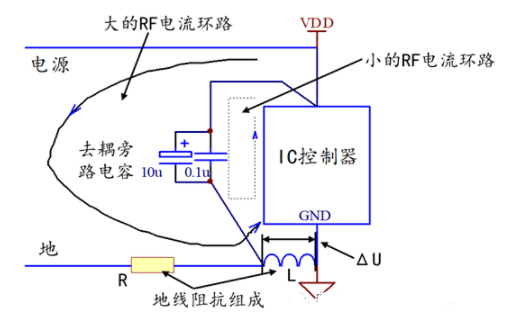

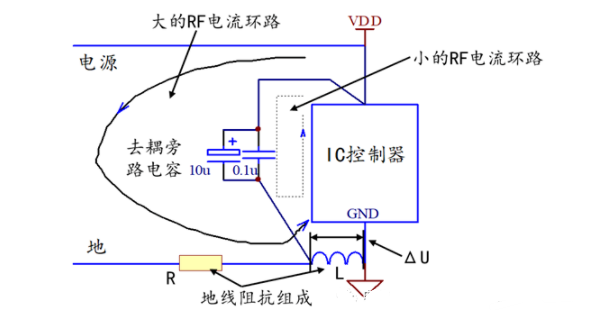

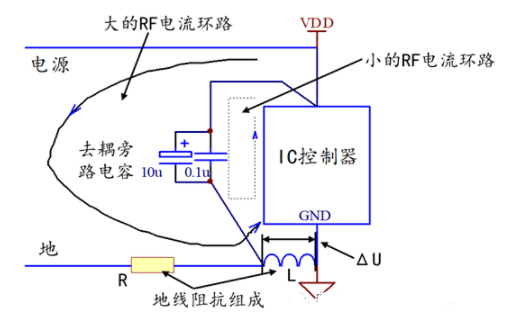

4677 能量從高頻器件的電源端泄放到電源分配網絡。去耦電容也為器件和元件提供一個局部的直流源,這對減小電流在板上傳播浪涌尖峰很有作用。 在數字電路及IC控制器電路中,必須要進行電源去耦。當元件開關消耗直流能量時,沒有去

2021-01-07 14:30:28 3351

3351

設計中,去耦電容器是必需品。這是因為提供給組件的電壓遠遠不夠理想。與理論上描述的完美水平線不同,即使擁有最干凈的電源,實際應用中的電壓讀數也會波動。 去耦起到儲能器的作用,并以兩種方式穩定電壓。當電壓增加到額定值以

2020-11-14 10:51:24 5007

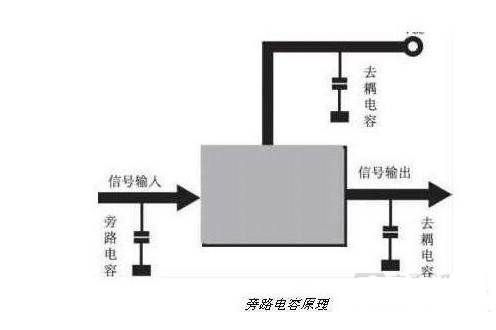

5007 旁路和去耦是指防止有用能量從一個電路傳到另一個電路中,并改變噪聲能量的傳輸路徑,從而提高電源分配網絡的品質。它有三個基本概念:電源、地平面,元件和內層的電源連接。去耦是當器件進行高速開關時,把射頻能量從高頻器件的電源端泄放到電源分配網絡

2020-12-26 04:00:19 1011

1011 一,什么是PCB中的板級去耦呢?

板級去耦其實就是電源平面和地平面之間形成的等效電容,這些等效電容起到了去耦的作用。主要在多層板中會用到這種設計方法,因為多層板可以構造出電源層和地層,而一層板

2022-02-10 11:34:48 2294

2294 一,什么是PCB中的板級去耦呢?

板級去耦其實就是電源平面和地平面之間形成的等效電容,這些等效電容起到了去耦的作用。主要在多層板中會用到這種設計方法,因為多層板可以構造出電源層和地層,而一層板

2022-02-10 10:03:29 1780

1780 一,什么是PCB中的板級去耦呢?

板級去耦其實就是電源平面和地平面之間形成的等效電容,這些等效電容起到了去耦的作用。主要在多層板中會用到這種設計方法,因為多層板可以構造出電源層和地層,而一層板與兩層

2021-02-19 06:38:42 14

14 一,什么是PCB中的板級去耦呢?

板級去耦其實就是電源平面和地平面之間形成的等效電容,這些等效電容起到了去耦的作用。主要在多層板中會用到這種設計方法,因為多層板可以構造出電源層和地層,而一層板與兩層

2021-03-14 06:08:22 22

22 什么是旁路電容、去耦電容、濾波電容?作用是什么??濾波電容——用在電源整流電路中,用來濾除交流成分,使輸出的直流更平滑。 去耦電容——用在放大電路中不需要交流的地方,用來消除自激,使放大器穩定工作

2021-03-17 01:17:50 3450

3450 MT-101:去耦技術

2021-03-21 10:02:14 1

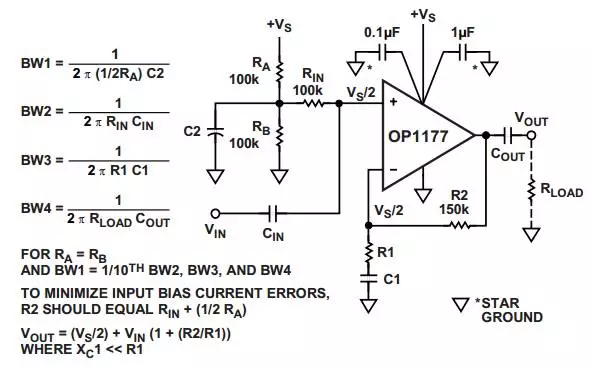

1 AN-581: 單電源應用中的偏置和去耦運算放大器

2021-03-21 11:51:03 6

6 旁路和去耦是指防止有用能量從一個電路傳到另一個電路中,并改變噪聲能量的傳輸路徑,從而提高電源分配網絡的品質。它有三個基本概念:電源、地平面,元件和內層的電源連接。

2021-03-31 06:02:01 3

3 是實際電源總線電壓所允許的降低,單位為V。 I是以A(安培)為單位的最大要求電流; ⊿t是這個要求所維持的時間。 去耦電容容值計算方法:推薦使用遠大于1/m乘以等效開路電容的電容值。 此處m是在IC的電源插針上所允許的電源總線電壓變化的最大百分

2021-04-06 10:59:06 3488

3488 電子發燒友網為你提供如何電源去耦?資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-17 08:41:51 7

7 是實際電源總線電壓所允許的降低,單位為V。 I是以A(安培)為單位的最大要求電流; ⊿t是這個要求所維持的時間。 去耦電容容值計算方法:推薦使用遠大于1/m乘以等效開路電容的電容值。 此處m是在IC的電源插針上所允許的電源總線電壓變化的最大百分

2021-06-13 10:15:00 1576

1576 旁路電容、去耦電容、濾波電容的作用介紹 什么是旁路電容、去耦電容、濾波電容?作用是什么? 濾波電容——用在電源整流電路中,用來濾除交流成分,使輸出的直流更平滑。去耦電容——用在放大電路中不需要交流

2021-06-22 10:53:19 6238

6238 電源去耦的最終目標是為了負載能夠正常工作,使電源特性更加接近理想電源——能快速響應負載的電流需求、電壓穩定、干凈無噪聲。使電路各部分之間通過電源產生的耦合干擾降至最小。

2021-07-05 17:12:43 4709

4709

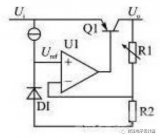

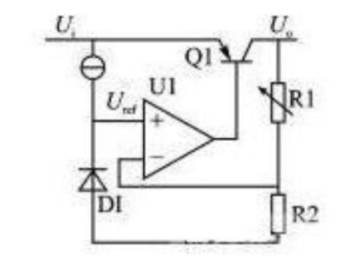

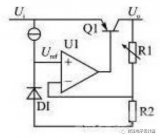

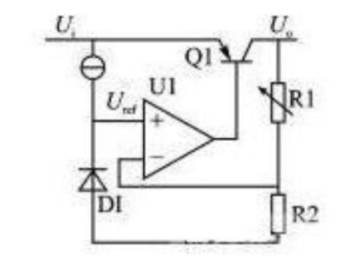

在放大器電路設計中,你一定被一些最常見的問題給“坑”過,例如——沒能用正確的方法對單電源運算放大器電路進行去耦。今天我們就討論下這個問題,并給出單電源放大器電路的正確去耦方法。 單電源運算放大器電路

2021-10-20 10:49:00 3550

3550

1.耦合機理及去耦需求集成電路芯片都有電源引腳,有的甚至有多個電源電壓和模擬數字混合電源。無論電源引腳數量如何,每路電源都有其允許范圍,包括推薦工作范圍和最大絕對值。為防止芯片損壞、保持正常工作

2021-11-10 10:20:59 12

12 去耦電容在集成電路電源和地之間的有兩個作用:一方面是本集成電路的蓄能電容,另一方面旁路掉該器件的高頻噪聲,數字電路中典型的去耦電容值是0.1μF。這個電容的分布電感的典型值是5μH。

2022-01-06 14:23:44 1996

1996 PCB PDN design guidelines (PCB電源完整性設計指導) ------PCB平面圖指南一、 不帶電源平面1.為每個有源設備至少提供一個“本地”去耦電容器,并為板上分布的每個

2022-01-06 12:25:33 9

9 2019.7.6 電源去耦設計原因:在直流電源回路中,負載的變化會引起電源噪聲。例如在數字電路中,當電路從一個狀態轉變為另一種狀態時,就會在電源線上產生一個很大的尖峰電流,形成瞬變的噪聲電壓。配置去

2022-01-11 11:41:35 8

8 Part 1 旁路電容和去耦電容基礎知識 “旁路電容”和“去耦電容” 一、定義和區別 旁路(bypass)電容:是把輸入信號中的高頻成分作為濾除對象; 去耦(decoupling)電容:也稱退耦電容

2022-10-25 20:36:59 2343

2343 去耦(decoupling)電容也稱退耦電容,一般都安置在元件附近的電源處,用來濾除高頻噪聲,使電壓穩定干凈,保證元件的正常工作。

2022-11-04 20:50:54 3796

3796 在電子電路中,去耦電容和旁路電容都是起到抗干擾的作用,電容所處的位置不同,稱呼就不一樣了。對于同一個電路來說,旁路(bypass)電容是把輸入信號中的高頻噪聲作為濾除對象,把前級攜帶的高頻雜波濾除,而去耦(decoupling)電容也稱退耦電容,是把輸出信號的干擾作為濾除對象。

2022-12-16 14:35:58 5885

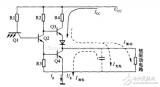

5885 這一節繼續對共射放大電路進行總結分析,確定電源的去耦電容!

2023-01-10 14:27:32 2054

2054

這一節繼續對共射放大電路進行總結分析,確定電源的去耦電容

2023-01-30 15:03:50 1471

1471

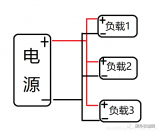

什么是去耦以及為什么要去耦? 模電書上講的去耦大多是講電源的去耦,就是一個電路的各個單元共用同一電源供電,為了防止各單元之間的耦合,需加去耦電路。 造成耦合的原因有:

2023-02-08 13:57:24 3702

3702 模電書上講的去耦大多是講電源的去耦,就是一個電路的各個單元共用同一電源供電,為了防止各單元之間的耦合,需加去耦電路。

2023-03-30 10:15:02 1707

1707

模電書上講的去耦大多是講電源的去耦,就是一個電路的各個單元共用同一電源供電,為了防止各單元之間的耦合,需加去耦電路。

2023-06-14 10:04:10 2946

2946

今天給大家分享的是:去耦電容,去耦電容PCB設計和布局。

2023-07-05 09:37:14 2167

2167

“去耦”電容并沒有去除來自電源網絡或某個“神秘來源”耦合過來的噪聲,從這個角度講,“去耦”電容的命名存在一定的誤導性。

2023-07-05 15:29:44 4561

4561

去耦(decoupling)電容也稱退耦電容,一般都安置在元件附近的電源處,用來濾除高頻噪聲,使電壓穩定干凈,保證元件的正常工作。

2023-08-06 17:02:56 7618

7618

看完本篇,幫你糾正錯誤的去耦方法

2023-10-26 15:22:26 1073

1073

何謂正確去耦?有何必要性? 如果電源引腳上存在紋波和/或噪聲,大多數IC都會有某種類型的性能下降。數字IC的噪聲裕量會降低,時鐘抖動則可能增加。對于高性能數字IC,例如微處理器和FPGA,電源額定容

2023-11-28 16:16:53 0

0 PCB去耦電容怎么放置?怎么選擇去耦電容? PCB(印刷電路板)去耦電容用于保持集成電路(IC)在運行過程中的穩定性,減少功率噪聲和干擾。它們通常由多個電解電容組成,安裝在布局上,以提供電源去耦

2023-11-29 11:03:19 2219

2219 在電子電路中,去耦電容和旁路電容都是起到抗干擾的作用,電容所處的位置不同,稱呼就不一樣了。對于同一個電路來說,旁路(bypass)電容是把輸入信號中的高頻噪聲作為濾除對象,把前級攜帶的高頻雜波濾除,而去耦(decoupling)電容也稱退耦電容

2023-12-10 14:26:02 2213

2213

在數字電路及IC控制器電路中,必須要進行電源去耦。當元件開關消耗直流能量時,沒有去耦電容的電源分配網絡中將發生一個瞬時尖峰。這是因為電源供電網絡中存在著一定的電感,而去耦電容能提供一個局部的沒有電感的或者說很小電感的電源。

2024-01-10 15:31:13 948

948

去耦電容是一種安裝在電路中的電容,主要用于提供穩定的電源,同時降低元件耦合到電源端的噪聲,間接可以減少其他元件受此元件噪聲的影響。去耦電容的作用主要包括兩個方面:一是去除高頻信號干擾,相當于

2024-02-10 14:57:00 4682

4682 去耦電容(decoupling)通常放置在芯片的電源引腳附近,用于濾除由于芯片自身用電過程中信號跳變產生的電源引腳對外的波形輸出。 在數字電路中,當電路從一個狀態轉換為另一種狀態時,會在電源線上產生

2024-02-16 16:54:00 3064

3064

耦合和去耦有什么區別,耦合電容和去耦電容的作用分別是什么,在電路中如何放置,有什么原則? 耦合和去耦是電子電路中的兩個重要概念,它們分別用于描述電路中信號的傳遞和消除噪聲。下面將詳細介紹這兩個概念

2024-02-04 09:05:32 7399

7399 去耦電容,也稱為去耦合電容或退耦電容,是電路中裝設在元件的電源端的電容。它的主要作用是為電路提供較穩定的電源,并降低元件耦合到電源端的噪聲,間接減少其他元件受此元件噪聲的影響。

2024-02-18 15:20:35 1981

1981 去耦電容的作用是將信號電源引腳的輸出干擾作為濾除對象,防止干擾信號返回電源。

2024-02-20 15:55:59 2430

2430 去耦電容(Decoupling Capacitor)在電子電路設計中扮演著至關重要的角色,它們用于減少電源線上的噪聲,確保電路的穩定性和性能。去耦電容的擺放位置和作用是電路設計中的一個重要考慮因素

2024-09-19 10:54:05 2172

2172 電子發燒友網站提供《分布式電源分配網絡建模及去耦設計研究.pdf》資料免費下載

2024-09-19 17:42:44 0

0 去耦電容,也被稱為退耦電容,是電路中裝設在元件的電源端的電容。它的工作原理基于電容器的基本原理,即通過兩個導體之間的電場來存儲電荷。當電荷在電源線上發生波動或噪聲時,去耦電容會吸收這些變化的電荷,從而保持電源電壓的穩定性。

2024-10-10 15:19:08 2727

2727 去耦通過添加電容器減少電源噪聲,陶瓷電容因其高頻響應好、ESR和ESL低,適合作為去耦電容器,提高電路穩定性和性能。

2025-01-03 10:29:28 1864

1864

電子發燒友網站提供《EE-253:SHARC處理器的電源旁路去耦.pdf》資料免費下載

2025-01-06 15:11:36 0

0 PCB設計電源去耦電容改善高速信號質量?!What?Why? How?

2025-05-19 14:27:18 613

613

電子發燒友App

電子發燒友App

評論