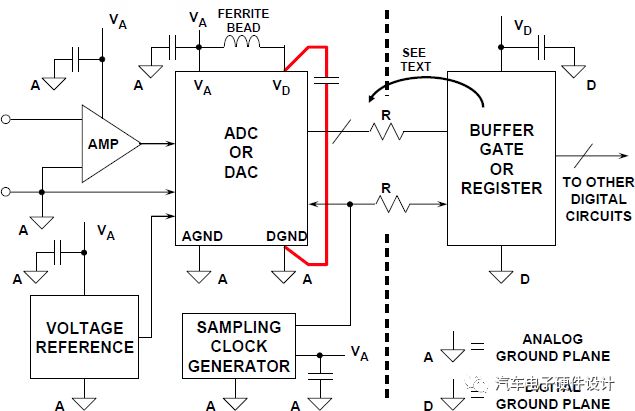

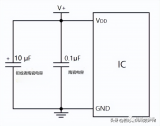

局部的高頻濾波器可以優化小小效果,去耦電容可以減小回路電感

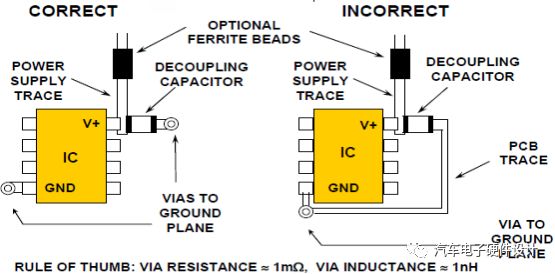

SOIC的去耦

經驗法則

–Via resistance ≈ 1mΩ, Via inductance ≈1nH

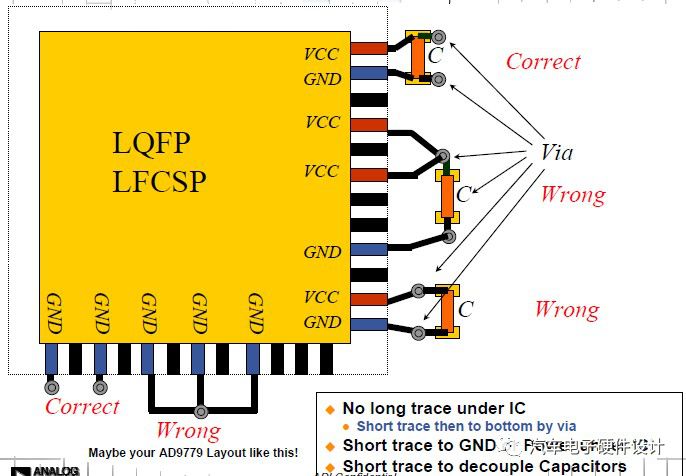

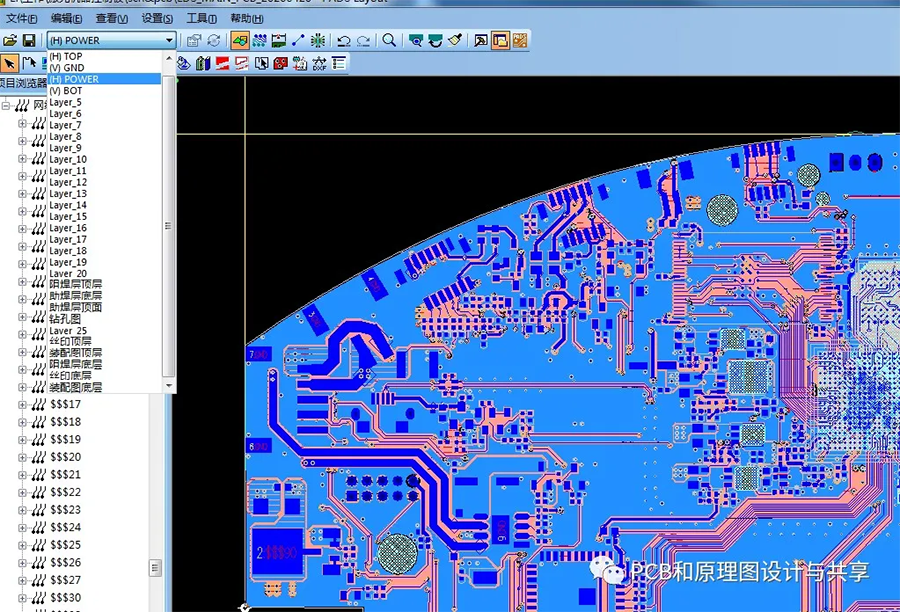

LQFP/LFCSP去耦

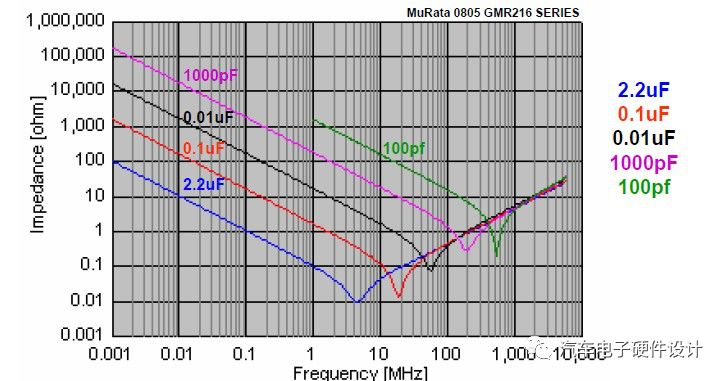

不同的去耦電容阻抗VS頻率

并聯電容可以在一個較寬的頻帶內降低阻抗

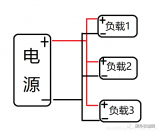

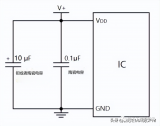

小的去耦電容盡可能靠近電源引腳

為什么每個電源引腳都需要去耦

去耦電容總結

旁路電容離電容引腳盡可能的近

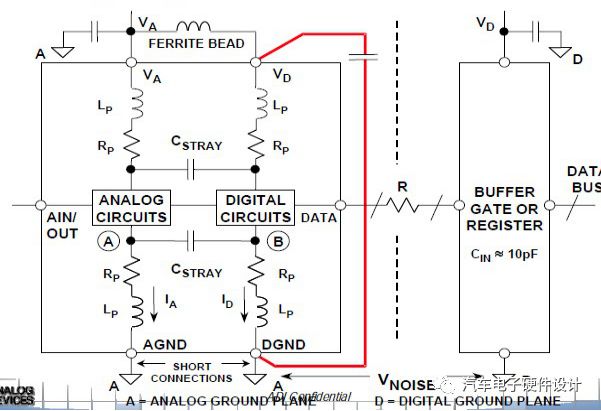

SMT磁珠對于降低Ripple非常有效

高頻時需要地平面

最小化寄生參數

使用穩定高效的器件

較少的漂移和較低的ESR

完全精確的分析是比較困難的

為了優化結果可以使用一引起模型分析

使用一組并聯的電容來去除較寬頻帶內的噪聲

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

電容

+關注

關注

100文章

6505瀏覽量

159918 -

去耦電容

+關注

關注

12文章

325瀏覽量

23602

原文標題:優秀PCB設計之去耦

文章出處:【微信號:QCDZYJ,微信公眾號:汽車電子工程知識體系】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

PCB設計之電容

1.PCB設計之電容的結構和特性給導體加電位,導體就帶上電荷。但對于相同的電位,導體容納電荷的數量卻因它本身結構的不同而不同。導體能夠容納電荷的能力稱為PCB設計之電容。 通常,某導體

發表于 08-13 10:49

高速PCB電源去耦設計指南

工程師們在設計PCB電源分配系統的時候,首先把整個設計分成四個部分:電源(電池、轉換器或者整流器)、PCB、電路板去耦電容和芯片去

發表于 10-16 12:49

?977次閱讀

PCB設計時處理去耦電容和旁路電容的注意事項

本篇介紹PCB設計時處理去耦電容和旁路電容的注意事項。

去耦電容(另見退耦電容、緩沖電容、儲能電容等),可以放置在電源電路公共出口

PCB設計之如何去耦

PCB設計之如何去耦

評論