對于簡單走線等長在以前文檔中都有涉及這里不再復(fù)述了,下面內(nèi)容將給大家介紹一下有關(guān)Xnet等長的設(shè)置問題, 如現(xiàn)在主板DDR, IDE 等部分設(shè)等長問題.

注意: 以下設(shè)置方法不是公板方式,是我自己摸索的設(shè)置方法,所以大家不必效仿,僅供參考!如果大家有任何其它或簡單方法也請分享一下經(jīng)驗(yàn)!

在這之前首先介紹一下一個(gè)新個(gè)概念Xnet,見下圖: ?

?

??? 我們把連續(xù)的幾段由無源元件(如電阻,電容或電感)連接的net合稱為一段Xnet.

??? 大家知道Allegro中有兩個(gè)常用的走線長度設(shè)置,PROPAGATION_DELAY, RELATIVE_ PROPAGATION_DELAY 都只能針對同一Net設(shè)置,

??? 下面是一個(gè)具體案例: ?

?

??? 現(xiàn)在要求U1 到U2 的走線Net*A + Net*B等長, 誤差為+/-20Mil,最簡單的方式就是分別設(shè)置Net*A等長和Net*B等長,誤差各為+/-10Mil, 這樣是可以達(dá)到要求,不過會加大Layout工程師繞線的難度,因?yàn)榭赡躈et*A部分空間比較大有足夠的繞線空間,而Net*B部分沒有空間繞線,所以就比較難達(dá)到要求.

??? 如果一種設(shè)置能把Net*A與Net*B相加,然后再做等長比對,這樣就可以解決問題了, 好的就是Allegro都早為這些問題考慮過了,只要把Net*A 與Net*B設(shè)置為一個(gè)Xnet問題就解決一半了.

??? 下面內(nèi)容將詳細(xì)介紹怎樣設(shè)置Xnet與Xnet等長.

第一部分: Xnet設(shè)置

(下面步驟可能有些簡單,不過能達(dá)到效果)

0, 需要Allegro Export版本或SPECCTRAQuest中設(shè)置, 還好大家有Cracked License天下無敵,什么版本都有J

1, 開啟Allegro Export或SPECCTRAQuest(以下省略,用Allegro簡稱這兩個(gè)), Open需要設(shè)置Xnet的板子.

2, 點(diǎn)擊菜單 Analyze>SI/EMI Sim>Model…(比正常方式設(shè)置Model簡單了些)出來的建議定義DC net直接Yes 即可,然后出現(xiàn)下面的Model設(shè)置窗體: ?

?

3, 直接在DevType Value/Refdes 中選擇要設(shè)定Model 的器件或直接在板子上點(diǎn)選要設(shè)置Model的器件;

4, 點(diǎn)選Create Model,建立該零件的Model,(如果已經(jīng)有該零件的Model,并在前面定義,然后Find Model即可,這里主要介紹沒有的情況) ?

?

在出現(xiàn)對話框中選擇Create ESpiceDevice model,點(diǎn)擊OK

5, 出現(xiàn)下面窗體: ?

?

ModelName: 輸入產(chǎn)生Model的名字

Circuit type: 選擇Type, 電阻,電感或電容

Value: 值

Single Pin: 各Pin的連接順序, 中間為空格,

這里要注意要看零件的pin的排列,1 2 3 4 5 6 7 8,就是: 1 和2 是一個(gè)電阻,其它同理所以如果就是普通電阻電容那就更簡單了. ?

?

Common Pin: 這里不用管它,空著就可以.

??? 上面都輸入好了就點(diǎn)擊OK,完成Model的建立.

??? 點(diǎn)擊OK退出就可以發(fā)現(xiàn)連接該排阻的兩邊的Net 都有了個(gè)Xnet屬性,如下圖: ?

?

??? 這樣就可以搞定Xnet,很簡單吧!

??? 下面就開始等長設(shè)置吧!

第二部分 針對Xnet部分的等長設(shè)置

??? 設(shè)置好了Xnet后就可以在Allegro中設(shè)置該Xnet的等長了,有兩種方法可以設(shè)置Xnet的等長.

第一種, 使用Edit>Properties定義

??? 注意必須使用Pin Pair 才能定義Xnet等長

RELATIVE_ PROPAGATION_DELAY= GroupX : G : U1.5 : U2.4 : 0 : 20

??? 在沒有定義Xnet之前這樣定義時(shí)會提示錯(cuò)誤的

??? 其它的和前面的等長設(shè)置方法都一樣.

如果大家覺得這樣設(shè)置有些麻煩的話,還有一招可以使用,見下面:

第二種, Constraint Manager 設(shè)置

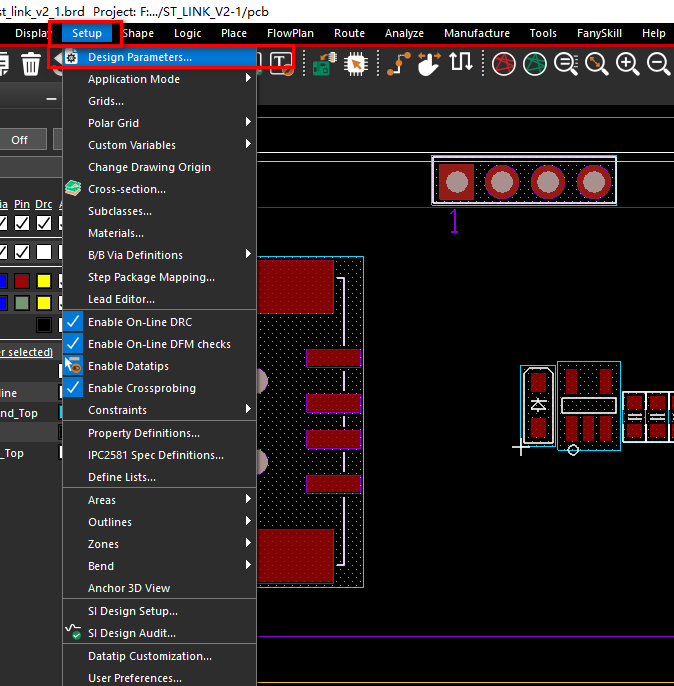

1, 開啟Constraint Manager, 點(diǎn)選菜單Setup>Electrical Constraint Spreadsheet或直接點(diǎn)擊工具欄![]()

出現(xiàn)Constraint Manager 窗體: ?

?

對于Constraint Manager 的一般使用方法這里不再做詳細(xì)介紹, 如果用戶對這部分不熟悉

可以參考其它有關(guān)Constraint Manager 使用進(jìn)行學(xué)習(xí).

2, 因?yàn)槲覀兡康氖且O(shè)置等長, 所以我們用Relative Propagation Delay這屬性, 從左邊控制欄中選擇Net>Routing>Relative Propagation Delay,

3, 在右邊就會顯示整塊板子所有的Net或Xnet, ??

??

4, 建立需要等長的Pin Pair, 右鍵點(diǎn)擊需要建立Pin Pair 的Xnet ?

?

選擇起始Pin和結(jié)束Pin, ?

?

注意:

1, 這里沒有先后順序.

2, 如果Pin Pair 的兩個(gè)Pin Type全是Passive的話不能Creat, 所以這里還需要定義一下Pin的形態(tài), 如:Out put, In put, Bidirectional等

下面是介紹如何在Allegro中定義Pin type。

如何在Allegro中定義Pin Type?

1, 點(diǎn)擊菜單Edit>Properties…

2, 在Find欄位中僅勾選Pin

3, 直接在PCB中選中需要修改Pin Type的Pin

4, 出現(xiàn)下面窗體: ?

?

選擇Pinuse,在右邊定義為BI即可

5, Ok完成Pin Type定義

這樣就可以Create Xnet的Pin Pair 了。

點(diǎn)擊Apply或OK 就完成Pin Pair 設(shè)置. ?

?

5, 設(shè)置等長Group

當(dāng)Xnet Pin Pair 建立完成后其它設(shè)置就和普通Pin Pair 設(shè)置等長是一樣的. ?

?

使用Ctrl鍵復(fù)選所有需要設(shè)置等長的Pin Pair, 右鍵Create>Match Group ?

?

輸入Group名字; ?

?

注意: Scope選擇Global

電子發(fā)燒友App

電子發(fā)燒友App

評論