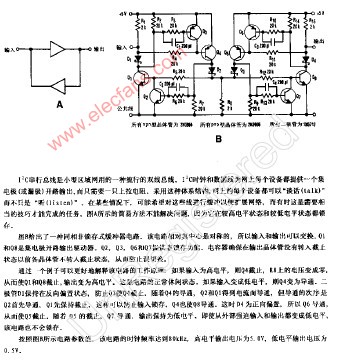

1Hz正弦波振蕩器

本電路利用兩個運算

2009-10-07 11:44:47 2823

2823

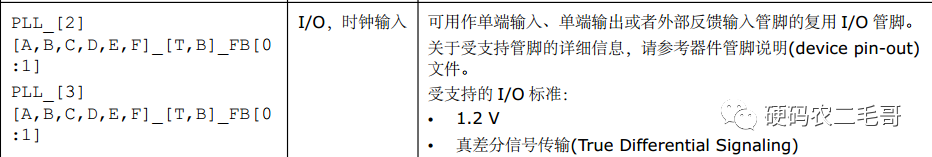

嗨,大家好,我向時鐘向導提供50 Mhz輸入,并使用MMCM方案生成80 MHz方案。在模擬中,我看到輸入時鐘和生成的時鐘之間存在延遲。這種延遲是什么?有什么辦法可以控制這種延遲嗎?任何建議都會非常

2019-04-26 13:01:43

,AD9106的輸入時鐘和我系統的采集卡時鐘是同步 的,這樣DDS輸出的波形就和采集卡的不同步,會導致采集有誤差!期待你們幫助!謝謝!另外DDSAD9834也存在這樣的問題!

2023-12-13 08:45:46

AD9163的時鐘輸入范圍多大,輸入時鐘大小與輸入數據速率是什么關系?

2023-12-08 08:20:20

如果不對Ad9959進行寫操作,sync_clk時鐘輸出為輸入時鐘的1/4。但是如果對輸入時鐘進行放大之后,sync_clk時鐘輸出不是放大之后的1/4;使用spi,時序都正確。求幫助。

2018-11-12 09:21:24

右對齊方式存儲在16位數據寄存器中。模擬看門狗特性允許應用程序檢測輸入電壓是否超出用戶定義的高/低閥值。ADC 的輸入時鐘不得超過14MHz,它是由PCLK2經分頻產生。圖1 ADC框圖...

2021-08-05 07:16:30

看了ADS1178的數據手冊,輸入時鐘CLK范圍是100kHz到27MHz之間,SCLK推薦為CLK的1、1/2等

問題:

1、轉換速率是否只與MODE有關,與輸入時鐘無關?若設置MODE為0

2025-01-24 07:21:21

在System Control and Interrupts Reference Guide中描述GPIO:GPIOINENCLK設置是否使能GPIO的輸入時鐘,關于GPIO的輸入時鐘有點暈,GPIO需要時鐘做什么?

2018-05-14 08:50:24

本帖最后由 zyf630197730 于 2015-3-30 10:36 編輯

用DAQ控件設計一個數據采集系統,采樣頻率為1HZ。起初用while循環,可是運行時間久了,發現采樣間隔不是1s。怎樣做到嚴格的1Hz啊。現在想用電腦上的時鐘作為采樣時鐘的頻率源,怎樣調用電腦系統的時鐘呢?

2015-03-27 16:38:39

MMCM是否也適用于40 Mhz或其他輸入時鐘?如果不工作,如何配置動態輸入時鐘MMCM?感謝您的幫助!以上來自于谷歌翻譯以下為原文Hi, I have a question about

2019-03-14 17:04:56

你好,最近在用PCM1794做一款產品,在模式選擇時,FTM1腳給一個高電平(3.3v)時,會把3.3v電位拉低到1V左右,FTM0腳則不會出現這種現象,在此存在疑惑,另外,對于PCM1794的輸入時鐘存在較小誤差,會引起PCM1794無法工作嗎?望解答,謝謝

2024-12-20 08:25:11

你好,我們在設計中需要使用 hmc7044 產生一系列頻率為 204MHz 且相位對齊的時鐘,并且所有的 204MHz 時鐘都由 外部VCO輸入時鐘 816MHz 所產生。

目前所有的時鐘都已經獲取

2023-12-01 10:15:39

一個1Hz的時鐘信號可否驅動led閃爍?

2014-03-29 14:05:05

本人在使用DS90CR286A芯片時出現如下情況,輸入穩定的40M差分時鐘,但是輸出時鐘時有時無,我的power dowm管腳是直接拉高的。

輸入時鐘

輸出時鐘

不知道出現這種情況的可能

2025-01-07 07:25:21

奇怪的行為。在深入了解“Ouroboros”時鐘之前,我們來看一下基本的時鐘切換術語和標準輸入時鐘切換配置。

2021-02-26 07:50:42

想用555定時器提供一個1hz的信號給數字時鐘,結果連接完了,輸出也正常,但是時鐘卻是從35s開始的,,不知道為啥,

2016-04-15 18:59:41

如果xilinx V5板子 程序中使用外部輸入時鐘,clk=36.15MHz,現在需要使用36.15*6=216.9MHz的時鐘進行運算,如何生成該時鐘?求指導。ucf文件中已定義NET "

2014-12-16 16:12:31

頻率計,multisim仿真,用晶振做1Hz和10Hz的時鐘,六位計數器,譯碼,數碼管顯示

2015-12-09 16:19:31

AD9163的時鐘輸入范圍多大,輸入時鐘大小與輸入數據速率是什么關系?

2018-07-31 09:42:19

1、參考時鐘REFin輸入采用方波輸入時:1)交流耦合還是直流耦合?2)采用3.3Vcmos方波輸入電平時,是直接直流耦合輸入還是交流耦合?手冊中的輸入口推薦電路該如何理解2、供電Vvco管腳的供電是否需要和VDD、AVDD供電分開,是否可以合用?

2019-03-04 16:01:45

,AD9106的輸入時鐘和我系統的采集卡時鐘是同步 的,這樣DDS輸出的波形就和采集卡的不同步,會導致采集有誤差!期待你們幫助!謝謝!另外DDSAD9834也存在這樣的問題!

2018-08-15 07:04:44

我們使用開發板,想實現輸入時鐘和輸出時鐘相位同步的功能,輸入和輸出時鐘都是LVCMOS電平,一路輸入時鐘12.288M,一路輸出時鐘49.152M。

要求輸入12.288M時鐘相位變化時,輸出時鐘

2024-11-11 08:25:23

lvds時鐘的時鐘。例如,SVGA的時鐘對頻率為40MHz,串行數據頻率為280MHz。但是selectIO向導假設輸入時鐘是280MHz?因為我看到它在源代碼中將輸入時鐘分為1/7。以上來自于谷歌翻譯以下

2019-07-17 07:20:11

我有一個輸入時鐘(SCKx4),它是我的RTL發送器端的源時鐘,這個時鐘通過FPGA傳送出去(命名為TDM_SCKx4)到另一個設備。此SCKx4的原理圖中的路徑如下:SCKx4 - >

2020-08-18 10:16:10

請問如果將c6457定時器的時鐘輸入源配置為內部時鐘輸入,那么它的實際輸入時鐘頻率怎么計算呢?謝謝!

2018-07-25 06:47:09

請問我要用74ls161怎么計數到2400時鐘頻率1HZ

2019-04-22 05:37:25

最小RBW 提高到1Hz升級文件

2017-12-25 16:04:36

DS1081L是擴展頻譜時鐘調制器IC,可降低高頻時鐘數字設備的EMI。DS1081L采用集成鎖相環(PLL),輸入時鐘信號范圍20MHz至134MHz,輸出經過頻譜擴展調制的時鐘。可通過引腳設

2008-04-15 09:07:29 36

36 DS26504是樓宇綜合定時供給系統(BITS)的時鐘恢復器件。該芯片還可用作基本的T1/E1收發器。接收部分可以從T1、E1、64kHz復合時鐘(64KCC)和6312kHz同步定時接口恢復時鐘。在T1/E1模式下,

2008-08-04 09:31:40 24

24 DS1083L是擴展頻譜時鐘調制器IC,可降低高頻時鐘數字電子設備的EMI。DS1083L采用集成鎖相環(PLL),輸入時鐘信號范圍為16MHz至134MHz,輸出經過頻譜擴展調制的時鐘信號。可通過引

2008-08-10 09:26:45 24

24

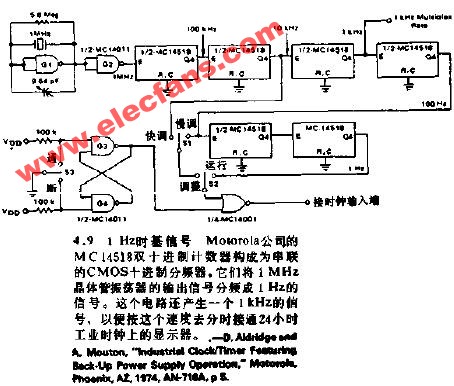

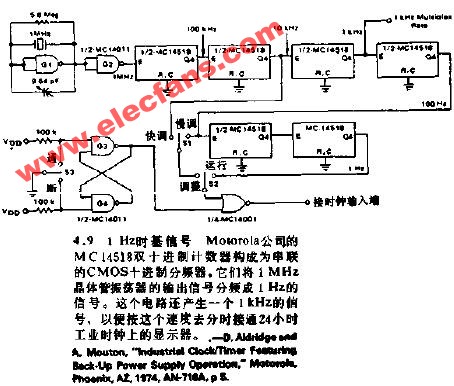

1HZ時基信號電路

2009-01-13 19:22:59 3262

3262

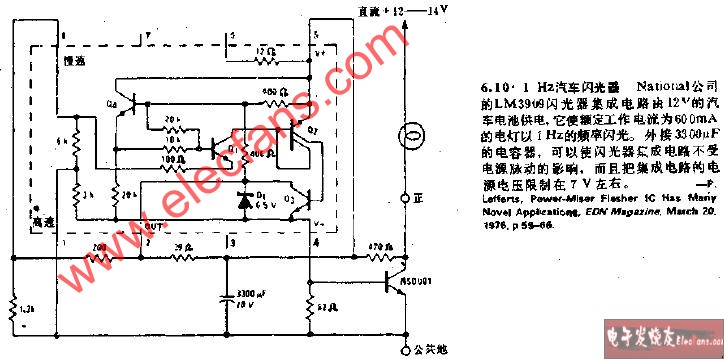

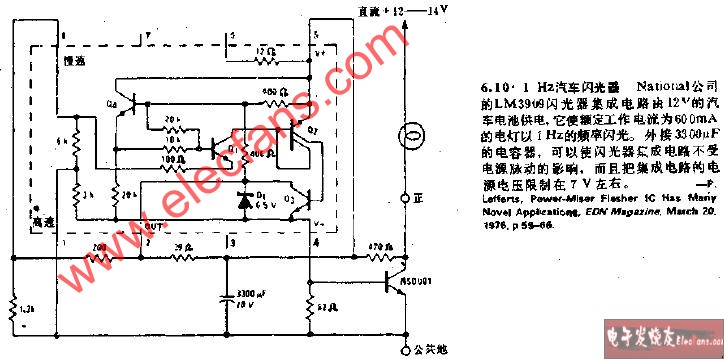

1Hz汽車閃光器電路

2009-01-17 13:57:58 2006

2006

AC2301是一款3GHz、10路差分扇出緩沖器,用于高頻、低抖動時鐘/數據分配和電平轉換。可從兩個差分輸入或一個晶體輸入中選擇輸入時鐘。所選擇的輸入時鐘被分配到兩組輸出,每組輸出包含5個差分輸出

2025-11-11 16:41:47

IC數據和時鐘時鐘線緩沖電路

2009-09-12 11:57:02 1707

1707

基于FPGA的提取位同步時鐘DPLL設計

在數字通信系統中,同步技術是非常重要的,而位同步是最基本的同步。位同步時鐘信號不僅用于監測輸入碼元信號,確保收發

2010-01-25 09:36:18 3699

3699

同步網時鐘及等級

基準時鐘 同步網由各節點時鐘和傳遞同步定時信號的同步鏈路構成.同步網的功能是準確地將同步定時信號從基

2010-04-03 16:27:34 4060

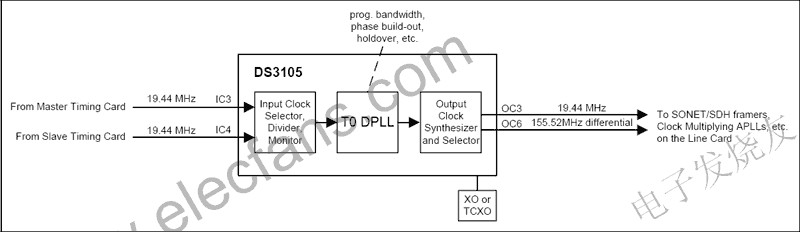

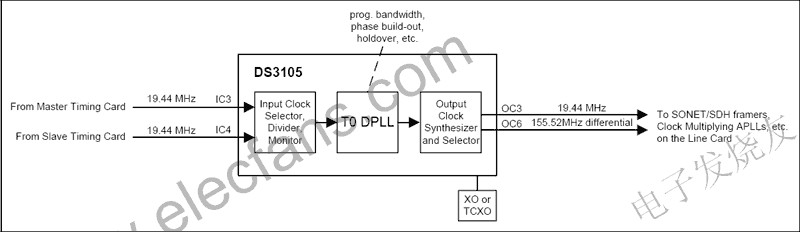

4060 DS3105是一款低成本、功能豐富的時鐘IC,用于電信線卡。通常,器件從雙冗余系統時鐘卡接收兩路參考時鐘。DS3105連續監測兩路輸入時鐘,并在主參考時鐘失效時自動地無縫切

2010-09-15 09:35:41 1174

1174

DS31400是一款靈活的高性能定時IC,用于各種頻率轉換和頻率合成應用。該器件的8路輸入時鐘和14路輸出時鐘的任何一

2010-11-24 09:35:36 1137

1137 DS31408是一個靈活的,高性能的不同頻率轉換時間和頻率合成中的應用集成電路。在其八個輸入時鐘和14個輸出時鐘,

2011-03-21 11:40:29 2070

2070 DS31404是一個靈活的,高性能的不同頻率轉換時間和頻率合成中的應用集成電路。在其四個和八個輸入時鐘的輸出時鐘,每個設備可以接受或生成幾乎任何2kHz和750MHz的頻率之間

2011-03-21 11:42:52 1592

1592 Abstract: This application note describes how Maxims DS314xx clock-synchronization ICs can be field

2011-03-28 09:44:09 41

41 基于實時時鐘模塊 時鐘芯片DS1302

2017-10-16 11:35:07 40

40 v2,SyncEth,ToP,TDM時鐘同步等,以滿足無線設備和傳輸設備的時鐘同步和傳輸需求。 微波時鐘同步組網 針對微波自身特點,將對目前常用的幾種同步方法進行簡要介紹,以加深時鐘同步的認識度。 1. 通過E1/T1實現時鐘同步 在這種方式下,E1/T1業務將攜帶的TDM原始時鐘

2017-12-07 20:51:01 1085

1085 對DS80C320雙串行口的運用,簡化了系統設計,并擴展了1PPM,1PPH等同步對時脈沖的輸出。該GPS衛星同步時鐘已用于變電站自動化系統中,其運行結果表明,它為整個系統提供了精確的時間信息,具有較高的可靠性和實用性,完全能夠滿足電力系統對高精度對時信號源

2018-02-10 11:17:57 4

4 DS12887是美國達拉斯半導體公司最新推出的時鐘芯片,采用CMOS技術制成,把時鐘芯片所需的晶振和外部鋰電池相關電路集于芯片內部,同時它與目前IBM AT計算機常用的時鐘芯片MC146818B

2018-03-16 16:29:42 11

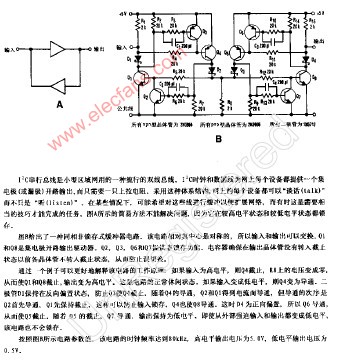

11 1Hz至1MHz的信號發生電路,1Hz~1MHz Signal generating circuit

關鍵字:運放方波信號發生電路

以

2018-09-20 19:58:21 2834

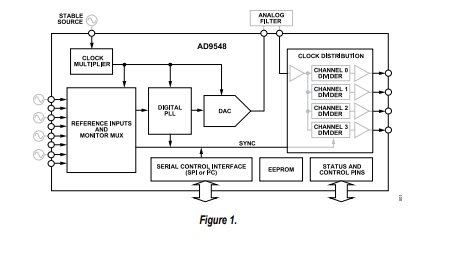

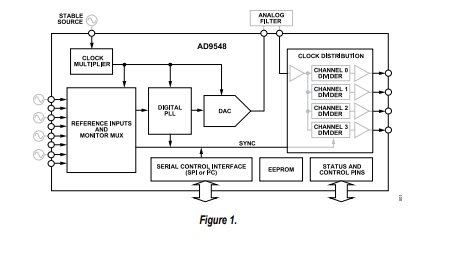

2834 AD9548: 8通道1HZ~750MHZ參考輸入,4通道1HZ~400MHZ差分輸出,典型輸出抖動小于1PS rms。應用范圍:網絡時鐘同步、GPS 1PPS同步、抖動濾除、2級鐘/3級鐘同步/保持/切換功能、無線基站時鐘同步。

2019-06-10 06:17:00 6942

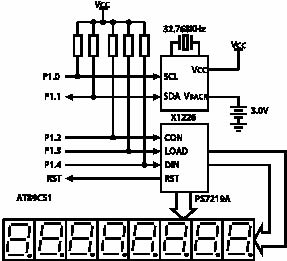

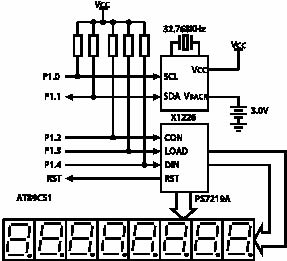

6942 RTC 時鐘模塊 DS1302實時時鐘 SPI接口

板載紐扣電池座 支持三線或四線同步串行通信 應用于手持設備 電子手表 鬧鐘

型號 DS1302 RTC Board

2019-12-30 10:03:10 4180

4180

X1226具有時鐘和日歷的功能,時鐘依賴時、分、秒寄存器來跟蹤,日歷依賴日期、星期、月和年寄存器來跟蹤,日歷可正確顯示至2099年,并具有自動閏年修正功能。擁有強大的雙報警功能,能夠被設置到任何時鐘/日歷值上,精確度可到1秒。可用軟件設置1Hz、4096Hz或32768Hz中任意一個頻率輸出。

2020-06-13 11:13:13 3752

3752

程序實現對輸入時鐘信號的7分頻介紹。

2021-03-17 14:59:23 11

11 電子發燒友網為你提供基本時鐘切換術語和標準輸入時鐘切換配置資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-05 08:40:34 7

7 EE-393:保護ADSP-CM41x器件免受輸入時鐘/電源故障

2021-05-07 13:55:11 2

2 存儲實時時鐘/日歷的 31 字節的靜態 RAM,可通過簡單的串行接口與微處理器通訊,將當前的是時鐘存于RAM。DS1302芯片對于少于 31 天的月份月末會自動調整,并會自動對閏年進行校正。由于有一個...

2022-01-17 13:03:59 29

29 1.介紹DS1302是一種串行接口的實時時鐘,芯片內部具有可編程的日歷時鐘和31個字節的靜態RAM。2.內部結構(1)SCLK:串行時鐘輸入端,控制數據輸入與輸出。(2)I/O:雙向輸入線(3)CE

2022-01-18 08:54:59 3

3 DS1302時鐘比起DS18B20而言要簡單的多。需要注意的大概兩點:1. 寫入時分秒void set_time(unsigned char shi, unsigned char fen

2022-01-18 08:55:59 4

4 實驗18:DS1302時鐘主程序

2022-01-18 09:08:02 29

29 如何使用實時時鐘 IC DS1307 制作準確的時鐘。時間將顯示在液晶顯示屏上。

2022-04-26 17:23:31 8101

8101

這是帶有板上芯片(COB)的1Hz時鐘發生器電路。通常,為數字時鐘和計數器電路應用產生1Hz時鐘的電路將IC與晶體和微調電容器等結合使用。

2022-06-07 10:43:50 3854

3854

? ISE版本為14.7 1、時 鐘IP核(Clocking Wizard) 第一頁 Clocking Features選項框中: (1)Frequency synthesis選項是允許輸出與輸入時鐘

2022-07-03 14:42:10 5988

5988 2022-11-17 12:42:26 0

0 電子發燒友網站提供《Arduino Shield NCS314 NIXIE電子管時鐘.zip》資料免費下載

2022-11-22 11:58:45 0

0 Maxim的DS314xx系列時鐘同步IC是功能強大、靈活的電信系統同步定時解決方案。這些器件最初設計用于鎖定2kHz至750MHz的輸入時鐘頻率,該頻率范圍可滿足大多數電信系統的需求。然而,有時

2023-01-29 19:05:34 1835

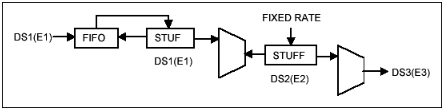

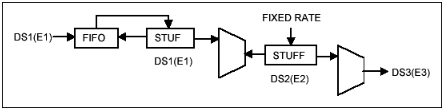

1835 在發射端,DS3(E3)時鐘和DS1(E1)時鐘由輸入引腳派生,但DS2(E2)時鐘頻率是DS3(E3)時鐘頻率的一小部分。出于設計原因,分數將表示為整數比率,這取決于設備的模式。DS1(E1)時鐘可以容忍基于DS3(E3)時鐘頻率和器件模式的頻率范圍。

2023-02-22 10:10:18 1372

1372

本應用筆記介紹了ADI公司的DS314xx時鐘同步IC如何進行現場升級,以接受并鎖定至1Hz輸入時鐘信號。它還描述了在少數情況下需要1Hz時鐘監控功能和系統軟件支持。有了這些元件,使用DS314xx器件構建的系統就可以與1Hz和更高速輸入時鐘的任意組合實現符合標準的時鐘同步行為。

2023-03-08 15:22:00 2248

2248 目前使用AD9545方案,備注:1PPS_IN為上升沿500ms的1HZ的時鐘信號,Rise time 160us左右,現在有以下問題請幫忙Spport一下

2023-03-08 16:00:00 1971

1971 DS3112具有六種不同的發送時鐘和六種不同的接收時鐘類型:發送DS3、DS2、DS1、E3、E2和E1時鐘,以及接收DS3、DS2、DS1、E3、E2和E1時鐘。由于電路中同一級的時鐘具有相似

2023-06-13 15:39:46 1210

1210

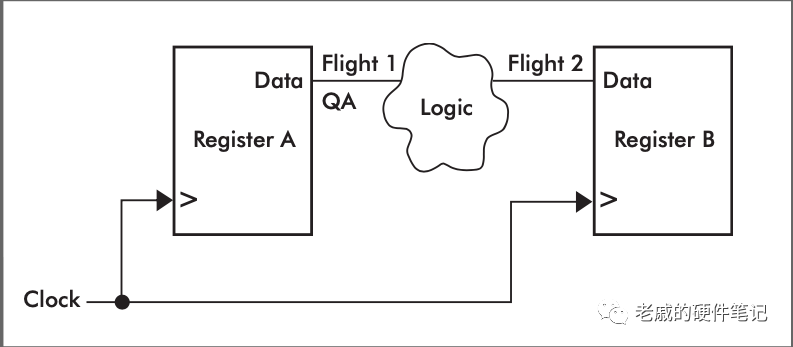

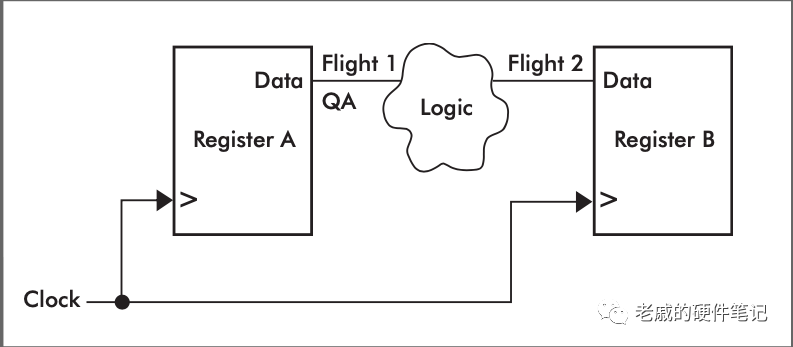

高速數字電路模塊通常以 同步 (synchronous)電路的形式實現,它們由一個或者多個時鐘驅動(觸發)。對于 單一時鐘(域) 的同步電路而言,只要輸入和時鐘的關系滿足 建立(setup)時間

2023-06-23 17:53:00 2782

2782

幾年前FPGA時鐘只需要連接一個單端輸入的晶振,非常容易。現在不同了,差分時鐘輸入,差分信號又分為LVDS和LVPECL,時鐘芯片輸出后還要經過直流或交流耦合才能接入FPGA,有點暈了,今天仔細研究一下。

2023-08-21 11:28:44 14322

14322

怎樣用CD40106芯片分別產生1Hz和50Hz的時鐘信號? 首先,讓我們了解一下CD40106芯片的基本原理和功能。CD40106芯片是一種多功能CMOS集成電路,內部有6個門電路,主要用于觸發器

2023-10-25 15:07:52 3077

3077 如何用時鐘振蕩器產生穩定的100hz或1hz的時鐘信號? 時鐘信號是電子系統中至關重要的組成部分,用于同步各種信號和操作。它需要穩定、準確、可靠地工作,以確保系統性能。時鐘信號的產生可以通過許多

2023-10-25 15:07:55 2951

2951 DS1302時鐘芯片是一種實時時鐘芯片,采用三線串行接口與微處理器相連,可以提供年、月、日、時、分、秒等時間信息。

2023-11-18 09:39:40 7050

7050 實現數據的正確傳輸和協調。 網絡時鐘同步的要求主要包括以下幾個方面: 1. 精度要求:根據不同的應用場景和需求,對網絡時鐘同步的精度要求也有所不同。例如,對于金融交易系統來說,時鐘同步的精度要求非常高,通常要求在毫

2024-01-16 16:03:25 2667

2667 FPGA輸入的時鐘信號必須是方波么?正弦波會有影響么? FPGA是一種可編程邏輯器件,通常用于實現數字電路。輸入時鐘信號是FPGA中非常重要的時序信號,對整個系統的穩定性和性能都有很大影響。在

2024-01-31 11:31:42 5410

5410 等領域得到了廣泛應用。 1. GPS衛星同步時鐘的工作原理 GPS衛星同步時鐘的工作原理可以分為以下幾個步驟: GPS衛星信號接收:GPS接收機接收來自多顆GPS衛星的導航信號,其中包含衛星的精確時間信息。 時間信息提取:接收機對接收到的導航信號

2024-03-19 10:28:04 3646

3646

電子發燒友網站提供《CDCLVP111-SP具有可選輸入時鐘驅動器的低電壓1:10 LVPECL數據表.pdf》資料免費下載

2024-08-20 09:15:44 0

0 電子發燒友網站提供《CDCLVP111低壓1:10 LVPECL,內置可選輸入時鐘驅動器數據表.pdf》資料免費下載

2024-08-21 11:37:08 0

0 電子發燒友網站提供《CDCLVP110帶可選輸入時鐘驅動器數據表.pdf》資料免費下載

2024-08-22 10:52:47 0

0 ,以確保視頻信號的同步和穩定。以下是關于視頻時鐘合成芯片的使用指南: 1. 視頻時鐘合成芯片的基本概念 視頻時鐘合成芯片是一種數字電路,它通過相位鎖定環(Phase-Locked Loop,PLL)技術來生成穩定的時鐘信號。這種芯片可以接收一個輸入時鐘信號,并根據需要生成

2024-10-10 11:17:18 1231

1231 時鐘緩沖器是一種用于生成、處理和分配時鐘信號的電子電路,主要用于確保數字系統中各模塊的同步操作。其核心功能是對輸入時鐘信號進行調理和分配,以提供高質量、低抖動的時鐘信號。

2025-02-17 14:34:51 2136

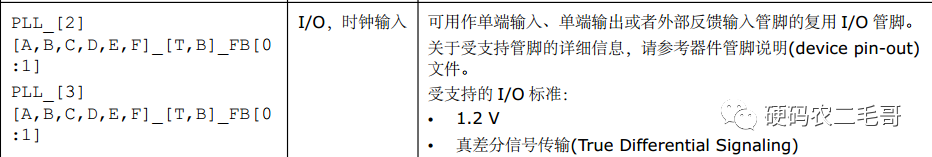

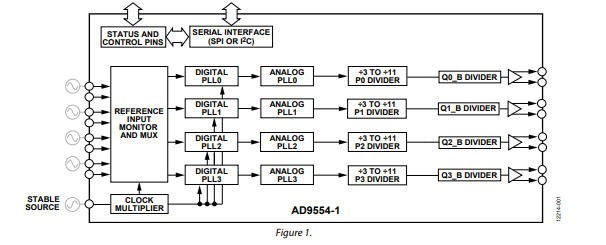

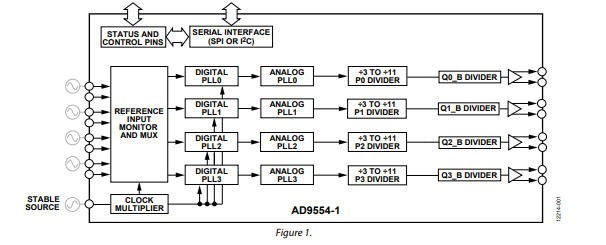

2136 AD9554-1是一款低環路帶寬時鐘倍頻器,可針對包括同步光纖網絡(SONET/SDH)的許多系統提供抖動清除和同步功能。 AD9554-1產生的輸出時鐘可以與多達四路外部輸入參考時鐘同步

2025-04-10 11:21:01 794

794

AD9547針對許多系統提供同步功能,包括同步光纖網絡(SONET/SDH)。該器件產生的輸出時鐘可以與兩路差分或四路單端外部輸入參考時鐘之一同步。數字鎖相環(PLL)可以降低與外部參考時鐘

2025-04-11 09:37:58 758

758

AD9548可為包括同步光纖網絡(SONET/SDH)在內的許多系統提供同步。它可以產生一個與高達四個差分或者八個單端外部輸入基準之一同步的輸出時鐘。數字PLL能減少與外部基準有關的輸入時間抖動或者

2025-04-11 10:40:04 810

810

CDC1104是一個 1 到 4 可配置的時鐘緩沖器。該器件接受輸入參考時鐘,并創建 4 個緩沖輸出時鐘,輸出頻率等于輸入時鐘的一半 頻率。四個控制輸入,S1、S2、S3、S4 時鐘輸出的可配置相位。

2025-09-16 09:37:34 658

658

探索RC192xx:PCIe Gen5/6 2 - 輸入時鐘復用器家族的卓越性能 在當今高速發展的電子領域,對于高性能時鐘復用器的需求日益增長。Renesas的RC192xx系列時鐘復用器,包括

2025-12-30 09:55:12 91

91

電子發燒友App

電子發燒友App

評論