ISE版本為14.7

1、時(shí)鐘IP核(Clocking Wizard)

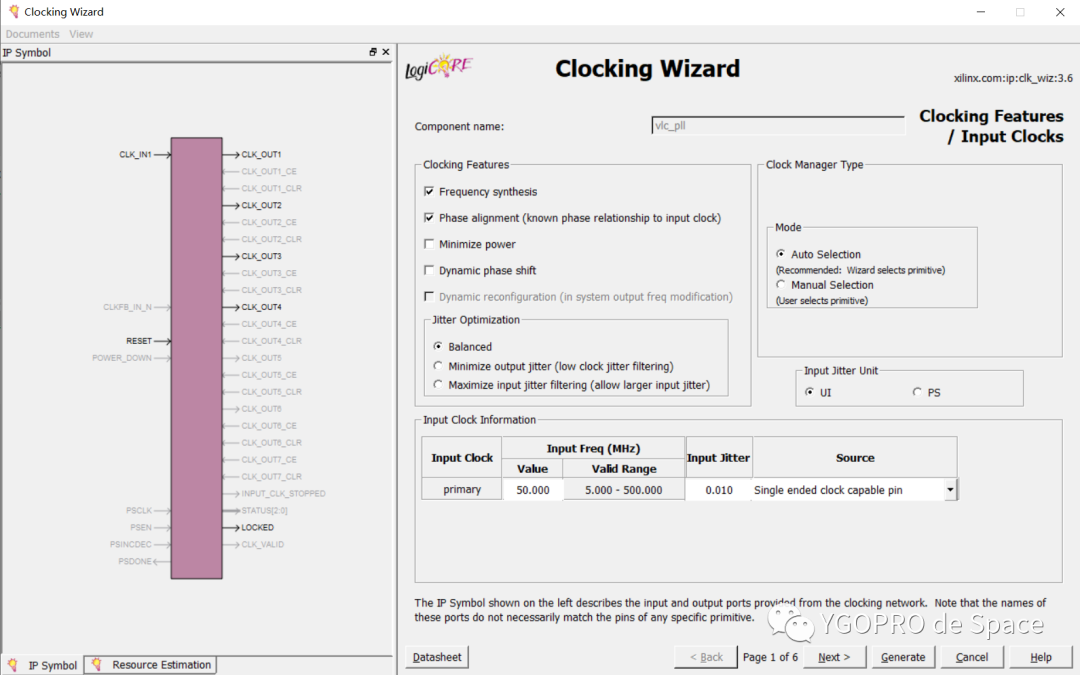

第一頁

Clocking Features選項(xiàng)框中:

(1)Frequency synthesis選項(xiàng)是允許輸出與輸入時(shí)鐘不同頻率的時(shí)鐘。

(2)Phase alignment選項(xiàng)是相位鎖定,也就是將輸出始終的相位和一個(gè)參考時(shí)鐘同步,大多是和輸入時(shí)鐘同步。

(3)Minimize power選項(xiàng)為降低功耗,也就是資源,取而代之的是相位、頻率的偏差,對(duì)于對(duì)時(shí)鐘要求不高、資源有限的情況下可以使用,一般不推薦選此選項(xiàng)。

(4)Dynamic Phase Shift該選項(xiàng)為提供動(dòng)態(tài)相移功能,選上此選項(xiàng)之后,可以在輸入端控制相移,并有相移完成之后的反饋,相移步進(jìn)長度為固定的幾個(gè)值。

Jitter Optimization選項(xiàng)框中:

(1)Balanced就是在抖動(dòng)優(yōu)化時(shí)選擇比較均衡的正確帶寬。(一般選這個(gè))

(2)Minimize output jitter:使輸出時(shí)鐘抖動(dòng)最小,但是可能會(huì)增加功耗或資源,可能導(dǎo)致輸出相位錯(cuò)誤。

(3)Maximize input jitter filtering:該選項(xiàng)表示可使輸入時(shí)鐘抖動(dòng)變大,但是可能會(huì)導(dǎo)致輸出時(shí)鐘抖動(dòng)變大。

其他選項(xiàng)按照?qǐng)D中選擇。

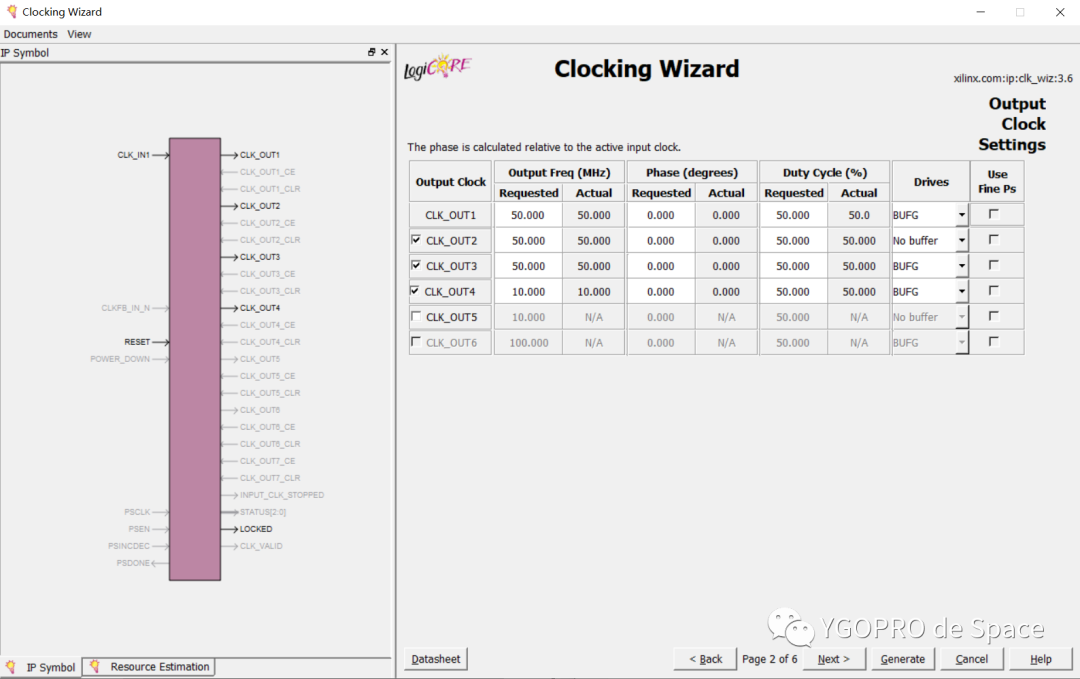

第二頁

選擇輸出CLK端口

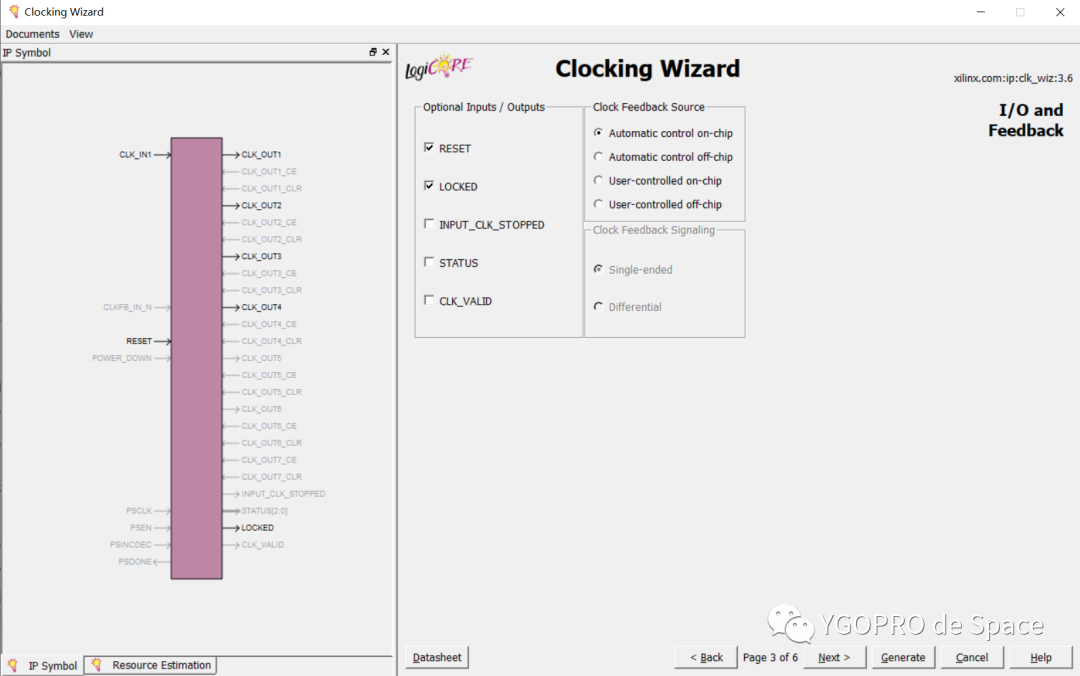

第三頁

可選端口,可根據(jù)實(shí)際應(yīng)用選擇,一般情況下reset,locked選上。

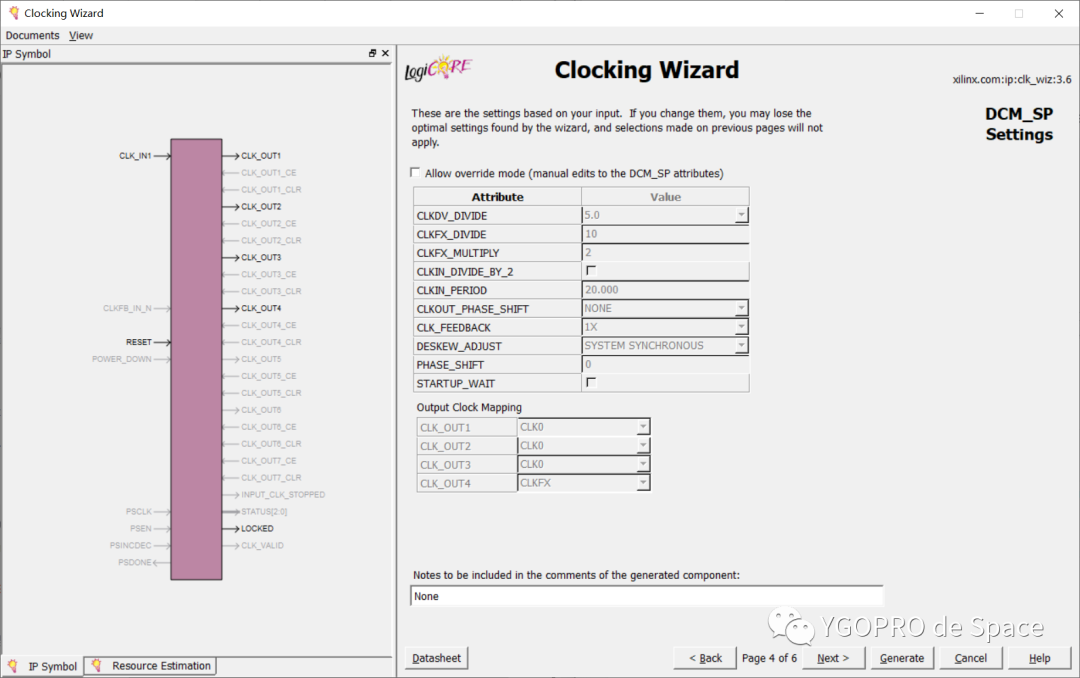

第四頁

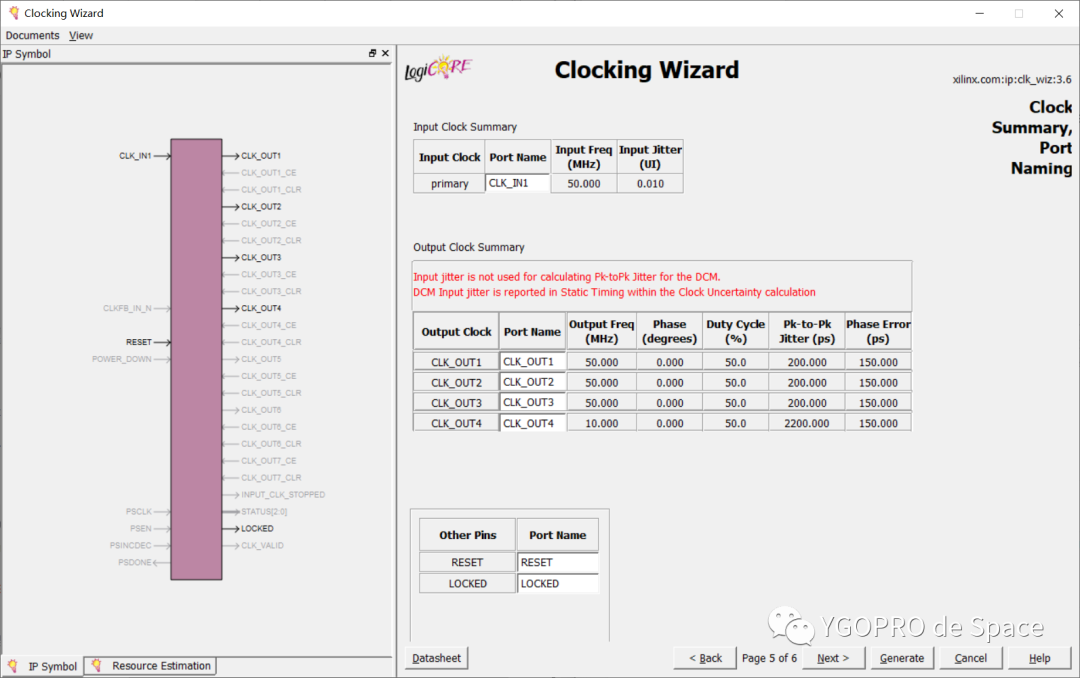

第五頁

可對(duì)端口進(jìn)行重命名。

2、FIFO IP核(FIFO Generator)

fifo是一種先進(jìn)先出的數(shù)據(jù)存儲(chǔ)和緩沖器,其本質(zhì)是RAM。fifo的位寬就是每個(gè)數(shù)據(jù)的位寬,fifo的深度簡單來說是需要存多少個(gè)數(shù)據(jù)。fifo有同步fifo和異步fifo兩種,同步即讀寫時(shí)鐘相同,異步fifo即讀寫時(shí)鐘不同。一般異步fifo用的較多,用來處理跨時(shí)鐘域的問題。

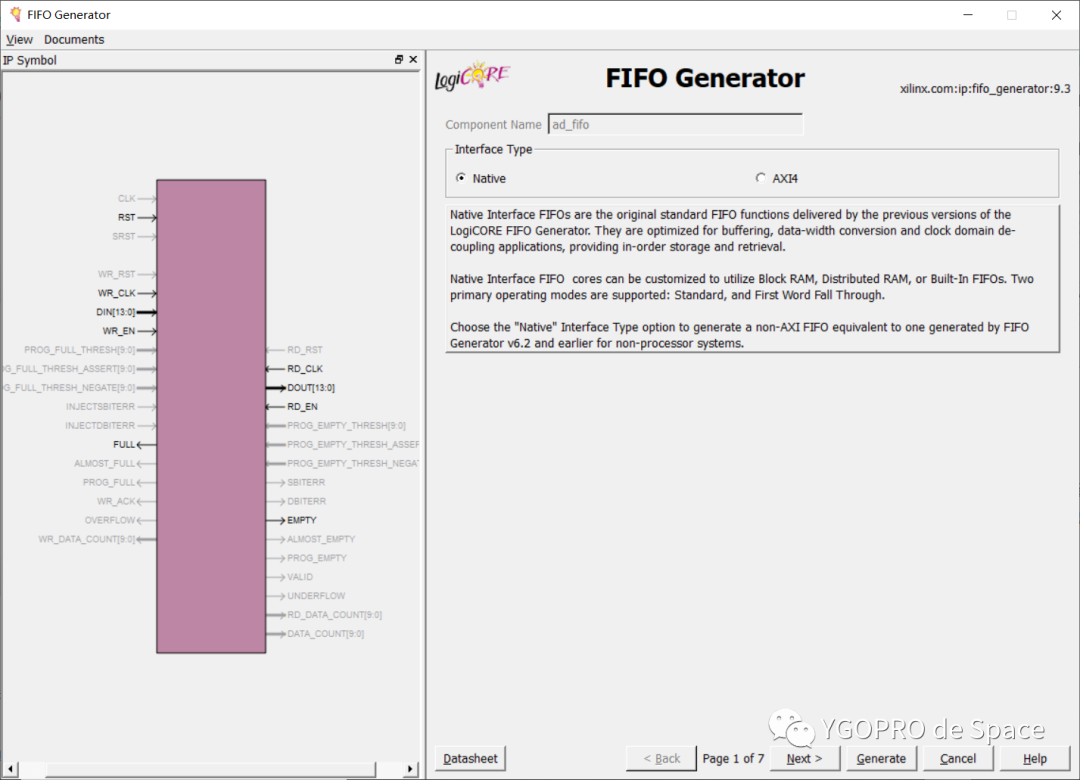

第一頁

接口類型選擇Native類型的,AXI4是與DMA或與其他有AXI4接口通信時(shí)使用的。

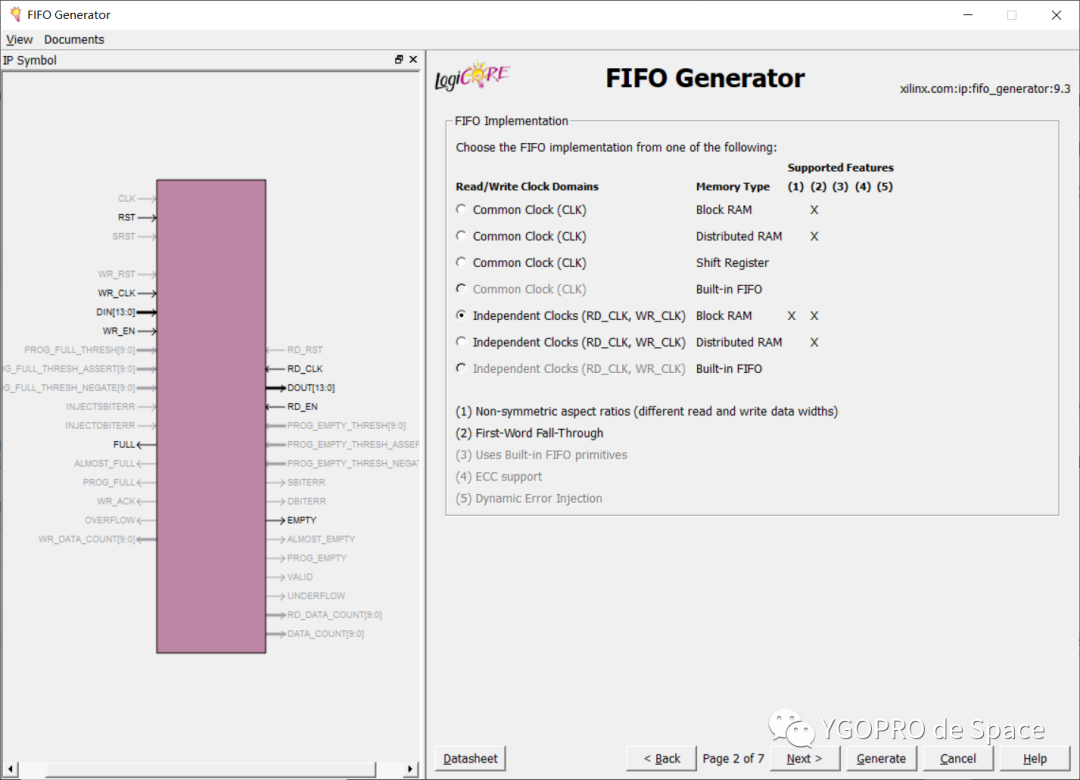

第二頁

(1)選擇異步時(shí)鐘,F(xiàn)IFO的主要功能就是用在異步時(shí)鐘域作為緩存,所以選擇獨(dú)立時(shí)鐘的模式使用范圍更廣。

(2)Memory Type :常用的有Block Ram 和 Distrubtion RAM ,前者使用片上ROM作為緩存,后者使用LUT邏輯資源搭建RAM緩存,如果使用FIFO不大,或者資源充足的情況下,使用Block RAM。

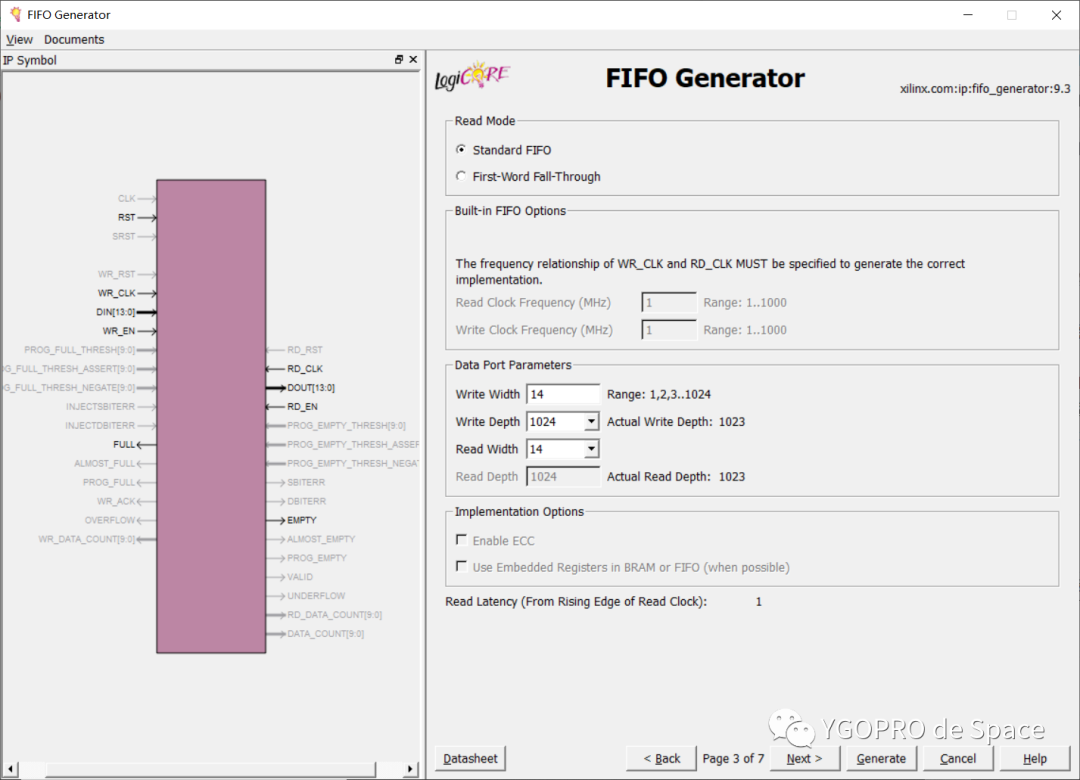

第三頁

(1)Read Mode:First-word Fall-Through 與 Stanbdard FIFO 的區(qū)別是,Standard FIFO為當(dāng)給出讀使能后,數(shù)據(jù)會(huì)延遲一拍;First-Word Fall-Through 則是當(dāng)給出讀使能,立即給出數(shù)據(jù)。

(2)根據(jù)自己的需求設(shè)置位寬和深度

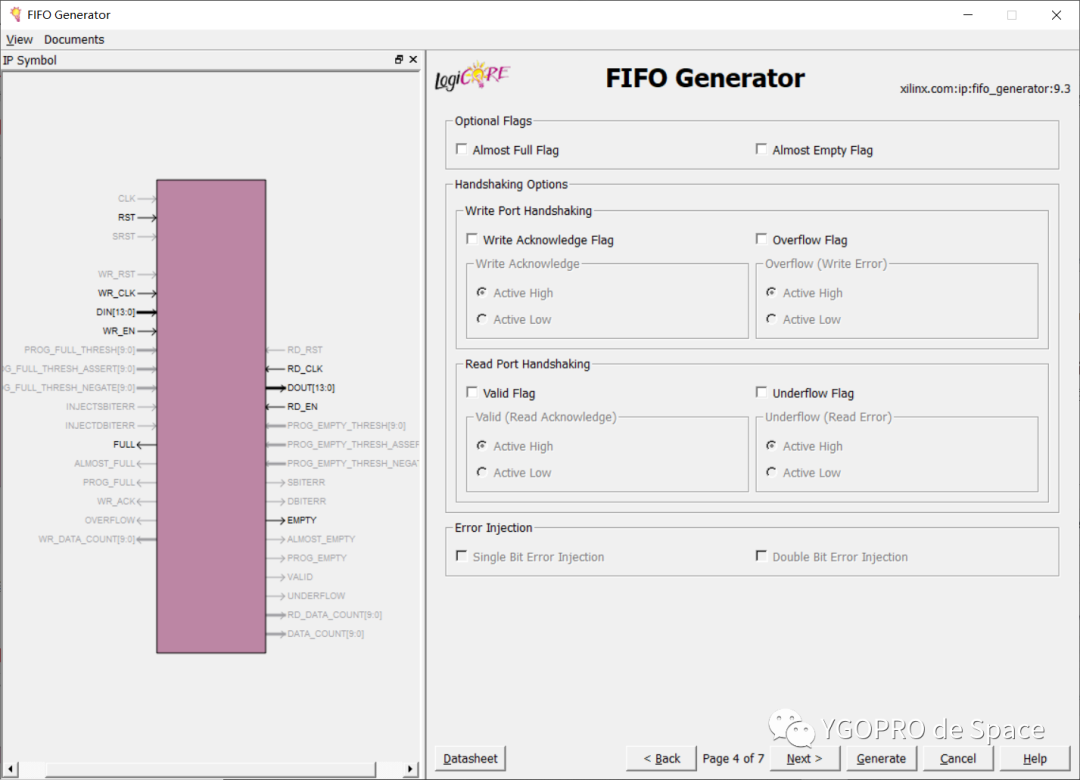

第四頁

Almost Full Flag 和 Almost Empty Flag 指示FIFIO快要滿/空,根據(jù)需求選擇。

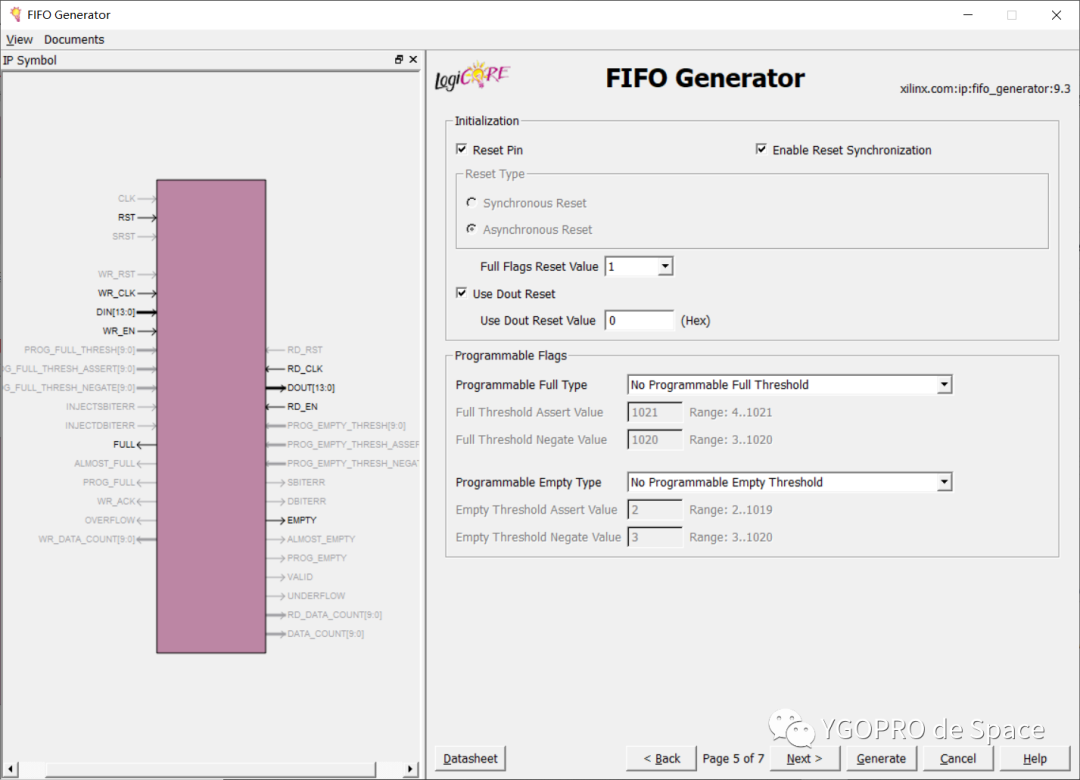

第五頁

Programmable Full Type 和 Programmable Empty Type 是:根據(jù)需要設(shè)置提前多少個(gè)數(shù)據(jù)來給自己提示即將寫滿還是即將讀空。

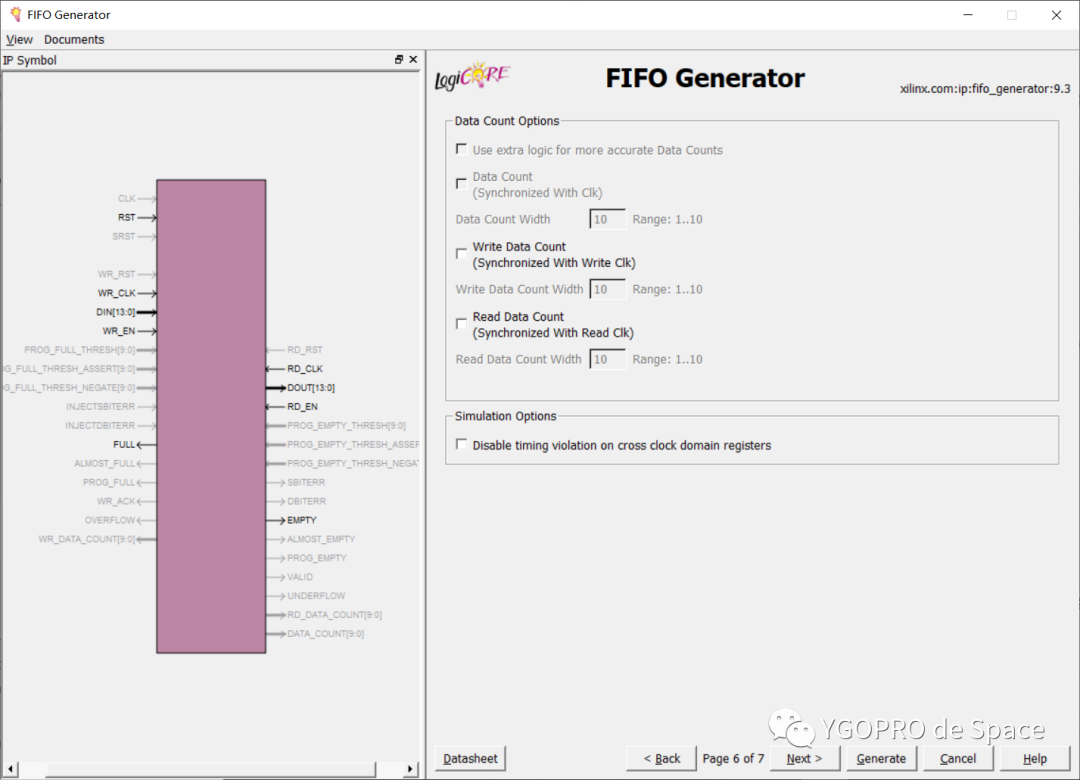

第六頁

默認(rèn)設(shè)置

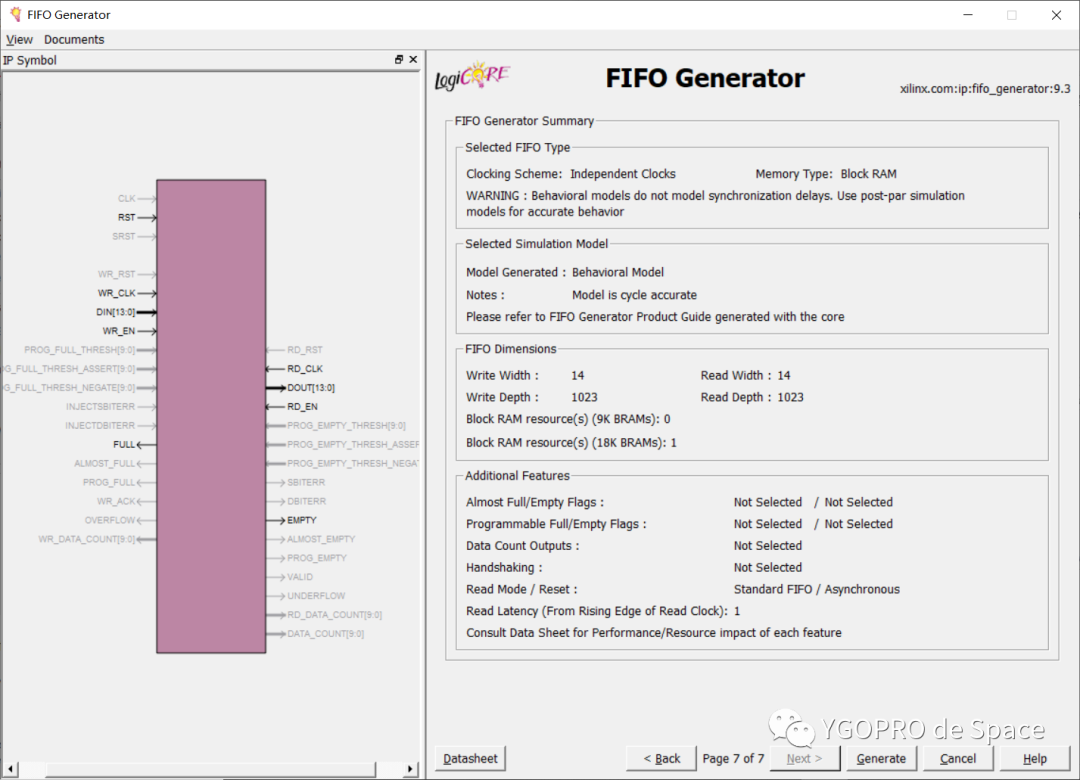

第七頁

最后給出設(shè)置的fifo的報(bào)告,點(diǎn)擊generate生成IP核心。

3、RAM IP核(Block Memory Generator)

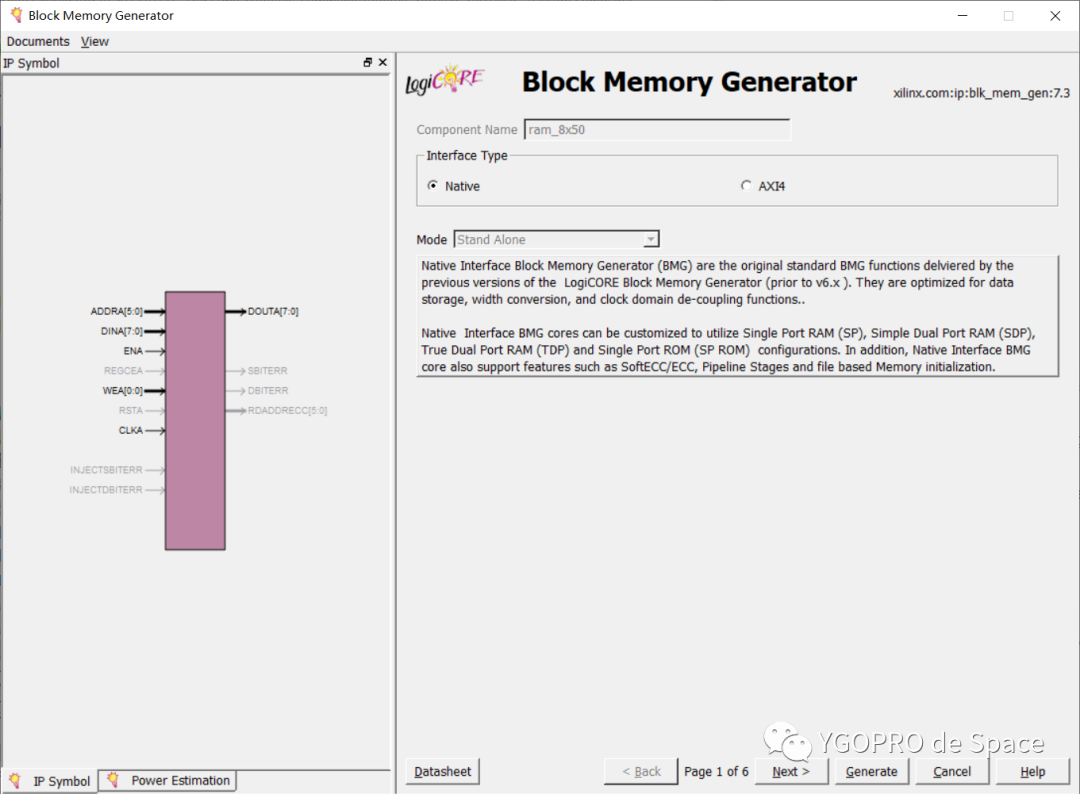

第一頁

InterfaceType選擇Native

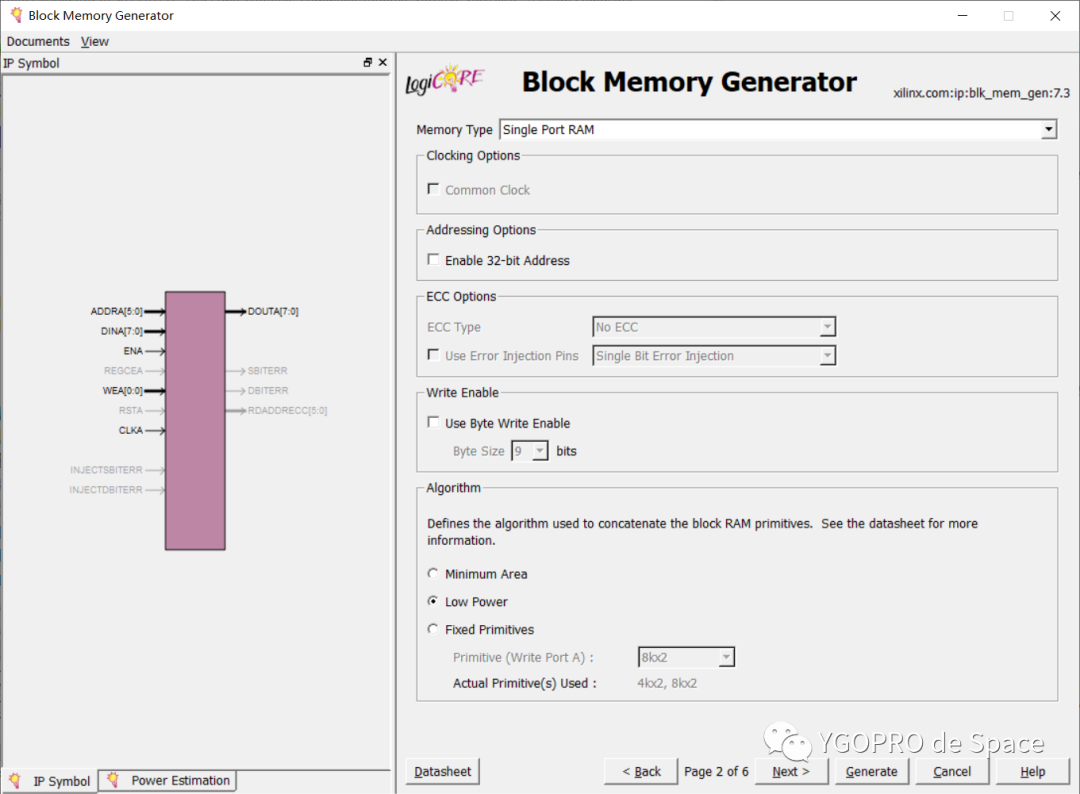

第二頁

Single Port RAM:單口RAM

ADDRA 為地址線

DINA 為數(shù)據(jù)輸入端

ENA 為可選端口,在其為高電平時(shí),才使能

WEA 為寫使能“當(dāng)其為高電平時(shí),DINA數(shù)據(jù)才會(huì)被寫入對(duì)應(yīng)的地址

DOUTA 為A輸出端

CLKA 為時(shí)鐘線

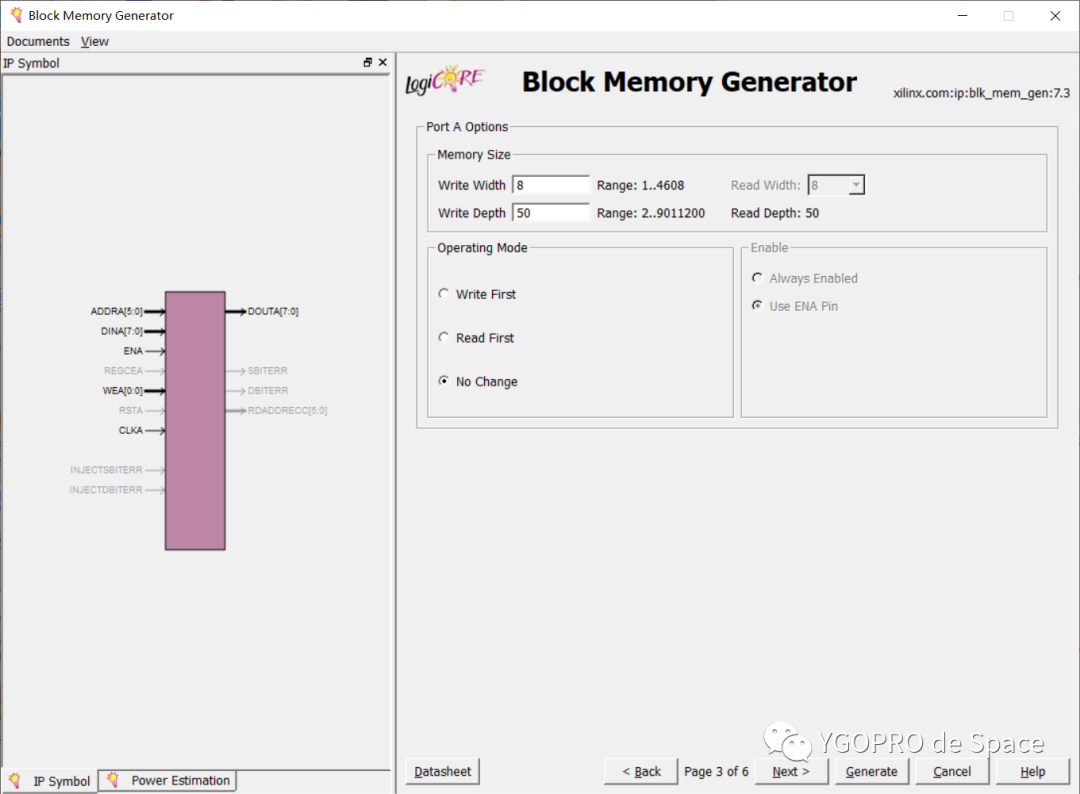

第三頁

配置寫入寬度和深度

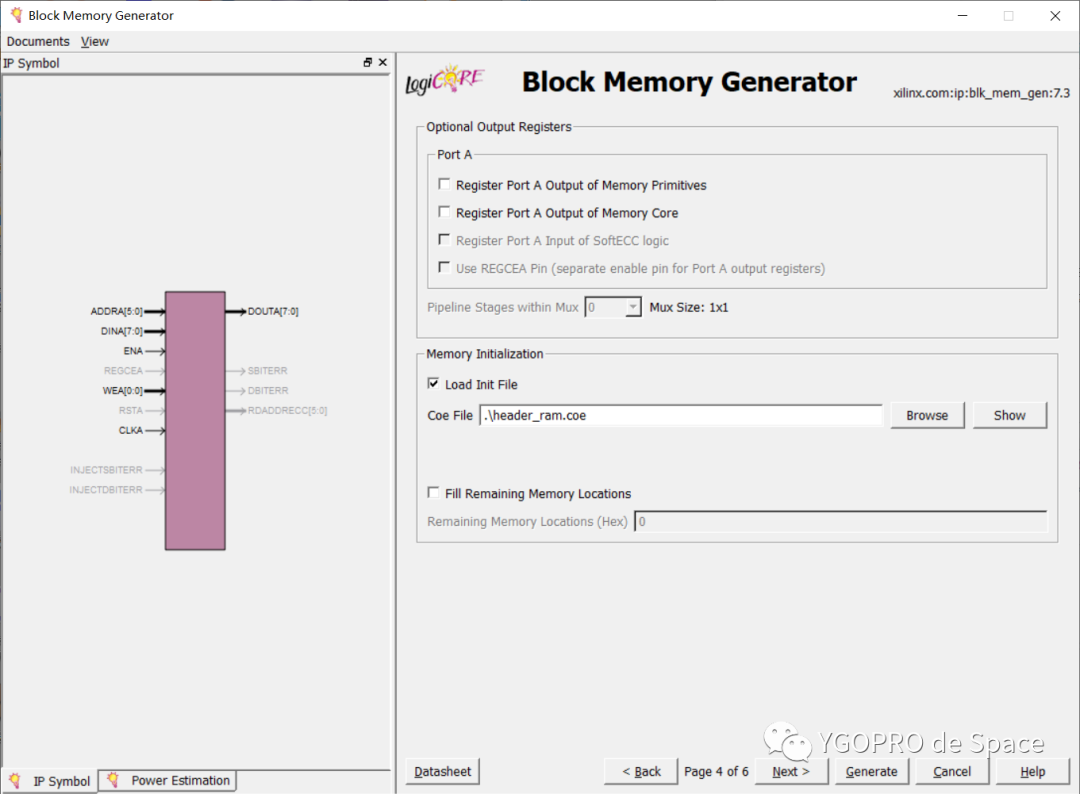

第四頁

加載coe文件:

memory_initialization_radix = 10; //數(shù)據(jù)進(jìn)制

memory_initialization_vector =1,2,3;//數(shù)據(jù),數(shù)據(jù)以分號(hào)結(jié)束

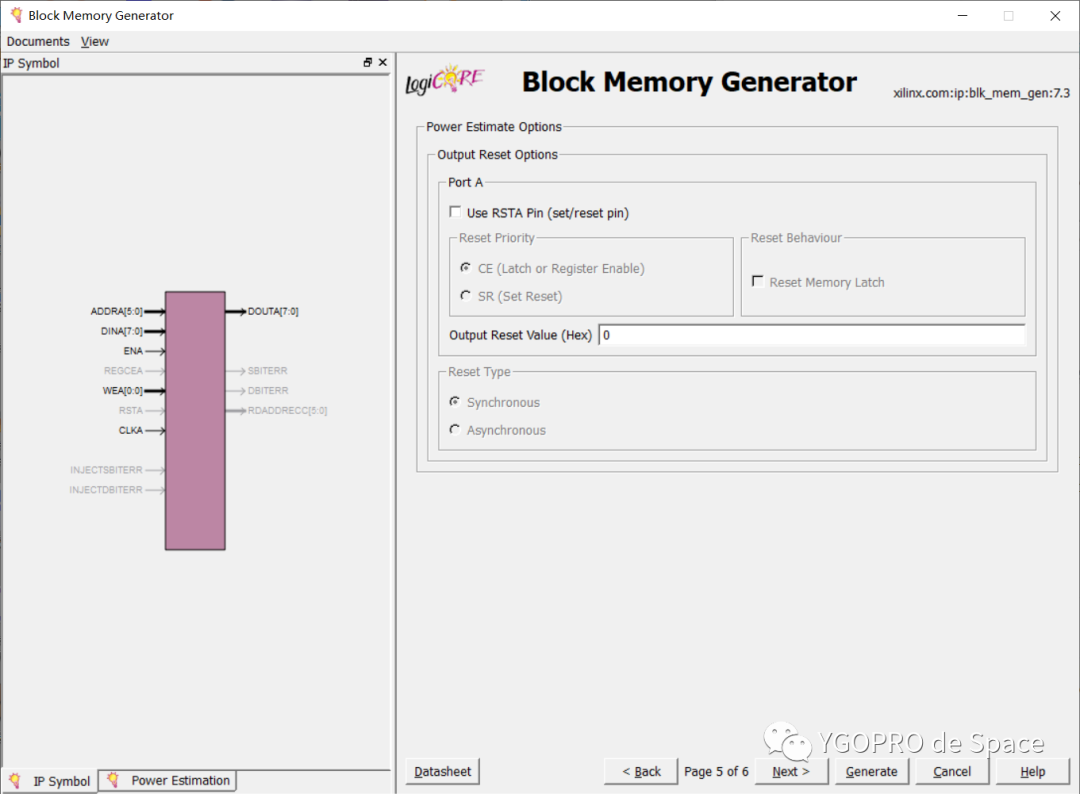

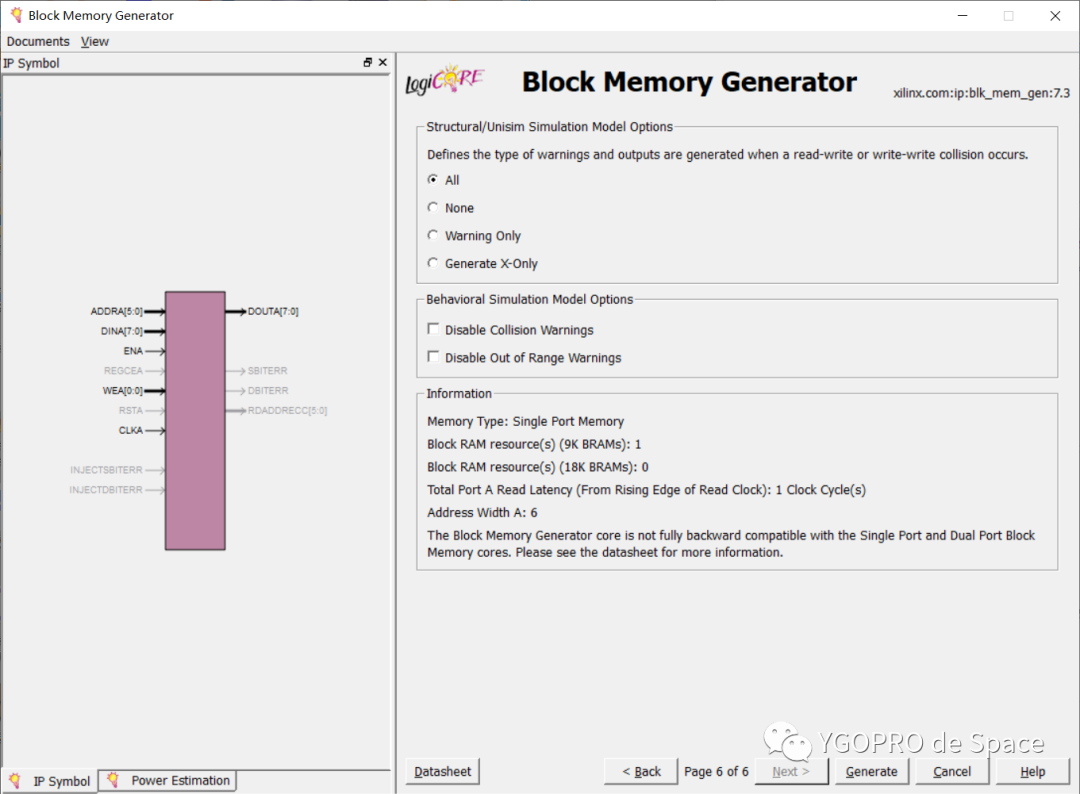

第五六頁

默認(rèn)設(shè)置。

原文標(biāo)題:Xilinx常用IP核配置

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

帶寬

+關(guān)注

關(guān)注

3文章

1040瀏覽量

43370 -

IP

+關(guān)注

關(guān)注

5文章

1863瀏覽量

155844 -

端口

+關(guān)注

關(guān)注

4文章

1104瀏覽量

33966

原文標(biāo)題:Xilinx常用IP核配置

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

基于AXI DMA IP核的DDR數(shù)據(jù)存儲(chǔ)與PS端讀取

E203軟核提高CPU時(shí)鐘頻率方法

VDMA IP核簡介

蜂鳥E203移植到FPGA開發(fā)板前的IP核例化工作

板子的差分時(shí)鐘如何正確地轉(zhuǎn)化為單端

E203移植genesys2(差分時(shí)鐘板)生成比特流文件全過程

Vivado浮點(diǎn)數(shù)IP核的握手信號(hào)

Vivado浮點(diǎn)數(shù)IP核的一些設(shè)置注意點(diǎn)

ram ip核的使用

【RK3568+PG2L50H開發(fā)板實(shí)驗(yàn)例程】FPGA部分 | Pango 的時(shí)鐘資源——鎖相環(huán)

VIVADO自帶Turbo譯碼器IP核怎么用?

FPGA時(shí)序約束之設(shè)置時(shí)鐘組

一文詳解Video In to AXI4-Stream IP核

時(shí)鐘IP核常用設(shè)置

時(shí)鐘IP核常用設(shè)置

評(píng)論