本文介紹的處理方法在國內外很多高速PCB電路里都有應用的. 這里簡單構造了一個“場景”,結合下圖介紹一

2010-06-18 14:43:31 1807

1807

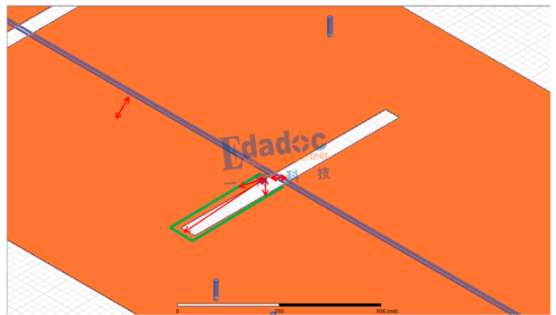

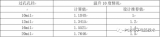

時鐘信號是由PCIE主機給到PCIE從機的,所以信號流向是指向左下角的。而此時的信號回流路徑包含包地路徑和地平面路徑。

2020-11-19 15:26:00 4296

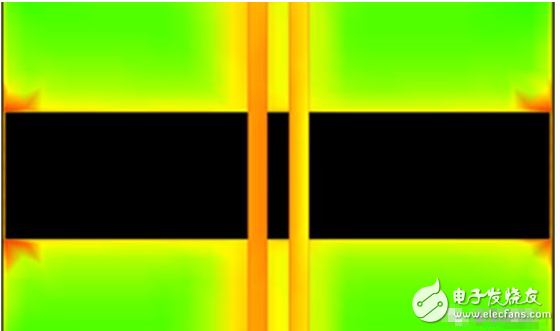

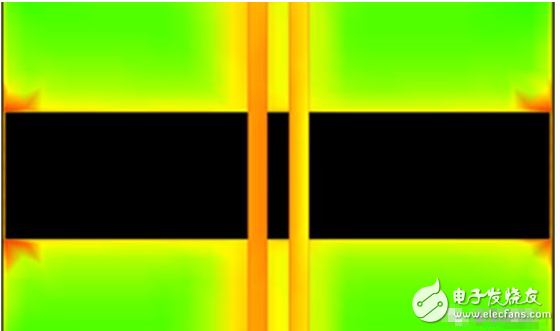

4296 當高速信號發生跨溝現象時,整個電流的環路面積將增加,通常系統的EMC輻射也將增加。同時傳輸線的特征阻抗也將發生變化(如下圖2所示為信號線阻抗變化曲線),信號遇到傳輸線特征阻抗突變點時將發生發射、振鈴等信號完整性問題。

2022-09-15 11:05:12 1527

1527 我在知乎看到了多bit信號跨時鐘的問題,于是整理了一下自己對于跨時鐘域信號的處理方法。

2022-10-09 10:44:57 8118

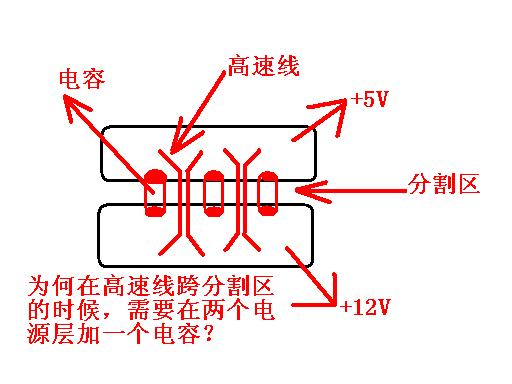

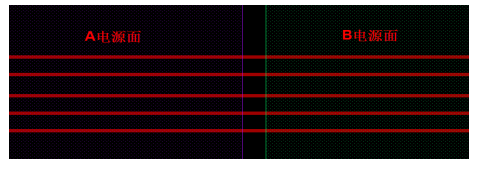

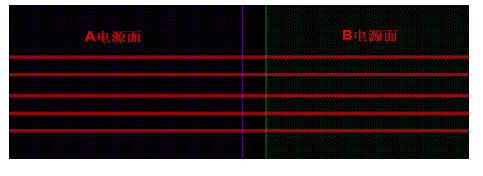

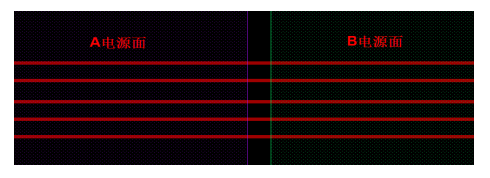

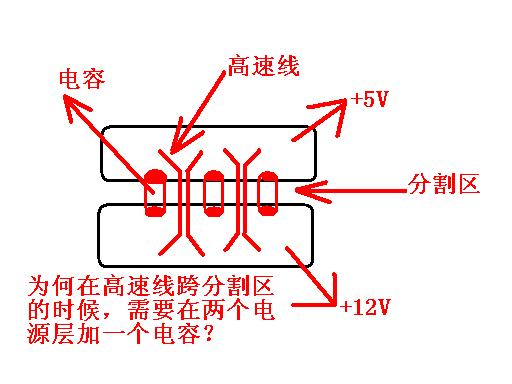

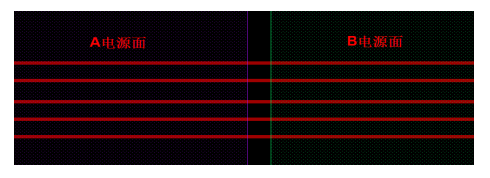

8118 在PCB設計過程中,電源平面的分割或者是地平面的分割,會導致平面的不完整,這樣信號走線的時候,它的參考平面就會出現從一個電源面跨接到另一個電源面,這種現象我們就叫做信號跨分割。

2023-03-09 09:27:48 4099

4099

能會導致設計中的缺陷和問題。為了克服這一挑戰,可以利用凡億skill中的“檢查跨分割”命令。這個工具能夠幫助設計者快速而準確地識別出高速信號參考平面的跨分割問題,從而避免了人工檢查時可能出現的疏漏。通過使用這種自動化

2025-06-19 11:50:05 1998

1998

可以。地平面和電源平面做參考平面還是有區別的,參考平面,給信號提供一個良好的信號回流路徑,那么,信號的回流,最終要回到哪里?電源的負極,若是以電源平面作為參考,回流要通過電源層,再回到電源的負極,不如直接通過地層回流好。...

2021-12-31 08:32:54

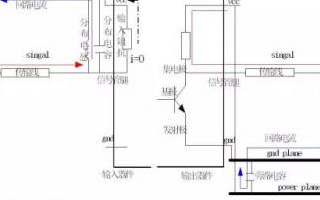

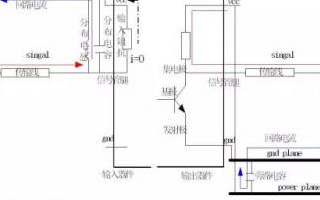

,如SDO、SCK、CONV等數字信號怎么回流呢?下圖中ADC數字信號直接接到數字邏輯ICs,模擬地平面與數字地平面是分割的。

2、如下圖連接,模擬地平面與數字地平面肯定有電壓差,這個電壓差對ADC肯定是有影響的吧?

3、模擬地平面、數字地平面在哪里連接呢?在系統電源地單點接地嗎?

2024-12-24 08:27:14

的控制信號下方進行一小塊覆銅進行兩者之間的橋連接。但是給模擬供電的電源是直接從分割的槽上方跨越過去,這樣,電源的回流路徑不就變大了嗎?會不會產生噪聲,對AD的采樣精度產生影響?

2018-08-19 07:11:08

“長途跋涉”才能形成一個完整的回流通路,而這個通路也是相鄰信號的回流通路,這個相同的回流通路和共地干擾的效果是一樣的,等效為信號之間的串擾。對于一些無法避免的跨電源分割的情況,可以在跨分割的地方跨接

2020-10-23 11:30:00

軌線嚴禁跨分割走線,避免造成阻抗不連續,引起嚴重的信號完整性問題; 當 PCB 板上存在不相容電路時,應該進行分地的處理,但分地不應該造成高速信號線的跨分割走線,也盡量不要造成低速信號線的跨分割走線

2022-06-23 10:23:40

通過外接電纜產生共模輻射;加大與板上其它電路產生高頻信號串擾的可能性(如下圖)。三 PCB 設計對開槽的處理對開槽的處理應該遵循以下原則:需要嚴格的阻抗控制的高速信號線,其軌線嚴禁跨分割走線,避免造成

2020-12-17 09:49:40

在 PCB 設計過程中,由于平面的分割,可能會導致信號參考平面不連續,對于低低頻信號,可能沒什么關系,而在高頻數字系統中,高頻信號以參考平面作返回路徑,即回流路徑,如果參考?面不連續,信號跨分割

2016-10-09 13:10:37

PCB板的跨分割設計,不看肯定后悔

2021-04-23 06:17:14

PCB設計中跨分割的處理高速信號布線技巧

2021-02-19 06:27:15

及一些關鍵的總線信號等與其他信號線布線必須滿足3W原則,且不跨分割,跨分割時需盡量短,至少有一個參考平面,最好是GND,鏈路上過孔盡量少,提示 3W原則:邊緣間距大于或等于2倍的線寬Display

2017-11-03 09:41:25

的跨電源分割的情況,可以在跨分割的地方跨接電容或RC串聯構成的高通濾波器(如10歐電阻串680p電容,具體的值要依自己的信號類型而定,即要提供高頻回流通路,又要隔離相互平面間的低頻串擾)。這樣可能會

2021-11-27 07:00:00

請問大家,所謂的“跨分割平面走線”,這個“分割平面”,是指“被分割的地平面”,還是“被分割的電源平面”,或是統指“被分割的地平面和電源平面”??謝謝

2010-07-06 13:26:39

路徑。如果必須對地線層進行分割,而且必須通過分割之間的間隙布線,可以先在被分割的地之間進行單點連接,形成兩個地之間的連接橋,然后通過該連接橋布線。這樣,在每一個信號線的下方都能夠提供一個直接的電流回流

2009-03-25 11:42:39

的,等效為信號之間的串擾。 對于一些無法避免的跨電源分割的情況,可以在跨分割的地方跨接電容或 RC 串聯構成的高通濾波器(如 10 歐電阻串 680p 電容,具體的值要依自己的信號類型而定,即要提供

2020-08-01 17:30:00

地干擾的效果是一樣的,等效為信號之間的串擾。對于一些無法避免的跨電源分割的情況,可以在跨分割的地方跨接電容或RC串聯構成的高通濾波器(如10歐電阻串680p電容,具體的值要依自己的信號類型而定,即要提供

2020-04-13 08:00:00

在涉及模擬數字混合系統的時候,有人建議電層分割,地平面采取整片敷銅,也有人建議電地層都分割,不同的地在電源源端點接,但是這樣對信號的回流路徑就遠了,具體應用時應如何選擇合適的方法?

2019-05-20 05:35:07

初學習layout時,都在說信號線不可跨分割,但是在工作中為了成本不能跨分割似乎也非絕對。

在后續工作中,跨分割的基礎都是相鄰層有一面完整的GND參考,跨分割發生在相鄰的另外一層。

但是看了快消品

2025-09-16 14:56:37

本帖最后由 eehome 于 2013-1-5 09:57 編輯

數字地和模擬地如何分割?如何降低數字信號和模擬信號之間的相互干擾?本文章將帶你認識分割方法和降低干擾的方法。數字地和模擬地如何分割?如何降低數字信號和模擬信號之間的相互干擾?

2011-11-21 15:47:54

關于模擬數字地分割的問題,還是有些不太明白,想請高手們再指教下。以前我畫板子,數字地和模擬地是分開的,然后通過電阻連接。但是這樣又有人說不可取,因為兩塊地隔開后如果有跨分割的走線,那么這條線的回流

2019-04-23 00:42:05

,回流的路徑必須是完整的,也就要求了信號不能跨分割,否則會引起很大的輻射和串擾。另外,回流平面也不一定總是地,和你的板子元件布局還有信號類型有關。 b)從抑制高頻

2008-07-14 16:27:56

我設計一個四層板,電源有3.3V,5V,12V的,如何在電源層進行信號分割?

2015-07-21 10:58:41

如果信號線必須跨電源或地平面分割的話,則需要橋接電容。那么橋接電容的位置是否要靠近信號線,為什么?有沒有理論根據?

2009-02-10 16:48:50

高速信號回流環路實際分析

2021-01-22 06:36:47

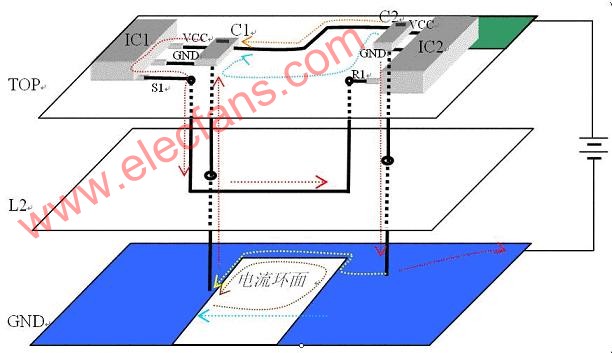

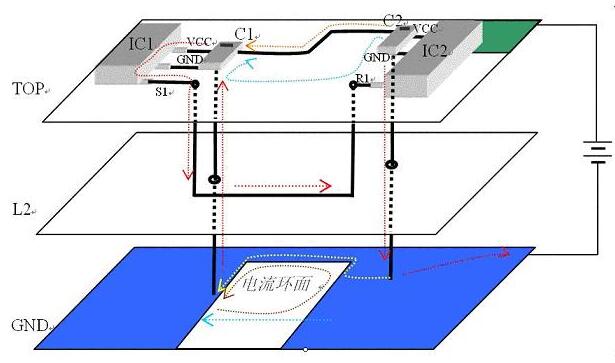

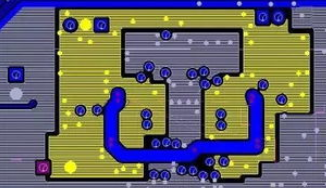

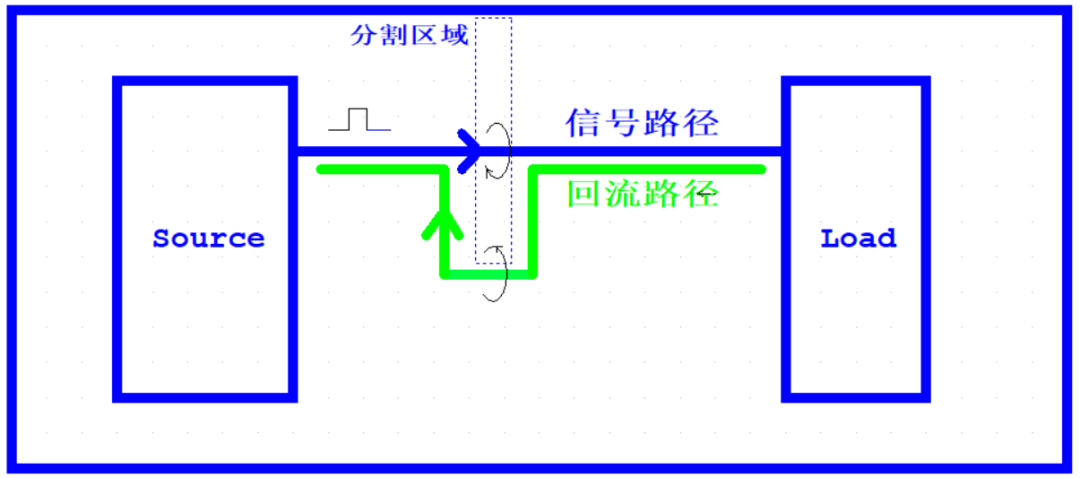

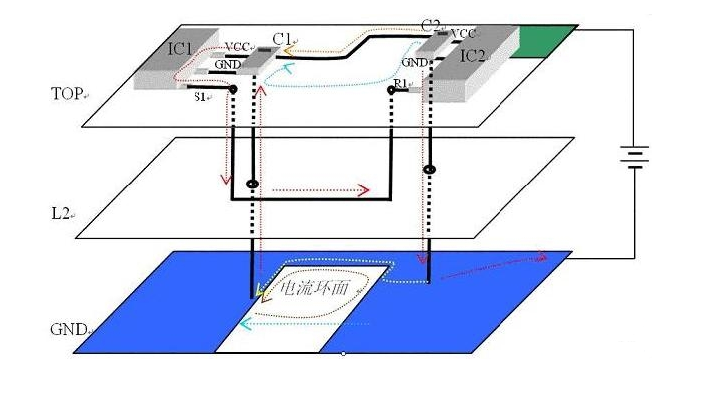

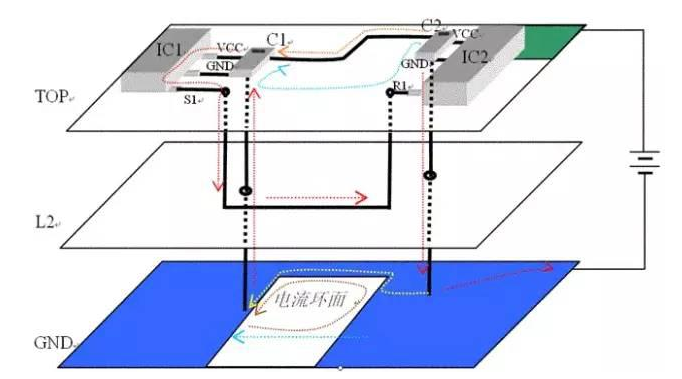

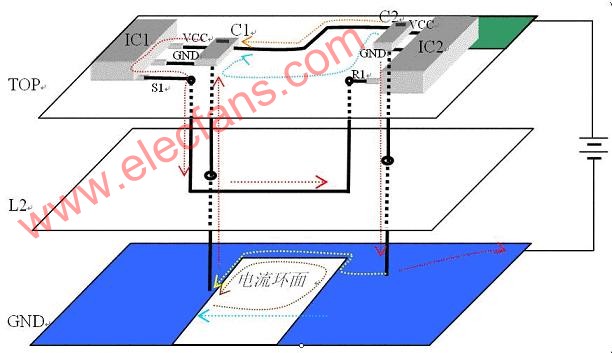

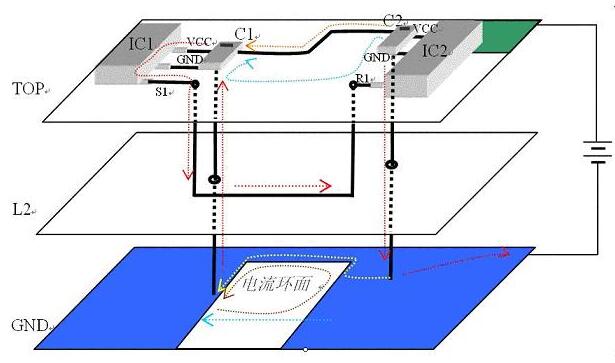

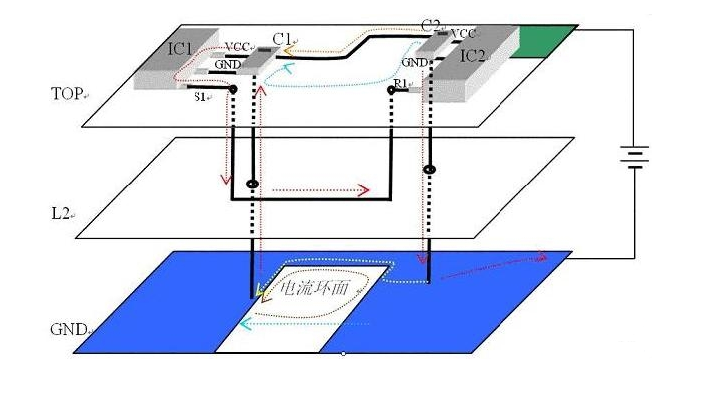

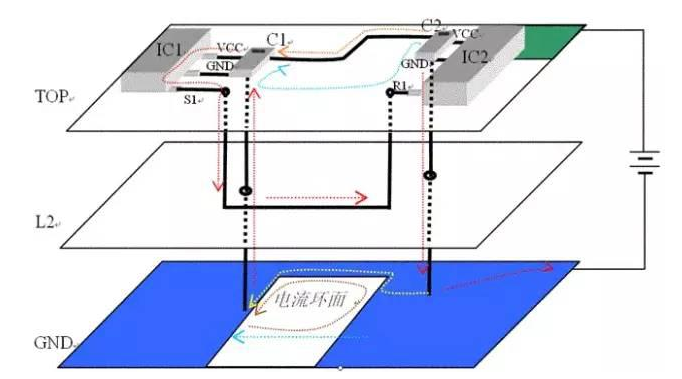

`高速PCB中的信號回流及跨分割這里簡單構造了一個“場景”,結合下圖介紹一下地回流和電源回流以及一些跨分割問題。為方便作圖,把層間距放大。 IC1為信號輸出端,IC2為信號輸入端(為簡化PCB模型

2013-10-24 11:12:40

這里簡單構造了一個“場景”,結合下圖介紹一下地回流和電源回流以及一些跨分割問題。為方便作圖,把層間距放大。 IC1為信號輸出端,IC2為信號輸入端(為簡化PCB模型,假定接收端內含

2018-11-22 15:58:42

工欲善其事必先利其器,在學習PCB設計必須先了解各種要求,只有學習了才能畫出設計需求的效果 廢話不多說后續將陸續上傳相關資料。后面我們在逐步學習 Altium Designer pads cadence等相關設計軟件

2016-07-14 14:54:16

高速PCB中的地回流和電源回流以及跨分割問題分析

2021-04-25 07:47:31

),至于差動信號打 Via 后旁邊要拱幾個 STItchingVia,那又是另外的故事了!甚或是最后不得已需添加縫補電容以填補那些跨不過壕溝(Moat),而導致成本增加以完善回流路徑,如下圖(四)TI

2021-02-05 07:00:00

的效果是一樣的,等效為信號之間的串擾。對于一些無法避免的跨電源分割的情況,可以在跨分割的地方跨接電容或RC串聯構成的高通濾波器(如10歐電阻串680p電容,具體的值要依自己的信號類型而定,即要提供高頻

2021-08-04 06:30:00

地的分割和數字信號的關系:著重研究的是數字信號在跨越割裂大地的印制線上傳輸的問題.計算過程中采用�方法對此問題的電磁場分布進行了模擬.并第一次定量地分析了數字信號在

2009-08-27 23:09:47 0

0 分割電源層的經典技巧及信號完整性處理絕招

2007-11-08 09:11:44 4143

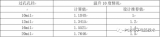

4143 高速信號號在電源層分割時的處理辦法

2007-11-08 09:13:59 4086

4086

高速PCB中的信號回流及跨分割

這里簡單構造了一個“場景”,結合下圖介紹一下地回流和電源回流以及一些跨分割問題。為方便

2009-11-17 08:56:03 1188

1188 本文以高速系統的差分信號回流路徑為基本出發點, 著重介紹了差分信號的參考平面的開槽間隙對回流路徑的影響。通過Ansoft-HFSS 對信號回路進行建模與參數分析;提取全波模型,在H

2011-11-09 09:33:14 85

85 回流路徑與傳輸線模型建構及信號完整性分析

2011-12-20 17:37:57 53

53 跨時鐘域信號的同步方法應根據源時鐘與目標時鐘的相位關系、該信號的時間寬度和多個跨時鐘域信號之間的時序關系來選擇。如果兩時鐘有確定的相位關系,可由目標時鐘直接采集跨

2012-05-09 15:21:18 63

63 圖像分割—基于圖的圖像分割圖像分割—基于圖的圖像分割

2015-11-19 16:17:11 0

0 在高速電路中經常會遇到跨分割設計,在2017年的時候也寫過一篇跨分割設計的文章。

今天給大家分享一篇跨分割設計對信號的影響。

2018-01-23 15:49:53 8663

8663

不應該跨分割,因為這將會增加串擾,并且很有可能過不了EMC,有人說如果小心設計層疊結構和電源/地平面上分割縫隙的寬度,應該不會有問題…那么應該是什么樣的呢?本文就來討論一下信號通過分割平面時的情況。

2018-02-27 11:39:11 9140

9140

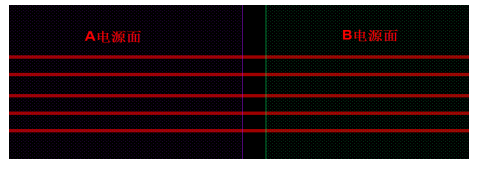

如果原理圖將模擬地和數字地分開,原則上電源不建議跨分割,對跨分割的電源建議通過磁珠(或者“Π”型濾波)來解決。在模擬電源跨界的磁珠旁邊再增加一個數字地和模擬地的跨接磁珠用于模擬電源和數字電源回流。

2018-07-20 17:08:32 5897

5897 IC1為信號輸出端,IC2為信號輸入端(為簡化PCB模型,假定接收端內含下接電阻)第三層為地層。IC1和IC2的地均來自于第三層地層面。頂層右上角為一塊電源平面,接到電源正極。C1和C2分別為IC1、IC2的退耦電容。圖上所示的芯片的電源和地腳均為發、收信號端的供電電源和地。

2019-06-14 15:25:06 5883

5883

那么到底什么是回流呢?回流又是如何影響信號完整性的呢?請看文中實例。作為一個對技術有追求的工程師來說,一定要多問幾個為什么?

2019-07-11 15:23:42 7187

7187

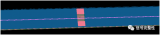

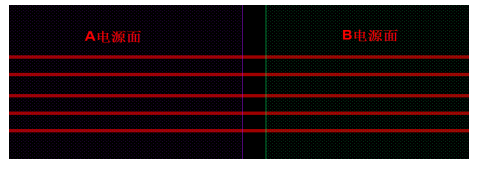

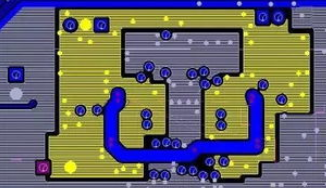

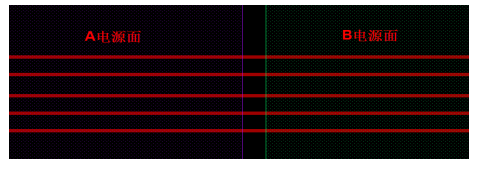

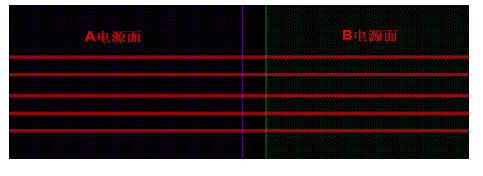

做電源分割時應盡量避免相鄰信號線跨分割情況,信號在跨分割(如下圖示紅色信號線有跨分割現象)處因參考平面不連續會有阻抗突變情況產生,會產生EMI、串擾問題,在做高速設計時,跨分割會對信號質量影響很大。

2020-04-26 16:53:21 2218

2218 數字電路通常借助于地和電源平面來完成回流。高頻信號和低頻信號的回流通路是不相同的,低頻信號回流選擇阻抗最低路徑,高頻信號回流選擇感抗最低的路徑。

2020-04-13 17:37:15 4669

4669

但在高頻時,PCB所呈現的分布特性會對信號產生很大影響。

2020-03-28 11:06:57 2012

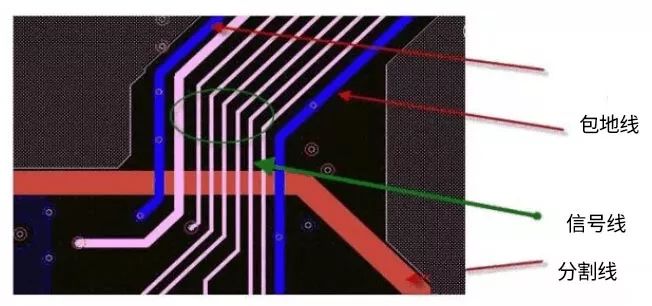

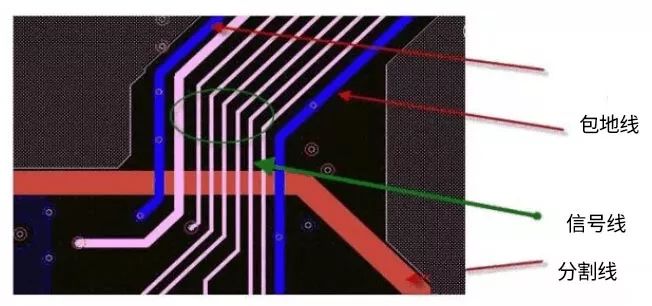

2012 跨線橋接。常見的就是在信號層對跨分割的“信號包地處理”,也可能包的是其他網絡的信號線,這個“包地線”要盡量粗。

2019-11-26 15:53:23 9947

9947

區分模擬和數字部分的目的是為了抗干擾,主要是數字電路對模擬電路的干擾。但是,分割可能造成信號回流路徑不完整,影響數字信號的信號質量,影響系統EMC質量。因此,無論分割哪個平面,要看這樣作,信號回流路徑是否被增大,回流信號對正常工作信號干擾有多大。

2019-12-31 15:26:01 1607

1607

跨分割,對于低速信號,可能沒有什么關系,但是在高速數字信號系統中,高速信號是以參考平面作為返回路徑,就是回流路徑。當參考平面不完整的時候,會出現如下影響。

2020-03-08 11:26:00 6235

6235 在PCB設計過程中,由于平面的分割,可能會導致信號參考平面不連續,對于低低頻信號,可能沒什么關系,而在高頻數字系統中,高頻信號以參考平面作返回路徑,即回流路徑,如果參考?面不連續,信號跨分割,這就會帶來諸多的問題,如EMI、串擾等問題。

2020-03-11 15:00:24 2511

2511 本文檔的主要內容詳細介紹的是信號回流的分析及與信號完整性的關系詳細說明包括了:1,信號回流介紹,2,微帶線回流的分析,3,帶狀線回流的分析,4,信號換層回流的分析,5,總結。

2020-05-15 08:00:00 6

6 在PCB設計過程中,電源平面的分割或者是地平面的分割,會導致平面的不完整,這樣信號走線的時候,它的參考平面就會出現從一個電源面跨接到另一個電源面,這種現象我們就叫做信號跨分割。

2020-09-02 11:06:40 7867

7867

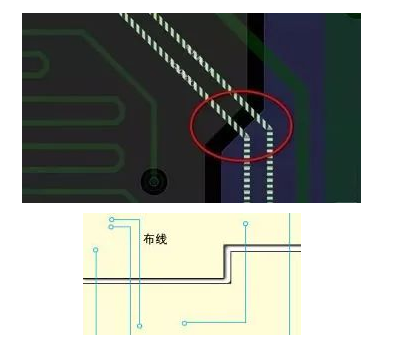

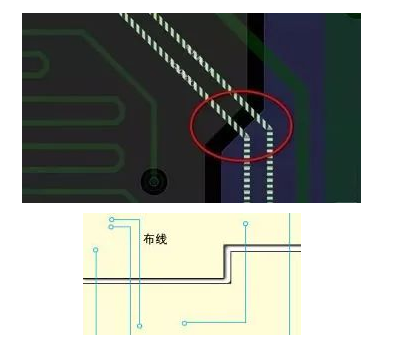

在PCB設計過程中經常會遇到高多層、高密度的設計,那么這種情況下就難免出現跨分割的情況,如下圖所示:

2020-09-25 17:14:36 5541

5541 最大的電容是信號路徑與地平面之間組成的電容。在跨分割的地方最大的電容變成了信號路徑與旁邊的信號路徑所組成的這個電容。

2021-04-11 09:49:20 5657

5657

數字電路通常借助于地和電源平面來完成回流。高頻信號和低頻信號的回流通路是不相同的,低頻信號回流選擇阻抗最低路徑,高頻信號回流選擇感抗最低的路徑。

2020-11-18 09:52:58 18949

18949 在PCB設計過程中,電源平面的分割或者是地平面的分割,會導致平面的不完整,這樣信號走線的時候,它的參考平面就會出現從一個電源面跨接到另一個電源面,這種現象我們就叫做信號跨分割。

2022-02-12 10:41:29 5861

5861

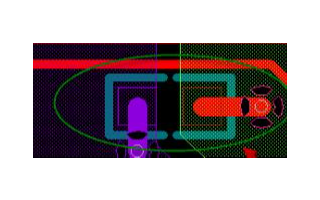

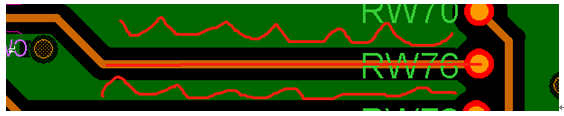

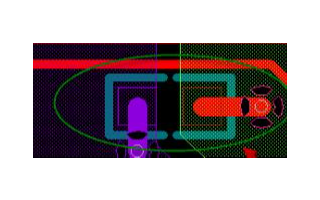

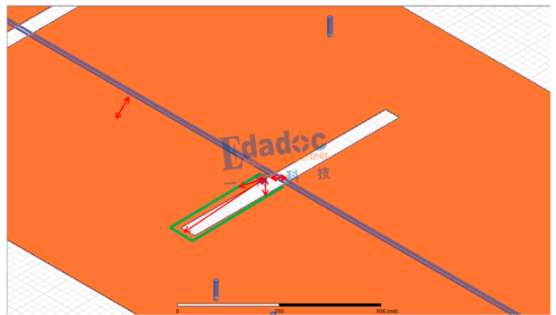

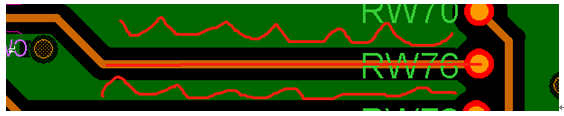

1、實際走線分析:

上面的走線橘色為信號走線,周圍綠色(波浪標注)為周圍包地,下方為第二層完整地平面。

從上圖來看設計師的本意是好的,有參考地平面,周圍也有包地,此時設計正確的話可以保證回流

2022-02-10 09:43:35 3899

3899

1、實際走線分析:

上面的走線橘色為信號走線,周圍綠色(波浪標注)為周圍包地,下方為第二層完整地平面。

從上圖來看設計師的本意是好的,有參考地平面,周圍也有包地,此時設計正確的話可以保證回流路徑

2021-02-24 06:51:51 4

4 在PCB設計過程中,電源平面的分割或者是地平面的分割,會導致平面的不完整,這樣信號走線的時候,它的參考平面就會出現從一個電源面跨接到另一個電源面,這種現象我們就叫做信號跨分割。

2021-03-18 06:24:14 5

5 為改善單目圖像語義分割網絡對圖像深度變化區域的分割效果,提出一種結合雙目圖像的深度信息和跨層次特征進行互補應用的語義分割模型。在不改變已有單目孿生網絡結構的前提下,利用該模型分別提取雙目左、右輸入

2021-03-19 14:35:24 21

21 為實現心音信號的有效分割,提出一種基于非平穩系統辨識的心音信號特征包絡自適應分割方法。根據非平穩系統辨識原理,提取心音信號特征包絡并對包絡作平滑與展寬處理。基于重尺度小波降噪信噪比與特征包絡均值

2021-03-30 11:11:30 15

15 PCB工程師注意啦:通常pcb上的打過孔換層會引起鏡像平面的非連續性,這就會導致信號的最佳回流途徑被破壞。 我們都知道,信號打孔換層會改變信號的回流路徑,如果信號換層,回流路徑也跟著換層,但是在信號

2021-05-29 14:32:12 7361

7361

信號在信號線和 參考平面上傳送 ● 在傳統的低速設計中,系統中的回路電流沿著最小的電阻路徑回流,而在高速系統中,電流沿著最小的阻抗回路回流。在高頻下,回路的電感表現出的感抗遠遠大于其本身的電阻值,因此最小阻抗路徑也就

2022-08-02 16:54:46 1090

1090 要獲得最佳的PCB設計,需要了解信號的回流的實際路徑。電路的信號完整性和EMC性能,直接與電流環路形成的電感相關,而電感大小則主要與環路的面積相關。

2022-11-14 11:42:13 6522

6522 通常PCB上的打過孔換層會引起鏡像平面的非連續性,這就會導致信號的最佳回流途徑被破壞。 我們都知道,信號打孔換層會改變信號的回流路徑,如果信號換層,回流路徑也跟著換層,但是在信號換層處過孔不能將信號回路連通起來,將引起信號回路面積增大,從而導致EMC問題。

2022-12-20 09:59:30 5042

5042 在PCB設計過程中,電源平面的分割或者是地平面的分割,會導致平面的不完整,這樣信號走線的時候,它的參考平面就會出現從一個電源面跨接到另一個電源面,這種現象我們就叫做信號跨分割。

2022-12-23 09:34:03 9387

9387

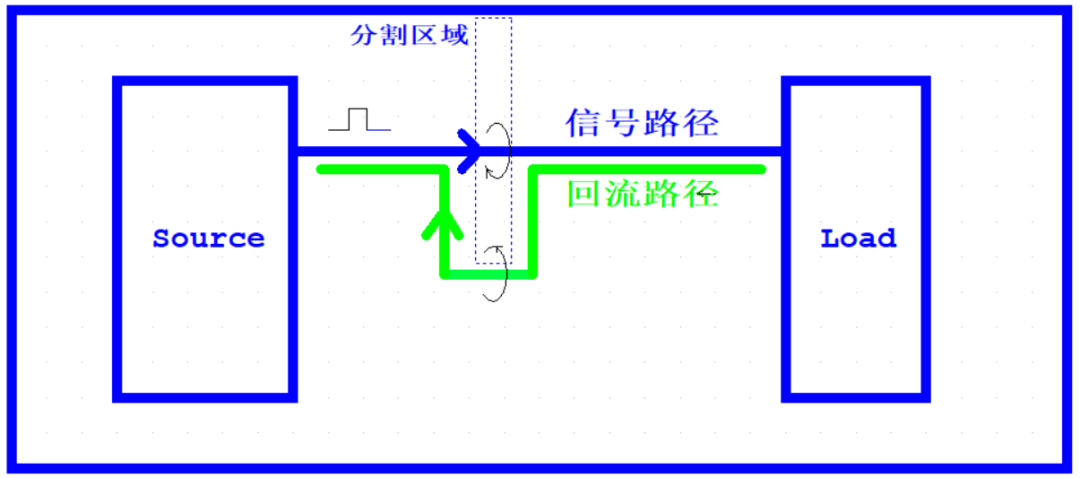

下圖所示為一個信號流向及其回流示意圖。基于基爾霍夫定律,電流是閉環的,也就是說任意一個電路的節點只要有電流流出就一定會有電流流入,返回到節點(通常是驅動器)的電流通常就叫返回電流

2023-02-14 16:49:33 2376

2376 跨分割,對于低速信號可能沒有什么關系,但是在高速數字信號系統中,高速信號是以參考平面作為返回路徑,就是回流路徑。

2023-02-21 13:44:36 2084

2084 單位寬(Single bit)信號即該信號的位寬為1,通常控制信號居多。對于此類信號,如需跨時鐘域可直接使用xpm_cdc_single

2023-04-13 09:11:37 2057

2057 通常在信號跨分割處擺放一個0402或者0603封裝的瓷片電容,電容的容值在0.01uF或者是0.1 uF,如果空間允許,可以多添加幾個這樣的電容;同時盡量保證信號線在縫補電容 200mil 范圍內,距離越小越好。

2023-04-26 09:03:00 879

879 當 RPQF 值越趨近于 1,則表示信號布線與與回流路徑是越貼近的,越高則代表回流路徑越曲折繞越遠的路徑。

2023-04-17 10:28:11 5208

5208 所謂信號回流是指信號在傳輸時,信號電流以走線為載體,從驅動端流向負載端,再由負載端通過最低阻抗路徑返回到信號的驅動端。

2023-04-18 09:03:43 2573

2573 在PCB設計過程中,電源平面的分割或者是地平面的分割,會導致平面的不完整,這樣信號走線的時候,它的參考平面就會出現從一個電源面跨接到另一個電源面,這種現象我們就叫做信號跨分割。

2023-04-28 09:08:21 2297

2297

做電源分割時應盡量避免相鄰信號線跨分割情況,信號在跨分割(如下圖示紅色信號線有跨分割現象)處因參考平面不連續會有阻抗突變情況產生,會產生 EMI、串擾問題,在做高速設計時,跨分割會對信號質量影響很大。

2023-08-22 09:25:35 873

873

高頻下信號會鏡像回流,但是由于有分割,導致信號不能鏡像回流。信號回流繞過分割區域形成大的環路,環形天線效應使差模輻射增加。

2023-10-01 17:33:00 1330

1330

在低頻時,如果S1端輸出高電平,整個電流回路是電源經導線接到VCC電源平面,然后經橙色路徑進入IC1,然后從S1端出來,沿第二層的導線經R1端進入IC2,然后進入GND層,經紅色路徑回到電源負極。

2023-10-16 15:18:36 1475

1475

地線回流是什么意思?地線回流問題? 地線回流是指電力系統中,地線攜帶了電流從而形成回路的現象。在正常情況下,電力系統的電流應該是通過相線和中性線流動的,而地線只應該用來提供安全接地。然而,當電力系統

2023-11-17 12:36:00 4681

4681 縫補電容Stiching Capacitor+通常在信號跨分割處擺放一個 0402 或者 0603封裝的瓷片電容,電容的容值在 0.01uF 或者是 0.1 uF,如果空間允許,可以多添加幾個?樣的電容?同時盡量保證信號線在縫補電容 200mil 范圍內,距離越小越好?

2023-11-23 15:25:50 1051

1051 什么是信號回流路徑? 信號回流路徑,也稱為信號返回路徑,是指電子系統中信號從輸出端返回到輸入端的路徑。在一個電路或系統中,信號在經過各種組件和部件的作用后,可能會反射、散射、干擾等,形成回流路徑

2023-11-24 14:44:50 3285

3285 的參考平面就會出現從一個電源面跨接到另一個電源面,這種現象我們就叫做信號跨分割。 跨分割現象示意圖 跨分割,對于低速信號可能沒有什么關系,但是在高速數字信號系統中,高速信號是以參考平面作為返回路徑,就是回流路徑。當參考平面不完整的時

2023-12-04 10:26:34 1525

1525

應該說從原理上講是一樣的。因為電源和地對高頻信號是等效的。區分模擬和數字部分的目的是為了抗干擾,主要是數字電路對模擬電路的干擾。但是,分割可能造成信號回流路徑不完整,影響數字信號的信號質量,影響系統EMC質量。

2023-12-15 16:40:16 496

496 我們PCB中的信號都是阻抗線,是有參考的平面層。但是由于PCB設計過程中,電源平面的分割或者是地平面的分割,會導致平面的不完整,這樣,信號走線的時候,它的參考平面就會出現從一個電源面跨接到另一個電源面,這種現象我們就叫做信號跨分割。

2024-01-03 15:12:19 1975

1975

數字電路通常借助于地和電源平面來完成回流。高頻信號和低頻信號的回流通路是不相同的,低頻信號回流選擇阻抗路徑,高頻信號回流選擇感抗的路徑。

2024-01-04 15:34:07 1240

1240

在PCB設計過程中,電源平面的分割或者是地平面的分割,會導致平面的不完整,這樣信號走線的時候,它的參考平面就會出現從一個電源面跨接到另一個電源面,這種現象我們就叫做信號跨分割。

2024-01-10 15:28:13 2293

2293

在PCB設計過程中經常會遇到高多層、高密度的設計,那么這種情況下就難免出現跨分割的情況

2024-05-27 09:34:57 1965

1965

今天講一下高速信號線跨溝對眼圖抖動的影響。Chrent高速信號跨溝及信號回流的基本概念下圖所示為一個信號流向及其回流示意圖。基于基爾霍夫定律,電流是閉環的,也就是說任意一個電路的節點只要有電流

2025-06-04 17:32:44 721

721

電子發燒友App

電子發燒友App

評論