加利福利亞州圣荷西2022年4月29日?/美通社/ -- 面向當今片上系統(SoC)市場的領先Total IP?解決方案提供商Arasan Chip Systems宣布,其eMMC? 5.1 PHY

2022-04-29 13:53:55 2987

2987

為包括汽車在內的所有移動產品提供半導體IP的領先提供商Arasan宣布推出其第2代CAN IP 加利福尼亞州圣何塞2022年5月23日?/美通社/ -- Arasan宣布即刻起提供CAN 2.0

2022-05-23 11:14:57 4655

4655

介紹了一款可配置的USB IP核設計,重點描述USB IP核的結構劃分,詳細闡述了各模塊的設計思想。為了提高USB lP的可重用性,本USB IP核設計了總線適配器,經

2010-07-17 10:39:51 3124

3124

MIPI RFFE 3.0SM主機IP和移動行業設備核心IP將立即上市。 Arasan的MIPI RFFE 3.0SM?Total IPTM解決方案以相對較高的52Mhz速度運行,具有眾多增強觸發功能

2022-05-19 15:56:12 1816

1816

本帖最后由 eehome 于 2013-1-5 09:59 編輯

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改

2011-07-06 14:15:52

IP核簡介IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM控制器、PCI接口等等設計成可修改參數的模塊,讓其它用戶可以直接調用這些模塊,以避免重復勞動。隨著CPLD

2011-07-15 14:46:14

我想問一下,在quartus上直接調用IP核和在qsys中用IP核有什么區別?自個有點迷糊了

2017-08-07 10:09:03

我調用了一個ip核 在下載到芯片中 有一個time-limited的問題 在完成ip核破解之后 還是無法解決 但是我在Google上的找到一個解決方法就是把ip核生成的v文件加到主項目文件中就是上面

2016-05-17 10:28:47

用Quartus II 調用IP核時,在哪可以查看IP核的例程

2014-07-27 20:28:04

我用的是xinlinx spartan6 FPGA,我想知道它的IP核RAM是與FPGA獨立的,只是集成在了一起呢,還是占用了FPGA的資源來形成一個RAM?如果我以ROM的形式調用該IP核,在

2013-01-10 17:19:11

FPGA的IP軟核使用技巧主要包括以下幾個方面:

理解IP軟核的概念和特性 :

IP軟核是指用硬件描述語言(如VHDL或Verilog)描述的功能塊,但并不涉及具體的電路實現細節。它通常只經過功能

2024-05-27 16:13:24

本帖最后由 gk320830 于 2015-3-8 09:29 編輯

LCD的通用驅動電路IP核設計 摘 要:本文介紹了一種新型的LCD驅動電路IP核的總體設計,采用自頂向下的設計方法將其

2012-08-12 12:28:42

的SOPC系統中設計了LCD顯示驅動IP核,并下載到Cyclone系列的FPGA中,實現了對LCD的顯示驅動。

2019-08-06 08:29:14

大家好,有沒有誰比較熟悉ALTERA公司的VIP系列ip核,我們用該系列IP核中的某些模塊(主要是scaler和interlacer)來實現高清圖像轉標清圖像(具體就是1080p50轉576i30

2015-04-13 14:12:18

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因為工程中很多IP核不能用所以在重新生成過程中發現了這個問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

quartus 編譯顯示沒有ip核權限,生成的pof文件是time-limited,然后我在網上找了一個全ip權限的licsense文件,HOSTID也替換好了,可是編譯又顯示該lic文件沒有我要用

2017-01-16 20:16:27

大家伙,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-15 12:05:13

通過Quartus II 軟件創建PLL IP核。首先,要新建一個工程,這個方法在之前的帖子中已經發過,不會的可以查看前面的相關帖子。創建好自己的工程:打開如下的菜單

2016-09-23 21:44:10

前面建好了mif文件,下面就要創建ROM IP核了。首先,我們新建一個工程。菜單欄:Tools --> MegaWizardPlug-InManager ,點擊“Next”選擇ROM的IP核

2016-09-25 09:38:33

剛剛接觸IP核做FFT,現在用的是FFTV9.0,已經建立了一個IP核,但是如何仿真呢?是用quartus自帶軟件,還是要用MATLAB?抑或其他?我用的自帶軟件,但是什么也沒有出來。正確的辦法應該怎樣呢,謝謝指點。

2011-04-21 10:22:31

對于深入學習使用FPGA的小伙伴們,特別是一些復雜的、大規模的設計應用,適宜的IP核對開發能起到事半功倍的作用。IP核的概念與我們sdk里庫的概念相似。IP即電路功能模塊,用戶可以直接調用這些模塊

2024-04-29 21:01:16

最近在做一個FIR低通濾波器,利用Matlab 產生濾波系數,導入到Quartus中,再利用其中的FIR IP核進行濾波器設計,在采用分布式全并行結構時,Modelsim 仿真有輸出;如果改為分布式

2018-07-05 08:33:02

quartus ii9.0創建的ip核,生成的一些文件,(.qip、 add_sub_bb.v、add_sub.v)這些文件都有用嗎,想在其他工程里調用這些IP核,這幾個文件全部要添加嗎?

2013-07-02 17:20:01

核的分類和特點是什么?基于IP核的FPGA設計方法是什么?

2021-05-08 07:07:01

、ARM的AMBA等。因為核的多樣性,使用完全相同的接口是不現實的,OCP將軟件中的分層概念應用到IP核接口,提供一種具有通用結構定義、可擴展的接口協議,方便了IP核與系統的集成。OCP協議使IP核與系統

2019-06-11 05:00:07

,LCD液晶顯示器憑借功耗低、體積小、輕薄及控制驅動簡單等特點,在智能儀器、儀表和低功耗電子產品中得到了廣泛應用。以深圳秋田視佳實業有限公司的液晶顯示模塊CBGl28064為例,告訴大家, 如何在SOPC的NiosII中設計LCD顯示驅動IP核?實現了對LCD的顯示驅動。

2019-08-05 07:56:59

我正在嘗試將Xilinx MIG IP Core從1.7版升級到1.9版。 Coregen UI左側有一個方便的“升級IP核”按鈕,但它顯示為灰色。我需要做什么才能進行IP核升級?我在Kintex

2019-11-04 09:26:19

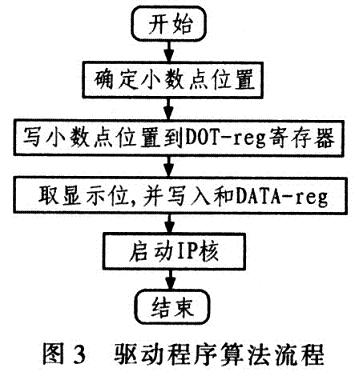

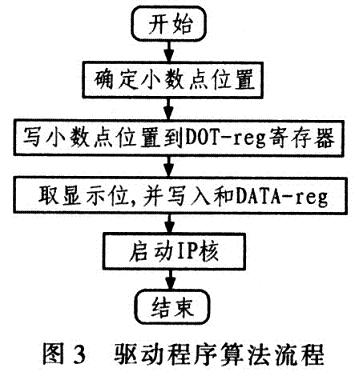

時,Builder開發工具中沒有提供現成的數碼管顯示IP核,這使設計者工作量增加。這里把數碼管控制器設計為一個共陰極(或共陽極)7段數碼管動態顯示IP核,并給出此核的一個參考驅動程序。

2019-08-09 06:09:05

的多樣性,使用完全相同的接口是不現實的,OCP將軟件中的分層概念應用到IP核接口,提供一種具有通用結構定義、可擴展的接口協議,方便了IP核與系統的集成。OCP協議使IP核與系統的接口與IP核的功能無關

2018-12-11 11:07:21

什么是三相全控橋整流電路?怎樣去設計IP軟核?怎樣對IP軟核進行仿真及驗證?

2021-04-23 07:12:38

我用MATLAB設計好單位增益的濾波器系數,然后導入 FIR 的IP核里面,系數轉換成定點數了,但是此時顯示的濾波器幅頻特性曲線卻是100dB的放大倍數,求問怎么讓其變成單位增益?

2018-01-27 13:53:00

請問Altera RAM IP核怎么使用?

2022-01-18 06:59:33

章禮宏 范全潤1 引言隨著電路規模不斷擴大,以及競爭帶來的上市時間的壓力,越來越多的電路設計者開始利用設計良好的、經反復驗證的電路功能模塊來加快設計進程。這些電路功能模塊被稱為IP

2019-07-29 08:33:45

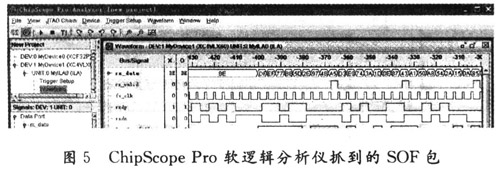

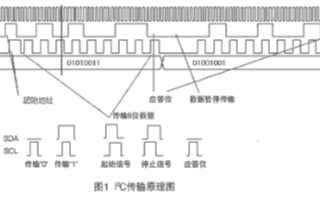

,我國也迫切需要發展自己的IP核。本文針對I2C的主方式串行擴展通信的特點,詳細給出設計過程和結果。1 IP核簡介 IP核是指:將一些在數字電路中常用但比較復雜的功能塊,如FIR濾波器、SDRAM

2019-04-12 07:00:09

IP核生成器生成ip后有兩個文件對我們比較有用,假設生成了一個asyn_fifo的核,則asyn_fifo.veo給出了例化該核方式(或者在Edit->Language Template->COREGEN中找到verilog/VHDL的例化方式)

2009-07-21 16:42:12 0

0 本文討論了基于Avalon 總線流傳輸的配置LCD 顯示控制器IP 核的設計,根據自頂向下的設計思想,將IP 核進行層次功能劃分設計,并對IP 核的仿真驗證,最后加入到NiosII 系統中。該I

2009-11-30 14:33:46 16

16 M31移動/汽車應用MIPI IP – M31 MIPI D-PHY v1.1/v1.2 IP D-PHY是為移動應用開發的一種流行的MIPI物理層,具有靈活、高速、低功耗和低成本的優點

2023-04-03 20:09:44

USB設備接口IP核的設計:討論了用Verilog硬件描述語言來實現USB設備接口IP核的方法,并進行了FPGA的驗證。簡要介紹USB系統的體系結構,重點描述USB設備接口IP核的結構劃分和各模塊的

2010-01-08 18:15:38 22

22 以 FPGA 技術為基礎,以Verilog HDL 為載體,設計了遵守Wishbone 片上總線規范的IP 核接口,實現了片上系統的IP 核互聯。

2010-01-13 15:09:14 13

13 基于Avalon總線的可配置LCD 控制器IP核的設計

本文討論了基于Avalon 總線流傳輸的配置LCD 顯示控制器IP 核的設計,根據自頂向下的設計思想,將IP 核進行層次功能

2010-02-09 09:34:44 27

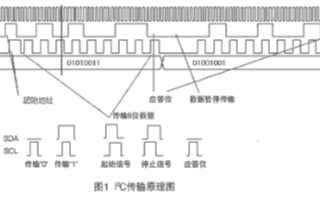

27 I2C器件接口IP核的CPLD設計

根據單片機I2C串行擴展的特點,在EDA軟件MaxplusII的環境下,利用AHDL語言,建立IP核。此設計利用狀態機實現,在給出設計的同時詳細說明IP核的建立

2009-03-28 16:21:35 1351

1351

摘 要: 根據單片機I2C串行擴展的特點,在EDA軟件MaxplusII的環境下,利用AHDL語言,建立IP核。此設計利用狀態機實現,在給出設計的同時詳細說明IP核的建立過程,并下載到

2009-06-20 13:36:12 1065

1065

基于FPGA的8段數碼管動態顯示IP核設計

引言

數碼管可顯示簡單的字符和數字,由于其價格低廉、性能穩定、顯示清晰、亮度高、使用電

2010-02-03 10:03:17 2608

2608

介紹了FreeARM7 IP核的基本概況及其接口特點,以LPC2101為原型對該IP核進行了擴展。結合USB 1.1設備控制器IP核和自定制硬件邏輯,構建了一種微控制器功能驗證回路。

2011-04-06 11:41:13 2369

2369

本文介紹的基于Wishbone總線的UART IP核的設計方法,通過驗證表明了各項功能達到預期要求,為IP核接口的標準化設計提供了依據。此外,該IP核代碼全部采用模塊化的Verilog-HDL語言編寫,

2011-06-10 11:47:37 4199

4199

文章采用TOP-DOWN 的方法設計了 AMBA 總線IP 核!它包括AHB 和APB兩個子IP 核 所有AMBA結構模塊均實現了RTL級建模

2011-07-25 18:10:52 93

93 FPGA中IP核的生成,簡單介紹Quartus II生成IP核的基本操作,簡單實用挺不錯的資料

2015-11-30 17:36:15 12

12 Arasan Chip Systems Inc.(簡稱Arasan)是為移動存儲和連接應用提供Total IP解決方案的領先廠商,擁有15年以上的市場經驗和超過10億片的芯片出貨量。

2016-01-06 17:38:12 2863

2863 領先的韓國半導體公司TLi采用Arasan的通用閃存(UFS)知識產權(IP)產品實現了芯片設計的出貨,該公司之前獲得了Arasan的UFS設備控制器IP及支持高達Gear 3速率的MPHY等產品的授權。TLi是最新一家使用Arasan的UFS Total IP解決方案成功實現芯片設計的公司。

2016-01-06 17:46:12 6084

6084 領先的MIPI攝像頭和顯示知識產權(IP)解決方案提供商Arasan Chip Systems宣布:其支持MIPI DSI-2 v1.0并支持MIPI C-PHY v1.0和MIPI D-PHY v2.0的IP解決方案上市。

2016-02-26 09:34:59 2614

2614 Xilinx FPGA工程例子源碼:PCI Express IP核應用參考設計

2016-06-07 14:13:43 14

14 Xilinx FPGA工程例子源碼:USB IP核

2016-06-07 14:41:57 13

13 Xilinx FPGA工程例子源碼:VGA顯示IP核(包括驅動)

2016-06-07 14:54:57 18

18 “我們利用自己在DPHY領域超過8年的經驗,來為DPHY開發了一種全新的、正在申請專利的架構。它將確保我們的客戶可以得到的是在功耗、面積和可靠性方面處于行業領先水平的DPHY IP 內核。”Arasan模擬IP架構師Sridhar Shashidharan說道。

2016-06-02 14:41:26 1957

1957 Synopsys的IP和原型設計營銷副總裁John Koeter表示:“MIPI接口廣泛應用于移動設備、汽車和物聯網等應用領域,以滿足不斷增加的對高帶寬、低能耗相機和顯示功能的需求

2016-07-21 17:31:55 1594

1594 基于8051內核IP核的應用,感興趣的小伙伴們可以瞧一瞧。

2016-11-11 18:18:32 1

1 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-02-08 13:08:11 3085

3085

電子設計工程 基于FPGA的Flexray IP核通信的研究與實現

2017-08-30 16:08:32 13

13 IP核(IP Core) Vivado中有很多IP核可以直接使用,例如數學運算(乘法器、除法器、浮點運算器等)、信號處理(FFT、DFT、DDS等)。IP核類似編程中的函數庫(例如C語言

2017-11-15 11:19:14 10746

10746 大家好,又到了每日學習的時間了,今天咱們來聊一聊vivado 調用IP核。 首先咱們來了解一下vivado的IP核,IP核(IP Core):Vivado中有很多IP核可以直接使用,例如

2018-05-28 11:42:14 38569

38569 AD的IP核哪里有?

2018-10-06 15:37:29 469

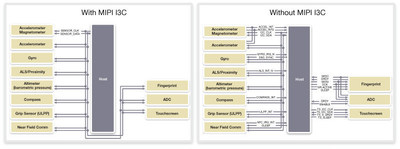

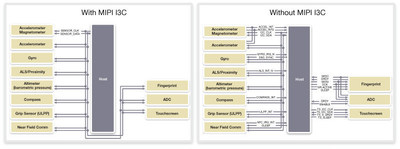

469 )。 SynopsysDesignWare?MIPII3C控制器IP在2線接口內集成了帶內中斷,可實現低引腳數。該IP符合MIPI攝像機控制接口(CCI),I2C和MIPI I3C規范,允許設計人員擴展和面向未來的傳感器接口設計。此外

2019-08-07 10:31:57 5052

5052

由于CPLD數字設計結構化的趨勢,將出現針對CPLD不同層次的IP(Intellectual Property)核。各個IP核可重復利用,可大大提高設計能力和效率。國外各大公司都推出了專門的IP核,我國也迫切需要發展自己的IP核。本文針對I2C的主方式串行擴展通信的特點,詳細給出設計過程和結果。

2020-04-07 09:54:10 4073

4073

? Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM ?IP核

2020-12-29 15:59:39 13270

13270 、DDR5、LPDDR5、MIPI、OTP NVM等 ●新思科技與GF的長期合作,成功實現了DesignWare IP核從180nm到12nm的開發,并可應用于廣泛領域 新思科技(Synopsys)近日宣布

2020-11-03 16:48:08 2984

2984 移動和汽車SoC(片上系統)半導體IP的領先供應商Arasan Chip Systems今天宣布,從即刻起提供第二代MIPI D-PHY v1.1 IP,支持速度高達1.5 Gbp的臺積電(TSMC

2021-01-18 15:00:24 2908

2908 / -- Arasan Chip Systems為臺積公司(TSMC)行業領先的22nm工藝技術擴展其IP產品,用于臺積公司22nm工藝SoC設計的eMMC PHY IP立即可用。臺積公司22nm工藝中

2021-01-21 10:18:23 3344

3344 IP核目前的IP設計已成為目前FPGA設計的主流方法之一,應用專用集成電路(ASIC)或者可編輯邏輯器件(FPGA)的邏輯塊或數據塊。IP核在SoC中的集成方式及應用場景,芯片設計中的IP核具有特定功能的可復用的標準性和可交易性,已經成為集成電路設計技術的核心與精華。

2021-10-01 09:08:00 3100

3100 面向物聯網(IoT)、移動和汽車SoC的領先半導體IP核提供商Arasan Chip Systems宣布立即供應MIPI Soundwire PHY I/O IP核。

2021-10-08 10:05:42 1762

1762 Arasan的MIPI I3C? Total IP?解決方案無縫集成MIPI I3C?控制器、MIPI I3C? PHY I/O和MIPI I3C?軟件棧。

2021-12-02 14:18:40 1825

1825 用于GF 12nm的Arasan MIPI D-PHYSM的速度高達每通道2.5Gbps,符合MIPI D-PHYSM v1.2規范。GF 12nm D-PHYSM是一款通用PHY IP,也可配置為獨立的發射器或接收器。

2021-12-13 11:18:02 1863

1863 電子發燒友網站提供《Gowin MIPI D PHY RX TXAdvance IP用戶指南.pdf》資料免費下載

2022-09-15 15:22:42 6

6 Arasan宣布可立即提供MIPI DSI IP,其支持FPGA設計高達54.72Gbps的C-PHY v2.0速度。? 加利福尼亞州圣何塞2022年11月10日 /美通社/ -- Arasan發布

2022-11-11 12:44:06 2411

2411 Arasan Chip Systems是移動和物聯網SoC半導體IP的領先供應商,今天宣布立即推出用于GF 22nm SoC設計的第二代MIPI D-PHY IP。

2023-05-19 14:51:22 1207

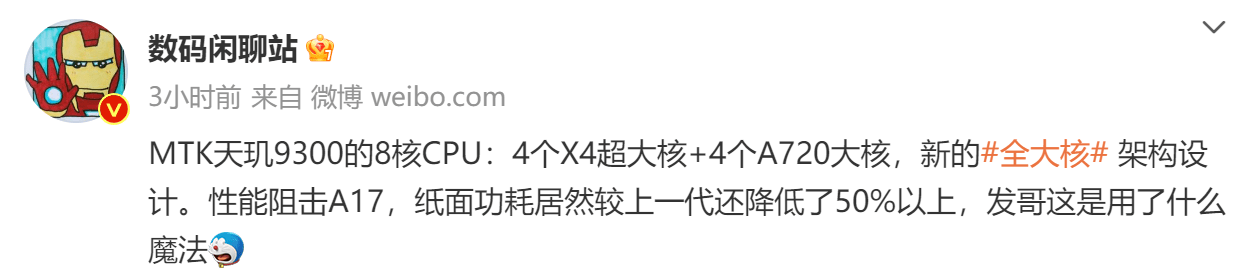

1207 你聽說過“全大核”設計嗎?最近,Arm發布了全新的移動平臺CPU IP,其中Cortex-X4超大核和Cortex-A720大核備受關注。根據知名數碼博主爆料,這次聯發科將推出全大核CPU架構

2023-05-31 13:38:56 1133

1133

在仿真Vivado IP核時分兩種情況,分為未使用SECURE IP核和使用了SECURE IP核。

2023-06-06 14:45:43 2875

2875

MIPI CSI-2 RX Subsystem IP實現MIPI CSI-2 v2.0協議以及底層的MIPI D-PHY v2.0協議

2023-07-07 14:15:02 3958

3958 的CAN IP產品組合,鞏固了我們十年來提供CAN IP核的承諾。 Arasan CAN XL IP符合CiA 613-2規范,并保持與CAN FD、CAN 2.0和TT-CAN的向后兼容性。 集成的CANsec IP增強了安全性并

2023-08-04 11:05:24 1390

1390 Vivado IP核提供了強大的FIFO生成器,可以通過圖形化配置快速生成FIFO IP核。

2023-08-07 15:36:28 7272

7272

Xilinx公司的FPGA中有著很多的有用且對整個工程很有益處的IP核,比如數學類的IP核,數字信號處理使用的IP核,以及存儲類的IP核,本篇文章主要介紹BRAM IP核的使用。 BRAM是FPGA

2023-12-05 15:05:02 3291

3291 MIPi(Mobile Industry Processor Interface)是一種用于移動設備的顯示接口標準,由MIPI聯盟制定。MIPi接口主要用于連接處理器和顯示設備,提供高速數據傳輸

2024-07-16 09:11:09 6503

6503 MIPI和LVDS顯示屏的區別

2024-09-23 10:02:58 5710

5710 在使用FPGA的時候,有些IP核是需要申請后才能使用的,本文介紹如何申請xilinx IP核的license。

2024-10-25 16:48:32 2275

2275

本文介紹了Vidado中FFT IP核的使用,具體內容為:調用IP核>>配置界面介紹>>IP核端口介紹>>MATLAB生成測試數據>>測試verilogHDL>>TestBench仿真>>結果驗證>>FFT運算。

2024-11-06 09:51:43 5641

5641

電子發燒友App

電子發燒友App

評論