鎖相環電路

鎖相環

2009-09-25 14:28:39 7723

7723

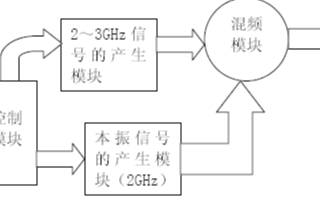

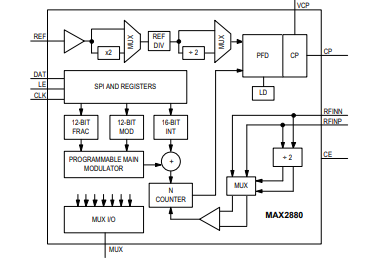

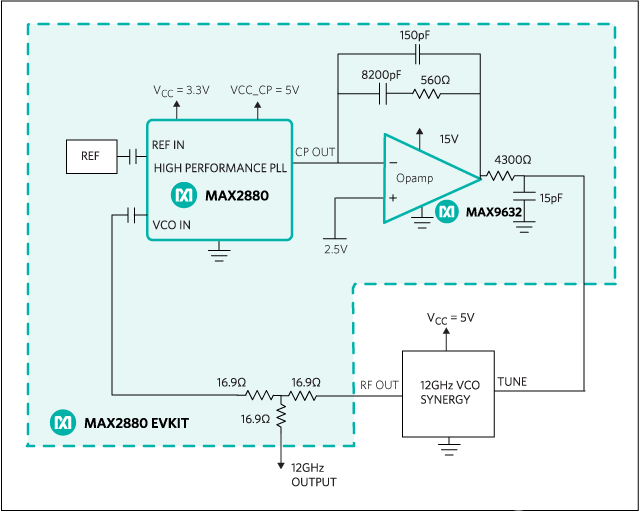

詳細介紹了具有外部VCO的完整12GHz,超低相位噪聲分數N鎖相環(PLL)的設計。它由高性能小數N分頻PLL(MAX2880),基于運算放大器的有源環路濾波器(MAX9632)和12GHz VCO(SYNERGY DXO11751220-5)組成。

2018-12-10 10:02:53 1721

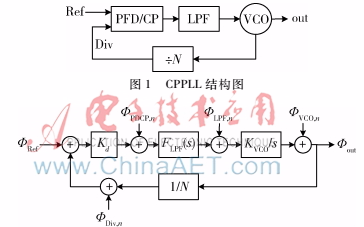

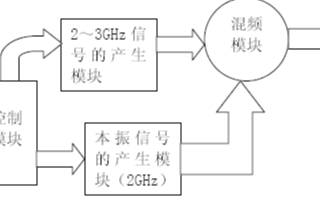

1721 數字鎖相環頻率合成系統的工作原理是:鎖相環對高穩定度的基準頻率(通常由晶體振蕩器直接或經分頻后提供)進行精確鎖定,環內串接可編程的分頻器,通過編程改變分頻器的分頻比,使環路總的分頻比為N(可通過編程改變),從而環路穩定的輸出 N倍的基準頻率,而整個程序和系統的控制是要由CPU來完成的。

2020-07-23 16:47:49 2086

2086

大家都知道鎖相環很重要,它是基石,鎖相環決定了收發系統的基礎指標,那么如此重要的鎖相環選型原則有哪些呢?

2023-08-01 09:37:05 7303

7303

Controlled Oscillator:VCO)。有了這三個模塊的話,最基本的鎖相環就可以運行了。但我們實際使用過程中,鎖相環系統還會加一些分頻器、倍頻器、混頻器等模塊。(這一點可以類比STM32的最小系統和我們實際使用STM32的開發板)

2023-09-03 12:01:12 3021

3021

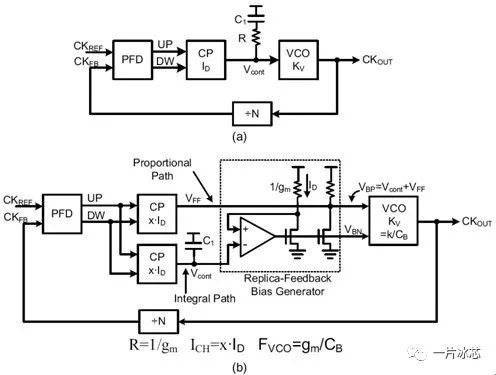

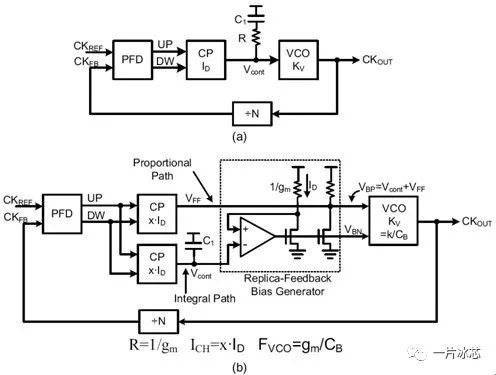

傳統鎖相環,環路帶寬、相位裕度與電荷泵電流、濾波器RC參數、分頻比、參考頻率等參數相關。

2023-10-30 16:47:58 2639

2639

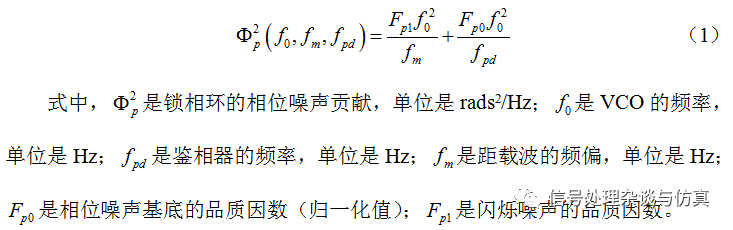

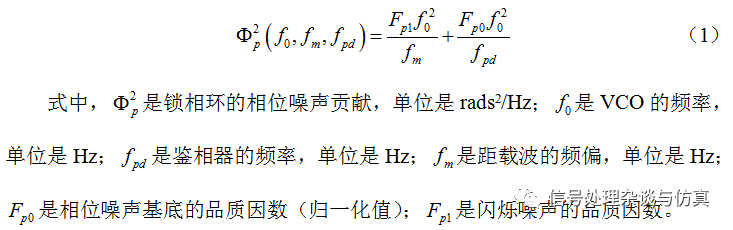

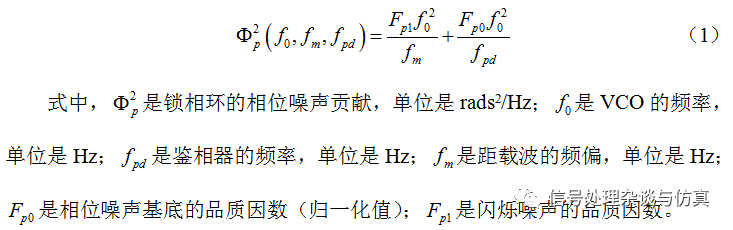

鎖相環性能度量標準包括品質因數、噪聲基底、閃爍噪聲模型。

2023-10-31 10:36:42 2490

2490

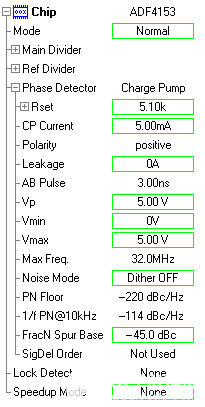

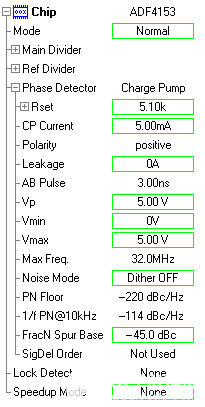

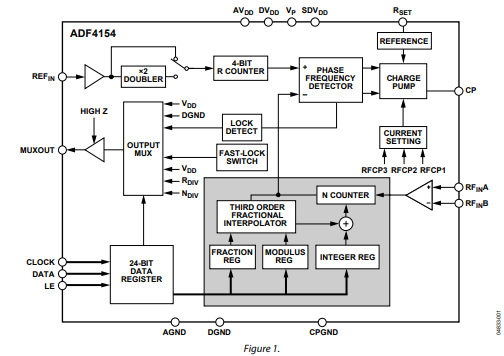

),因為它具有更佳的總帶內相位噪聲。相反,若要求具有較小的頻率步進,則應首選小數N 分頻PLL(如ADF4153),因為它的總噪聲性能優于整數N 分頻PLL。相位噪聲是一個基本的PLL 規格,但數據

2018-10-22 09:45:08

概述:LTC6946是一款全集成型 VCO 的高性能、低噪聲、6.39GHz 鎖相環 (PLL),它包括一個基準分頻器、具鎖相指示器的相位-頻率檢測器 (PFD)、超低噪聲充電泵、整數反饋分頻器和 VCO 輸出...

2021-04-13 06:31:10

不僅包括整數分頻,小數分頻VCO外置產品,還包括集成了VCO的產品,從而大大簡化您的設計,降低系統成本。 整數分頻PLL小數分頻PLL單環PLL雙環PLL集成VCO的PLL快速鎖定PLL高電壓電荷泵PLL附件鎖相環常見問題解答.pdf518.7 KB

2018-10-31 15:08:45

不僅包括整數分頻,小數分頻VCO外置產品,還包括集成了VCO的產品,從而大大簡化您的設計,降低系統成本。附件鎖相環常見問題解答.rar.zip492.4 KB

2018-11-06 09:03:16

電荷泵鎖相環的基本原理是什么?電荷泵鎖相環的噪聲模型與相位噪聲特性是什么?電荷泵鎖相環的相位噪聲與環路帶寬關系是什么?

2021-06-07 06:57:53

本帖最后由 zhihuizhou 于 2011-12-21 17:43 編輯

鎖相環PLL原理與應用 第一部分:鎖相環基本原理 一、鎖相環基本組成 二、鑒相器(PD) 三

2011-12-21 17:35:00

Actel FPGA PLL鎖相環的最大能達到幾倍頻幾分頻?我在網上查了一下有人說是20倍頻,10分頻,但是我沒有在芯片手冊里面找到資料,想要確認一下。

2014-12-04 11:25:15

DC1959B-C,用于LTC6948IUFD-3超低噪聲和雜散小數N分頻合成器的演示板,集成VCO。演示電路采用LTC6948,具有集成VCO的超低噪聲和雜散小數N分頻合成器

2019-07-17 06:34:42

DC1959B-D,用于LTC6948IUFD-1超低噪聲和雜散小數N分頻合成器的演示板,集成VCO。演示電路采用LTC6948,具有集成VCO的超低噪聲和雜散小數N分頻合成器

2019-07-19 08:59:53

`可編程鎖相環(PLL)解決方案有多種尺寸和類型可供選擇。 PLL以整數N或小數N形式提供同時根據帶寬利用無源或有源環路濾波器。 可以通過3線串行接口對其進行快速編程同時提供非常低的雜散抑制和較小

2021-04-03 17:00:58

信號源的任何應用的理想選擇,并且利用微帶或陶瓷諧振器拓撲結構可提供出色的相位噪聲性能。測試儀器雷達系統SFS10500H-LF鎖相環SFS10625H-LF鎖相環SFS10640H-LF鎖相環

2021-04-03 17:05:46

`編輯推薦《鎖相環(PLL)電路設計與應用》內容豐富、實用性強,便于讀者自學與閱讀理解,可供電子、通信等領域技術人員以及大學相關專業的本科生、研究生參考,也可供廣大的電子愛好者學習參考。作者簡介作者

2017-09-18 17:56:02

注意事項以及詳細信息,請參考利用低噪聲 LDO 調節器為小數 N 分頻壓控振蕩器(VCO)供源,以降低相位噪聲 (CN-0147)再則,用于組成環路濾波器的電阻和電容應當放置在盡可能離PLL 芯片近的地方

2019-11-09 08:00:00

,因為fc=IDCLOCK/2N,因此通過改變分頻值N可以得到不同的環路中心頻率fc。 3全數字鎖相環的實現與仿真 本設計在Altera公司的Max+PlusⅡ開發軟件平臺上,利用VHDL語言運用自頂

2010-03-16 10:56:10

。本文基于鎖相環芯片ADF4106設計的頻率器具有低噪聲、低功耗、低成本及電路結構簡單等特點,從而被廣泛應用于無線通信系統領域。

2018-09-06 14:32:13

ADF4351鎖相環介紹及相關硬件設計ADF4351是ADI公司推出的一款集成VCO的鎖相環芯片。其輸出頻率范圍可配置為35MHZ到4400MHZ,這取決于參考頻率和寄存器配置。其內部包括整數N

2022-01-11 07:28:51

該電路是低噪聲微波小數N分頻PLL的完整實現方案,以 ADF4156 作為核心的小數N分頻PLL器件。使用 ADF5001 外部預分頻器將PLL頻率范圍擴展至18 GHz。采用具有適當偏置和濾波

2019-08-20 06:44:35

中提到的濾波。第3步提到R/2計數器而后在第4步用cnt的狀態翻轉lowclk來實現R分頻,是為了強調輸出的lowclk的展空比為50%。數字鎖相環設計總思路:數字鎖相環完成的功能就是利用clock從

2012-01-12 15:29:12

fpga中的用鎖相環產生時鐘信號相比于用計數器進行分頻有哪些優點,看fpga中鎖相環的結構,其前期的輸入信號和后期的輸出信號不也是通過計數器進行分頻實現的嗎

2014-10-06 10:46:05

DC1959B-B,用于LTC6948IUFD-2超低噪聲和雜散小數N分頻合成器的演示板,集成VCO。演示電路采用LTC6948,具有集成VCO的超低噪聲和雜散小數N分頻合成器

2019-02-28 09:49:17

DC1959B-D,用于LTC6948IUFD-4超低噪聲和雜散小數N分頻合成器的演示板,集成VCO。演示電路采用LTC6948,具有集成VCO的超低噪聲和雜散小數N分頻合成器

2019-02-28 09:33:14

詳細介紹了具有外部VCO的完整12GHz,超低相位噪聲分數N鎖相環(PLL)的設計。它由高性能小數N分頻PLL(MAX2880),基于運算放大器的有源環路濾波器(MAX9632)和12GHz VCO

2018-12-10 09:50:52

您好,我們目前在做一個調頻連續波的雷達,DDS輸出50~60MHz,使用ADI的鎖相環ADF4108 96倍頻至4.8GHz~5.8GHz,掃頻周期4ms,點頻測試時鎖相環的相位噪聲還可

2018-08-16 07:18:19

根據虛擬無線電技術的特點和鎖相環的基本原理,提出一種適于計算機軟件化實現的鎖相環數學模型,分析不同參數對鎖相環捕獲和跟蹤性能的影響,得出不同情況下參數設定的基

2008-08-15 12:36:19 101

101 一、實驗目的1、掌握模擬鎖相環的組成及工作原理。2、學習用集成鎖相環構成鎖相解調電路。3、學習用集成鎖相環構成鎖相倍頻電路。

二、鎖相環路的基本原理

2009-03-22 11:44:37 127

127 鎖相環電路的設計:

2009-07-25 17:05:36 0

0 鎖相環設計舉例:鎖相環設計主要包括:確定所需環的類型,選擇適當的帶寬,指出希望的穩定度。下面將舉例說明要滿足這些設計要求而常用的基本方法。

2009-09-05 08:51:42 105

105 議程PLL介紹及小數分頻鎖相環的優點小數分頻鎖相環的錯誤使用小數分頻鎖相環詳解參考雜散及如何減少雜散總結

2010-05-28 14:58:36 0

0

利用鎖相環進行載波跟蹤是獲取本地載波的一種重要方法,針對鎖相環的噪聲性能和跟蹤速度不能同時達到最優的限制,在鎖相環PLL中引入自適應模塊,根據環路所處

2010-11-25 17:19:33 29

29 鎖相環原理

鎖相環路是一種反饋電路,鎖相環的英文全稱是Phase-Locked Loop,簡稱PLL。其作用是使得電路上的時鐘和某一外部時鐘的相位同步。因鎖相環可以

2007-08-21 14:46:04 5484

5484 鎖相環(PLL),鎖相環(PLL)是什么意思

PLL的概念

我們所說的PLL。其

2010-03-23 10:47:48 6368

6368 數字鎖相環(DPLL),數字鎖相環(DPLL)是什么?

背景知識:

隨著數字電路技術的發展,數字鎖相環在調制解調、頻率合成、FM 立體聲解碼、彩色副

2010-03-23 15:06:21 6110

6110 模擬鎖相環,模擬鎖相環原理解析

背景知識:

鎖相技術是一種相位負反饋控制技術,它利用環路的反饋原理來產生新的頻率點。它的主要

2010-03-23 15:08:20 6264

6264 頻率跟蹤的 鎖相環電路 由專用鎖相芯片CD4046和分頻芯片CD4040組成,以實現工頻信號的鎖相倍頻,分頻比為1/64。在工頻信號恰好為50 Hz的情況下,該電路的鎖相倍頻頻率為5064=3 200 Hz,相

2011-10-26 11:17:47 9369

9369

鎖相環英文為PLL,即PLL鎖相環。可以分為模擬鎖相環和數字鎖相環。兩種分類的鎖相環原理有較大區別,通過不同的鎖相環電路實現不同的功能。

2011-10-26 12:40:28

該電路是低噪聲微波小數N分頻PLL的完整實現方案,以 ADF4156 作為核心的小數N分頻PLL器件。使用 ADF5001 外部預分頻器將PLL頻率范圍擴展至18 GHz。

2011-10-26 15:02:22 1852

1852

小數N分頻PLL從上世紀七十年代開始就已投入使用。小數N分頻使PLL輸出的分辨率可以降至PFD頻率的一小部分

2012-06-08 16:07:17 11610

11610

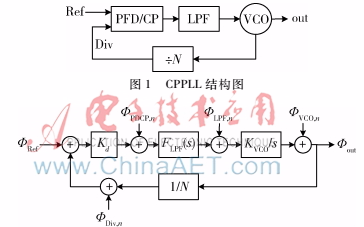

利用鎖相環的等效噪聲模型,重點分析電荷泵鎖相環系統的相位噪聲特性,得出系統噪聲特性的分布特點以及與環路帶寬的關系。

2012-11-22 10:44:47 23978

23978 本材料是基于單片機分頻的鎖相環測試系統電路圖。

2015-10-28 13:47:49 9

9 有關鎖相環的部分資料,對制作鎖相環有一定的幫助。

2015-10-29 14:16:55 70

70 雙向遙控鑰匙(RKE)系統為用戶提供安全和便利。對于設計師,一個復雜的IC陣列提供完整的收發器功能,利用未經授權的ISM頻段。其中,sub-GHz收發器集成電路從模擬設備,飛思卡爾半導體和集成功能的小數N分頻鎖相環在先進的雙向RKE系統設計更大的靈活性。

2017-07-11 09:32:07 0

0 的估計。 通過USB接口與電腦實現通信來交換有關鎖相環的參數。電腦傳遞鎖相環所需的參數(如等效噪聲帶寬等),FPGA將鎖相環的結果傳遞給電腦(如鎖定時間,多普勒頻率等)。 二、設計任務 鎖相環的輸入具有自動增益控制AGC模塊,這樣可以允許

2017-10-16 11:36:45 19

19 介紹一種2.4 GHz的低噪聲亞采樣鎖相環。環路鎖定是利用亞采樣鑒相器對壓控振蕩器的輸出進行采樣。不同于傳統電荷泵鎖相環,由于在鎖定狀態下沒有分頻器的作用,由鑒相器和電荷泵所產生的帶內噪聲不會被放大

2018-06-07 15:58:00 11427

11427

ADI第一款微波頻段整數N分頻鎖相環頻率綜合器產。

2018-06-04 13:47:00 4554

4554 本文將從小數鎖相環的需求,Delta-Sigma 小數鎖相環的邏輯以及Delta-Sigma的特性三方面展開。

2019-01-01 08:45:00 9244

9244

設計概述

鎖相式頻率源具有輸出頻率高,頻率穩定度高、頻譜純、寄生雜波小及相位噪聲低等優點。本方案就是利用小數分頻的鎖相環,來實現一個寬頻帶低噪聲的頻率合成器,實現0~1GHz的低噪聲正弦波信號。

2021-03-22 16:06:38 4033

4033

LTC6950:1.4 GHz低相位噪聲、低抖動鎖相環,帶時鐘分布數據表

2021-04-19 12:13:04 3

3 微波無線電用低相位噪聲GaAs壓控振蕩器高性能SiGe鎖相環對

2021-04-22 19:06:02 11

11 UG-873:評估ADF4355-3小數/整數N鎖相環頻率合成器

2021-04-28 14:35:35 5

5 UG-1404:評估集成小數N鎖相環和壓控振蕩器的ADMV4420,K波段下變頻器

2021-04-29 15:58:03 5

5 一種新型的采用電流轉向電荷泵的快速鎖定小數分頻鎖相環介紹。

2021-05-08 10:55:08 5

5 UG-804:評估ADF4355-2小數/整數N鎖相環頻率合成器

2021-05-10 08:26:33 9

9 LTC6947:超低噪聲0.35 GHz至6 GHz小數N合成器數據表

2021-05-10 08:35:41 0

0 射頻/微波鎖相環集成低噪聲壓控振蕩器

2021-05-16 09:01:47 8

8 UG-1025:評估ADRF6821 450 MHz至2800 MHz,集成小數N鎖相環和壓控振蕩器的DPD RFIC

2021-05-16 13:15:14 1

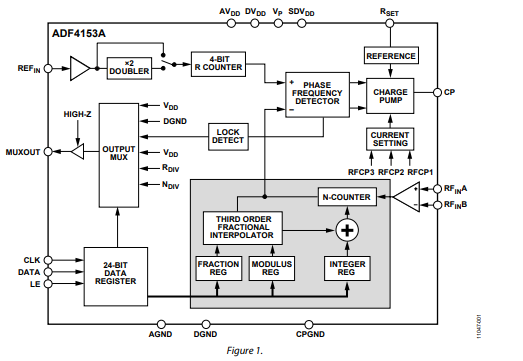

1 UG-485:ADF4153A小數N鎖相環頻率合成器評估板

2021-05-16 13:22:43 9

9 UG-742:評估集成小數N鎖相環和壓控振蕩器的ADRF6720-27寬帶正交調制器

2021-05-16 14:59:18 11

11 UG-652:評估集成小數N鎖相環和壓控振蕩器的ADRF6820-a 695 MHz至2700 MHz正交解調器

2021-05-17 12:50:56 3

3 ADRF6720-27:集成小數N鎖相環和壓控振蕩器的寬帶正交調制器

2021-05-18 20:43:41 10

10 ADRF6655:集成小數N鎖相環和壓控振蕩器的寬帶上/下變頻混頻器

2021-05-24 12:59:25 2

2 該電路是低噪聲微波小數N分頻PLL的完整實現方案,以 adf4156 作為核心的小數N分頻PLL器件。使用adf5001 外部預分頻器將PLL頻率范圍擴展至18 GHz。采用具有適當偏置和濾波的超低噪聲

2021-06-03 19:01:14 3

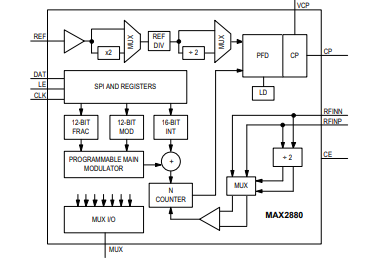

3 本應用筆記詳細介紹了集成外部VCO的完整12GHz、超低相位噪聲小數N分頻鎖相環(PLL)的設計。它由高性能小數N分頻PLL(MAX2880)、基于運算放大器的有源環路濾波器(MAX9632)和12GHz VCO(SYNERGY DXO11751220-5)組成。

2023-01-16 11:27:08 2339

2339

PLL,輸出頻率階躍等于PFD輸入頻率除以MOD值,因此您可以使用較高的參考頻率來獲得較小的頻率步進。在決定是使用整數N還是小數N分頻時,頻率階躍可以用相位噪聲換取,PFD頻率越低,輸出頻率分辨率越好,但相位噪聲越差。

2023-01-30 15:25:32 3731

3731

模擬鎖相環和數字鎖相環的主要區別在于它們的控制方式不同。模擬鎖相環是通過模擬電路來控制頻率和相位,而數字鎖相環是通過數字信號處理技術來控制頻率和相位。此外,模擬鎖相環的精度較低,而數字鎖相環的精度較高。

2023-02-15 13:47:53 6625

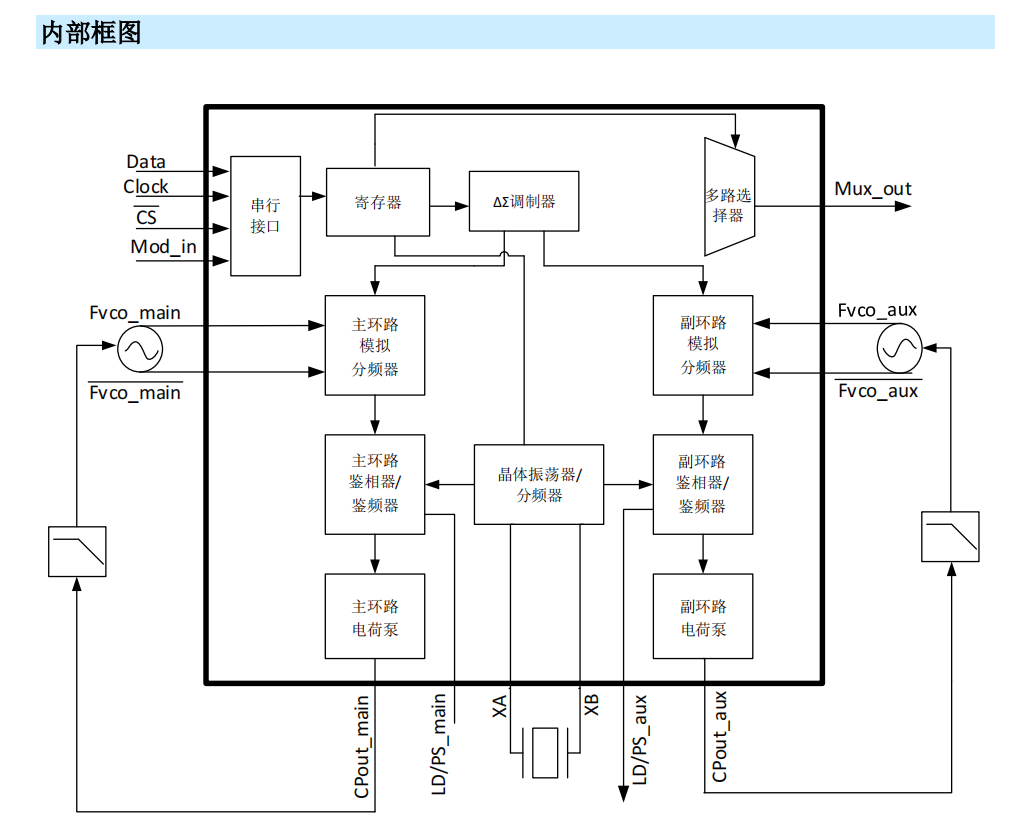

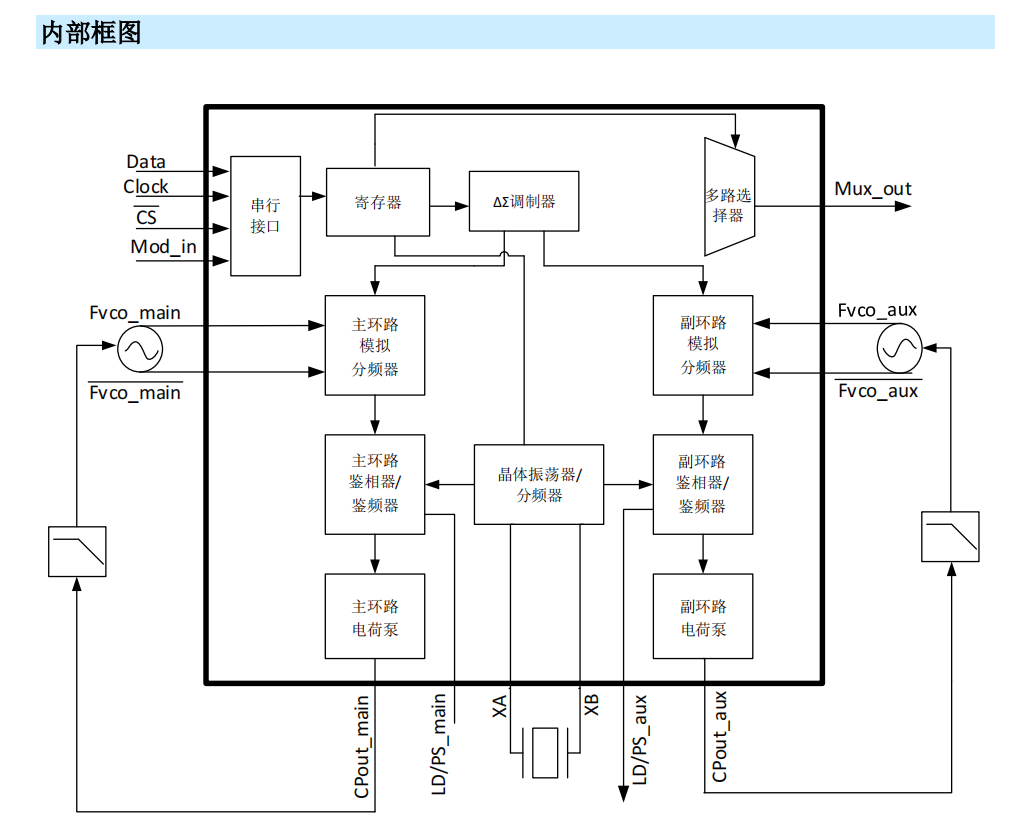

6625 MS72300 是一款雙環路、小數 N 分頻頻率綜合器。包含主環路和副環路鎖相環。它提供了極高的頻率分辨率、快的輸出頻率切換速度和低相位噪聲性能。芯片須使用外部壓控振蕩器,主環路最大工作頻率 2.1GHz,適合應用于無線通信系統中。

2023-07-01 16:36:19 2111

2111

核芯互聯發布射頻鎖相環CLF4371,CLF4371是一款低噪聲寬頻段的鎖相環,支持整數模式和小數模式,可以工作在-40~85℃全溫度范圍。芯片采用3x3mm 超小型BGA封裝,可以為用戶節省面積

2023-08-29 21:53:50 2321

2321

鎖相環是如何實現倍頻的?? 鎖相環(Phase Locked Loop, PLL)是一種電路,用于穩定和恢復輸入信號的相位和頻率。它可以廣泛應用于通信、計算機、音頻等領域中。其中一個重要的應用就是

2023-09-02 14:59:37 5119

5119 基本PLL鎖相環、整數型頻率合成器和分數型頻率合成器。下面將詳細介紹這三種模式的作用和特點。 第一種:基本PLL鎖相環 基本PLL鎖相環是PLLf工作的最基本形式,它主要由比較器、低通濾波器、VCO和分頻器組成。其基本工作原理是將輸入信號和VCO輸出的信號進行

2023-10-13 17:39:48 5285

5285 是將某一參考信號的頻率和相位鎖定到一個輸出信號的頻率和相位。 然而,在一些情況下,鎖相環無法鎖定輸入信號。特別是在輸入信號頻率發生了劇烈變化時,鎖相環的反應速度跟不上變化,導致無法鎖定。此外,輸入信號中存在噪聲干擾,也會

2023-10-13 17:39:58 3086

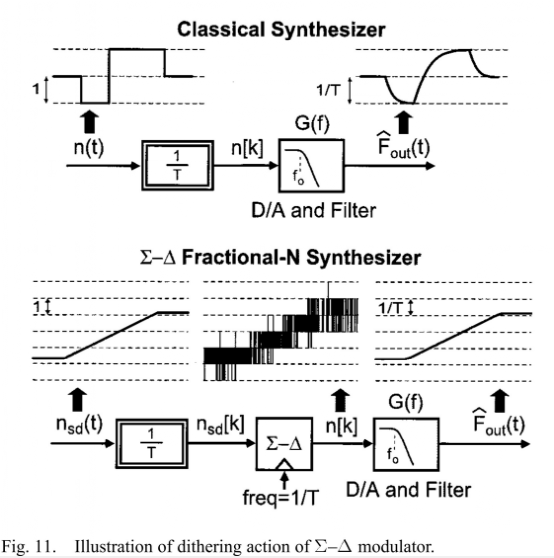

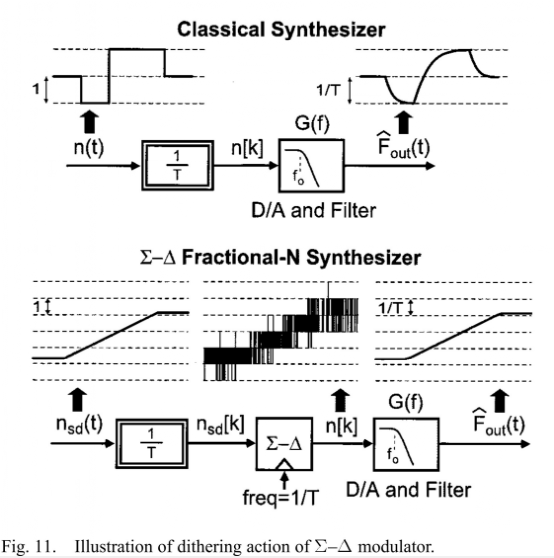

3086 為了理解Σ-Δ調制器在頻率綜合器中究竟引起了啥影響,圖11可以比較好的說明。需要指出的是,圖11中把分頻比的變化看作一個連續信號

2023-10-25 14:36:37 2118

2118

本應用筆記詳細介紹了具有外部VCO的完整12GHz、超低相位噪聲小數N分頻鎖相環(PLL)的設計。它由高性能小數N分頻PLL (MAX2880)、基于運算放大器的有源環路濾波器(MAX9632

2023-10-28 14:45:41 9534

9534 和調試,以確定并解決問題。 一、鎖相環無法鎖定的原因 1.輸入信號不穩定 當鎖相環輸入的信號不穩定時,即可能無法正確鎖定。如果輸入信號有幅度變化、頻率漂移、相位噪聲等問題,這些都會導致鎖相環的不穩定。因此,需要確保輸

2023-10-30 10:16:33 3646

3646 鎖相環性能度量標準包括品質因數、噪聲基底、閃爍噪聲模型。

2023-10-30 17:19:51 1513

1513

鎖相環整數分頻和小數分頻的區別是什么? 鎖相環(PLL)是一種常用的電子電路,用于將輸入的時鐘信號與參考信號進行同步,并生成輸出信號的一種技術。在PLL中,分頻器模塊起到關鍵作用,可以實現整數分頻

2024-01-31 15:24:48 5373

5373 2024年07月09日,一站式定制芯片及IP供應商——燦芯半導體(上海)股份有限公司(燦芯股份,688691)宣布成功研發出一款通用高性能小數分頻鎖相環(fractional-N PLL)IP,支持

2024-07-09 14:13:58 62633

62633 鎖相環(Phase Locked Loop, PLL)相位噪聲是評估鎖相環性能的重要指標之一,它描述了輸出信號相位的不穩定性。相位噪聲的存在會直接影響系統的性能,如降低信號的信噪比、增加誤碼率、影響雷達系統的目標分辨能力等。以下將詳細分析鎖相環相位噪聲的影響因素,并從多個方面進行歸納和總結。

2024-07-30 15:31:57 4497

4497 MS72300 是一款雙環路、小數 N 分頻頻率綜合器,包含主環路和副環路鎖相環。它具有頻率分辨率高、輸出頻率切換快、相位噪聲低的特點。歡迎咨詢了解

2024-12-11 16:30:14 906

906

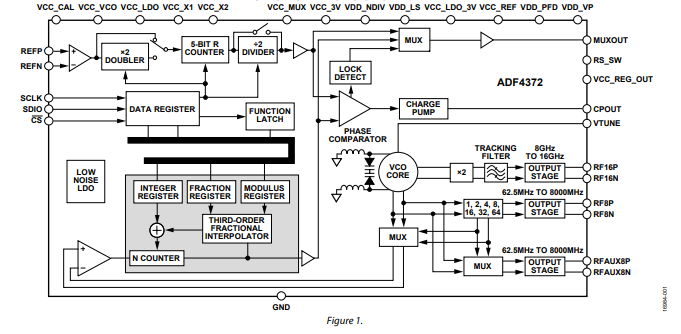

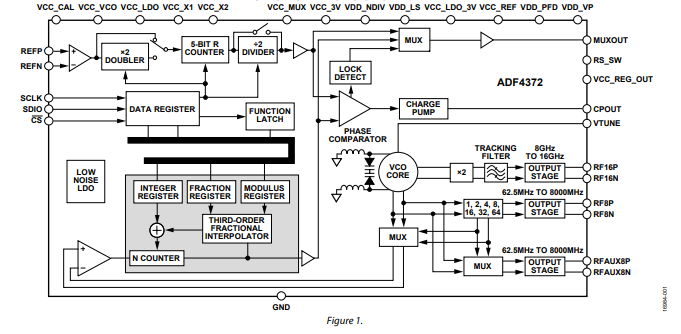

ADF4372 結合外部環路濾波器和外部基準頻率使用時,可實現小數 N 分頻或整數 N 分頻鎖相環 (PLL) 頻率合成器。寬帶微波壓控振蕩器 (VCO) 設計允許產生 62.5 MHz 至 16 GHz 的頻率。

2025-04-25 09:57:01 1059

1059

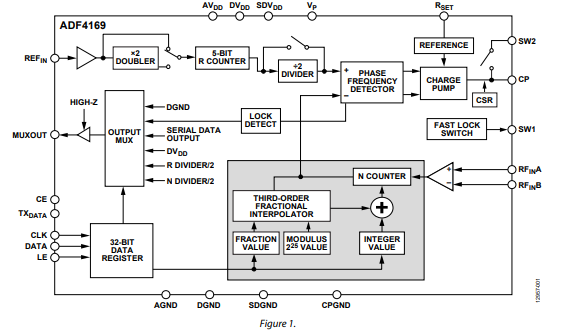

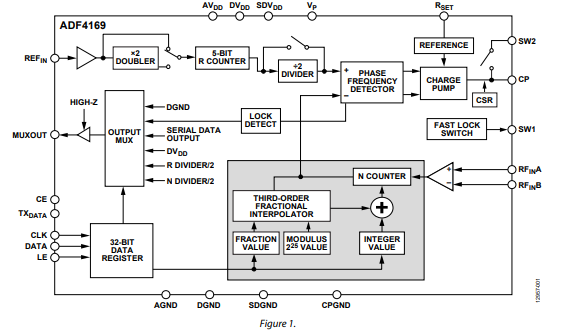

ADF4169是一款具有調制、以及快速和慢速波形產生能力的13.5 GHz小數N分頻頻率合成器, 該器件使用25位固定模數,提供次赫茲頻率分辨率。

ADF4169由低噪聲數字鑒頻鑒相器(PFD

2025-04-25 11:18:48 840

840

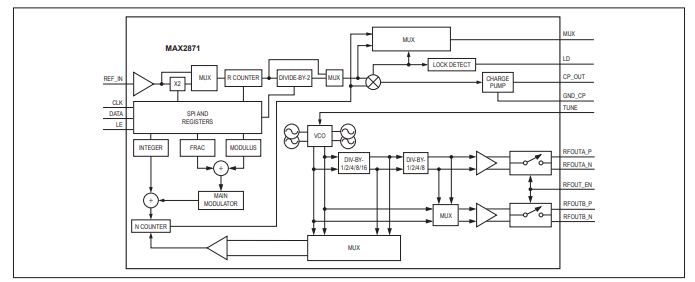

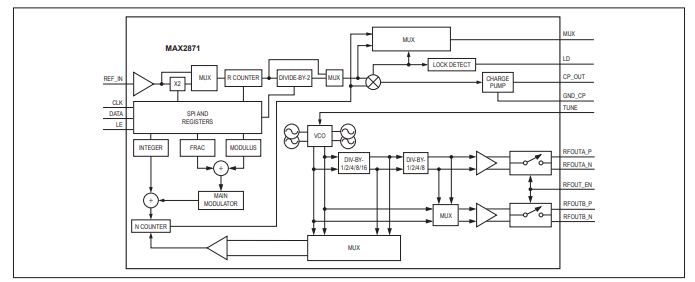

MAX2871是一款超寬帶鎖相環(PLL),集成壓控振蕩器(VCO),可在整數N分頻和小數N分頻模式下工作。與外部基準振蕩器和環路濾波器結合使用時,MAX2871是一款高性能頻率合成器,能夠合成23.5MHz至6.0GHz的頻率,同時保持出色的相位噪聲和雜散性能。

2025-04-25 13:55:10 936

936

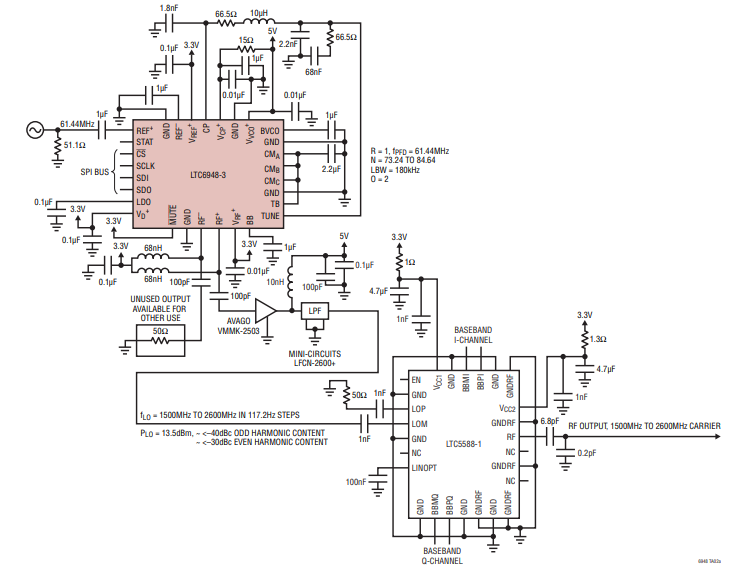

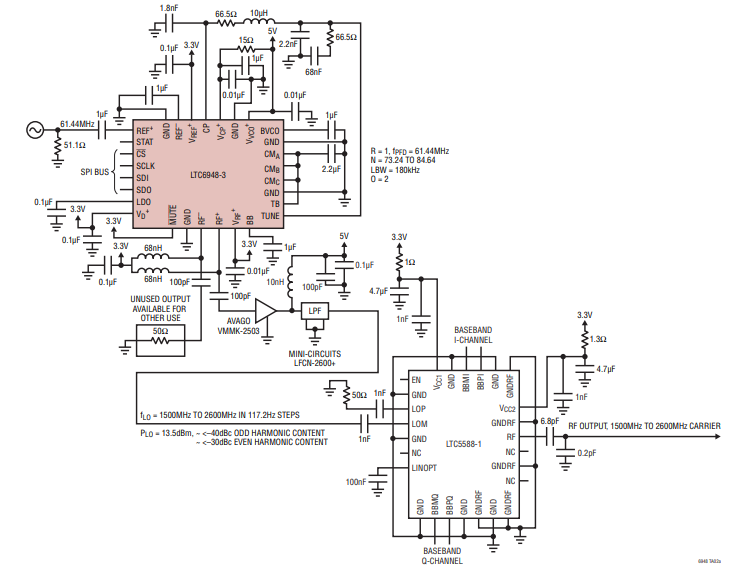

LTC6948 是一款具全集成型 VCO 的高性能、低噪聲、6.39GHz 鎖相環 (PLL),其包括一個基準分頻器、相位-頻率檢測器 (PFD)、超低噪聲充電泵、分數反饋分頻器和 VCO 輸出分頻器。

2025-04-25 14:08:33 724

724

ADF4155結合外部環路濾波器、外部壓控振蕩器(VCO)和外部基準頻率使用時,可實現小數N分頻或整數N分頻鎖相環(PLL)頻率合成器。

ADF4155能夠與外部VCO器件配合使用,工作頻率高達8 GHz。 高分辨率可編程模塊允許精確頻率合成,誤差為0 Hz。

2025-04-25 14:15:12 860

860

MAX2880為高性能鎖相環(PLL),提供整數或分數N分頻工作模式。器件配合外部參考時鐘振蕩器、環路濾波器和VCO,可以構成超低噪聲、低雜散頻率合成器,可接受高達12.4GHz的RF輸入。

2025-04-25 14:21:08 783

783

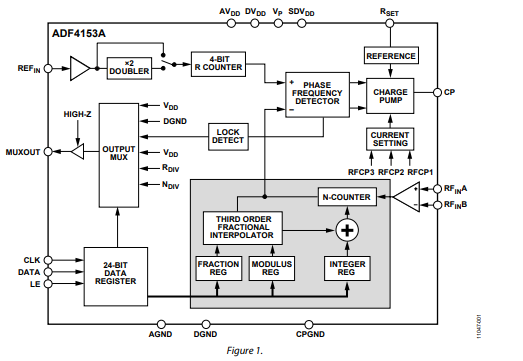

ADF4153A是一款小數N分頻頻率合成器,用來在無線接收機和發射機的上變頻和下變頻部分實現本振。它由低噪聲數字鑒頻鑒相器(PFD)、精密電荷泵和可編程參考分頻器組成。該器件內置一個Σ-Δ型小數插值

2025-04-25 14:58:27 853

853

ADF4151結合外部電壓控制振蕩器(VCO)、環路濾波器和外部基準頻率使用時,可實現小數N分頻或整數N分頻鎖相環(PLL)頻率合成器。

它能夠與外部VCO器件配合使用,且與ADF4350尺寸

2025-04-25 15:15:29 933

933

ADF4158是一款具有調制和波形產生能力的6.1 GHz小數N分頻頻率合成器,包含25位固定模數,可在6.1 GHz下提供次赫茲頻率分辨率。它由低噪聲數字鑒頻鑒相器(PFD)、精密電荷泵和可編程

2025-04-25 15:52:01 959

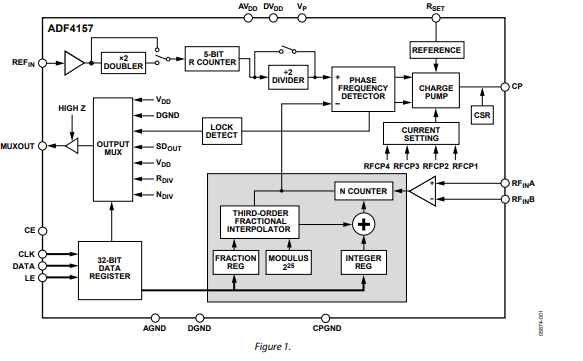

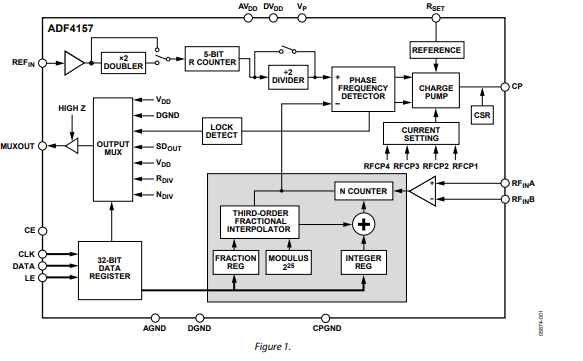

959 ADF4157是一款6 GHz、小數N分頻合成器,具有25 bit固定模數,在6 GHz實現亞赫茲頻率分辨率。ADF4157包括低噪聲數字鑒相器、精密電荷泵、可編程參考除法器。其基于∑-Δ的分數內插

2025-04-25 17:47:47 865

865

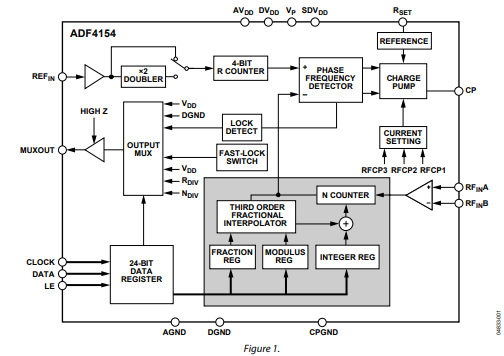

,能夠實現可編程小數N分頻。INT、FRAC和MOD寄存器可構成一個總N分頻器(N = (INT + (FRAC/MOD)))。此外,4位參考分頻器(R分頻器)允許PFD輸入端的REFIN頻率為可選值。如果頻率合成器與外部環路濾波器和電壓控制振蕩器(VCO)一起使用,則可以實現完整的鎖相環(PLL)。

2025-04-27 09:36:56 878

878

Analog Devices ADF4382x小數N分頻鎖相環 (PLL) 是一款高性能、超低抖動、小數N分頻鎖相環 (PLL)。它集成了壓控振蕩器 (VCO),是5G或數據轉換器時鐘應用生成

2025-06-04 11:15:21 862

862

電子發燒友App

電子發燒友App

評論