完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > vivado

Vivado設(shè)計(jì)套件,是FPGA廠商賽靈思公司2012年發(fā)布的集成設(shè)計(jì)環(huán)境。包括高度集成的設(shè)計(jì)環(huán)境和新一代從系統(tǒng)到IC級(jí)的工具,這些均建立在共享的可擴(kuò)展數(shù)據(jù)模型和通用調(diào)試環(huán)境基礎(chǔ)上。

文章:641個(gè) 瀏覽:71122次 帖子:973個(gè)

基于Digilent basys 3開(kāi)發(fā)板的FPGA示波器設(shè)計(jì)

首先,AD模塊對(duì)模擬信號(hào)進(jìn)行采樣,觸發(fā)電路根據(jù)采樣信號(hào)判斷觸發(fā)條件(例如:上升沿觸發(fā))。滿足觸發(fā)條件后,連續(xù)采樣一定數(shù)量的點(diǎn)(本系統(tǒng)中為640個(gè)點(diǎn)),存...

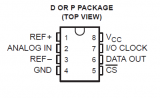

Vivado系列之TCL549驅(qū)動(dòng)設(shè)計(jì)

? 系統(tǒng)性的掌握技術(shù)開(kāi)發(fā)以及相關(guān)要求,對(duì)個(gè)人就業(yè)以及職業(yè)發(fā)展都有著潛在的幫助,希望對(duì)大家有所幫助。本次帶來(lái)Vivado系列,TLC549驅(qū)動(dòng)設(shè)計(jì)。話不多...

2023-07-27 標(biāo)簽:數(shù)模轉(zhuǎn)換驅(qū)動(dòng)設(shè)計(jì)Vivado 2.9k 0

AXI VIP當(dāng)作master時(shí)如何使用?

?AXI接口雖然經(jīng)常使用,很多同學(xué)可能并不清楚Vivado里面也集成了AXI的Verification IP,可以當(dāng)做AXI的master、pass t...

基于fpga的信號(hào)發(fā)生器設(shè)計(jì)方案

信號(hào)發(fā)生器能夠產(chǎn)生頻率波形可調(diào)的信號(hào)輸出,目前僅限于1Hz~4999Hz頻率范圍,波形可選擇三角波,方波,鋸齒波,以及正弦波。本系統(tǒng)在Basys3上構(gòu)建...

2023-07-26 標(biāo)簽:fpgaHDL信號(hào)發(fā)生器 3.8k 0

Modelsim是十分常用的外部仿真工具,在Vivado中也可以調(diào)用Modelsim進(jìn)行仿真,下面將介紹如何對(duì)vivado進(jìn)行配置并調(diào)用Modelsim...

在Vivado中利用Report QoR Suggestions提升QoR

Report QoR Suggestions (RQS) 可識(shí)別設(shè)計(jì)問(wèn)題,并提供工具開(kāi)關(guān)和可影響工具行為的設(shè)計(jì)單元屬性的解決方案,即便在無(wú)法自動(dòng)執(zhí)行解決...

2023-07-19 標(biāo)簽:fpgaFPGA設(shè)計(jì)REPORT 2.4k 0

vivado開(kāi)發(fā)軟件自帶了仿真工具,下面將介紹vivado的仿真流程,方便初學(xué)者進(jìn)行仿真實(shí)驗(yàn)。

2023-07-18 標(biāo)簽:仿真文件開(kāi)發(fā)軟件 6.9k 0

FPGA設(shè)計(jì)中動(dòng)態(tài)時(shí)鐘的使用方法

時(shí)鐘是每個(gè) FPGA 設(shè)計(jì)的核心。如果我們正確地設(shè)計(jì)時(shí)鐘架構(gòu)、沒(méi)有 CDC 問(wèn)題并正確進(jìn)行約束設(shè)計(jì),就可以減少與工具斗爭(zhēng)的時(shí)間。

2023-07-12 標(biāo)簽:FPGA設(shè)計(jì)寄存器CDC 1.9k 0

vivado的工程創(chuàng)建流程對(duì)于大部分初學(xué)者而言比較復(fù)雜,下面將通過(guò)這篇博客來(lái)講解詳細(xì)的vivado工程創(chuàng)建流程。幫助自己進(jìn)行學(xué)習(xí)回顧,同時(shí)希望可以對(duì)有需...

Vivado設(shè)計(jì)套件助力快速編譯設(shè)計(jì)并達(dá)到性能目標(biāo)

Suhel?Dhanani AMD 自適應(yīng) SoC 與 FPGA 事業(yè)部軟件營(yíng)銷總監(jiān) 在設(shè)計(jì)規(guī)模和復(fù)雜性不斷增長(zhǎng)的世界里,SoC 和 FPGA 設(shè)計(jì)需要...

系統(tǒng)性的掌握技術(shù)開(kāi)發(fā)以及相關(guān)要求,對(duì)個(gè)人就業(yè)以及職業(yè)發(fā)展都有著潛在的幫助,希望對(duì)大家有所幫助。后續(xù)會(huì)陸續(xù)更新 Xilinx 的 Vivado、ISE 及...

Versal? 是由多個(gè)高度耦合的可配置塊組成的自適應(yīng)計(jì)算加速平臺(tái)?(ACAP)

2023-07-07 標(biāo)簽:NoCVivado啟動(dòng)文件 2.1k 0

Versal ACAP XPE設(shè)計(jì)咨詢-電源排序更改

在某些情況下,部分 VCCO 能與該序列中的其它電源軌共享

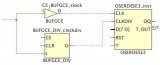

如何減少OSERDES的CLK-CLKDIV與IDDR的CLK及CLK-CLK_B之間的歪斜

本文就幫助解決歪斜違規(guī)問(wèn)題提供幾個(gè)解決方案

2023-07-07 標(biāo)簽:緩沖器計(jì)數(shù)器時(shí)鐘 1.4k 0

Vivado 202x-Versal時(shí)鐘校準(zhǔn)去歪斜的時(shí)序問(wèn)題

使用“時(shí)鐘校準(zhǔn)去歪斜”時(shí),在 Vivado 中會(huì)顯示下列消息以指明是否啟用該功能特性

Vivado統(tǒng)一Web安裝程序:下載和安裝過(guò)程中無(wú)法繞過(guò)用戶帳戶身份驗(yàn)證階段

當(dāng)我嘗試在機(jī)器上安裝 Vivado 時(shí),無(wú)法通過(guò)帳戶身份驗(yàn)證檢查。為什么會(huì)出現(xiàn)此問(wèn)題?

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |