完善資料讓更多小伙伴認(rèn)識(shí)你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > pcie

PCI-Express(peripheral component interconnect express)是一種高速串行計(jì)算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),它原來(lái)的名稱(chēng)為“3GIO”,是由英特爾在2001年提出的,旨在替代舊的PCI,PCI-X和AGP總線標(biāo)準(zhǔn)。

文章:1249個(gè) 瀏覽:88473次 帖子:361個(gè)

前面的文章中介紹過(guò),PCIe收發(fā)的都是差分信號(hào),有的時(shí)候Link兩端的設(shè)備的對(duì)應(yīng)信號(hào)的極性可能是相反的。因此,PCIe Spec允許在鏈路訓(xùn)練與初始化的...

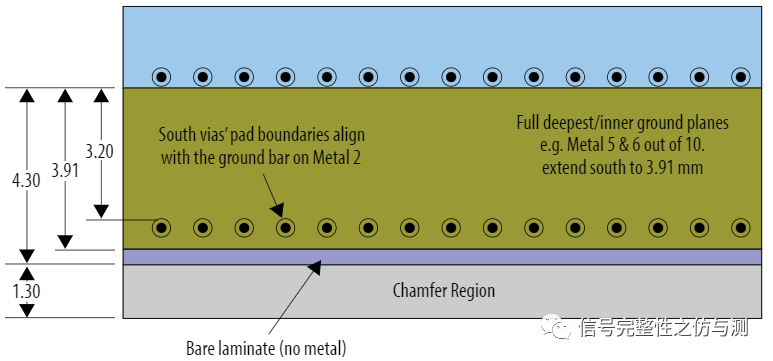

PCIe Gen5 Card金手指仿真與設(shè)計(jì)(上)

金手指是沿著印刷電路板 (PCB) 的連接邊緣看到的鍍金柱。金手指的目的是將輔助PCB連接到計(jì)算機(jī)的主板上。PCB金手指還用于通過(guò)數(shù)字信號(hào)進(jìn)行通信的各種...

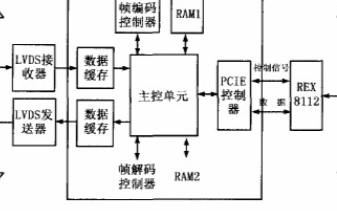

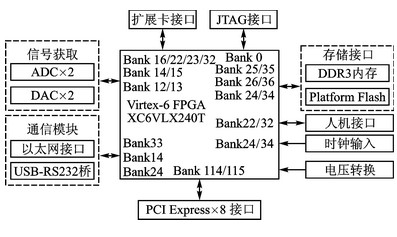

基于FPGA技術(shù)的LVDS傳輸模式如何實(shí)現(xiàn)PCIE接口卡設(shè)計(jì)

隨著電子技術(shù)的飛速發(fā)展,微處理器、存儲(chǔ)器技術(shù)的不斷革新,傳統(tǒng)的并行總線PCI逐漸成為系統(tǒng)整體性能的瓶頸。新一代的PCIE總線是最新的總線接口標(biāo)準(zhǔn),它變革...

PCIE 加速卡熱設(shè)計(jì)的難點(diǎn)和前期需要注意的事項(xiàng)

1, 在前期的布局時(shí),請(qǐng)邀上你的熱專(zhuān)家,即使你有“全能型”稱(chēng)號(hào)的榮譽(yù),也不防聽(tīng)聽(tīng)專(zhuān)家的建議,前期布局很重要,可少走彎路,不要老把改版當(dāng)習(xí)慣,費(fèi)了時(shí)間又燒...

需要注意的是,PCIe物理層處理可以轉(zhuǎn)發(fā)LTP和DLLP之外,還可以直接發(fā)送命令集(Ordered Sets)。之所以稱(chēng)其為命令集,是因?yàn)樗⒉皇钦嬲?..

采用CXL計(jì)劃應(yīng)對(duì)異構(gòu)計(jì)算中的內(nèi)存解決方案

在計(jì)算世界中,不可思議的事情之一是在數(shù)據(jù)中心中迅速采用人工智能(AI)和云計(jì)算。這些和其他因素正在推動(dòng)異構(gòu)計(jì)算-使用CPU,GPU,F(xiàn)PGA,ASIC加...

2021-03-19 標(biāo)簽:控制器PCIe異構(gòu)計(jì)算 1.1萬(wàn) 0

PCIe總線實(shí)現(xiàn)了一種叫做Quality of Service(QoS)的機(jī)制

PCIe驅(qū)動(dòng)程序(配置軟件)通過(guò)修改VC資源控制寄存器(VC Resource Control Register)中的TC/VC Map位來(lái)實(shí)現(xiàn)TC/V...

手機(jī)主流存儲(chǔ)器件UFS與NVMe詳細(xì)對(duì)比分析

NVMe是專(zhuān)門(mén)為高速閃存芯片設(shè)計(jì)的協(xié)議,主要是為企業(yè)級(jí)和數(shù)據(jù)中心的PCIe SSD設(shè)計(jì)的接口標(biāo)準(zhǔn),來(lái)充分發(fā)揮閃存的性能。NVMe通訊協(xié)議+PCIe總線協(xié)...

前面的關(guān)于PCI總線的文章介紹過(guò)PCI總線的配置空間,PCIe總線為了兼容這些PCI設(shè)備,幾乎完整的保留了PCI總線的配置空間。并將配置空間擴(kuò)展到4KB...

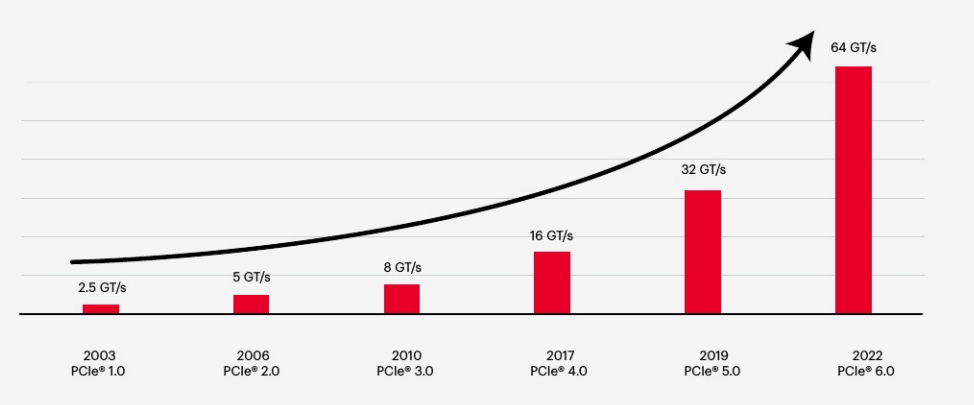

PCIe標(biāo)準(zhǔn)的演進(jìn)歷史 各代PCIe標(biāo)準(zhǔn)之間的主要差異

自2003年推出以來(lái),PCIe發(fā)展至今已經(jīng)從最初的1.0升級(jí)到了6.0,本文則為大家簡(jiǎn)單介紹一下PCIe標(biāo)準(zhǔn)的演進(jìn)歷史以及各代PCIe標(biāo)準(zhǔn)之間的主要差異。

2023-12-14 標(biāo)簽:接口通信系統(tǒng)PCIe 1.1萬(wàn) 0

針對(duì)PCIe Gen5 M.2 NVMe SSD的L1.2低功耗測(cè)試

隨著兩周前Gigabyte AORUS Gen5 10000 SSD在美國(guó)Amazon和newegg的發(fā)售,以及其它廠家PCIe Gen5 M.2 SS...

PCIe標(biāo)準(zhǔn)自從推出以來(lái),1代和2代標(biāo)準(zhǔn)已經(jīng)在PC和Server上逐漸普及,用于滿足高速顯卡、高速存儲(chǔ)設(shè)備對(duì)于高速數(shù)據(jù)傳輸?shù)囊蟆3鲇谥С指呖偩€數(shù)據(jù)吞...

ZYNQ PCIe接口層次結(jié)構(gòu)及數(shù)據(jù)傳輸方式解析

一、PCIe概況 隨著現(xiàn)代處理器技術(shù)的發(fā)展,使用高速差分總線替代并行總線已是大勢(shì)所趨。與單端并行信號(hào)相比,高速差分信號(hào)可以使用更高的時(shí)鐘頻率,從而可以使...

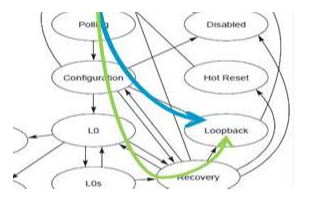

2020-12-31 標(biāo)簽:cpuPCIe狀態(tài)機(jī) 1.0萬(wàn) 0

CXL技術(shù)的三種模式 CXL技術(shù)與其他技術(shù)的對(duì)比

CXL的目標(biāo):解決CPU和設(shè)備、設(shè)備和設(shè)備之間的內(nèi)存鴻溝。服務(wù)器有巨大的內(nèi)存池和數(shù)量龐大的基于PCIe運(yùn)算加速器,每個(gè)上面都有很大的內(nèi)存。內(nèi)存的分割已經(jīng)...

基于Virtex-6 FPGA的雙緩沖模式PCIe總線設(shè)計(jì)方案和實(shí)現(xiàn)

本文設(shè)計(jì)了基于Xilinx Virtex6 FPGA的通用軟件無(wú)線電平臺(tái),利用C語(yǔ)言開(kāi)發(fā)了基于Linux系統(tǒng)的驅(qū)動(dòng)程序,利用Verilog語(yǔ)言設(shè)計(jì)基于X...

一個(gè)簡(jiǎn)單的Byte Enable使用的例子

TLP的類(lèi)型和路由方式由Fmt和Type所決定,這在前面關(guān)于TLP路由的文章中已經(jīng)詳細(xì)的介紹過(guò)。上圖顯示的是各種不同格式的TLP Header的相同的部分。

固態(tài)硬盤(pán)與U盤(pán)有什么區(qū)別

大家相信都買(mǎi)過(guò)U盤(pán),有一個(gè)很大的問(wèn)題就是很容易丟失數(shù)據(jù)。其實(shí)主要的原因就是U盤(pán)需要經(jīng)常插拔于不同的主機(jī)之間, 不正確的插拔操作 ,力度和角度控制不好,或...

一個(gè)簡(jiǎn)單地的例子來(lái)回顧PCIe總線的結(jié)構(gòu)、事務(wù)層、數(shù)據(jù)鏈路層和物理層

如下圖所示,Completer的應(yīng)用層會(huì)根據(jù)接受到的信息進(jìn)行相應(yīng)的處理,處理完成后會(huì)將數(shù)據(jù)發(fā)送至事務(wù)層,事務(wù)層根據(jù)這一信息創(chuàng)建一個(gè)新的TLP(即CplD...

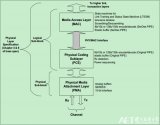

PCIe物理層接口定義了物理層中的,媒介層和物理編碼子層之間的統(tǒng)一接口

隨著高速串行技術(shù)的發(fā)展,各種串行通信技術(shù)的物理層逐漸走向了統(tǒng)一,用戶甚至可以基于FPGA中的SerDes/PCS完成多種高速串行通信接口的設(shè)計(jì)。這些通信...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語(yǔ)言教程專(zhuān)題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動(dòng)駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無(wú)刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺(jué) | 無(wú)人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國(guó)民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹(shù)莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |