完善資料讓更多小伙伴認(rèn)識你,還能領(lǐng)取20積分哦,立即完善>

標(biāo)簽 > pcie

PCI-Express(peripheral component interconnect express)是一種高速串行計算機(jī)擴(kuò)展總線標(biāo)準(zhǔn),它原來的名稱為“3GIO”,是由英特爾在2001年提出的,旨在替代舊的PCI,PCI-X和AGP總線標(biāo)準(zhǔn)。

文章:1249個 瀏覽:88473次 帖子:361個

西部數(shù)據(jù)My Net N900路由器內(nèi)部詳細(xì)拆解

My Net N900尚沒有與開源固件兼容,但另一款N750卻支持OpenWrt。說實話,由于My Net N900基于的是Ubicom的QoS處理器,...

本視頻介紹了設(shè)置和測試Xilinx PCIe DMA子系統(tǒng)性能的過程。

PCIe鏈路訓(xùn)練之通道極性和順序翻轉(zhuǎn)

PCIe使用差分信號對來傳輸數(shù)據(jù),即通過兩根電氣線傳輸,每根線攜帶相同的信號,但電壓極性相反,稱為正極(D+)和負(fù)極(D-)。通常發(fā)射端的D+直接連接到...

作為一個初學(xué)者,有的時候很難弄清楚ISE如何使用,本視頻教程以一種最簡單的方式展示如何使用ISE來開發(fā)一個XILINX FPGA工程。由于錄屏的原因,本...

xilinx sp605 PCIe EDK使用方法(之一:EDK設(shè)置部分)視頻教程

在EDK環(huán)境中針對在xilinx sp605 PCIe開發(fā)板,舉一個簡單的例子,介紹如何使用PCIE核與PC進(jìn)行數(shù)據(jù)通訊。

CvP系統(tǒng)結(jié)構(gòu)解析 PCIE協(xié)議實現(xiàn)FPGA 配置案例

1. CvP 簡介 CvP(Configuration via Protocol)是一種通過協(xié)議實現(xiàn) FPGA 配置的方案,Arria V,Cyclon...

物理層邏輯知識,關(guān)于擾碼器需要遵循的規(guī)則

前面的文章中提到過Ordered Sets,其主要用于鏈路訓(xùn)練等。每一個Ordered Set都是按照DW對齊的(即四個字節(jié)),且Ordered Set...

揭開Altera公司支持OpenCL的設(shè)計工具的神秘面紗

美國Altera公司將于2013年內(nèi)開始面向普通用戶提供可自動由按照異構(gòu)計算標(biāo)準(zhǔn)規(guī)格“Open-CL”編寫的程序生成FPGA專用電路的工具“Altera...

熱插拔的基本目的是要讓PCIe設(shè)備按照規(guī)定的順序、原則,從系統(tǒng)中移除或插入到系統(tǒng)中來,并能正常的工作,且不影響系統(tǒng)的正常運行。事實上,PCIe“熱插拔”...

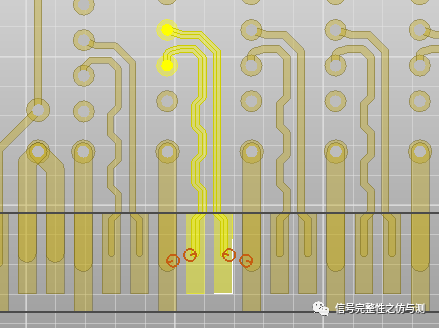

PCIe Gen5 Card金手指仿真與設(shè)計(下)

接上文提到有沒有更簡便的方法可以不做那么復(fù)雜的彎針模型呢?模型建立越接近真實情況固然越準(zhǔn)確,但是耗費時間,準(zhǔn)確和效率找到平衡才是智者所為。

什么是PCIe?PCIe有什么用途?PCIe 5.0有何不同?

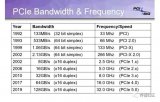

隨著英特爾Alder Lake CPU的發(fā)布,以及AMD 7000 Ryzen CPU的即將發(fā)布,PCIe 5.0 硬件終于成為現(xiàn)實。但什么是 PCIe...

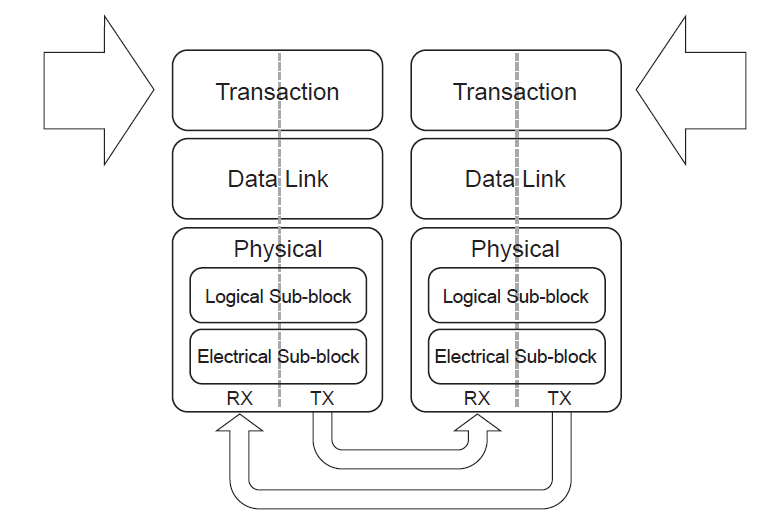

一個簡化的PCIe總線體系結(jié)構(gòu)如上圖所示,其中Device Core and interface to Transaction Layer就是我們常說的...

2018-04-21 標(biāo)簽:總線PCIe數(shù)據(jù)鏈路層 6.4k 0

PCI-SIG 組織期望這兩個標(biāo)準(zhǔn)在市場上共存一段時間,PCIe 5.0主要用于渴望達(dá)到最高吞吐量的高性能設(shè)備,如用于AI工作負(fù)載的GPU和網(wǎng)絡(luò)應(yīng)用。這...

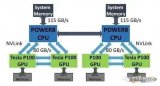

一文解析Nvlink的誕生和技術(shù)演進(jìn)歷程

Nvlink-C2C是個錯誤的技術(shù)路徑。 我仿佛記得Nvlink-C2C的主架構(gòu)師Wei wei是我大學(xué)同學(xué) ?有這么個模糊印象。 如果單純從技術(shù)的角度...

作為協(xié)議的最高層,事務(wù)層的主要功能是: ? 流水線式完整拆分交易協(xié)議 ? 區(qū)分事務(wù)層數(shù)據(jù)包 (TLP) 的排序和處理要求的機(jī)制 ? 基...

2023-05-22 標(biāo)簽:PCIe數(shù)據(jù)包TLP 6.2k 0

如何為KCU105評估套件創(chuàng)建Tandem設(shè)計

了解如何針對KCU105評估套件創(chuàng)建Tandem設(shè)計。 Tandem方法將比特流分成兩部分,允許首先加載比特流的PCIe部分,以確保在系統(tǒng)期間枚舉PCIe塊

隨著大數(shù)據(jù)中心、云計算服務(wù)的不斷增長,對于系統(tǒng)性能、功能和帶寬的要求也是越來越高,同時也驅(qū)動通信總線技術(shù)不斷取得新的進(jìn)步。由英特爾提出的第三代高性能I/...

換一批

換一批

編輯推薦廠商產(chǎn)品技術(shù)軟件/工具OS/語言教程專題

| 電機(jī)控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機(jī) | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機(jī) | PID | MOSFET | 傳感器 | 人工智能 | 物聯(lián)網(wǎng) | NXP | 賽靈思 |

| 步進(jìn)電機(jī) | SPWM | 充電樁 | IPM | 機(jī)器視覺 | 無人機(jī) | 三菱電機(jī) | ST |

| 伺服電機(jī) | SVPWM | 光伏發(fā)電 | UPS | AR | 智能電網(wǎng) | 國民技術(shù) | Microchip |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |