PCIe總線中的鏈路初始化與訓練(Link Initialization & Training)是一種完全由硬件實現的功能,處于PCIe體系結構中的物理層。整個過程由鏈路訓練狀態機(Link Training and Status State Machine,LTSSM)自動完成,也就說基本沒有數據鏈路層和事務層啥事。

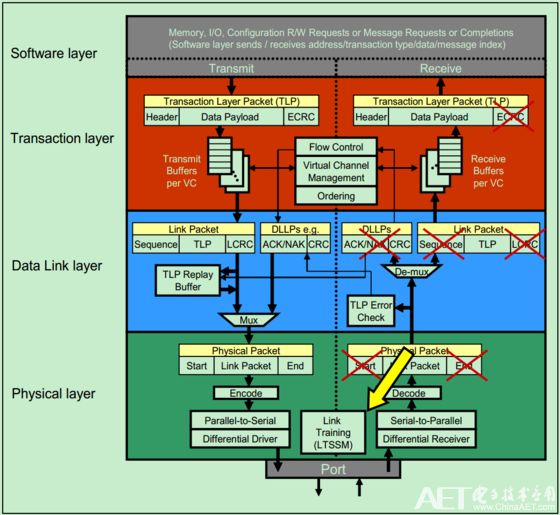

LTSSM在PCIe體系結構中的位置的示意圖如下:

在系統復位后,會自動進行鏈路訓練,以達成以下目標:位鎖定(Bit Lock)、字符鎖定(Symbol Lock,Gen1 & Gen2 Only)、塊鎖定(Block Lock,Gen3 Only)、確定鏈路寬度(Link Width)、通道位置翻轉(Lane Reversal)、信號極性翻轉(Polarity Inversion)、確定鏈路的數據率(Data Rate)和通道對齊(Lane-to-Lane De-skew)等功能。

下面依次的,簡要地介紹一下這些目標。

注:本次連載博文主要Gen2為主,所以一些和Gen3相關的內容只會簡單提及,并不會深入地介紹,有興趣的可以閱讀PCIe Spec V3.0或者Mindshare的相關書籍。

首先是

位鎖定(Bit Lock):

前面的文章中提到過,PCIe總線采用了一種嵌入式時鐘的機制,即發送端只向接收端發送數據信號,并不發送時鐘信號(時鐘信號影藏在數據信號中)。接收端可以通過CDR(Clock and Data Recovery)邏輯將時鐘從數據流中恢復出來,然后再用恢復出來的時鐘對數據信號進行采樣。當然,時鐘恢復需要一定的時間,才能保證時鐘信號與數據信號的相位對應關系符合要求。一旦CDR完成了時鐘的恢復,我們就說PCIe總線完成了位鎖定。

字符鎖定(Symbol Lock):

完成了位鎖定之后,只是能夠準確地識別出數據流中的0和1,還是不知道發送的內容是個啥。對于Gen1&Gen2來說,采用的8b/10b編碼,即傳輸的數據是以10bit為一個字符。LTSSM可以引導物理層相關邏輯通過識別COM字符(K28.5)來確定每個字符的開始與結束為止,即字符鎖定。

鏈路寬度(Link Width):

由于PCIe允許將x1的PCIe卡插入x4、x8甚至是x16的PCIe插槽中。因此在鏈路訓練與初始化過程中,相鄰的兩個PCIe設備需要相互通信來確定其支持的最大鏈路寬度。

注:實際上PCIe Spec還允許采用動態帶寬的機制,即允許鏈路寬度和數據率動態調整,以實現降低功耗等功能。

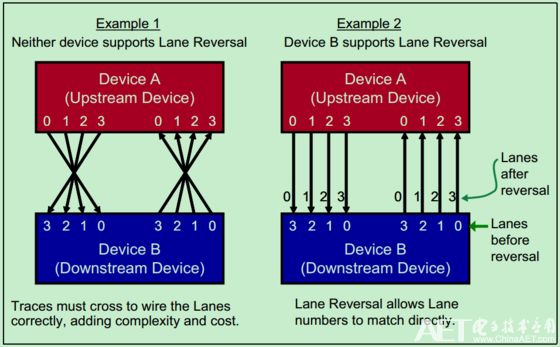

通道位置翻轉(Lane Reversal):

有的時候兩個PCIe設備的通道排列位置可能不太一致,PCIe Spec允許對默認的通道排列位置重新排列,如下圖所示。但是,從大部分的PCIe設備(PCIe卡和插槽等)都是按照統一的標準實現的,一般不會出現這種情況,因此這一功能是可選的。

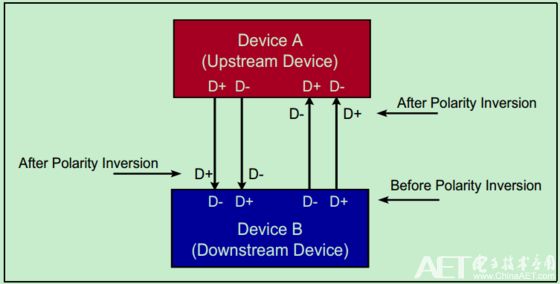

信號極性翻轉(Polarity Inversion):

前面的文章中介紹過,PCIe收發的都是差分信號,有的時候Link兩端的設備的對應信號的極性可能是相反的。因此,PCIe Spec允許在鏈路訓練與初始化的時候,對其進行調整,如下圖所示。和通道位置翻轉(Lane Reversal)不一樣的是,信號極性翻轉(Polarity Inversion)并不是一個可選項,而是所有標準PCIe設備都應支持的。

鏈路的數據率(Data Rate):

系統剛復位的時候,鏈路訓練和初始化都是基于2.5G T/s的速率的。如果Link兩端的設備都支持更高的速率,則會自動進入Re-training狀態,以重新切換速率。

注:PCIe Spec規定,高速率的PCIe設備必須能夠向下兼容。即Gen2必須同時支持2.5G T/s和5G T/s。

通道對齊(Lane-to-Lane De-skew):

PCIe鏈路完成字符鎖定后,還需要進行通道對齊。因為有的通道的信號可能先到達,有的可能后到達。PCIe Spec規定PCIe鏈路應有能力對一定范圍了的Lane-to-Lane Skew進行移除,使得各個Lane上的信號是同步的。關于通道對齊,會在后續的博文中詳細地介紹。

-

嵌入式

+關注

關注

5198文章

20442瀏覽量

333967 -

總線

+關注

關注

10文章

3040瀏覽量

91657 -

PCIe

+關注

關注

16文章

1460瀏覽量

88392

原文標題:【博文連載】PCIe掃盲——鏈路初始化與訓練基礎(一)

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

NVMe高速傳輸之擺脫XDMA設計34:初始化功能驗證與分析2

NVMe高速傳輸之擺脫XDMA設計49:主要功能測試結果與分析1

SRIO重復初始化后鏈路不通了

PCIe總線必須要先完成Flow Control初始化

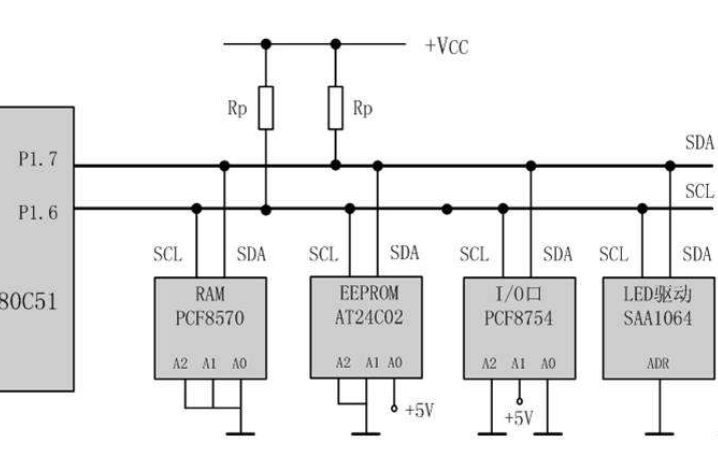

IIC總線初始化基本驅動參考程序應用代碼免費下載

DDR4-初始化、訓練和校準

GraniStudio:初始化例程

EtherCAT總線初始化步驟

PCIe總線中的鏈路初始化與訓練

PCIe總線中的鏈路初始化與訓練

評論