Spansion公司(紐約證交所代碼:CODE)今天宣布推出Spansion?語音協處理器,這是業界首款支持語音控制系統接口的人機接口(HMI)協處理器。憑借Nuance Communications公司(納斯達克代碼:

2012-07-04 09:21:42 1150

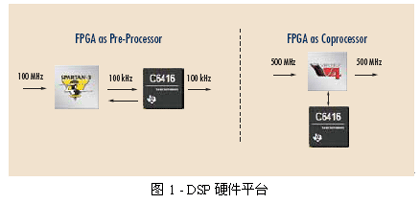

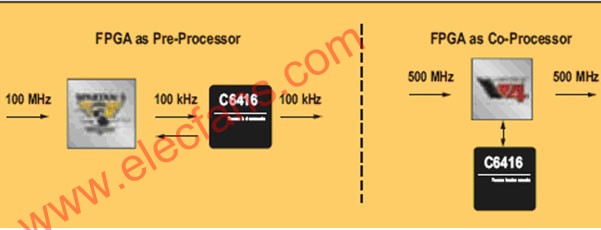

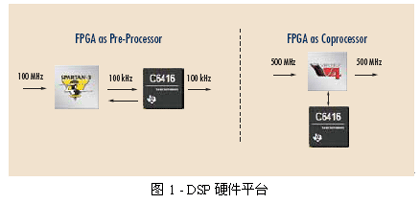

1150 傳統的、基于通用DSP處理器并運行由C語言開發的算法的高性能DSP平臺,正在朝著使用FPGA預處理器和/或協處理器的方向發展。這一最新發展能夠為產品提供巨大的性能、功耗和成本優勢。 盡管優勢如此明顯

2023-10-21 16:55:02 2727

2727

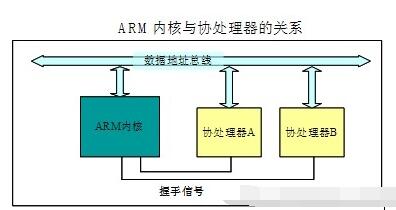

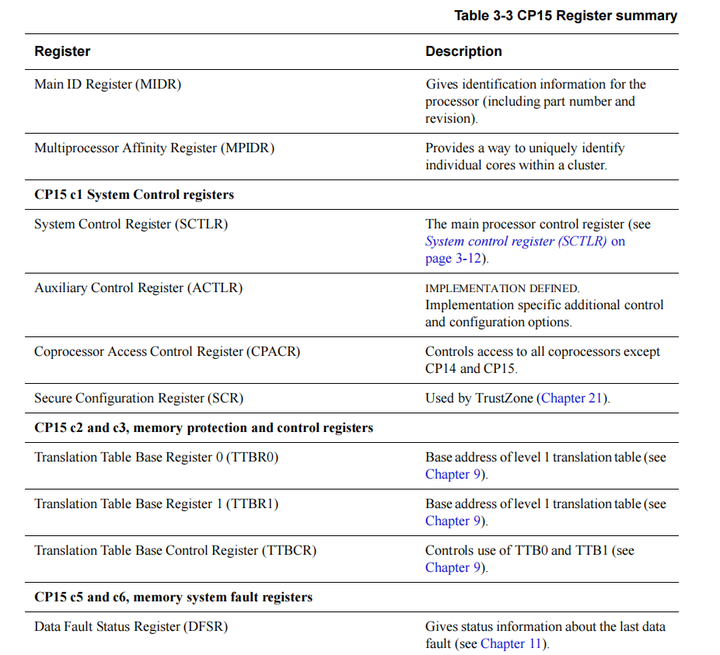

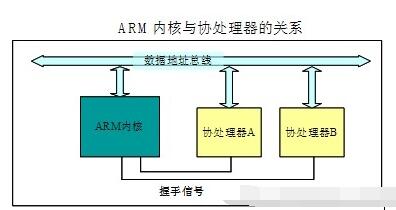

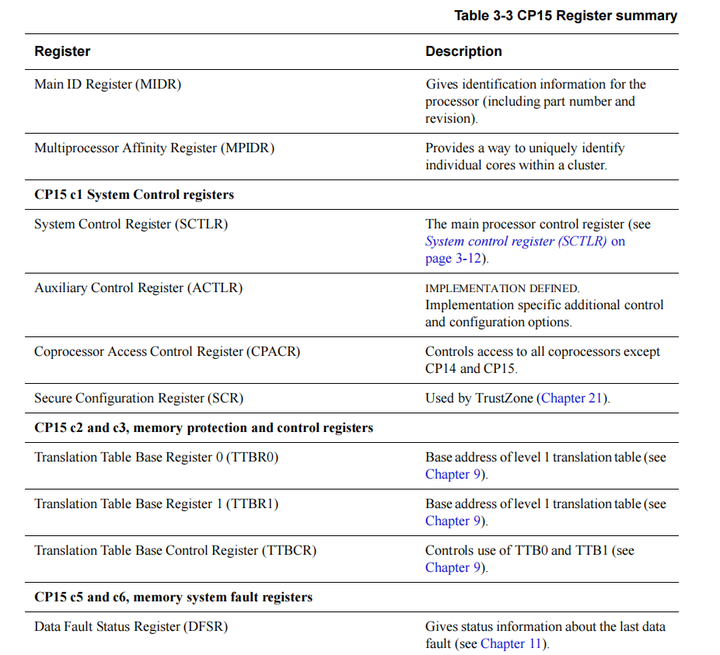

ARM架構通過支持協處理器來擴展處理器的功能。ARM架構的處理器支持最多16個協處理器,通常稱為CP0~CP15。下述的協處理器被ARM用于特殊用途。

2023-10-31 16:07:40 3831

3831

BlueNRG 系列芯片從最早的一代 BlueNRG-MS 開始就支持協處理器模式。

2024-01-05 18:16:10 3256

3256

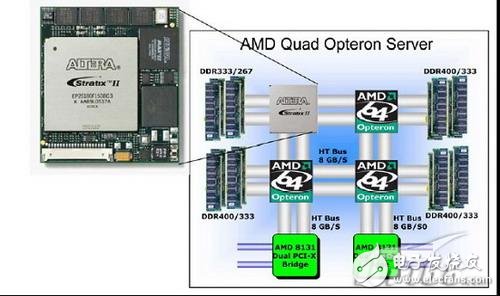

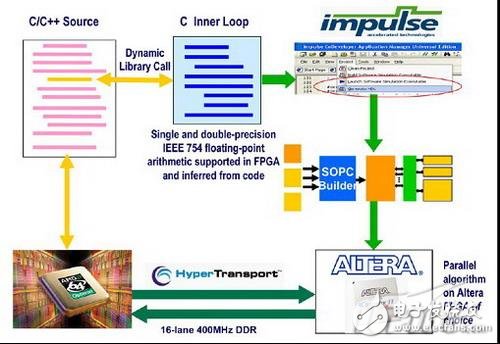

有誰來闡述一下FPGA協處理的優勢有哪些?如何去使用FPGA協處理?怎樣借助FPGA協處理去提升性能?怎樣借助FPGA嵌入式處理去降低成本?從C程序到系統門指的是什么?采用FPGA協處理的障礙是什么?

2021-04-14 06:07:36

傳統的、基于通用DSP處理器并運行由C語言開發的算法的高性能DSP平臺,正在朝著使用FPGA預處理器和/或協處理器的方向發展。這一最新發展能夠為產品提供巨大的性能、功耗和成本優勢。

2011-09-29 16:28:38

ARM的MMU主要實現什么功能?協處理器cp15主要主要實現何功能?簡述MMU使能時存儲訪問過程

2021-03-16 07:57:10

有了解AM335x的協處理器來做IO控制的嗎? 我目前看資料就只了解有PRU-ICSS這個協處理器,看了TI的一些維基百科的一些資料,知道要操作協處理器,必選要linux的SDK支持PRU,然后具體的就不知道怎么做了?

2018-11-29 16:52:29

本帖最后由 qzq378271387 于 2012-8-15 16:56 編輯

Altera的DSP_Builder現支持FPGA協處理器

2012-08-15 16:37:33

誰能向我解釋 BlueNRG-2 SoC 和 BlueNRG-2N 協處理器之間的區別?

2022-12-09 07:34:29

本設計首先根據MD5協處理器的功能設計MD5算法IP核,軟件部分使用串口程序助手進行64位加解密結果的輸出,E203內核根據地址取出對應的數據,使用相關的指令進行傳輸顯示。通過NICE接口將MD5協

2025-10-30 07:54:24

實現思路:

1.硬件設計,編寫相應的verilog文件,需要注意的是NICE協處理器定義了一些基本的接口;

2.編寫驅動,通過內聯匯編的偽指令.insn配置相關的驅動設置;

3.編寫用于測試

2025-10-23 07:05:09

使用擴展指令調用NICE協處理器完成預定操作,給出的優勢通常為代替CPU處理數據,但其實使用片上總線掛一個外設,然后驅動外設完成操作也可以實現相同的功能,所以想問一下協處理器相比于外設實現還有沒有其它方面的優勢

2025-05-28 08:31:12

cpu發送的信號,demo中狀態機在到達需要訪存的時刻把該信號置為有效,如下圖所示。

nice_icb_cmd_ready信號是cpu告知協處理器收到了訪存請求的反饋信號

2025-10-31 08:01:35

NICE協處理器最多可以處理多少個周期再抬高nice_rsp_valid啊?

2023-08-16 07:56:35

賽普拉斯的 PSoC? 模擬協處理器是可編程模擬協處理器的可擴展和可重配置的平臺架構;它能夠簡化帶有多個傳感器的嵌入式系統的設計。 PSoC 模擬協處理器設備集成了 PSoC 的靈活模擬前端

2020-09-01 16:50:45

XMC1300的MATH協處理器 1XMC1300芯片帶有一個MATH協處理器,它包含以下兩個子模塊除法器Cordic協處理器 2 除法器特性可做32位/32位,32位/16位,16位/16位除法

2018-12-11 10:57:03

呵呵,s3c2410...在vivi中的s3c2410.h文件中設置時鐘時 有這么一段mrc p15,0,r1,c1,c0,0orr r1,r1,#0xc0000000;mcr p15,0,r1,c1,c0,0這段的每句 的意思是什么?為什么要用到些處理器指令?協處理器指令的作用是干什么?

2019-02-25 12:34:48

處理器功能在硬件中實現以替代幾種軟件指令。通過減少多種代碼指令為單一指令,以及在硬件中直接實現指令的方式,從而實現代碼加速。最常用的協處理器是浮點單元(FPU),這是與CPU緊密結合的唯一普通協處理器

2015-02-02 14:18:19

代碼加速和代碼轉換到硬件協處理器的方法如何采用FPGA協處理器實現算法加速?

2021-04-13 06:39:25

舉例說明FPGA作為協處理器在實時系統中有哪些應用?FPGA用于協處理器有什么結構特點和設計原則?

2021-04-08 06:48:20

問題一:在vivado中編寫約束文件時,由于nice接口的指令是由CPU、協處理器和內存互相發送的,因此是否只需要約束clk和復位信號即可?

問題二:從軟件示例程序中可知,數據是由軟件輸入的,那

2023-08-16 07:24:08

本次給大家介紹的是利用Verdi調試協處理器的實現步驟。

有時為了觀察協處理器運行情況,需要查看協處理器接口的信號波形,此時可以用Verdi來查看主處理器發給協處理器的自定義指令以進一步追蹤協處理器

2025-10-30 08:26:28

國一的協處理器應用

(1) 概念

領域特定架構(Domain SpecificArchitecture,DSA),使用特定的硬件做特定的事情[18],也就是說,將主處理器和協處理器加速器適當

2025-10-21 14:35:54

實現功能:基于官方提供的demo nice的硬件代碼,設計一個基于e203 nice協處理的加法器。

NICE協處理器理論學習

nice協處理器的作用主要是用于控制通路的管理

去年國一的協處理器

2025-10-21 10:39:24

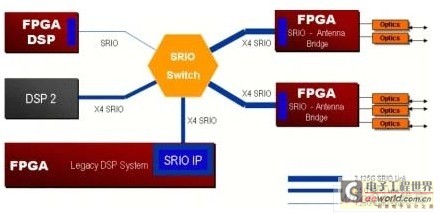

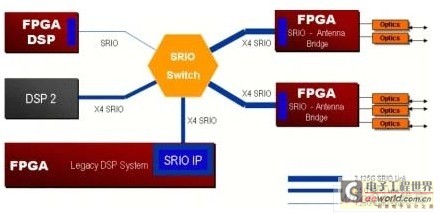

要跟上日益提高的性能需求,還得注意保持成本低廉有效利用基于串行RapidIO的FPGA作為DSP協處理器就能達到這些目的。那么,我們該怎么做呢?

2019-08-07 06:47:06

按照這句話的意思,協處理器拓展指令只能實現讀寫操作嗎,官方的案例貌似也只是讀寫指令。那如何用協處理器拓展指令實現更高級運算呢,用內聯匯編嗎

2023-08-16 07:41:54

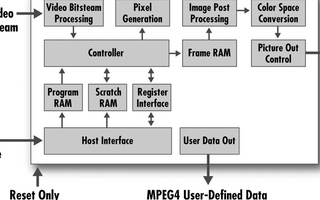

本文講述汽車娛樂系統的需求,討論主流系統構架,以及FPGA協處理器是如何集成到軟硬件體系中,以滿足高性能處理、靈活性和降低成本的要求。

2021-04-30 07:21:43

。5.協處理器寄存器傳送除了以上情況,在ARM和協處理器寄存器之間傳送數據有時是有用的。再以使用浮點協處理器為例,FIX指令從協處理器寄存器取得浮點數據,將它轉換為整數,并將整數傳送到ARM寄存器中

2022-04-24 09:36:47

`微機原理--數學協處理器[hide][/hide]`

2017-04-30 21:19:48

協處理器進行gpio操作,執行完成后 ULP RISC-V 協處理器退出,等待下一個ULP喚醒周期。可當在主MCU程序中使能 esp_sleep_enable_ulp_wakeup() 函數后,每當

2023-02-09 06:52:26

指令操作的協處理器名.標準名為pn,n,為0~15 opcode1協處理器的特定操作碼. 對于CP15寄存器來說,opcode1永遠為0,不為0時,操作結果不可預知CRd 作為目標寄存器的協處理器

2017-01-12 21:10:30

,各種不同的組合代表了不同的指令類型,我們用到了預定義的custom-3指令擴展協處理器指令,因此指令的opcode為7’b1111011。

由于蜂鳥E203處理器核基于Custom指令進行協

2025-10-24 07:23:37

當今的設計工程師受到面積、功率和成本的約束,不能采用GHz級的計算機實現嵌入式設計。在嵌入式系統中,通常是由相對數量較少的算法決定最大的運算需求。使用設計自動化工具可以將這些算法快速轉換到硬件協處理器中。然后,協處理器可以有效地連接到處理器,產生“GHz”級的性能。

2019-09-03 06:26:27

請問FPGA協處理器有哪些優勢?

2021-05-08 08:29:13

請問E203 Core和 NICE協處理器的主頻各是多少?

2023-08-12 08:06:09

我在ULP RISC-V協處理器的例程中,沒有發現有對ADC的操作,請問RISC-V協處理器目前還不支持嗎?使用的IDF版本為4.4.2。我想在ULP模式下,通過ADC來讀取外部器件的數據。

2023-02-13 06:34:36

我在ULP RISC-V協處理器的例程中,沒有發現有對ADC的操作,請問RISC-V協處理器目前還不支持嗎?使用的IDF版本為4.4.2。我想在ULP模式下,通過ADC來讀取外部器件的數據。

2023-03-06 06:33:44

使用擴展指令調用NICE協處理器完成預定操作,給出的優勢通常為代替CPU處理數據,但其實使用片上總線掛一個外設,然后驅動外設完成操作也可以實現相同的功能,所以想問一下協處理器相比于外設實現還有沒有其它方面的優勢

2025-05-29 08:21:02

;

:\"=r\"(zero)

:\"r\"(addr));}

這里把addr賦給x0,但是x0作為零寄存器不會保存任何信息?

然后func3和func7定義為2,2的含義是?

.insn是否為實現訪問協處理器的意思?

協處理器是否可以實現乘法加速?

2023-08-16 08:00:42

,有這樣定義的“協處理器可以附屬于 ARM 處理器。一個協處理器通過擴展指令集或提供配置寄存器來擴展內核處理功能。一個或多個協處理器可以通過協處理器接口與 ARM 內核相連。”如果定義“協處理器”為

2019-07-29 15:36:26

處理器。這些可配置協處理器可幫助設計人員解決傳統ASIC仿真中存在的許多問題,并更省力、更快捷地實現更精確的設計。

2019-07-23 06:24:16

飛思卡爾C29x加密協處理器:網絡數據安全的“門神”

2021-02-02 06:11:09

采用軟硬件結合的方法,給出一種基于VLIW 的并行可配置橢圓曲線密碼體制(ECC)專用指令協處理器架構。該協處理器采用點加、倍點并行調度算法,功能單元微結構采

2009-03-20 16:14:02 25

25 提出一種能同時在素數域和二進制有限域下支持任意曲線、任意域多項式的高速橢圓曲線密碼體系(ECC)協處理器。該協處理器可以完成ECC 中的各種基本運算,根據指令調用基本運算

2009-03-24 09:43:36 27

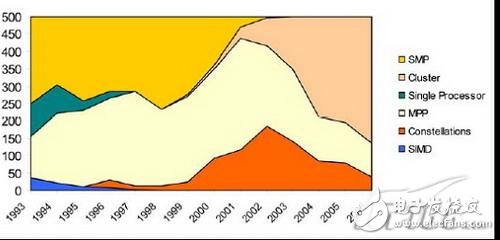

27 簡述了協處理器的概念、任務、發展歷程和現狀,探討了協處理器之所以引起人們重視和再重視的原因及其優勢,簡單介紹和展望了如何用FPGA 等類型協處理器構建高性能計算平臺。

2010-01-02 11:23:57 18

18 為性能加速的空間圖像處理開發FPGA協處理器快速、精確的圖像數據的板上分類是現代衛星圖像處理的關鍵部分。對于地球科學和其它應用而言,空間智能有效載荷利用智能機器

2010-04-27 08:30:31 15

15 利用串行RapidIO實現FPGA協處理

為了支持“三重播放”應用,人們對高速通信和超快速計算的需求日益增大,這向系統開發師

2010-03-25 14:48:25 1835

1835

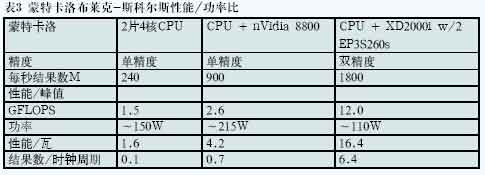

FPGA協處理技術介紹及進展

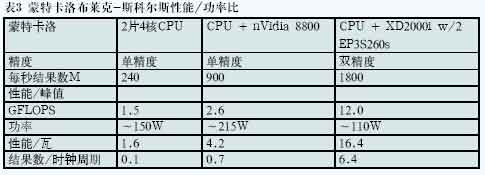

FPGA的架構使得許多算法得以實現,較之采用四核CPU或通用圖形處理器(GPGPU),這些算法的持續性能更接近器件的峰值性能

2010-04-26 18:15:08 1122

1122

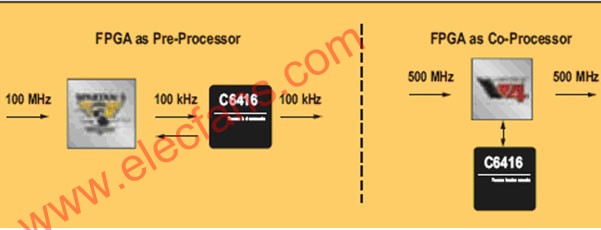

子系統劃分選擇方案

??????? FPGA可與DSP處理器一起使用,作為獨立的預處理器(有時是后處理器)器件,或者作為協

2010-08-11 10:03:47 823

823

微機原理--數學協處理器

2016-12-12 22:07:22 0

0 多核處理器中的超越函數協處理器設計_黃小康

2017-01-07 18:39:17 2

2 一種面向流應用加速的可重構協處理器_曹姍

2017-01-07 22:14:03 0

0 協處理器(coprocessor),一種芯片,用于減輕系統微處理器的特定處理任務。協處理器,這是一種協助中央處理器完成其無法執行或執行效率、效果低下的處理工作而開發和應用的處理器。

2017-11-10 15:56:35 3161

3161 當今的設計工程師受到面積、功率和成本的約束,不能采用GHz級的計算機實現嵌入式設計。在嵌入式系統中,通常是由相對數量較少的算法決定最大的運算需求。使用設計自動化工具可以將這些算法快速轉換到硬件協處理器中。然后,協處理器可以有效地連接到處理器,產生“GHz”級的性能。

2018-07-22 11:54:00 1630

1630

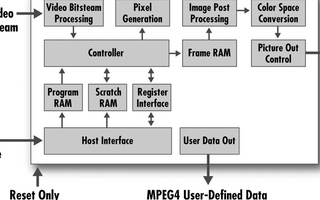

集成了數據通信、本地服務和視頻娛樂功能的高端汽車信息娛樂系統需要高性能的可編程處理技術支持,將FPGA協處理器整合進主流汽車信息通訊系統架構是最理想的解決方案。本文提出了汽車娛樂系統的要求,討論了

2017-12-07 05:25:01 2229

2229 協處理器,這是一種協助中央處理器完成其無法執行或執行效率、效果低下的處理工作而開發和應用的處理器。這種中央處理器無法執行的工作有很多,比如設備間的信號傳輸、接入設備的管理等;而執行效率、效果低下的有圖形處理、聲頻處理等。

2018-01-09 13:43:40 27647

27647

協處理器,一種芯片,用于減輕系統微處理器的特定處理任務。CPU的縮寫,譯為中央處理器。也做叫微處理器。指具有運算器和控制器功能的大規模集成電路。GPU圖形處理芯片。是顯示卡的“心臟”,也就相當于CPU在電腦中的作用

2018-01-09 14:46:03 12086

12086 協處理器共有68條不同的指令,匯編程序在遇到協處理器指令助記符時,都會將其轉換成機器語言的ESC指令,ESC指令代表了協處理器的操作碼。協處理器指令在執行過程中,需要訪問內存單元時,CPU會為其形成內存地址。協處理器在指令執行期間內利用數據總線來傳遞數據。

2018-01-09 14:58:28 2451

2451

Observer協處理器通常在一個特定的事件(諸如Get或Put)之前或之后發生,相當于RDBMS中的觸發器。Endpoint協處理器則類似于RDBMS中的存儲過程,因為它可以讓你在RegionServer上對數據執行自定義計算,而不是在客戶端上執行計算。

2018-01-09 16:18:54 2125

2125

協處理器,這是一種協助中央處理器完成其無法執行或執行效率、效果低下的處理工作而開發和應用的處理器。

2018-07-15 09:27:00 4868

4868 供電通道的實時電壓和電流,通過計算獲得協處理器實時功耗,并在實測數據的基礎上分別分析Xeon Phi協處理器啟動、空閑、線程和存儲系統等的功耗特征。實驗結果表明,該功耗模型為功耗優化提供了可信的基礎數據,能夠指導基于Xeon Phi處理器上的功耗優化。

2018-02-05 15:57:12 0

0 本文首先介紹了協處理器概念,其次介紹了協處理器內部結構與手機協處理器的作用,最后介紹了蘋果的M8協處理器的作用。

2018-04-24 09:27:14 23023

23023 本文主要介紹了五款內置協處理器的手機。協處理器用于減輕系統微處理器的負擔,執行特定處理任務。如,控制數字處理、處理圖像或視頻數據,或者感應和測量運動數據等。

2018-04-24 09:58:29 17393

17393 本文首先介紹了協處理器的相關概念,其次分析了驍龍835里是否有協處理器,最后闡述了驍龍835的性能參數。

2018-04-24 15:14:39 7034

7034 本文首先介紹了ARM處理器特點與主要模式,其次介紹了arm的協處理器有幾個,最后介紹了CP14和CP15系統控制協處理器。

2018-04-24 15:34:25 9690

9690 使用英特爾?至強處理器和英特爾?至強融核?協處理器為您的Fortran應用程序供電

2018-10-30 06:32:00 4118

4118 性能驗證-ON-Intel的Xeon的處理器和Xeon的PHI-協處理器簇

2018-11-07 06:36:00 4721

4721 使用英特爾?至強處理器和英特爾?至強融核?協處理器為您的Fortran應用程序供電

2018-11-07 06:36:06 3582

3582 了解協處理的價值,Zynq-7000加速器一致性端口,使用協處理器加速器的方法以及協處理器設計實例的概述。

2018-11-30 06:15:00 4782

4782 ARM7TDMI處理器指令集使您可以通過協處理器來實現特殊的附加指令。

2020-07-20 14:43:14 3545

3545

集成了數據通信,定位服務和視頻娛樂的高端汽車信息娛樂系統需要高性能的可編程處理技術,其最佳實現方法是在主流汽車信息通信系統構架中集成FPGA協處理器。本文講述汽車娛樂系統的需求,討論主流系統構架,以及FPGA協處理器是如何集成到軟硬件體系中,以滿足高性能處理、靈活性和降低成本的要求。

2020-07-24 15:25:00 1036

1036

IP核心平臺,可在FPGA和ASIC上的SoC環境中加速加密操作,其中包括了加速加密算法,增強篡改和入侵的檢測,增強數據和密鑰保護的安全性,增強內存訪問和I/O。 SoC/FPGA市場正在迅速發展,通過將加密協處理器IP嵌入到相關產品中,使之具有更多明顯的優勢。與軟件層相比,具有加密

2020-07-31 10:45:00 2805

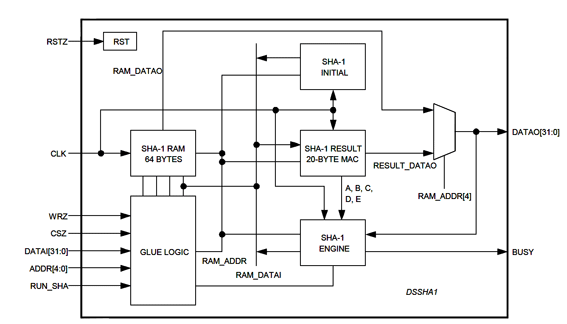

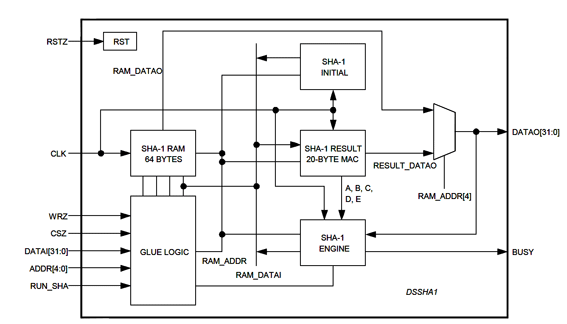

2805 本應用筆記介紹了 DSSHA1 可合成 SHA-1 協處理器,它可以在專用集成電路 (ASIC) 或現場可編程門陣列 (FPGA) 中實現,作為 DS2460 SHA-1 協處理器或基于微處理器的實現的替代方案.

2021-06-17 11:55:22 1965

1965

處理器中。然后,協處理器可以有效地連接到處理器,產生“GHz”級的性能。 本文主要研究了代碼加速和代碼轉換到硬件協處理器的方法。我們還分析了通過一個涉及到基于輔助處理器單元(APU)的實際圖像顯示案例的基準數據均衡決策的過

2021-09-28 10:38:04 4756

4756

通過Z-Wave OTA協處理器

2021-12-09 14:36:08 3

3 協處理器是一個處理單元,該處理單元與一個主處理單元一起使用來承擔通常由主處理單元執行的運算。通常,協處理器功能在硬件中實現以替代幾種軟件指令。通過減少多種代碼指令為單一指令,以及在硬件中直接實現指令的方式,從而實現代碼加速。

2022-10-27 12:41:27 1286

1286 WOLA 濾波器組協處理器:介紹性概念和技術

2022-11-15 19:48:19 11

11 的主機處理器。本應用筆記介紹了DSSHA1可合成SHA-1協處理器,該協處理器可在專用集成電路(ASIC)或現場可編程門陣列(FPGA)中實現,作為DS2460 SHA-1協處理器或基于微處理器的替代方案。

2023-02-20 13:44:53 1507

1507

的主機處理器。本應用筆記介紹了DSSHA1可合成SHA-1協處理器,該協處理器可在專用集成電路(ASIC)或現場可編程門陣列(FPGA)中實現,作為DS2460 SHA-1協處理器或基于微處理器的替代方案。

2023-06-13 16:26:33 1573

1573

處理器中。然后,協處理器可以有效地連接到處理器,產生“GHz”級的性能。 本文主要研究了代碼加速和代碼轉換到硬件協處理器的方法。我們還分析了通過一個涉及到基于輔助處理器單元(APU)的實際圖像顯示案例的基準數據均衡決策的過

2023-08-22 18:50:01 1460

1460 1、 ARM C15 協處理器 在 ARM 嵌入式應用系統中, 很多系統控制由 ARM CP15 協處理器來完成的。CP15 協處理器包含編號 0-15 的 16 個 32 位的寄存器。例如,ARM

2024-02-20 14:28:03 1372

1372

電子發燒友網站提供《使用TMS320C6416協處理器:Viterbi協處理器(VCP).pdf》資料免費下載

2024-10-21 09:36:00 0

0 電子發燒友網站提供《使用TMS320C6416協處理器:Turbo協處理器(TCP).pdf》資料免費下載

2024-10-23 10:16:19 0

0

電子發燒友App

電子發燒友App

評論