GPU作為一種協(xié)處理器,傳統(tǒng)用途主要是處理圖像類并行計算任務;計算機系統(tǒng)面對的計算任務有著復雜而不同的性能要求,當 CPU 無法滿足特定處理任務時,則需要一個針對性的協(xié)處理器輔助計算。GPU 就是

2023-01-10 10:12:45 2702

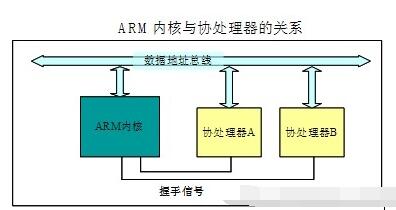

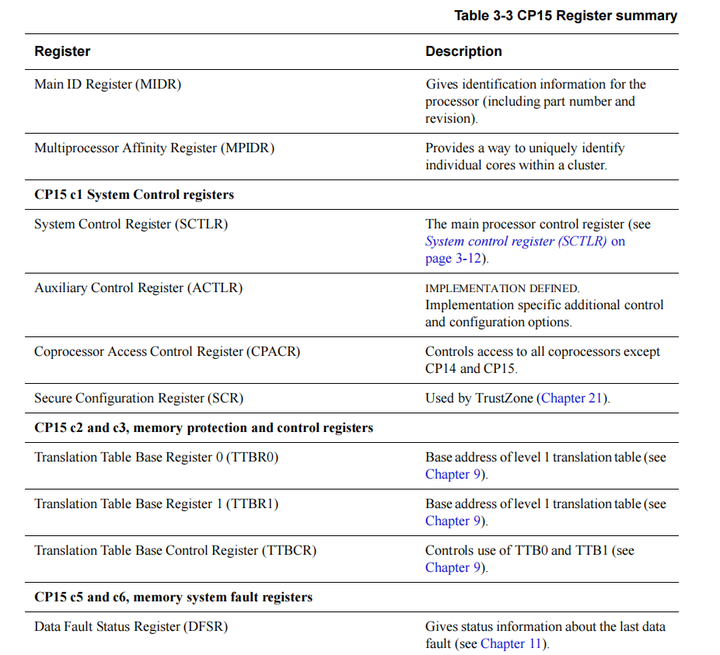

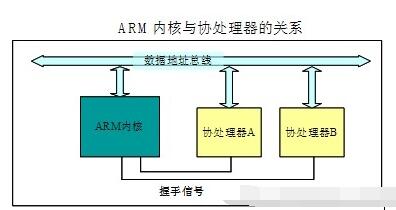

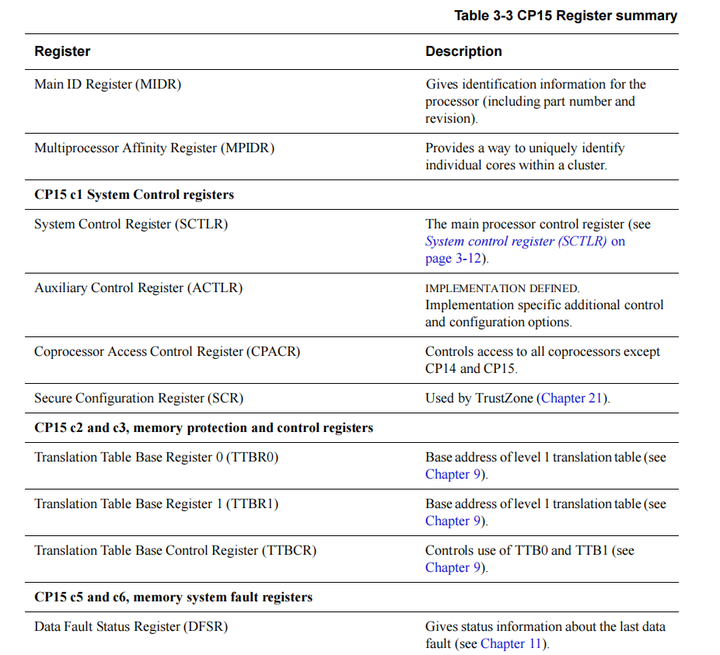

2702 ARM架構(gòu)通過支持協(xié)處理器來擴展處理器的功能。ARM架構(gòu)的處理器支持最多16個協(xié)處理器,通常稱為CP0~CP15。下述的協(xié)處理器被ARM用于特殊用途。

2023-10-31 16:07:40 3839

3839

處理器中斷處理的過程是怎樣的?處理器在讀內(nèi)存的過程中,CPU核、cache、MMU如何協(xié)同工作?

2021-10-18 08:57:48

ARM處理器狀態(tài)ARM微處理器的工作狀態(tài)一般有兩種,并可在兩種狀態(tài)之間切換:第一種為ARM狀態(tài),此時處理器執(zhí)行32位的字對齊的ARM指令;第二種為Thumb狀態(tài),此時處理器執(zhí)行16位的、半字對齊

2011-01-27 11:13:20

ARM處理器狀態(tài)ARM微處理器的工作狀態(tài)一般有兩種,并可在兩種狀態(tài)之間切換:第一種為ARM狀態(tài),此時處理器執(zhí)行32位的字對齊的ARM指令;第二種為Thumb狀態(tài),此時處理器執(zhí)行16位的、半字對齊

2011-01-27 14:19:05

傳統(tǒng)的、基于通用DSP處理器并運行由C語言開發(fā)的算法的高性能DSP平臺,正在朝著使用FPGA預處理器和/或協(xié)處理器的方向發(fā)展。這一最新發(fā)展能夠為產(chǎn)品提供巨大的性能、功耗和成本優(yōu)勢。

2011-09-29 16:28:38

本設(shè)計首先根據(jù)MD5協(xié)處理器的功能設(shè)計MD5算法IP核,軟件部分使用串口程序助手進行64位加解密結(jié)果的輸出,E203內(nèi)核根據(jù)地址取出對應的數(shù)據(jù),使用相關(guān)的指令進行傳輸顯示。通過NICE接口將MD5協(xié)

2025-10-30 07:54:24

寫?)

(e203_hbirdv2-mastere203_hbirdv2-masterrtle203subsyse203_subsys_nice_core.v)

NICE協(xié)處理器工作機理:?

請求通道:主處理器在流水線的EXU級時,將指令的編碼信息和源操作數(shù)傳輸?shù)?b class="flag-6" style="color: red">協(xié)處理器。

反饋

2025-10-23 07:05:09

使用擴展指令調(diào)用NICE協(xié)處理器完成預定操作,給出的優(yōu)勢通常為代替CPU處理數(shù)據(jù),但其實使用片上總線掛一個外設(shè),然后驅(qū)動外設(shè)完成操作也可以實現(xiàn)相同的功能,所以想問一下協(xié)處理器相比于外設(shè)實現(xiàn)還有沒有其它方面的優(yōu)勢

2025-05-28 08:31:12

的復位信號。

nice_active表示nice協(xié)處理器是否正在工作,但該信號在上層文件中未例化,如下圖所示。

nice_mem_holdup信號在e203_lsu_ctrl.v文件中用于覆蓋cpu

2025-10-31 08:01:35

。 PSoC模擬協(xié)處理器使設(shè)計能夠通過串行通信接口將聚合的,預處理的和格式化的傳感器數(shù)據(jù)發(fā)送到主機處理器。 產(chǎn)品亮點:1.具有可編程模擬模塊,如運算放大器,比較器,ADC,可為傳感器接口創(chuàng)建定制的模擬前端

2020-09-01 16:50:45

本帖最后由 一只耳朵怪 于 2018-6-7 15:52 編輯

WL1837MOD的CPU處理器需要滿足什么功能?其參考設(shè)計里提到用嵌入式ARM處理器作為CPU,用其他的也可以嗎,為什么?如果用ARM處理器,選哪種型號呢?希望能一一解答,謝謝

2018-06-07 06:39:30

XMC1300的MATH協(xié)處理器 1XMC1300芯片帶有一個MATH協(xié)處理器,它包含以下兩個子模塊除法器Cordic協(xié)處理器 2 除法器特性可做32位/32位,32位/16位,16位/16位除法

2018-12-11 10:57:03

arm處理器復位cpu后先進入管理模式,然后內(nèi)核是怎樣切換模式的,在程序中好像無法體現(xiàn)出來。

2023-02-09 16:59:39

。沒有通用的協(xié)處理器庫,即使是存在這樣的庫,將依然難以簡單地將協(xié)處理器與一個CPU(例如Pentium 4)連接。Xilinx Virtex-4 FX FPGA擁有一個或兩個PowerPC,每個都有一個

2015-02-02 14:18:19

代碼加速和代碼轉(zhuǎn)換到硬件協(xié)處理器的方法如何采用FPGA協(xié)處理器實現(xiàn)算法加速?

2021-04-13 06:39:25

舉例說明FPGA作為協(xié)處理器在實時系統(tǒng)中有哪些應用?FPGA用于協(xié)處理器有什么結(jié)構(gòu)特點和設(shè)計原則?

2021-04-08 06:48:20

問題一:在vivado中編寫約束文件時,由于nice接口的指令是由CPU、協(xié)處理器和內(nèi)存互相發(fā)送的,因此是否只需要約束clk和復位信號即可?

問題二:從軟件示例程序中可知,數(shù)據(jù)是由軟件輸入的,那

2023-08-16 07:24:08

分享一下RK3399處理器的GPU和CPU性能方法

2022-03-07 06:36:23

本次給大家介紹的是利用Verdi調(diào)試協(xié)處理器的實現(xiàn)步驟。

有時為了觀察協(xié)處理器運行情況,需要查看協(xié)處理器接口的信號波形,此時可以用Verdi來查看主處理器發(fā)給協(xié)處理器的自定義指令以進一步追蹤協(xié)處理器

2025-10-30 08:26:28

國一的協(xié)處理器應用

(1) 概念

領(lǐng)域特定架構(gòu)(Domain SpecificArchitecture,DSA),使用特定的硬件做特定的事情[18],也就是說,將主處理器和協(xié)處理器加速器適當

2025-10-21 14:35:54

創(chuàng)建用戶自定義RISC-V的指令。

(2) 如何調(diào)用NICE協(xié)處理器

調(diào)用NICE接口有4個通道,請求通道、存儲器請求通道、反饋通道、和存儲器反饋通道。請求通道:主處理器在流水線的EXU級時,將指令

2025-10-21 10:39:24

要跟上日益提高的性能需求,還得注意保持成本低廉有效利用基于串行RapidIO的FPGA作為DSP協(xié)處理器就能達到這些目的。那么,我們該怎么做呢?

2019-08-07 06:47:06

按照這句話的意思,協(xié)處理器拓展指令只能實現(xiàn)讀寫操作嗎,官方的案例貌似也只是讀寫指令。那如何用協(xié)處理器拓展指令實現(xiàn)更高級運算呢,用內(nèi)聯(lián)匯編嗎

2023-08-16 07:41:54

對于WL1837MOD的CPU的選擇,如果僅用一個ARM處理器來作為CPU可以嗎?該ARM處理器需要滿足什么功能?目前的ARM處理器,選擇哪款比較好呢?

希望大神們可以一一做出解答,萬分感謝!!!

2018-06-07 10:07:52

的數(shù)據(jù)類型,所以每個寄存器傳送的字數(shù)與協(xié)處理器有關(guān)。ARM產(chǎn)生的存儲器地址,但協(xié)處理器控制傳送的字數(shù)。協(xié)處理器可能執(zhí)行一些類型轉(zhuǎn)換作為傳送的一部分。例如,浮點協(xié)處理器將讀取的值轉(zhuǎn)換成它的80位內(nèi)部表示形式

2022-04-24 09:36:47

`微機原理--數(shù)學協(xié)處理器[hide][/hide]`

2017-04-30 21:19:48

怎么使用ARM處理器上的GPU進行編程工作呢?有哪位大神可以解釋一下

2022-08-04 14:17:35

ULP喚醒周期到的時候,喚醒 ULP RISC-V 協(xié)處理器的同時,將主MCU也喚醒了,然而ULP處理代碼中并未執(zhí)行 ulp_riscv_wakeup_main_processor() 函數(shù)。除非在主

2023-02-09 06:52:26

指令操作的協(xié)處理器名.標準名為pn,n,為0~15 opcode1協(xié)處理器的特定操作碼. 對于CP15寄存器來說,opcode1永遠為0,不為0時,操作結(jié)果不可預知CRd 作為目標寄存器的協(xié)處理器

2017-01-12 21:10:30

為什么盡管所有的趨勢都朝高端軟件開發(fā)和抽象級發(fā)展,而不重視底層的CPU與GPU指令集架構(gòu)(ISA)。但是當設(shè)計CPU、GPU和移動裝置用的其他處理器時,利用從一開始就為可擴展性建構(gòu)的高效處理架構(gòu)還是會帶來顯著的差異。

2021-02-26 07:06:39

我想在我的Realsense D415模塊中使用英特爾實感D4視覺處理器作為協(xié)處理器。那就是我有一對從一對相機中捕獲的立體聲圖像(我之前使用Opencv和2個相機系統(tǒng)的棋盤進行了校準)。是否可以將

2018-11-14 11:44:15

接口主要包含4個通道:

l 請求通道(RequestChannel):主要用于主處理器在EXU級將指令信息和源操作數(shù)派發(fā)給協(xié)處理器。

l 反饋通道(ResponseChannel):主要用于協(xié)處理器

2025-10-24 07:23:37

當今的設(shè)計工程師受到面積、功率和成本的約束,不能采用GHz級的計算機實現(xiàn)嵌入式設(shè)計。在嵌入式系統(tǒng)中,通常是由相對數(shù)量較少的算法決定最大的運算需求。使用設(shè)計自動化工具可以將這些算法快速轉(zhuǎn)換到硬件協(xié)處理器中。然后,協(xié)處理器可以有效地連接到處理器,產(chǎn)生“GHz”級的性能。

2019-09-03 06:26:27

請問FPGA協(xié)處理器有哪些優(yōu)勢?

2021-05-08 08:29:13

使用擴展指令調(diào)用NICE協(xié)處理器完成預定操作,給出的優(yōu)勢通常為代替CPU處理數(shù)據(jù),但其實使用片上總線掛一個外設(shè),然后驅(qū)動外設(shè)完成操作也可以實現(xiàn)相同的功能,所以想問一下協(xié)處理器相比于外設(shè)實現(xiàn)還有沒有其它方面的優(yōu)勢

2025-05-29 08:21:02

本帖最后由 一只耳朵怪 于 2018-6-8 10:52 編輯

TMS320F28035的協(xié)處理器CLA與主處理器如何協(xié)同工作,二者的接口是什么,是否有相關(guān)的中文資料提供呀!項目需要用到,如有中文資料或例程還望發(fā)給我一份!謝謝

2018-06-07 07:27:20

;

:\"=r\"(zero)

:\"r\"(addr));}

這里把addr賦給x0,但是x0作為零寄存器不會保存任何信息?

然后func3和func7定義為2,2的含義是?

.insn是否為實現(xiàn)訪問協(xié)處理器的意思?

協(xié)處理器是否可以實現(xiàn)乘法加速?

2023-08-16 08:00:42

是,uboot 新版的源碼中自帶這部分源碼。 這里給大家簡要介紹下上面的幾個重要名詞概念。3.2.2 ARM 的協(xié)處理器作者將介紹前面涉及到的寄存器(SVC32、MMU 和 iCACHE 等寄存器),對應

2019-07-29 15:36:26

處理器。這些可配置協(xié)處理器可幫助設(shè)計人員解決傳統(tǒng)ASIC仿真中存在的許多問題,并更省力、更快捷地實現(xiàn)更精確的設(shè)計。

2019-07-23 06:24:16

飛思卡爾C29x加密協(xié)處理器:網(wǎng)絡數(shù)據(jù)安全的“門神”

2021-02-02 06:11:09

簡述了協(xié)處理器的概念、任務、發(fā)展歷程和現(xiàn)狀,探討了協(xié)處理器之所以引起人們重視和再重視的原因及其優(yōu)勢,簡單介紹和展望了如何用FPGA 等類型協(xié)處理器構(gòu)建高性能計算平臺。

2010-01-02 11:23:57 18

18 系統(tǒng)控制協(xié)處理器是MIPS體系結(jié)構(gòu)CPU中必需的一個單元模塊。它最主要的功能就是利用一系列特權(quán)寄存器記錄當前CPU所處的狀態(tài),負責異常/中斷處理,提供指令正常執(zhí)行所需的環(huán)境。

2010-01-17 09:31:12 29

29 IPS體系結(jié)構(gòu)中的系統(tǒng)控制協(xié)處理器簡稱CP0,專門提供指令正常執(zhí)行所需的環(huán)境,進行異常/中斷處理、高速緩存填充、虛實地址轉(zhuǎn)換、操作模式轉(zhuǎn)換等操作。單從硬件的角度而言,系統(tǒng)控制協(xié)處理器對指令集的作用就相當于操作系統(tǒng)對應用程序的作用一樣。

2018-07-12 06:16:00 3883

3883

微機原理--數(shù)學協(xié)處理器

2016-12-12 22:07:22 0

0 多核處理器中的超越函數(shù)協(xié)處理器設(shè)計_黃小康

2017-01-07 18:39:17 2

2 IPS體系結(jié)構(gòu)中的系統(tǒng)控制協(xié)處理器簡稱CP0,它提供指令正常執(zhí)行所需的環(huán)境,進行異常/中斷處理、高速緩存填充、虛實地址轉(zhuǎn)換、操作模式轉(zhuǎn)換等操作。單從硬件的角度而言,系統(tǒng)控制協(xié)處理器對指令集的作用

2017-10-10 14:05:08 3

3 協(xié)處理器(coprocessor),一種芯片,用于減輕系統(tǒng)微處理器的特定處理任務。協(xié)處理器,這是一種協(xié)助中央處理器完成其無法執(zhí)行或執(zhí)行效率、效果低下的處理工作而開發(fā)和應用的處理器。

2017-11-10 15:56:35 3161

3161 集成了數(shù)據(jù)通信、本地服務和視頻娛樂功能的高端汽車信息娛樂系統(tǒng)需要高性能的可編程處理技術(shù)支持,將FPGA協(xié)處理器整合進主流汽車信息通訊系統(tǒng)架構(gòu)是最理想的解決方案。本文提出了汽車娛樂系統(tǒng)的要求,討論了

2017-12-07 05:25:01 2235

2235 協(xié)處理器,這是一種協(xié)助中央處理器完成其無法執(zhí)行或執(zhí)行效率、效果低下的處理工作而開發(fā)和應用的處理器。這種中央處理器無法執(zhí)行的工作有很多,比如設(shè)備間的信號傳輸、接入設(shè)備的管理等;而執(zhí)行效率、效果低下的有圖形處理、聲頻處理等。

2018-01-09 13:43:40 27647

27647

協(xié)處理器共有68條不同的指令,匯編程序在遇到協(xié)處理器指令助記符時,都會將其轉(zhuǎn)換成機器語言的ESC指令,ESC指令代表了協(xié)處理器的操作碼。協(xié)處理器指令在執(zhí)行過程中,需要訪問內(nèi)存單元時,CPU會為其形成內(nèi)存地址。協(xié)處理器在指令執(zhí)行期間內(nèi)利用數(shù)據(jù)總線來傳遞數(shù)據(jù)。

2018-01-09 14:58:28 2451

2451

Observer協(xié)處理器通常在一個特定的事件(諸如Get或Put)之前或之后發(fā)生,相當于RDBMS中的觸發(fā)器。Endpoint協(xié)處理器則類似于RDBMS中的存儲過程,因為它可以讓你在RegionServer上對數(shù)據(jù)執(zhí)行自定義計算,而不是在客戶端上執(zhí)行計算。

2018-01-09 16:18:54 2125

2125

協(xié)處理器,這是一種協(xié)助中央處理器完成其無法執(zhí)行或執(zhí)行效率、效果低下的處理工作而開發(fā)和應用的處理器。

2018-07-15 09:27:00 4870

4870 精確測量和分析Xeon Phi協(xié)處理器的功耗特征是實現(xiàn)協(xié)處理器功耗管理和優(yōu)化的基本前提,但準確提取和分析運行在Xeon Phi上并行程序的功耗較為復雜。為此,采用特制的功耗測量設(shè)備,完整提取14路

2018-02-05 15:57:12 0

0 命令處理器CP(Command Processor)是GPU中用來獲取從CPU中生成的命令,并進行解釋的處理單元。

2018-03-29 08:52:58 6490

6490 本文首先介紹了協(xié)處理器概念,其次介紹了協(xié)處理器內(nèi)部結(jié)構(gòu)與手機協(xié)處理器的作用,最后介紹了蘋果的M8協(xié)處理器的作用。

2018-04-24 09:27:14 23024

23024 本文主要介紹了五款內(nèi)置協(xié)處理器的手機。協(xié)處理器用于減輕系統(tǒng)微處理器的負擔,執(zhí)行特定處理任務。如,控制數(shù)字處理、處理圖像或視頻數(shù)據(jù),或者感應和測量運動數(shù)據(jù)等。

2018-04-24 09:58:29 17397

17397 本文首先介紹了協(xié)處理器的相關(guān)概念,其次分析了驍龍835里是否有協(xié)處理器,最后闡述了驍龍835的性能參數(shù)。

2018-04-24 15:14:39 7034

7034 本文首先介紹了ARM處理器特點與主要模式,其次介紹了arm的協(xié)處理器有幾個,最后介紹了CP14和CP15系統(tǒng)控制協(xié)處理器。

2018-04-24 15:34:25 9691

9691 據(jù)外媒報道,打造最好的人工智能芯片的戰(zhàn)斗已經(jīng)打響。作為CPU(中央處理器)和Xeon微處理器制造商,英特爾開始接受這個挑戰(zhàn)。作為GPU(圖形處理器)制造商,英偉達也發(fā)起了進攻。這兩家公司都在研發(fā)AI處理器。

2018-08-14 11:20:00 583

583 深度學習應用大量涌現(xiàn)使超級計算機的架構(gòu)逐漸向深度學習應用優(yōu)化,從傳統(tǒng) CPU 為主 GPU 為輔的英特爾處理器變?yōu)?GPU 為主 CPU 為輔的結(jié)構(gòu)。不過,未來相當長一段時間內(nèi),計算系統(tǒng)仍將保持 CPU + 協(xié)處理器的混合架構(gòu)。

2018-08-31 09:55:00 2087

2087 性能驗證-ON-Intel的Xeon的處理器和Xeon的PHI-協(xié)處理器簇

2018-11-07 06:36:00 4721

4721 了解協(xié)處理的價值,Zynq-7000加速器一致性端口,使用協(xié)處理器加速器的方法以及協(xié)處理器設(shè)計實例的概述。

2018-11-30 06:15:00 4782

4782 CPU-Z 1.91 現(xiàn)已發(fā)布。CPU-Z是一種診斷工具,可提供有關(guān)CPU的信息,包括:處理器名稱和供應商,核心步進和過程,處理器軟件包,內(nèi)部和外部時鐘,時鐘倍頻器,部分超頻檢測,處理器功能,支持的指令集,L1和L2緩存信息,位置,大小,速度和技術(shù)。

2019-12-17 14:18:48 3104

3104 ARM7TDMI處理器指令集使您可以通過協(xié)處理器來實現(xiàn)特殊的附加指令。

2020-07-20 14:43:14 3553

3553

CPU、GPU等協(xié)處理器、DSP、ASIC、FPGA等。一個異構(gòu)計算平臺往往包含使用不同指令集架構(gòu)(ISA)的處理器。

2020-09-04 15:03:09 7793

7793

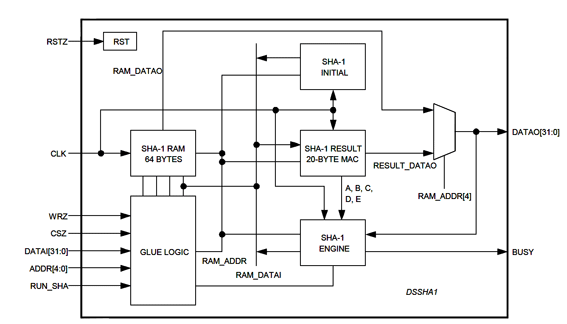

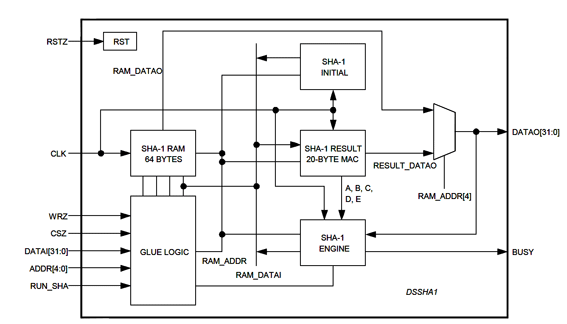

本應用筆記介紹了 DSSHA1 可合成 SHA-1 協(xié)處理器,它可以在專用集成電路 (ASIC) 或現(xiàn)場可編程門陣列 (FPGA) 中實現(xiàn),作為 DS2460 SHA-1 協(xié)處理器或基于微處理器的實現(xiàn)的替代方案.

2021-06-17 11:55:22 1966

1966

處理器中。然后,協(xié)處理器可以有效地連接到處理器,產(chǎn)生“GHz”級的性能。 本文主要研究了代碼加速和代碼轉(zhuǎn)換到硬件協(xié)處理器的方法。我們還分析了通過一個涉及到基于輔助處理器單元(APU)的實際圖像顯示案例的基準數(shù)據(jù)均衡決策的過

2021-09-28 10:38:04 4756

4756

通過Z-Wave OTA協(xié)處理器

2021-12-09 14:36:08 3

3 GPU是協(xié)處理器,與CPU端存儲是分離的,故GPU運算時必須先將CPU端的代碼和數(shù)據(jù)傳輸?shù)?b class="flag-6" style="color: red">GPU,GPU才能執(zhí)行kernel函數(shù)。涉及CPU 與GPU通信,其中通信接口PCI-E的版本和性能會直接影響通信帶寬。

2022-11-29 14:48:25 6537

6537 的主機處理器。本應用筆記介紹了DSSHA1可合成SHA-1協(xié)處理器,該協(xié)處理器可在專用集成電路(ASIC)或現(xiàn)場可編程門陣列(FPGA)中實現(xiàn),作為DS2460 SHA-1協(xié)處理器或基于微處理器的替代方案。

2023-02-20 13:44:53 1507

1507

圖形處理器 (GPU) 是專用于圖形處理運算的處理器。GPU 的主要功能之一是減輕中央處理器 (CPU) 上的負載,特別是在運行圖形密集型游戲或應用程序時。GPU 可以集成,也可以獨立。

2023-03-19 11:57:48 2509

2509 的主機處理器。本應用筆記介紹了DSSHA1可合成SHA-1協(xié)處理器,該協(xié)處理器可在專用集成電路(ASIC)或現(xiàn)場可編程門陣列(FPGA)中實現(xiàn),作為DS2460 SHA-1協(xié)處理器或基于微處理器的替代方案。

2023-06-13 16:26:33 1573

1573

現(xiàn)代GPU提供了頂點處理器和片段處理器兩個可編程并行處理部件。在利用GPU執(zhí)行圖像處理等通用計算任務時,要做的主要工作是把待求解的任務映射到GPU支持的圖形繪制流水線上。

2023-08-07 09:46:42 1805

1805

gpu和cpu哪個更重要? 當我們談到計算機的性能時,CPU(中央處理器)和GPU(圖形處理器)都是非常重要的組件。然而,在某些情況下,GPU和CPU的重要性會有所不同。在本文中,我們將討論GPU

2023-08-09 15:51:10 9330

9330 )中央處理器,它是電腦中的主要計算器件。CPU的主要任務是管理電腦的計算和處理。CPU可以理解為電腦“大腦”,它可以執(zhí)行所有的命令和計算任務。 GPU(Graphics Processing Unit

2023-08-09 16:15:53 15511

15511 GPU和CPU是計算機系統(tǒng)中最重要的兩種處理器,它們在不同的應用中發(fā)揮不同的作用。

2023-08-09 18:24:05 7491

7491 處理器中。然后,協(xié)處理器可以有效地連接到處理器,產(chǎn)生“GHz”級的性能。 本文主要研究了代碼加速和代碼轉(zhuǎn)換到硬件協(xié)處理器的方法。我們還分析了通過一個涉及到基于輔助處理器單元(APU)的實際圖像顯示案例的基準數(shù)據(jù)均衡決策的過

2023-08-22 18:50:01 1461

1461 (CPU)、Graphics Processing Unit(GPU)和Neural Processing Unit(NPU)等處理器和芯片被廣泛應用于各種領(lǐng)域。這些處理器和芯片在計算能力、功耗、功能

2023-08-27 17:03:08 13215

13215 以下是以表格形式提供的CPU和GPU之間的一些區(qū)別:中央處理器圖形處理器CPU代表中央處理器。GPU代表圖形處理單元。CPU是通用處理器。GPU是專用處理器。CPU更靈活,指令集更大,可以執(zhí)行廣泛

2023-12-14 08:28:03 2242

2242

處理器是GPU還是CPU,以及它們的計算方法和應用領(lǐng)域。 首先,讓我們了解一下何為GPU。GPU是圖形處理器的縮寫,它是用于處理圖形和高性能計算任務的專用處理器。與CPU不同,GPU具有大規(guī)模并行計算能力,可以同時處理數(shù)以千計的任務。因此,GPU非常適合處理需

2024-01-30 15:31:14 2215

2215 GPU和CPU是兩種常見的計算機處理器,它們在結(jié)構(gòu)和功能上有很大的區(qū)別。在這篇文章中,我們將探討GPU和CPU的區(qū)別,并詳細介紹它們的原理、應用領(lǐng)域和性能特點。 一、概述 1.1 GPU(圖形處理器

2024-02-20 11:24:47 21728

21728 1、 ARM C15 協(xié)處理器 在 ARM 嵌入式應用系統(tǒng)中, 很多系統(tǒng)控制由 ARM CP15 協(xié)處理器來完成的。CP15 協(xié)處理器包含編號 0-15 的 16 個 32 位的寄存器。例如,ARM

2024-02-20 14:28:03 1372

1372

電子發(fā)燒友網(wǎng)站提供《使用TMS320C6416協(xié)處理器:Viterbi協(xié)處理器(VCP).pdf》資料免費下載

2024-10-21 09:36:00 0

0 電子發(fā)燒友網(wǎng)站提供《使用TMS320C6416協(xié)處理器:Turbo協(xié)處理器(TCP).pdf》資料免費下載

2024-10-23 10:16:19 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論