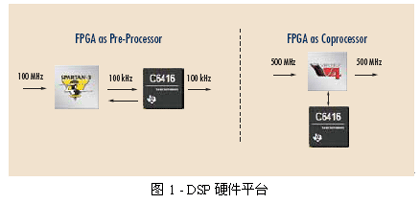

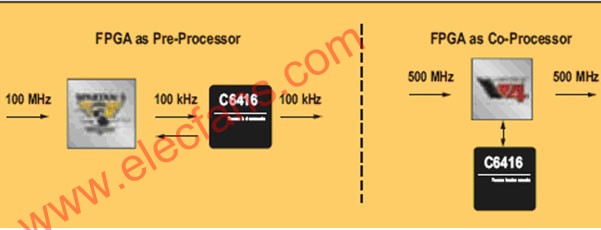

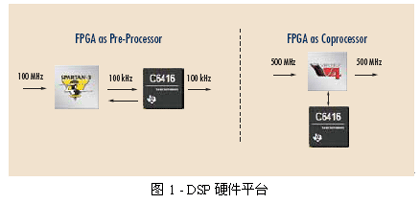

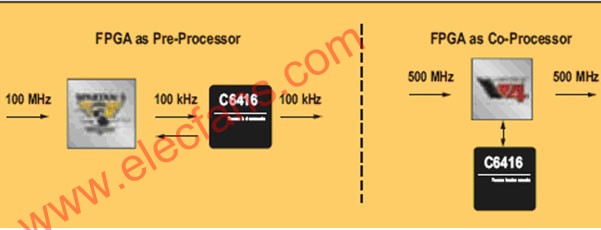

傳統(tǒng)的、基于通用DSP處理器并運行由C語言開發(fā)的算法的高性能DSP平臺,正在朝著使用FPGA預(yù)處理器和/或協(xié)處理器的方向發(fā)展。這一最新發(fā)展能夠為產(chǎn)品提供巨大的性能、功耗和成本優(yōu)勢。 盡管優(yōu)勢如此明顯

2023-10-21 16:55:02 2727

2727

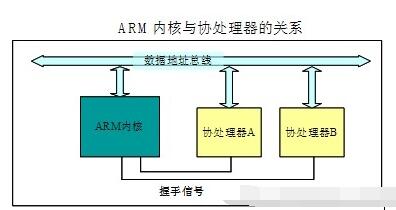

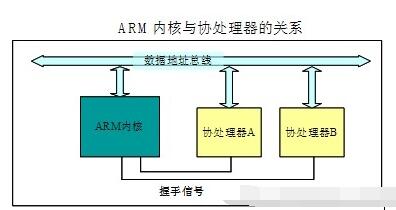

ARM架構(gòu)通過支持協(xié)處理器來擴展處理器的功能。ARM架構(gòu)的處理器支持最多16個協(xié)處理器,通常稱為CP0~CP15。下述的協(xié)處理器被ARM用于特殊用途。

2023-10-31 16:07:40 3831

3831

近日在中國光谷”國際光電子博覽會暨論壇(OVC EXPO2018)期間,“5G時代的信息通信產(chǎn)業(yè)高峰論壇”在中國光谷科技會展中心隆重舉行。烽火通信技術(shù)專家馬俊在現(xiàn)場發(fā)表了“5G時代的承載網(wǎng)絡(luò)技術(shù)演進”的主題演講,主要介紹了5G承載網(wǎng)絡(luò)需求與新技術(shù)進展,以及烽火在5G承載領(lǐng)域的進展和5G承載網(wǎng)部署建議。

2021-02-03 07:58:39

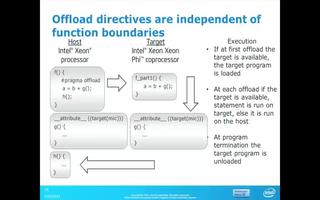

傳統(tǒng)的、基于通用DSP處理器并運行由C語言開發(fā)的算法的高性能DSP平臺,正在朝著使用FPGA預(yù)處理器和/或協(xié)處理器的方向發(fā)展。這一最新發(fā)展能夠為產(chǎn)品提供巨大的性能、功耗和成本優(yōu)勢。

2011-09-29 16:28:38

有誰來闡述一下FPGA協(xié)處理的優(yōu)勢有哪些?如何去使用FPGA協(xié)處理?怎樣借助FPGA協(xié)處理去提升性能?怎樣借助FPGA嵌入式處理去降低成本?從C程序到系統(tǒng)門指的是什么?采用FPGA協(xié)處理的障礙是什么?

2021-04-14 06:07:36

介紹IXIAIP測試平臺和所提供測試方案的最新進展

2021-05-26 06:46:28

本帖最后由 qzq378271387 于 2012-8-15 16:56 編輯

Altera的DSP_Builder現(xiàn)支持FPGA協(xié)處理器

2012-08-15 16:37:33

)等關(guān)鍵技術(shù),能大大提高無線通信系統(tǒng)的峰值數(shù)據(jù)速率、峰值譜效率、小區(qū)平均譜效率以及小區(qū)邊界用戶性能,同時也能提高整個網(wǎng)絡(luò)的組網(wǎng)效率,這使得LTE和LTE-A系統(tǒng)成為未來幾年內(nèi)無線通信發(fā)展的主流,本文將對這些關(guān)鍵技術(shù)及其標(biāo)準(zhǔn)進展進行介紹。

2019-06-14 06:41:50

的復(fù)位信號。

nice_active表示nice協(xié)處理器是否正在工作,但該信號在上層文件中未例化,如下圖所示。

nice_mem_holdup信號在e203_lsu_ctrl.v文件中用于覆蓋cpu

2025-10-31 08:01:35

賽普拉斯的 PSoC? 模擬協(xié)處理器是可編程模擬協(xié)處理器的可擴展和可重配置的平臺架構(gòu);它能夠簡化帶有多個傳感器的嵌入式系統(tǒng)的設(shè)計。 PSoC 模擬協(xié)處理器設(shè)備集成了 PSoC 的靈活模擬前端

2020-09-01 16:50:45

XMC1300的MATH協(xié)處理器 1XMC1300芯片帶有一個MATH協(xié)處理器,它包含以下兩個子模塊除法器Cordic協(xié)處理器 2 除法器特性可做32位/32位,32位/16位,16位/16位除法

2018-12-11 10:57:03

數(shù)據(jù)均衡決策的過程。該設(shè)計使用了在一個平臺FPGA中實現(xiàn)的一個嵌入式PowerPC。協(xié)處理器的意義協(xié)處理器是一個處理單元,該處理單元與一個主處理單元一起使用來承擔(dān)通常由主處理單元執(zhí)行的運算。通常,協(xié)

2015-02-02 14:18:19

代碼加速和代碼轉(zhuǎn)換到硬件協(xié)處理器的方法如何采用FPGA協(xié)處理器實現(xiàn)算法加速?

2021-04-13 06:39:25

舉例說明FPGA作為協(xié)處理器在實時系統(tǒng)中有哪些應(yīng)用?FPGA用于協(xié)處理器有什么結(jié)構(gòu)特點和設(shè)計原則?

2021-04-08 06:48:20

我需要在FPGA部分中構(gòu)建一個協(xié)處理器,例如計算CRC或其他對一塊數(shù)據(jù)執(zhí)行一些糾錯。我想知道哪些應(yīng)用筆記(和/或用戶指南/教程)談?wù)撨@個主題:像一個簡單的基于axi寄存器的自定義IP,或基于AXIS

2019-04-23 15:18:59

問題一:在vivado中編寫約束文件時,由于nice接口的指令是由CPU、協(xié)處理器和內(nèi)存互相發(fā)送的,因此是否只需要約束clk和復(fù)位信號即可?

問題二:從軟件示例程序中可知,數(shù)據(jù)是由軟件輸入的,那

2023-08-16 07:24:08

dB時能測到雷達(dá)信號,使雷達(dá)的有效作用距離提高。本文主要介紹基于DSP和FPGA技術(shù)的低信噪比情況下雷達(dá)信號的檢測。

2019-07-04 06:55:39

本次給大家介紹的是利用Verdi調(diào)試協(xié)處理器的實現(xiàn)步驟。

有時為了觀察協(xié)處理器運行情況,需要查看協(xié)處理器接口的信號波形,此時可以用Verdi來查看主處理器發(fā)給協(xié)處理器的自定義指令以進一步追蹤協(xié)處理

2025-10-30 08:26:28

單片機自檢技術(shù)的研究現(xiàn)狀及進展情況??要弄開題報告,求大神幫助!!

2015-03-25 11:37:26

1、實現(xiàn)功能

基于官方提供的demo nice的硬件代碼,設(shè)計一個基于e203 nice協(xié)處理的加法器。

2NICE協(xié)處理器理論學(xué)習(xí)

nice協(xié)處理器的作用主要是用于控制通路的管理

去年

2025-10-21 14:35:54

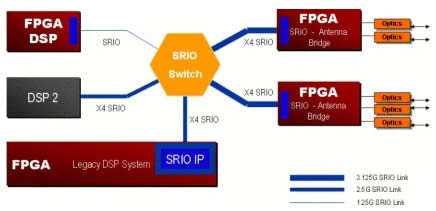

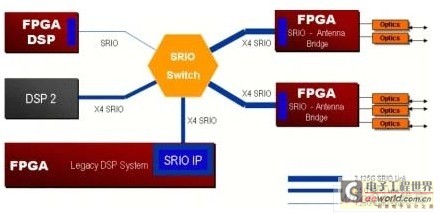

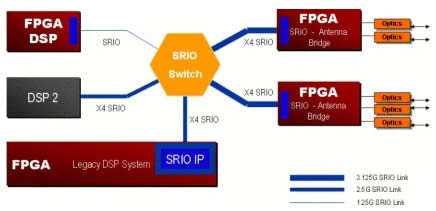

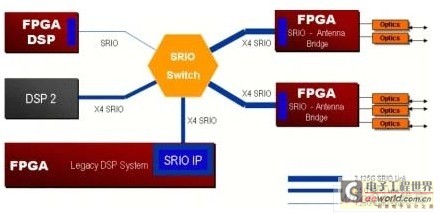

運算平臺之間是如何連接的?SRIO系統(tǒng)的應(yīng)用實例有哪些?如何利用串行RapidIO去實現(xiàn)FPGA協(xié)處理?

2021-04-29 06:17:59

要跟上日益提高的性能需求,還得注意保持成本低廉有效利用基于串行RapidIO的FPGA作為DSP協(xié)處理器就能達(dá)到這些目的。那么,我們該怎么做呢?

2019-08-07 06:47:06

按照這句話的意思,協(xié)處理器拓展指令只能實現(xiàn)讀寫操作嗎,官方的案例貌似也只是讀寫指令。那如何用協(xié)處理器拓展指令實現(xiàn)更高級運算呢,用內(nèi)聯(lián)匯編嗎

2023-08-16 07:41:54

您可以顯著提高無線系統(tǒng)中信號處理功能的性能。怎樣提高呢?有效方法是利用FPGA結(jié)構(gòu)的靈活性和目前受益于并行處理的FPGA架構(gòu)中的嵌入式DSP模塊。

2019-10-23 07:04:22

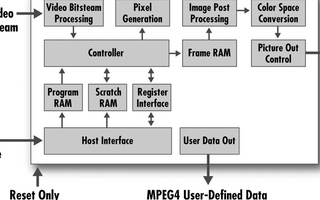

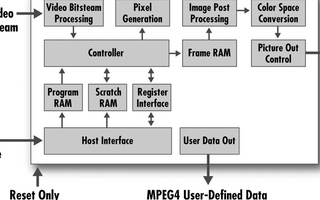

本文講述汽車娛樂系統(tǒng)的需求,討論主流系統(tǒng)構(gòu)架,以及FPGA協(xié)處理器是如何集成到軟硬件體系中,以滿足高性能處理、靈活性和降低成本的要求。

2021-04-30 07:21:43

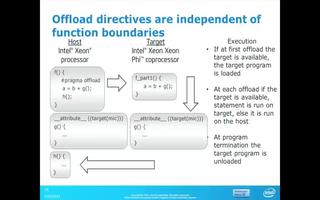

ARM通過增加硬件協(xié)處理器來支持對其指令集的通用擴展,通過未定義指令陷阱支持這些協(xié)處理器的軟件仿真。簡單的ARM核提供板級協(xié)處理器接口,因此協(xié)處理器可作為一個獨立的元件接入。高速時鐘使得板級接口非常

2022-04-24 09:36:47

`微機原理--數(shù)學(xué)協(xié)處理器[hide][/hide]`

2017-04-30 21:19:48

您可以顯著提高無線系統(tǒng)中信號處理功能的性能。怎樣提高呢?有效方法是利用FPGA結(jié)構(gòu)的靈活性和目前受益于并行處理的FPGA架構(gòu)中的嵌入式DSP模塊。

2019-09-19 07:50:50

有什么方法可以增強DSP協(xié)處理能力嗎?

2021-05-28 06:52:41

大家好,我們是想的不對做的隊,報名編號是CICC1429,本次給大家介紹示例協(xié)處理器詳細(xì)的實現(xiàn)步驟以及部分錯誤

1. mcs文件的生成與燒寫

參考4.2. How to generate mcs

2025-10-31 06:22:30

當(dāng)今的設(shè)計工程師受到面積、功率和成本的約束,不能采用GHz級的計算機實現(xiàn)嵌入式設(shè)計。在嵌入式系統(tǒng)中,通常是由相對數(shù)量較少的算法決定最大的運算需求。使用設(shè)計自動化工具可以將這些算法快速轉(zhuǎn)換到硬件協(xié)處理器中。然后,協(xié)處理器可以有效地連接到處理器,產(chǎn)生“GHz”級的性能。

2019-09-03 06:26:27

請問FPGA協(xié)處理器有哪些優(yōu)勢?

2021-05-08 08:29:13

`直播主題及亮點:在介紹中國車聯(lián)網(wǎng)的發(fā)展歷史的基礎(chǔ)上,分析目前的車聯(lián)網(wǎng)產(chǎn)品類型和技術(shù)路線,分析5G的技術(shù)特點、優(yōu)勢和未來市場發(fā)展趨勢,介紹北斗與GPS的區(qū)別和北斗衛(wèi)星的最新進展和應(yīng)用。針對即將成為車

2018-09-21 14:01:58

嘗試采用多核和硬件協(xié)處理加速技術(shù)朝系統(tǒng)并行化方向發(fā)展。在實際設(shè)計中,FPGA已經(jīng)成為CPU的硬件協(xié)加速器,很多芯片廠商采用了硬核或軟核CPU+FPGA的模式,今后這一趨勢也將繼續(xù)下去

2011-07-21 10:52:00

是,uboot 新版的源碼中自帶這部分源碼。 這里給大家簡要介紹下上面的幾個重要名詞概念。3.2.2 ARM 的協(xié)處理器作者將介紹前面涉及到的寄存器(SVC32、MMU 和 iCACHE 等寄存器),對應(yīng)

2019-07-29 15:36:26

在緊迫的時間要求和一次成功的巨大壓力下,ASIC仿真已成為設(shè)計流程中一個關(guān)鍵的環(huán)節(jié)。但一直以來,設(shè)計人員在ASIC仿真方面的優(yōu)選并不多。現(xiàn)在,許多設(shè)計人員開始轉(zhuǎn)而選用一種新工具——基于FPGA的協(xié)

2019-07-23 06:24:16

您可以顯著提高無線系統(tǒng)中信號處理功能的性能。怎樣提高呢?有效方法是利用FPGA結(jié)構(gòu)的靈活性和目前受益于并行處理的FPGA架構(gòu)中的嵌入式DSP模塊。常見于無線應(yīng)用中這類處理包括有限沖激響應(yīng)(FIR

2019-07-15 06:18:56

風(fēng)光互補技術(shù)原理及最新進展摘要: 簡要回顧國內(nèi)外風(fēng)電、光伏技術(shù)與應(yīng)用發(fā)展態(tài)勢,結(jié)合風(fēng)光互補系統(tǒng)應(yīng)用, 分析、介紹了風(fēng)光互補LED路燈照明系統(tǒng)、智能控制器設(shè)計、分布式供電電源、風(fēng)光互補水泵系統(tǒng),并著重

2009-10-26 13:45:56

風(fēng)光互補技術(shù)及應(yīng)用新進展 [hide]風(fēng)光互補技術(shù)及應(yīng)用新進展.rar[/hide] [此貼子已經(jīng)被作者于2009-10-22 11:52:24編輯過]

2009-10-22 11:51:20

簡述了協(xié)處理器的概念、任務(wù)、發(fā)展歷程和現(xiàn)狀,探討了協(xié)處理器之所以引起人們重視和再重視的原因及其優(yōu)勢,簡單介紹和展望了如何用FPGA 等類型協(xié)處理器構(gòu)建高性能計算平臺。

2010-01-02 11:23:57 18

18 為性能加速的空間圖像處理開發(fā)FPGA協(xié)處理器快速、精確的圖像數(shù)據(jù)的板上分類是現(xiàn)代衛(wèi)星圖像處理的關(guān)鍵部分。對于地球科學(xué)和其它應(yīng)用而言,空間智能有效載荷利用智能機器

2010-04-27 08:30:31 15

15 的Kintex-7系列FPGA JFM7K325T16作為協(xié)處理單元,具有1個FMC子卡接口,具有4路SFP+萬兆光纖接口,具有2路RJ45千兆以太網(wǎng)接口,其中1路掛在

2025-12-19 17:48:31

利用串行RapidIO實現(xiàn)FPGA協(xié)處理

為了支持“三重播放”應(yīng)用,人們對高速通信和超快速計算的需求日益增大,這向系統(tǒng)開發(fā)師、算法開發(fā)師和硬件工程師等人員提出了新

2010-02-25 17:06:55 1674

1674

利用串行RapidIO實現(xiàn)FPGA協(xié)處理

為了支持“三重播放”應(yīng)用,人們對高速通信和超快速計算的需求日益增大,這向系統(tǒng)開發(fā)師

2010-03-25 14:48:25 1835

1835

子系統(tǒng)劃分選擇方案

??????? FPGA可與DSP處理器一起使用,作為獨立的預(yù)處理器(有時是后處理器)器件,或者作為協(xié)

2010-08-11 10:03:47 823

823

借助FPGA協(xié)處理提升性能 設(shè)計人員能夠利用由FPGA架構(gòu)的并行性所帶來的使用靈活的特點,大幅提升DSP系統(tǒng)的性能。通常的設(shè)計示例包括(并不局限于)FIR濾波、FFT、數(shù)字下變頻和前向糾錯(FEC)模塊等。 Xilinx Virtex TM-4和Virtex-5架構(gòu)提供了多達(dá)512個并行乘

2011-02-28 12:50:41 46

46 對FPGA技術(shù)來說,早期研發(fā)在5年前就已開始嘗試采用多核和硬件協(xié)處理加速技術(shù)朝系統(tǒng)并行化方向發(fā)展。在實際設(shè)計中,FPGA已經(jīng)成為CPU的硬件協(xié)加速器,很多芯片廠商采用了硬核或軟核CPU+FPGA的

2011-09-23 15:30:06 938

938 微機原理--數(shù)學(xué)協(xié)處理器

2016-12-12 22:07:22 0

0 多核處理器中的超越函數(shù)協(xié)處理器設(shè)計_黃小康

2017-01-07 18:39:17 2

2 協(xié)處理器(coprocessor),一種芯片,用于減輕系統(tǒng)微處理器的特定處理任務(wù)。協(xié)處理器,這是一種協(xié)助中央處理器完成其無法執(zhí)行或執(zhí)行效率、效果低下的處理工作而開發(fā)和應(yīng)用的處理器。

2017-11-10 15:56:35 3161

3161 當(dāng)今的設(shè)計工程師受到面積、功率和成本的約束,不能采用GHz級的計算機實現(xiàn)嵌入式設(shè)計。在嵌入式系統(tǒng)中,通常是由相對數(shù)量較少的算法決定最大的運算需求。使用設(shè)計自動化工具可以將這些算法快速轉(zhuǎn)換到硬件協(xié)處理器中。然后,協(xié)處理器可以有效地連接到處理器,產(chǎn)生“GHz”級的性能。

2018-07-22 11:54:00 1630

1630

集成了數(shù)據(jù)通信、本地服務(wù)和視頻娛樂功能的高端汽車信息娛樂系統(tǒng)需要高性能的可編程處理技術(shù)支持,將FPGA協(xié)處理器整合進主流汽車信息通訊系統(tǒng)架構(gòu)是最理想的解決方案。本文提出了汽車娛樂系統(tǒng)的要求,討論了

2017-12-07 05:25:01 2229

2229 本文主要介紹了一種基于DSP+FPGA視頻圖像采集處理系統(tǒng)的設(shè)計與實現(xiàn),DSP-BF561作為主處理器,負(fù)責(zé)整個算法的調(diào)度和數(shù)據(jù)流的控制,完成圖像數(shù)據(jù)的采集與顯示及核心算法的實現(xiàn),FPGA作為DSP的協(xié)處理器,依托其高度的并行處理能力,完成圖像預(yù)處理中大量的累乘加運算。實驗證明系統(tǒng)達(dá)到了實時性要求。

2017-12-25 10:39:47 5649

5649

協(xié)處理器,這是一種協(xié)助中央處理器完成其無法執(zhí)行或執(zhí)行效率、效果低下的處理工作而開發(fā)和應(yīng)用的處理器。這種中央處理器無法執(zhí)行的工作有很多,比如設(shè)備間的信號傳輸、接入設(shè)備的管理等;而執(zhí)行效率、效果低下的有圖形處理、聲頻處理等。

2018-01-09 13:43:40 27647

27647

協(xié)處理器共有68條不同的指令,匯編程序在遇到協(xié)處理器指令助記符時,都會將其轉(zhuǎn)換成機器語言的ESC指令,ESC指令代表了協(xié)處理器的操作碼。協(xié)處理器指令在執(zhí)行過程中,需要訪問內(nèi)存單元時,CPU會為其形成內(nèi)存地址。協(xié)處理器在指令執(zhí)行期間內(nèi)利用數(shù)據(jù)總線來傳遞數(shù)據(jù)。

2018-01-09 14:58:28 2451

2451

協(xié)處理器,這是一種協(xié)助中央處理器完成其無法執(zhí)行或執(zhí)行效率、效果低下的處理工作而開發(fā)和應(yīng)用的處理器。

2018-07-15 09:27:00 4868

4868 精確測量和分析Xeon Phi協(xié)處理器的功耗特征是實現(xiàn)協(xié)處理器功耗管理和優(yōu)化的基本前提,但準(zhǔn)確提取和分析運行在Xeon Phi上并行程序的功耗較為復(fù)雜。為此,采用特制的功耗測量設(shè)備,完整提取14路

2018-02-05 15:57:12 0

0 本文首先介紹了協(xié)處理器概念,其次介紹了協(xié)處理器內(nèi)部結(jié)構(gòu)與手機協(xié)處理器的作用,最后介紹了蘋果的M8協(xié)處理器的作用。

2018-04-24 09:27:14 23024

23024 本文主要介紹了五款內(nèi)置協(xié)處理器的手機。協(xié)處理器用于減輕系統(tǒng)微處理器的負(fù)擔(dān),執(zhí)行特定處理任務(wù)。如,控制數(shù)字處理、處理圖像或視頻數(shù)據(jù),或者感應(yīng)和測量運動數(shù)據(jù)等。

2018-04-24 09:58:29 17393

17393 本文首先介紹了協(xié)處理器的相關(guān)概念,其次分析了驍龍835里是否有協(xié)處理器,最后闡述了驍龍835的性能參數(shù)。

2018-04-24 15:14:39 7034

7034 本文首先介紹了ARM處理器特點與主要模式,其次介紹了arm的協(xié)處理器有幾個,最后介紹了CP14和CP15系統(tǒng)控制協(xié)處理器。

2018-04-24 15:34:25 9690

9690 第2部分,共4部分 - 英特爾?至強融核?協(xié)處理器硬件和軟件架構(gòu)介紹

2018-10-30 06:14:00 4412

4412

第1部分,共4部分 - 英特爾?至強融合?協(xié)處理器硬件和軟件架構(gòu)介紹

2018-10-30 06:10:00 6058

6058 性能驗證-ON-Intel的Xeon的處理器和Xeon的PHI-協(xié)處理器簇

2018-11-07 06:36:00 4721

4721 此網(wǎng)絡(luò)研討會介紹了開發(fā)用于Windows *的英特爾?至強融核?協(xié)處理器的Fortran應(yīng)用程序的開發(fā)環(huán)境。

2018-11-06 06:37:00 3761

3761 該視頻將向開發(fā)人員介紹Xilinx和Avnet的新平臺,通過XilinxSpartan?-6 FPGA輕松提升TI OMAP或DSP處理器的性能。

2018-11-20 05:51:00 3442

3442 了解協(xié)處理的價值,Zynq-7000加速器一致性端口,使用協(xié)處理器加速器的方法以及協(xié)處理器設(shè)計實例的概述。

2018-11-30 06:15:00 4782

4782 近日,協(xié)鑫集成科技股份有限公司(以下簡稱“協(xié)鑫集成”)公布了關(guān)于投資半導(dǎo)體產(chǎn)業(yè)基金暨關(guān)聯(lián)交易的進展公告。

2018-12-24 14:08:52 3516

3516 ARM7TDMI處理器指令集使您可以通過協(xié)處理器來實現(xiàn)特殊的附加指令。

2020-07-20 14:43:14 3546

3546

集成了數(shù)據(jù)通信,定位服務(wù)和視頻娛樂的高端汽車信息娛樂系統(tǒng)需要高性能的可編程處理技術(shù),其最佳實現(xiàn)方法是在主流汽車信息通信系統(tǒng)構(gòu)架中集成FPGA協(xié)處理器。本文講述汽車娛樂系統(tǒng)的需求,討論主流系統(tǒng)構(gòu)架,以及FPGA協(xié)處理器是如何集成到軟硬件體系中,以滿足高性能處理、靈活性和降低成本的要求。

2020-07-24 15:25:00 1036

1036

IP核心平臺,可在FPGA和ASIC上的SoC環(huán)境中加速加密操作,其中包括了加速加密算法,增強篡改和入侵的檢測,增強數(shù)據(jù)和密鑰保護的安全性,增強內(nèi)存訪問和I/O。 SoC/FPGA市場正在迅速發(fā)展,通過將加密協(xié)處理器IP嵌入到相關(guān)產(chǎn)品中,使之具有更多明顯的優(yōu)勢。與軟件層相比,具有加密

2020-07-31 10:45:00 2805

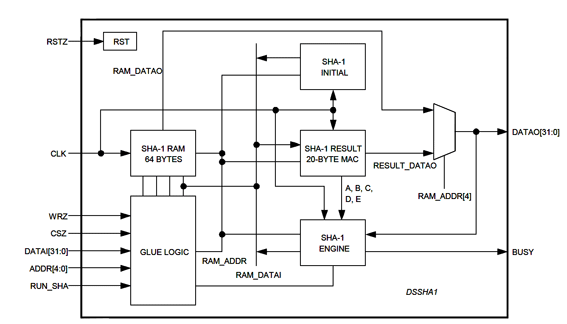

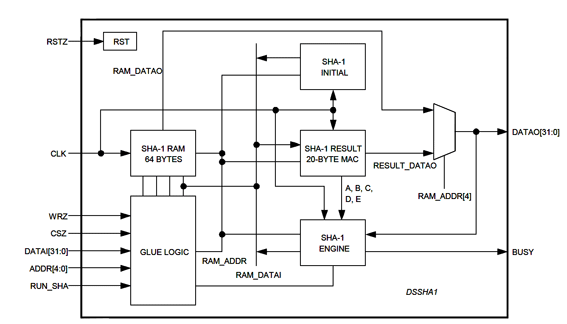

2805 本應(yīng)用筆記介紹了 DSSHA1 可合成 SHA-1 協(xié)處理器,它可以在專用集成電路 (ASIC) 或現(xiàn)場可編程門陣列 (FPGA) 中實現(xiàn),作為 DS2460 SHA-1 協(xié)處理器或基于微處理器的實現(xiàn)的替代方案.

2021-06-17 11:55:22 1965

1965

該文在闡述了灰度圖像順序形態(tài)變換的基礎(chǔ)上,介紹了順序形態(tài)變換硬件實現(xiàn)的圖像處理系統(tǒng).該系統(tǒng)采用DSP+FPGA的框架結(jié)構(gòu),利用FPGA的可重構(gòu)特性將其中一片FPGA作為協(xié)處理器可以實現(xiàn)不同的圖像處理

2021-04-01 11:21:46 8

8 處理器中。然后,協(xié)處理器可以有效地連接到處理器,產(chǎn)生“GHz”級的性能。 本文主要研究了代碼加速和代碼轉(zhuǎn)換到硬件協(xié)處理器的方法。我們還分析了通過一個涉及到基于輔助處理器單元(APU)的實際圖像顯示案例的基準(zhǔn)數(shù)據(jù)均衡決策的過

2021-09-28 10:38:04 4756

4756

通過Z-Wave OTA協(xié)處理器

2021-12-09 14:36:08 3

3 FPGA圖像處理應(yīng)用詳細(xì)介紹

2022-02-28 10:29:49 51

51 協(xié)處理器是一個處理單元,該處理單元與一個主處理單元一起使用來承擔(dān)通常由主處理單元執(zhí)行的運算。通常,協(xié)處理器功能在硬件中實現(xiàn)以替代幾種軟件指令。通過減少多種代碼指令為單一指令,以及在硬件中直接實現(xiàn)指令的方式,從而實現(xiàn)代碼加速。

2022-10-27 12:41:27 1286

1286 WOLA 濾波器組協(xié)處理器:介紹性概念和技術(shù)

2022-11-15 19:48:19 11

11 的主機處理器。本應(yīng)用筆記介紹了DSSHA1可合成SHA-1協(xié)處理器,該協(xié)處理器可在專用集成電路(ASIC)或現(xiàn)場可編程門陣列(FPGA)中實現(xiàn),作為DS2460 SHA-1協(xié)處理器或基于微處理器的替代方案。

2023-02-20 13:44:53 1507

1507

協(xié)程是一種輕量級的線程,它可以在單個線程中實現(xiàn)并發(fā)執(zhí)行。與線程不同,協(xié)程不需要操作系統(tǒng)的上下文切換,因此可以更高效地使用系統(tǒng)資源。Kotlin 協(xié)程是 Kotlin 語言的一項特性,它提供了一種簡單而強大的方式來處理異步任務(wù)。

2023-04-19 10:20:30 1530

1530 的主機處理器。本應(yīng)用筆記介紹了DSSHA1可合成SHA-1協(xié)處理器,該協(xié)處理器可在專用集成電路(ASIC)或現(xiàn)場可編程門陣列(FPGA)中實現(xiàn),作為DS2460 SHA-1協(xié)處理器或基于微處理器的替代方案。

2023-06-13 16:26:33 1573

1573

處理器中。然后,協(xié)處理器可以有效地連接到處理器,產(chǎn)生“GHz”級的性能。 本文主要研究了代碼加速和代碼轉(zhuǎn)換到硬件協(xié)處理器的方法。我們還分析了通過一個涉及到基于輔助處理器單元(APU)的實際圖像顯示案例的基準(zhǔn)數(shù)據(jù)均衡決策的過

2023-08-22 18:50:01 1460

1460 電子發(fā)燒友網(wǎng)站提供《使用TMS320C6416協(xié)處理器:Viterbi協(xié)處理器(VCP).pdf》資料免費下載

2024-10-21 09:36:00 0

0 電子發(fā)燒友網(wǎng)站提供《使用TMS320C6416協(xié)處理器:Turbo協(xié)處理器(TCP).pdf》資料免費下載

2024-10-23 10:16:19 0

0

電子發(fā)燒友App

電子發(fā)燒友App

評論