一,JESD204B應(yīng)用的優(yōu)缺點接觸過FPGA高速數(shù)據(jù)采集設(shè)計的朋友,應(yīng)該會聽過新術(shù)語“JESD204B”。這是一種新型的基于高速SERDES的ADC/DAC數(shù)據(jù)傳輸接口。隨著ADC/DAC的采樣

2019-12-04 10:11:26

,具有高速并串轉(zhuǎn)換的作用。2、使用JESD204B接口的原因a.不用再使用數(shù)據(jù)接口時鐘(時鐘嵌入在比特流中,利用恢復(fù)時鐘技術(shù)CDR)b.不用擔(dān)心信道偏移(信道對齊可修復(fù)此問題,RX端FIFO緩沖器)c.

2019-12-03 17:32:13

、LVDS高速接口等,FPGA需要實現(xiàn)相應(yīng)的關(guān)鍵技術(shù)以支持數(shù)據(jù)傳輸。

布線與布局 :

時鐘信號布線:FPGA和高速DAC的時鐘信號必須保證正常傳輸和同步,避免布線過長,注意信號阻抗匹配。

信號布局:在布線

2024-05-27 16:02:50

的是,FPGA可以采用IP內(nèi)核技術(shù),以通過繼承、共享或購買所需的知識產(chǎn)權(quán)內(nèi)核提高其開發(fā)進度。而利用EDA工具進行設(shè)計、綜合和驗證,則可加速設(shè)計過程,降低開發(fā)風(fēng)險,縮短了開發(fā)周期,效率高而且更能適應(yīng)市場。

2019-11-01 07:40:10

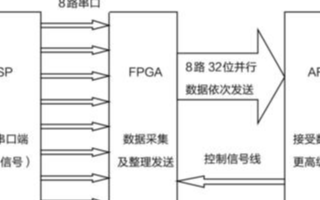

進行高速數(shù)據(jù)傳輸有幾種方案我知道可以用雙口RAM 或者協(xié)議的方式 但是不知道還有沒有其他的方式要求之間的通信速度要快 相互之間進行數(shù)據(jù)的交換其實就是FPGA把數(shù)據(jù)交給DSP進行處理 處理完了之后再有FPGA進行實時的圖像顯示而已

2012-08-06 10:56:57

系統(tǒng)的主要優(yōu)點討歸納如下:(1)頻譜利用率高,有利于提高系統(tǒng)容量。采用低速率的語音編碼技術(shù)、高效率的數(shù)字調(diào)制解調(diào)技術(shù)、先進的多址方式,以及語音激活與動態(tài)信道分配技術(shù)等,可以在不增加工作頻段的條件下增加

2018-02-27 09:21:22

錯誤的機制。通常,在物理層進行數(shù)據(jù)的錯誤檢出,采用抗干擾編碼。在數(shù)據(jù)鏈路層進行錯誤糾正,例如,采用幀檢驗序列對數(shù)據(jù)進行檢驗。產(chǎn)錯控制產(chǎn)生差錯的原因有以下幾方面的原因:1、噪聲。熱噪聲是由于分子運動

2011-07-08 11:03:10

運行的高速公路網(wǎng)絡(luò)一樣,為FPGA外部高速接口和內(nèi)部可編程邏輯的數(shù)據(jù)傳輸提供了超高帶寬(~27Tbps)。圖1Speedster 7t FPGA結(jié)構(gòu)圖NoC使用一系列高速的行和列網(wǎng)絡(luò)通路在整個FPGA

2020-05-12 08:00:00

了具體的匹配準則和算法流程;對車載終端與監(jiān)控中心交互數(shù)據(jù)的傳輸流程進行了詳細分析,設(shè)計了監(jiān)控中心數(shù)據(jù)庫,并根據(jù)通信協(xié)議,解析了具體的數(shù)據(jù)包實例;最后,在對高速公路GPS 車輛動態(tài)監(jiān)控技術(shù)研究的基礎(chǔ)上

2009-04-16 13:47:49

:對系統(tǒng)資源要求較多,工作效率沒有UDP高,且每條TCP連接只能進行點對點的傳遞,但是它的傳輸數(shù)據(jù)的可靠性高,無差錯,不丟失,不重復(fù),且按序到達。UDP:對系統(tǒng)資源要求相對較少,具有較好的實時...

2022-03-01 07:23:51

PCIE高速傳輸方案傳輸的帶寬利用率可達到90%以上,延遲可達到理論的最低延遲值。該方案已經(jīng)應(yīng)用到航天航空、雷達等領(lǐng)域。一、 高效率傳輸方案 該采集方案 Demo 基于 VC709 開發(fā)板

2021-05-19 08:58:02

各種編程語言調(diào)用。FPGA為網(wǎng)表文件,可以直接嵌入到FPGA工程中。FX3固件程序出廠時已經(jīng)固化到模塊當中,無須再進行編程。●提供高速、穩(wěn)定的數(shù)據(jù)傳輸示例。FPGA -> FIFO ->

2018-10-12 11:38:37

。FPGA為網(wǎng)表文件,可以直接嵌入到FPGA工程中。FX3固件程序出廠時已經(jīng)固化到模塊當中,無須再進行編程。●提供高速、穩(wěn)定的數(shù)據(jù)傳輸示例。FPGA -> FIFO -> FX3 ->

2018-10-15 10:04:55

。FPGA為網(wǎng)表文件,可以直接嵌入到FPGA工程中。FX3固件程序出廠時已經(jīng)固化到模塊當中,無須再進行編程。●提供高速、穩(wěn)定的數(shù)據(jù)傳輸示例。FPGA -> FIFO -> FX3 ->

2018-10-22 11:21:03

。FPGA為網(wǎng)表文件,可以直接嵌入到FPGA工程中。FX3固件程序出廠時已經(jīng)固化到模塊當中,無須再進行編程。●提供高速、穩(wěn)定的數(shù)據(jù)傳輸示例。FPGA -> FIFO -> FX3 ->

2019-01-22 14:17:09

親愛的社區(qū)成員,我正在實施XAPP861中推薦的8x過采樣和數(shù)據(jù)恢復(fù)單元(DRU),以便在Virtex-4 FPGA上進行異步串行數(shù)據(jù)恢復(fù)。我通過3米DVI電纜接收了160bbps的8b10b編碼流

2020-06-18 16:00:28

wireline高速數(shù)據(jù)傳輸的均衡技術(shù)

2020-12-23 06:07:55

,在數(shù)字頻率計這樣的高速運用中有很大的用武之地,因此今天學(xué)習(xí)一下如何利用FPGA進行收發(fā)數(shù)據(jù)。為了保證電子系統(tǒng)中的上位機、下位機正確通信傳輸數(shù)據(jù),我們需要為它們編寫通信協(xié)議。目前常用的通信協(xié)議有I2C

2017-07-12 13:03:36

現(xiàn)代先進的貼片機采用一系列先進的智能控制技術(shù),逐漸向高速度、高靈活性和無差錯貼裝發(fā)展。關(guān)于速度和靈活性我們將在后面的章節(jié)中詳細討論,這里只介紹幾種流行先進貼裝技術(shù)。 (1)智能供料器 傳統(tǒng)

2018-09-07 16:11:53

在用鼎陽示波器什么情況下需要自校正?自校正有多大作用,自校正后,精度能達到多少?

2010-08-13 10:21:13

如題,不知哪位有用過鼎陽的示波器,想請教下鼎陽的示波器在什么情況下需要進行自校正?自校正有多大作用,自校正后,精度能達到多少?我用的是SDS1102CNL

2013-01-08 09:03:37

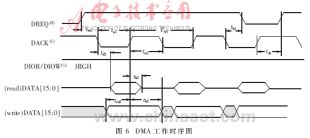

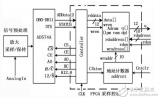

1 引言高速數(shù)據(jù)傳輸系統(tǒng)在通信系統(tǒng)、測試儀器等電子系統(tǒng)中有著廣泛應(yīng)用,人們對數(shù)據(jù)傳輸的處理速度、可靠性及實時性的要求越來越高。高速穩(wěn)定可靠的數(shù)據(jù)傳輸技術(shù),在高速數(shù)據(jù)采集系統(tǒng)中扮演著重要的角色,隨著數(shù)據(jù)傳輸

2018-08-09 14:18:42

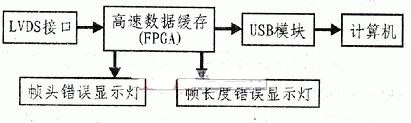

、聲納、圖像處理、語音識別、通信、瞬態(tài)信號測試等領(lǐng)域得到廣泛應(yīng)用。它的關(guān)鍵技術(shù)是高速ADC技術(shù)、高速數(shù)據(jù)緩沖存儲技術(shù)與傳輸技術(shù)。當大量的高速實時數(shù)據(jù)經(jīng)過模數(shù)轉(zhuǎn)換后,必須高速存儲,然后再讀回計算機進行處理。把高速海量的數(shù)據(jù)緩存下

2010-04-26 16:12:39

。因此,為了采集數(shù)據(jù)量大的圖像數(shù)據(jù),本文采用了具有較高傳輸速率的增強型并行口協(xié)議(EPP)和FPGA,實現(xiàn)對OV7620CMOS圖像傳感器進行高速數(shù)據(jù)采集,它最高速率可以達到2Mb/s。

2020-04-30 07:47:07

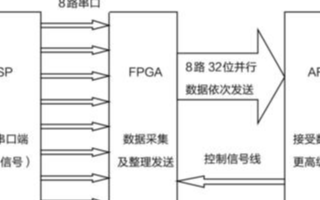

傳輸,因而只能做需求數(shù)據(jù)較少的測向工作,并不能做實時波束形成。為了克服這些困難,這里將測向數(shù)據(jù)和波束形成數(shù)據(jù)分開進行傳輸,采用LVDS技術(shù)解決多通道高速數(shù)據(jù)傳輸,選擇內(nèi)置高性能DSP內(nèi)核的高密度FPGA并行實現(xiàn)波束形成中的大量復(fù)乘運算。

2020-11-25 06:49:42

的出現(xiàn)使FPGA的功能更加強大,但隨之而來的是要求提高數(shù)據(jù)的傳輸速率,過去人們總是關(guān)心如何提高處理器運行速度,而現(xiàn)在關(guān)心的是怎樣才能更快地將數(shù)據(jù)從一個芯片傳輸到另一個芯片。可見,高速數(shù)據(jù)采集系統(tǒng)

2018-12-18 10:22:18

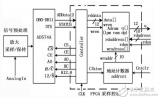

高速傳輸,但DSP價格過于昂貴。而利用FPGA和USB接口芯片結(jié)合的方案,具有功耗低、時鐘頻率高、速度快、效率高、組合形式靈活等特點,是單片機和DSP所無法比擬的。

2019-09-05 07:22:57

22.4Gbps(Kintex-7).2. 1對LVDS接收時鐘+16對LVDS接收數(shù)據(jù).本人可以提供FPGA源代碼.同時還可以在Xilinx評估板ML555/ML605/KC705上演示驗證.如有高速LVDS數(shù)據(jù)傳輸相關(guān)方面的技術(shù)合作,可聯(lián)系我。聯(lián)系方式:neteasy163z@163.com

2014-03-01 18:47:47

自頻調(diào)系統(tǒng)靜差;τ為接收目標回波的延時。將式(1)和(2)作相關(guān)處理后,可得:[/url]可見DSU利用A/D對發(fā)射脈沖樣本進行取樣,然后用該取樣值和回波信號進行相關(guān)或卷積來實現(xiàn)相位校正,達到消除隨機

2015-02-05 15:34:43

基于DSP在算法實現(xiàn)和調(diào)試方面更為方便[6]。因為中高端的FPGA支持軟CPU內(nèi)核(典型的如Nios),可以用高級語言(如C語言)進行非線性校正算法的編程和調(diào)試,所以我們采用基于FPGA的校正方案。數(shù)字

2018-07-30 18:09:06

SystemACE_CompactFlash外設(shè)以支持從CF卡配置FPGA;添加IP核opb_hwicap以支持嵌入式內(nèi)核通過ICAP讀取配置數(shù)據(jù)動態(tài)地配置FPGA。(2)EDK包含有軟件開發(fā)工具SDK,因此利用SDK

2015-02-05 15:31:50

隨著現(xiàn)代通信技術(shù)的迅速發(fā)展,信號的調(diào)制方式向多樣化發(fā)展,解淵技術(shù)也隨之不斷向前發(fā)展。為了對高速大帶寬的信號進行實時解調(diào),現(xiàn)在很多的解調(diào)關(guān)鍵算法都是在高速硬件上用可編程邏輯器件(FPGA)實觀,利用

2019-09-19 07:29:47

。它定義了8種透明業(yè)務(wù)承載者,所提供的比特率范圍為9.6kbit/s~64kbit/s。非透明業(yè)務(wù)承載者用無線鏈路協(xié)議來保證無差錯數(shù)據(jù)傳輸。對于這種情況,有8種承載者,所提供的比特率為4.8kbit/s

2009-11-13 21:30:43

高速連續(xù)數(shù)據(jù)采集系統(tǒng)的背景及功能是什么?如何利用FPGA實現(xiàn)高速連續(xù)數(shù)據(jù)采集系統(tǒng)設(shè)計?FPGA在高速連續(xù)數(shù)據(jù)采集系統(tǒng)中的應(yīng)用有哪些?

2021-04-08 06:19:37

在無線電接收機系統(tǒng)中,由于會受到發(fā)射機運動、接收機運動和標準頻率隨時間動態(tài)變化等因素的影響,其接收機接收信號往往會發(fā)生頻率偏移,因而需要進行頻偏校正。在擴頻通信系統(tǒng)中,頻偏校正電路能消除中頻偏移對接收機擴頻碼的捕獲以及數(shù)據(jù)解調(diào)性能的影響,從而提高接收機的性能。

2019-11-08 06:06:58

隨著現(xiàn)場可編程門陣列(FPGA)已發(fā)展成為真正的可編程系統(tǒng)級芯片,利用這些芯片設(shè)計印制電路板(PCB)的任務(wù)變得愈加復(fù)雜。目前動輒數(shù)百萬門的電路密度和6Gbps以上的收發(fā)器數(shù)據(jù)傳輸率及其它考慮事項

2019-08-20 07:33:53

本文結(jié)合實際系統(tǒng)中的前端圖像處理和圖像數(shù)據(jù)傳輸的需要,充分利用ARM的靈活性和FPGA的并行性的特點,設(shè)計了一種基于ARM+FPGA的高速圖像數(shù)據(jù)采集傳輸系統(tǒng)。

2021-06-02 06:18:50

再利用FET5718核心板控制超高速雙通道ADC進行數(shù)據(jù)采集,并實現(xiàn)動態(tài)波形繪制顯示,硬件設(shè)計需要如何進行資源分配,可以達到顯示不丟失數(shù)據(jù)的性能. ADC 為24bit 采樣率 為256K~1Mhz需要提供高速同步時鐘獲取數(shù)據(jù).硬件設(shè)計可以實現(xiàn)嗎?

2022-11-21 12:10:01

的發(fā)生。醫(yī)囑信息差錯能夠在醫(yī)院信息系統(tǒng)中反映出來,其中大部分差錯可在護士執(zhí)行醫(yī)囑之前發(fā)現(xiàn)和糾正。所以怎么利用利用RFID技術(shù)減少醫(yī)療差錯,這個問題急需解決。

2019-08-07 07:16:59

本文設(shè)計的基于FPGA和USB的高速數(shù)據(jù)傳輸、記錄系統(tǒng)不但具有體積小、功耗低、成本低、使用靈活方便、硬件電路簡單、可在線更新等特點;而且還充分利用了微機的資源,因而易開發(fā)且擴展性好。

2021-04-30 06:50:49

對更高密度和更快速度配置存儲器的需求。現(xiàn)代FPGA在配置期間需要加載多達128MB的數(shù)據(jù)。這些高密度配置比特流需要更長的時間才能從NOR閃存器件傳輸到FPGA。配置接口不僅針對讀取吞吐量進行了優(yōu)化,還專注

2021-05-26 07:00:00

隨著現(xiàn)代通信技術(shù)的迅速發(fā)展,信號的調(diào)制方式向多樣化發(fā)展,解淵技術(shù)也隨之不斷向前發(fā)展。為了對高速大帶寬的信號進行實時解調(diào),現(xiàn)在很多的解調(diào)關(guān)鍵算法都是在高速硬件上用可編程邏輯器件(FPGA)實觀,利用

2019-09-05 07:08:02

差等缺點,難以滿足對高速寬帶信號采集和處理的要求。FPGA具有時鐘頻率高、速度快、采集實時性高、控制靈活等特點,與A/D轉(zhuǎn)換器等外圍電路結(jié)合,更適于高速數(shù)字信號處理。光纖傳輸與電氣傳輸相比,具有傳輸

2019-09-02 06:01:52

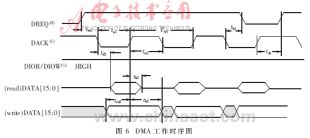

本文介紹了基于Xilinx Virtex-6 FPGA的高速串行數(shù)據(jù)傳輸系統(tǒng)的設(shè)計與實現(xiàn),系統(tǒng)包含AXI DMA和GTX串行收發(fā)器,系統(tǒng)增加了流量控制機制來保證高速數(shù)據(jù)傳輸的可靠性。最后進行了仿真測試,測試結(jié)果顯示系統(tǒng)可以高速可靠地傳輸數(shù)據(jù)。

2021-05-25 06:45:36

如何采用具有較高傳輸速率的增強型并行口協(xié)議(EPP)和FPGA,實現(xiàn)對OV7620CMOS圖像傳感器進行高速數(shù)據(jù)采集,讓它的最高速率可以達到2Mb/s?

2021-04-12 07:08:41

綜合考慮到圖像采集系統(tǒng)所要求的實時性,可靠性,以及FPGA在數(shù)字電路的設(shè)計中的優(yōu)勢,為此本文討論如何利用FPGA設(shè)計基于LVDS的圖像數(shù)據(jù)采集傳輸系統(tǒng)?

2021-04-08 06:48:28

通常我們使用USB作為通道,在數(shù)據(jù)采集項目中將大量的高速數(shù)據(jù)從FPGA傳輸到PC。我正在考慮使用JTAG作為數(shù)據(jù)傳輸的方式。你有這樣的經(jīng)歷嗎?有可能嗎?以上來自于谷歌翻譯以下為原文Usually

2019-02-13 13:11:52

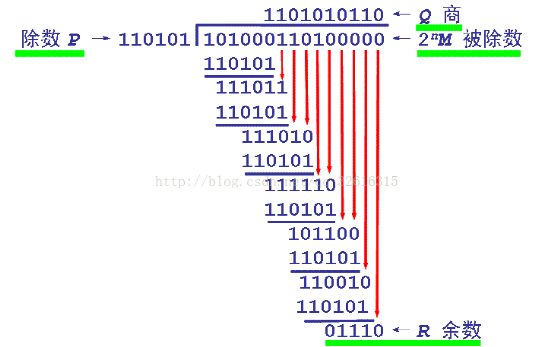

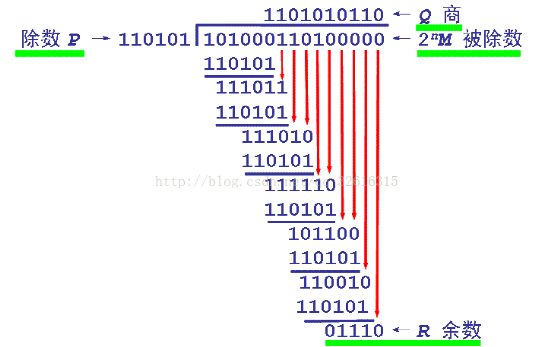

2.6 差錯控制與校驗2.6.1 差錯控制方法2.6.2 常用的差錯控制編碼2.6.1 差錯控制方法 差錯控制編碼就是對網(wǎng)絡(luò)中傳輸的數(shù)字信號進行抗干擾編

2009-06-27 21:47:39 0

0 本文介紹了一種應(yīng)用FPGA 器件完成高速數(shù)字傳輸的方法,利用這種方法實現(xiàn)無線收發(fā)芯片nRF2401A 的高速數(shù)據(jù)接口。為進一步提高信息的傳輸速率,這里還對待傳輸的數(shù)據(jù)進行了壓縮處

2009-08-04 09:16:20 9

9 兩點校正算法是一種行之有效的紅外圖像非均勻校正方法.本文對兩點校正算法進行了分析,并推導(dǎo)出了該算法的定點表示形式.利用FPGA在硬件上實現(xiàn)了該算法,內(nèi)部采用流水線技術(shù),

2009-08-15 11:37:59 18

18 DVI[1]接口標準作為新一代的數(shù)字顯示技術(shù)通訊標準,以全數(shù)字化的數(shù)據(jù)碼流在傳輸信道上傳輸,本文針對DVI 接口標準提出了一種基于FPGA 的高速實時的數(shù)據(jù)傳輸方案。方案中重

2009-09-22 10:12:34 15

15 本文設(shè)計了一種以 FPGA 為數(shù)據(jù)壓縮和數(shù)據(jù)緩存單元的高速數(shù)據(jù)采集系統(tǒng),其主要特點是對高速采集的數(shù)據(jù)進行實時壓縮,再將壓縮后的數(shù)據(jù)進行緩沖存儲。該設(shè)計利用數(shù)據(jù)比較模

2009-11-30 15:32:36 20

20 隨著技術(shù)的發(fā)展, 往往需要在不同的系統(tǒng)之間實現(xiàn)高速通信, 現(xiàn)介紹了一種基于LVDS的高速數(shù)據(jù)傳輸的接口LinkPort , 給出了在Xilinx 的FPGA 中實現(xiàn)該接口的原理以及關(guān)鍵設(shè)計, 并成功

2010-09-22 08:26:14 98

98 摘 要:介紹了FPGA最新一代器件Virtex25上的高速串行收發(fā)器RocketIO。基于ML505開發(fā)平臺構(gòu)建了一個高速串行數(shù)據(jù)傳輸系統(tǒng),重點說明了該系統(tǒng)采用RocketIO實現(xiàn)1. 25Gbp s高速串行傳輸的設(shè)

2010-09-22 08:41:18 44

44 §物理層:透明的傳輸比特流,硬件的

§接口。

§數(shù)據(jù)鏈路層:無差錯的傳輸幀。

§網(wǎng)絡(luò)層:路由選擇,包。

§傳輸層:保證端到端的

2010-10-25 16:56:06 34

34 為解決目前高速信號處理中的數(shù)據(jù)傳輸速度瓶頸以及傳輸距離的問題,設(shè)計并實現(xiàn)了一種基于FPGA 的高速數(shù)據(jù)傳輸系統(tǒng),本系統(tǒng)借助Altera Cyclone III FPGA 的LVDS I/O 通道產(chǎn)生LVDS 信號,穩(wěn)

2010-11-02 15:27:43 42

42

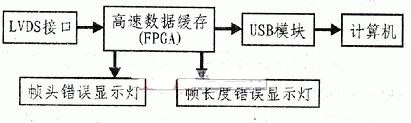

摘要:提出了一種基于FPGA和USB的高速數(shù)據(jù)傳輸、記錄及顯示系統(tǒng)的設(shè)計方案,并對其中的低電壓差分信號(LVDS

2006-04-16 21:36:33 750

750

基于USB2.0與FPGA技術(shù)的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計

基于USB2.0與FPGA技術(shù)的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計

近年來筆記本電腦迅速普及和更新,其中大部分已經(jīng)

2009-04-22 19:56:15 1960

1960

差錯控制編碼,差錯控制編碼工作原理是什么

差錯控制編碼也稱為糾錯編碼。在實際信道上傳輸數(shù)字信號時,由于信道傳輸特性不理想

2010-03-17 17:37:33 8882

8882 差錯校驗,差錯校驗是什么意思

差錯檢驗的原因:

數(shù)據(jù)在傳輸過程中,會受到來自信道內(nèi)外的干擾與噪聲,從而產(chǎn)生差錯

差錯檢驗的方法:

2010-03-18 14:56:47 2393

2393 提出了一種簡單、快速的正交頻分復(fù)用(OFDM)系統(tǒng)的自適應(yīng)調(diào)制算法。該算法在子信道分配已經(jīng)完成的前提下,通過信道參數(shù)的估計,動態(tài)地分配子信道上的比特和功率, 使得發(fā)送的每個符號的總比特數(shù)最大,從而提高信道的利用率及數(shù)據(jù)傳輸速率,滿足了高速遙測系

2011-02-12 15:13:39 21

21 信號編碼技術(shù) 數(shù)據(jù)、信號和傳輸的模擬與數(shù)字之分 信號編碼準則 數(shù)字數(shù)據(jù)與模擬信號 模擬數(shù)據(jù)與模擬信號 模擬數(shù)據(jù)與數(shù)字信號 擴頻技術(shù) 差錯控制技術(shù)

2011-03-31 12:19:38 38

38 該設(shè)計系統(tǒng)采用高速AD轉(zhuǎn)換,以靈活、高效性價比FPGA芯片-EP1C6為平臺,利用USB傳輸,實現(xiàn)了基于Verilog 的聲幅測井系統(tǒng)。最終,在上位機得到的聲幅測井曲線用來判斷固井質(zhì)量。在水泥膠結(jié)良

2011-12-22 17:26:54 35

35 根據(jù)日本媒體《日刊工業(yè)新聞》報道,日本三菱電機公司開發(fā)出利用電網(wǎng)金屬線纜實現(xiàn)每秒2兆比特(Mbit/s)高速大容量數(shù)據(jù)通信技術(shù)。利用此技術(shù),用戶可通過市電電網(wǎng)實現(xiàn)高速數(shù)據(jù)通信。

2013-07-17 14:24:38 1879

1879 利用FPGA和多通道光模塊組合長距離傳送高速數(shù)據(jù)

2016-01-06 16:59:09 0

0 一種基于FPGA的以太網(wǎng)高速傳輸平臺,采用DM9000和FPGA芯片,實現(xiàn)100M以太網(wǎng)數(shù)據(jù)傳輸

2016-02-25 14:45:56 17

17 利用FPGA和多通道光模塊組合長距離傳送高速數(shù)據(jù)

2016-05-09 11:42:36 0

0 DSP與FPGA高速的數(shù)據(jù)傳輸有三種常用接口方式: EMIF, HPI 和 McBSP 方式。而采用 EMIF 接口方式, 利用 FPGA ( 現(xiàn)場可編程邏輯門陣列) 設(shè)計 FIFO的接口電路,即可實現(xiàn)高速互聯(lián)。

2017-02-11 14:16:10 2950

2950

(Xilinx)FPGA中LVDS差分高速傳輸的實現(xiàn)

2017-03-01 13:12:04 66

66 在變電站中,為了保證現(xiàn)場環(huán)境、設(shè)備外部狀況的全面監(jiān)測,需要安裝大量的攝像頭進行晝夜監(jiān)控,攝像頭采集的視頻數(shù)據(jù)量比其他的環(huán)境狀態(tài)數(shù)據(jù)、設(shè)備狀態(tài)數(shù)據(jù)量要大得多。數(shù)據(jù)信息的快速傳輸是站內(nèi)狀態(tài)實時監(jiān)控實現(xiàn)

2017-11-15 16:27:42 14

14 在各種不同的場合中,人們需要將大批數(shù)據(jù)從一個設(shè)備無差錯地傳輸到另一個設(shè)備上。對于設(shè)備間距離較近的場合,可以選擇PCIE(典型距離是15~30cm)或者USB(最長傳輸距離5m)等接口。而對于距離較遠

2017-11-22 09:04:01 5791

5791 數(shù)字信號在傳輸過程中受到干擾的影響,使信號波形變壞,發(fā)生誤碼,可以采用一些方法解決。同時設(shè)計系統(tǒng)時,還要合理地選擇調(diào)制、解調(diào)、發(fā)送功率等因素,采用上述措施仍難以滿足性能要求,就要采用差錯控制措施了

2017-11-24 09:23:54 13

13 基于RBF網(wǎng)絡(luò)辨識的自校正控制,自校正控制有兩種結(jié)構(gòu):直接型與間接型。直接型自校正控制也稱直接逆動態(tài)控制,是前饋控制。間接自校正控制是一種由辨識器將對象參數(shù)進行在線估計,用調(diào)節(jié)器(或控制器)實現(xiàn)參數(shù)

2017-12-06 15:09:02 0

0 利用AD574A設(shè)計基于FPGA的高速數(shù)據(jù)采集系統(tǒng),系統(tǒng)包含內(nèi)嵌雙口,在FPGA內(nèi)部實現(xiàn)的RAM用于寫入操作;地址計數(shù)器,用于提供存儲地址保存采集數(shù)據(jù)。具備高采樣精度、高集成度,并且速度快、靈活性強、可靠性高,易于升級與擴展。

2017-12-18 17:37:20 9294

9294

許多 FPGA 設(shè)計都采用高速存儲器接口,可能調(diào)試比較困難,不過只要采用正確的方法就能成功進行調(diào)試。 現(xiàn)代 FPGA 通常連接高速 SRAM 和 SDRAM 存儲器 。要確保這種器件無差錯運行,調(diào)試

2018-01-12 11:48:44 1662

1662

物理層,指的是電信號的傳遞方式,透明的傳輸比特流。 鏈路層,在兩個相鄰結(jié)點間的線路上無差錯地傳送以幀為單位的數(shù)據(jù)。網(wǎng)絡(luò)層,負責(zé)為分組交換網(wǎng)上的不同主機提供通信,數(shù)據(jù)傳送的單位是分組或包。傳輸層,負責(zé)

2018-02-03 10:24:42 13044

13044

整個系統(tǒng)主要由低電壓差分信號(LVDS)接口電路、基于FPGA的高速數(shù)據(jù)緩存、判斷數(shù)據(jù)錯誤模塊、USB傳輸模塊和計算機組成,其系統(tǒng)結(jié)構(gòu)框圖如圖1所示。當?shù)碗妷翰罘中盘柦涌陔娐钒呀邮盏睦走_數(shù)據(jù)形成分機數(shù)據(jù)送入FPGA緩存后,該信息便可通過USB接口進行傳輸、記錄并在計算機上顯示。

2019-05-16 08:14:00 4530

4530

為提高處理能力,設(shè)計了2 ×2并行流水結(jié)構(gòu)的FPGA矩陣并作為處理核心用于高速數(shù)據(jù)采集與控制。在分析了多片FPGA的同步驅(qū)動原理以及協(xié)作模型的基礎(chǔ)上,綜合利用雙時鐘沿觸發(fā)傳輸、資源重復(fù)與時間重疊技術(shù)

2018-11-07 10:46:17 10

10 數(shù)據(jù)鏈路層在物理層提供服務(wù)的基礎(chǔ)上向網(wǎng)絡(luò)層提供服務(wù),其主要作用是加強物理層傳輸原始比特流的功能,將物理層提供的可能出錯的物理連接改造成為邏輯上無差錯的數(shù)據(jù)鏈路,使之對網(wǎng)絡(luò)層表現(xiàn)為一條無差錯的鏈路。

2019-02-21 16:49:08 15126

15126 隨著集成電路技術(shù)的發(fā)展,FPGA和DSP以及ARM以其體積小、速度快、功耗低、設(shè)計靈活、利于系統(tǒng)集成、擴展升級等優(yōu)點,被廣泛地應(yīng)用于高速數(shù)字信號傳輸及數(shù)據(jù)處理,以DSP+FPGA+ARM的架構(gòu)組成滿足實時性要求的高速數(shù)字處理系統(tǒng)已成為一種趨勢,本文主要研究FPGA在高速多路數(shù)據(jù)傳輸中的應(yīng)用。

2021-04-24 09:04:49 7109

7109

點擊上方 藍字 關(guān)注我們 1.概述 隨著圖像處理技術(shù)的快速發(fā)展,圖像采集處理系統(tǒng)在提高工業(yè)生產(chǎn)自動化程度中的應(yīng)用越來越廣泛。本文結(jié)合實際系統(tǒng)中的前端圖像處理和圖像數(shù)據(jù)傳輸的需要,充分利用ARM

2023-09-27 10:45:02 2692

2692 、實時性低、傳輸速度慢、通用性差等缺點,難以滿足對高速寬帶信號采集和處理的要求。FPGA具有時鐘頻率高、速度快、采集實時性高、控制靈活等特點,與A/D轉(zhuǎn)換器等外圍電路結(jié)合,更適于高速數(shù)字信號處理。光纖傳輸與電氣傳輸相比,具

2023-10-18 16:35:01 2971

2971 在數(shù)據(jù)傳輸過程中,很難實現(xiàn)無差錯傳輸。差錯傳輸導(dǎo)致接收方收到的數(shù)據(jù)發(fā)生錯誤。為盡量提高接收數(shù)據(jù)的正確率,在接收數(shù)據(jù)之前需要對數(shù)據(jù)進行差錯檢測。

2023-11-03 15:49:15 10501

10501

電子發(fā)燒友App

電子發(fā)燒友App

評論