開發(fā)方面的能力,每一個(gè)章節(jié)中都有針對(duì)性的代碼書寫以及代碼的講解,可作為讀者參考。 第一章:模塊書寫 Verilog HDL 語言的基本語法與 C語言相似,因此與 VHDL 相比較更容易上手。本章將會(huì)在實(shí)際小項(xiàng)目的基礎(chǔ)上,以 Verilog HDL 語言為主, 教讀者怎么更方便、更高效的

2020-11-13 16:02:12 4676

4676

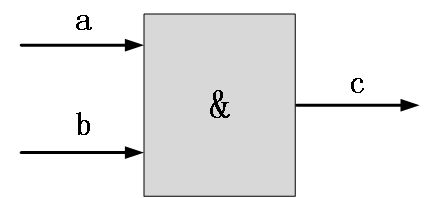

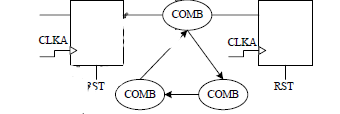

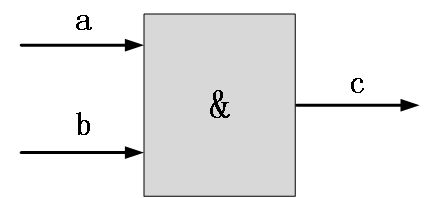

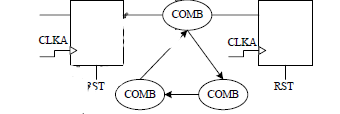

一、邏輯設(shè)計(jì) (1)組合邏輯設(shè)計(jì) 下面是一些用Verilog進(jìn)行組合邏輯設(shè)計(jì)時(shí)的一些注意事項(xiàng): ①組合邏輯可以得到兩種常用的RTL 級(jí)描述方式。第一種是always 模塊的觸發(fā)事件為電平敏感信號(hào)列表

2020-11-23 13:05:17 3923

3923

優(yōu)秀的 Verilog/FPGA開源項(xiàng)目介紹(三十四)- PDM音頻接口設(shè)計(jì)及信號(hào)處理 ? 緒論 今天介紹幾個(gè)與PDM接口相關(guān)的開源項(xiàng)目。 FPGA使用Delta-sigma ADC實(shí)現(xiàn)PDM音頻

2022-10-17 09:10:33 4424

4424 可綜合的語法是指硬件能夠?qū)崿F(xiàn)的一些語法,這些語法能夠被EDA工具支持,能夠通過編譯最終生成用于燒錄到FPGA器件中的配置數(shù)據(jù)流。

2023-07-23 12:25:10 2600

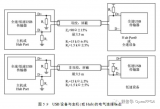

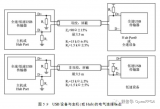

2600 本文介紹一個(gè)FPGA常用模塊:SRIO(Serial RapidIO)。SRIO協(xié)議是一種高速串行通信協(xié)議,在我參與的項(xiàng)目中主要是用于FPGA和DSP之間的高速通信。有關(guān)SRIO協(xié)議的詳細(xì)介紹網(wǎng)上有很多,本文主要簡(jiǎn)單介紹一下SRIO IP核的使用和本工程的源代碼結(jié)構(gòu)。

2023-12-12 09:19:08 3688

3688

本篇將詳細(xì)介紹如何利用Verilog HDL在FPGA上實(shí)現(xiàn)SRAM的讀寫測(cè)試。SRAM是一種非易失性存儲(chǔ)器,具有高速讀取和寫入的特點(diǎn)。在FPGA中實(shí)現(xiàn)SRAM讀寫測(cè)試,包括設(shè)計(jì)SRAM接口模塊

2025-10-22 17:21:38 4118

4118

FPGA、CPLD常用protel庫FPGA&CPLD_LIB.ddb

2012-08-11 10:32:00

商店的IP核庫中索取組件進(jìn)行配置,最后像搭積木一樣完成一個(gè)項(xiàng)目,或者整個(gè)設(shè)計(jì)都不需要見到一句代碼。當(dāng)然了,未來什么情況都有可能發(fā)生,但是底層的代碼邏輯編寫方式無論如何還是有其生存空間的,畢竟一個(gè)個(gè)IP

2015-01-29 09:20:41

可以了解目前最流行的Verilog HDL語言的基本語法,掌握Verilog HDL語言中最常用的基本語法。通過本節(jié)課程學(xué)習(xí),學(xué)員可以設(shè)計(jì)一些簡(jiǎn)單的FPGA程序,掌握組合邏輯和時(shí)序邏輯電路的設(shè)計(jì)方法

2014-11-30 17:38:06

。筆者基于實(shí)際項(xiàng)目中所涉及到的技術(shù)點(diǎn),一步一步指導(dǎo)初學(xué)者學(xué)會(huì)FPGA設(shè)計(jì),要想學(xué)會(huì)FPGA,必須經(jīng)歷一下幾個(gè)關(guān)鍵點(diǎn):1:對(duì)一個(gè)中等規(guī)模的模塊(500-1000行代碼)必須敢于下手,在綜合的過程中

2014-12-12 09:38:19

語法,這些語法能夠被EDA工具所支持,能夠通過編譯最終生成用于燒錄到FPGA器件中的配置數(shù)據(jù)流。無論是Verilog語言還是VHDL語言,可綜合的子集都很小。但是如何用好這些語法,什么樣的代碼風(fēng)格

2015-06-12 10:59:24

的邏輯電路。模塊四 FPGA設(shè)計(jì)常用IP模塊使用[size=12.0000pt]FPGA設(shè)計(jì)常用IP模塊使用課程主要內(nèi)容為FPGA設(shè)計(jì)中常用IP模塊的使用(單/雙口RAM、DPRAM、FIFO、ROM及串行

2015-09-29 16:33:54

的邏輯電路。模塊四 FPGA設(shè)計(jì)常用IP模塊使用[size=12.0000pt]FPGA設(shè)計(jì)常用IP模塊使用課程主要內(nèi)容為FPGA設(shè)計(jì)中常用IP模塊的使用(單/雙口RAM、DPRAM、FIFO、ROM及串行

2015-09-30 10:36:41

處理器的數(shù)字鐘設(shè)計(jì) 第9章 FPGA系統(tǒng)設(shè)計(jì)原則和技巧 9.1 FPGA系統(tǒng)設(shè)計(jì)的3個(gè)基本原則 9.2 FPGA系統(tǒng)設(shè)計(jì)的3種常用技巧 9.3 FPGA系統(tǒng)設(shè)計(jì)的3種常用IP模塊 第10章 利用

2012-02-09 15:45:32

FPGA的IP軟核使用技巧主要包括以下幾個(gè)方面:

理解IP軟核的概念和特性 :

IP軟核是指用硬件描述語言(如VHDL或Verilog)描述的功能塊,但并不涉及具體的電路實(shí)現(xiàn)細(xì)節(jié)。它通常只經(jīng)過功能

2024-05-27 16:13:24

apex20ke_atoms.v編譯到其中。2:在圖形界面中的Load Design對(duì)話框中裝入仿真設(shè)計(jì)時(shí),在Verilog 標(biāo)簽下指定預(yù)編譯庫的完整路徑。(見下圖)邏輯綜合目前可用的FPGA綜合工具

2020-05-15 07:00:00

FPGA系統(tǒng)設(shè)計(jì)原則和技巧之:FPGA系統(tǒng)設(shè)計(jì)的3種常用IP模塊.pdf(1012.86 KB)

2019-04-24 13:33:04

語言(Verilog HDL)是FPGA工程師的基本要求。通過本節(jié)課程的學(xué)習(xí),學(xué)員可以了解目前最流行的Verilog HDL語言的基本語法,掌握Verilog HDL語言中最常用的基本語法。通過本節(jié)課程學(xué)習(xí),學(xué)員可以

2014-04-23 15:28:29

1. 目的本規(guī)范的目的是提高書寫代碼的可讀性、可修改性、可重用性,優(yōu)化代碼綜合和仿真的結(jié)果,指導(dǎo)設(shè)計(jì)工程師使用VerilogHDL規(guī)范代碼和優(yōu)化電路,規(guī)范化可編程技術(shù)部的FPGA設(shè)計(jì)輸入,從而做到

2017-12-08 14:36:30

關(guān)鍵字:Altera 、FPGA、軟硬件協(xié)調(diào)設(shè)計(jì)(Verilog & C)、CPU、總線、外設(shè)FPGA硬件結(jié)構(gòu)知識(shí)Verilog HDL語言編程基礎(chǔ)FPGA常用開發(fā)工具 SOPC硬件系統(tǒng)開發(fā)SOPC軟件系統(tǒng)開發(fā)Avalon總線規(guī)范Nios II外設(shè)及其編程 七段數(shù)碼管時(shí)鐘...

2021-12-22 08:06:06

Verilog可綜合子集

2013-04-01 12:44:46

這里在網(wǎng)上找到一個(gè)fpga/cpld常用protel庫,傳上來給大家一起分享,好動(dòng)西就是要大家一起,[hide][/hide]

2012-01-09 10:57:07

語句在用綜合工具綜合時(shí)將被忽略或者報(bào)錯(cuò)。作為設(shè)計(jì)者,應(yīng)該對(duì)可綜合模型的結(jié)構(gòu)有所了解。 雖然不同的綜合工具對(duì)Verilog HDL語法結(jié)構(gòu)的支持不盡相同,但Verilog HDL中某些典型的結(jié)構(gòu)是很

2012-10-20 08:10:13

1,在一個(gè)verilog程序里,如果循環(huán)是一個(gè)循環(huán)次數(shù)不可定的循環(huán),那么它能被綜合工具綜合嗎2,如果程序里有always @(clock)里面又嵌套了@(clock)這樣的控制事件,這個(gè)能被綜合嗎

2015-02-03 15:29:11

,若不是,則只能用于仿真),while, 建立可綜合模型的原則 要保證Verilog HDL賦值語句的可綜合性,在建模時(shí)應(yīng)注意以下要點(diǎn): (1)不使用initial。 (2)不使用#10。 (3)不使

2015-01-05 19:42:44

的編程風(fēng)格SYSTEM VERILOG是VERILOG的一種延伸15.IP核的應(yīng)用:軟核soft core: 功能經(jīng)過驗(yàn)證的、可綜合的、實(shí)現(xiàn)后門數(shù)在5K以上的HDL代碼固核firm core: 功能經(jīng)過

2012-01-12 15:15:21

可綜合的Verilog語法和語義(劍橋大學(xué),影印)

2012-08-06 13:03:57

可綜合的VerilogHDL設(shè)計(jì)實(shí)例在前面七章里我們已經(jīng)學(xué)習(xí)了VerilogHDL的基本語法、簡(jiǎn)單組合邏輯和簡(jiǎn)單時(shí)序邏輯模塊的編寫、Top-Down設(shè)計(jì)方法、還學(xué)習(xí)了可綜合風(fēng)格的有限狀態(tài)機(jī)

2009-11-23 16:01:33

請(qǐng)問開源FPGA項(xiàng)目有哪些?

2023-12-26 12:09:06

,都有Xilinx公司自己寫好的可綜合的模塊,想請(qǐng)教一下為什么要分成這樣兩項(xiàng)?它們里面的模塊有區(qū)別嗎?2、上述談到的可綜合模塊和ISE 自帶的IP core又有什么區(qū)別呢?

2013-09-28 18:17:54

,都有Xilinx公司自己寫好的可綜合的模塊,想請(qǐng)教一下為什么要分成這樣兩項(xiàng)?它們里面的模塊有區(qū)別嗎?2、上述談到的可綜合模塊和ISE 自帶的IP core又有什么區(qū)別呢?

2013-09-28 18:20:29

7.2設(shè)計(jì)入門(視頻)第8講:NIOSII 7.2 設(shè)計(jì)入門(視頻)第9講:FPGA系統(tǒng)設(shè)計(jì)技巧-乒乓操作(視頻)第10講:FPGA設(shè)計(jì)常用IP核-鎖相環(huán)(視頻)地址:http

2009-03-26 16:37:40

:從零開始設(shè)計(jì)FPGA最小系統(tǒng)一: 核心電路(PDF、視頻)第3講:從零開始設(shè)計(jì)FPGA最小系統(tǒng)二: 外圍電路(PDF、視頻)第4講:Verilog HDL語法一:常用語句(視頻)第5講

2009-03-09 22:56:25

方式;固核則通常介于上面兩者之間,它已經(jīng)通過功能驗(yàn)證、時(shí)序分析等過程,設(shè)計(jì)人員可以以邏輯門級(jí)網(wǎng)表的形式獲取。FPGA的開發(fā)方式分為三種,分別是:原理圖、Verilog HDL以及IP核。其中原理圖方式

2016-12-22 23:37:00

II、ISE等一種以上開發(fā)工具進(jìn)行綜合布局布線,熟悉顯示行業(yè)常用的相關(guān)接口;能獨(dú)立承擔(dān)硬件FPGA設(shè)計(jì)項(xiàng)目,按照項(xiàng)目計(jì)劃要求完成任務(wù),能夠獨(dú)立進(jìn)行FPGA需求分析、芯片評(píng)估、器件選型,并完成相關(guān)硬件系統(tǒng)

2017-06-29 13:47:39

的 Verilog/FPGA開源項(xiàng)目》內(nèi)容介紹更加詳細(xì),包括但不限于綜合、上板測(cè)試等。兩者相輔相成,互補(bǔ)互充~

這幾年DPU的概念越來越火,有和CPU、GPU并駕齊驅(qū)的勢(shì)頭,通俗的講DPU分擔(dān)的工作

2023-11-01 16:27:44

XST支持哪些語言?VHDL, Verilog-2002, 以及Mixed Language of VHDL and Verilog。所支持的可綜合的VHDL和Verilog的子集可以查看XST

2018-08-08 10:31:27

的基本要求。通過本節(jié)課程的學(xué)習(xí),學(xué)員可以了解目前最流行的Verilog HDL語言的基本語法,掌握Verilog HDL語言中最常用的基本語法。通過本節(jié)課程學(xué)習(xí),學(xué)員可以設(shè)計(jì)一些簡(jiǎn)單的FPGA程序

2018-09-19 11:34:03

,是指硬件能夠?qū)崿F(xiàn)的一些語法,這些語法能夠被EDA工具所支持,能夠通過編譯最終生成用于燒錄到FPGA器件中的配置數(shù)據(jù)流。無論是Verilog語言還是VHDL語言,可綜合的子集都很小。但是如何用好這些語法

2017-12-06 19:50:25

`勇敢的芯伴你玩轉(zhuǎn)Altera FPGA連載33:可綜合的語法子集4特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1i5LMUUD 連續(xù)賦值

2017-12-19 21:36:24

工程師的基本要求。通過本節(jié)課程的學(xué)習(xí),學(xué)員可以了解目前最流行的Verilog HDL語言的基本語法,掌握Verilog HDL語言中最常用的基本語法。通過本節(jié)課程學(xué)習(xí),學(xué)員可以設(shè)計(jì)一些簡(jiǎn)單的FPGA

2015-10-27 17:57:38

1 背景知識(shí)采用基于FPGA的方式進(jìn)行系統(tǒng)設(shè)計(jì),具備運(yùn)行傳輸速度快、并行處理內(nèi)部程序、有大量開發(fā)好的IP核、引腳眾多、設(shè)計(jì)靈活等優(yōu)點(diǎn)。針對(duì)被測(cè)樣機(jī)的功能模式和受控電路模塊眾多,對(duì)控制器I/O引腳資源

2018-08-07 10:08:19

的挑戰(zhàn)。本文采用RFC815中的重組算法實(shí)現(xiàn)的基于FPGA的IP碎片重組模塊能夠提供對(duì)OC-48接口流量的支持,具有硬件開銷小,可擴(kuò)展性好的特點(diǎn),并提供了一種針對(duì)IP碎片攻擊的預(yù)警機(jī)制,能夠抵抗常見

2008-10-07 11:00:19

作為我項(xiàng)目的一部分,我需要將ADC與7系列FPGA接口,我有一個(gè)SelectIO?接口向?qū)У?b class="flag-6" style="color: red">IP核。但是,我的整個(gè)項(xiàng)目都在VHDL中,IPi得到的是Verilog。請(qǐng)指出我如何在我的VHDL頂級(jí)模塊中使用該IP核的一些示例。最好的祝福

2020-05-21 12:31:59

閱讀目錄 linux/嵌入式常用開源庫列表其他資料參考資料linux下/嵌入式常用的開源庫名字及簡(jiǎn)介,使用文檔和教程可以自己百度 (自己整理,不定時(shí)完善) linux/嵌入式常用開源庫列表

2021-12-24 06:53:15

verilog代碼,該代碼描述了一個(gè)加法器功能。該代碼經(jīng)過綜合器解釋后,轉(zhuǎn)化成一個(gè)加法器電路。QUARTUS、ISE和VIVADO都是綜合器,集成電路常用的綜合器是DC。我們?cè)?b class="flag-6" style="color: red">FPGA設(shè)計(jì)的過程中,不可避免

2018-10-08 15:19:23

是在描述硬件,即用代碼畫圖。在 Verilog 語言中,always 塊是一種常用的功能模塊,也是結(jié)構(gòu)最復(fù)雜的部分。筆者初學(xué)時(shí)經(jīng)常為 always 語句的編寫而苦惱.

2021-07-29 07:42:25

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包軟件。提供了一些基礎(chǔ)的函數(shù)庫以及常用的控制函數(shù)模塊,配合

2022-05-19 09:16:05

Verilog HDL 綜合實(shí)用教程第1章 基礎(chǔ)知識(shí)第2章 從Verilog結(jié)構(gòu)到邏輯門第3章 建模示例第4章 模型的優(yōu)化第5章 驗(yàn)證附錄A 可綜合的語言結(jié)構(gòu)附錄B 通用庫

2009-07-20 11:21:13 86

86 給出了一種基于FPGA的分頻電路的設(shè)計(jì)方法.根據(jù)FPGA器件的特點(diǎn)和應(yīng)用范圍,提出了基于Verilog的分頻方法.該方法時(shí)于在FPGA硬件平臺(tái)上設(shè)計(jì)常用的任意偶數(shù)分頻、奇數(shù)分頻、半整數(shù)分頻

2011-11-09 09:49:33 355

355 可綜合的Verilog語法和語義(劍橋大學(xué),影印):第七版

2012-05-21 14:50:14 27

27 文中在FPGA芯片中嵌入MC8051 IP Core,作為控制核心,利用Verilog HDL語言進(jìn)行編程,設(shè)計(jì)了以MC8051 IPCore為核心的控制模塊、計(jì)數(shù)模塊、鎖存模塊和LCD顯示模塊等模塊電路,采用等精度測(cè)量法

2012-12-24 09:51:45 2670

2670 Xilinx FPGA工程例子源碼:IP camera的開源系統(tǒng)

2016-06-07 14:13:43 13

13 FPGA verilog 相關(guān)設(shè)計(jì)實(shí)踐

2017-09-06 11:19:34 34

34 本文檔的主要內(nèi)容詳細(xì)介紹的是常用模塊的Verilog HDL設(shè)計(jì)詳細(xì)資料免費(fèi)下載。

2018-10-16 11:12:54 20

20 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA視頻教程之Verilog基礎(chǔ)的詳細(xì)資料說明包括了:1.Verilog HDL簡(jiǎn)介,2.Verilog HDL模型的基本結(jié)構(gòu),3.Verilog HDL模塊的組成

2019-03-21 15:02:49 37

37 在接觸Verilog 語法參考手冊(cè)的時(shí)候,我們發(fā)現(xiàn)其提供了一組非常豐富的功能來描述硬件。所以大家往往會(huì)疑惑那些Verilog語句是可綜合的,那些是只能用于寫Testbench的,其實(shí),參考手冊(cè)中只有

2019-04-20 10:59:39 5221

5221 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的視頻教程之Verilog模塊的基本構(gòu)成要素資料說明。

2019-03-26 16:55:21 13

13 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的視頻教程之Verilog模塊中的信號(hào)詳細(xì)資料說明。

2019-03-26 16:55:23 17

17 本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計(jì)、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時(shí)序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-02 07:10:00 3646

3646

Verilog中提供了四種循環(huán)語句,可用于控制語句的執(zhí)行次數(shù),分別為:for,while,repeat,forever。其中,for,while,repeat是可綜合的,但循環(huán)的次數(shù)需要在編譯之前就確定,動(dòng)態(tài)改變循環(huán)次數(shù)的語句是不可綜合的。forever語句是不可綜合的,主要用于產(chǎn)生各種仿真激勵(lì)。

2019-10-13 12:23:00 20332

20332 端口添加多數(shù)表決電路。構(gòu)建這種三重化方案是一項(xiàng)非常重要的任務(wù),需要花費(fèi)大量的時(shí)間和精力來修改設(shè)計(jì)代碼。本文開發(fā)了RASP-TMR工具,該工具具有以可綜合的Verilog設(shè)計(jì)文件為輸入,對(duì)設(shè)計(jì)進(jìn)行解析和三次復(fù)制的功能。該工具還生成了一個(gè)頂層模塊,其中所有三個(gè)模塊都

2020-04-16 08:00:00 5

5 可綜合模塊最終生成的bit文件會(huì)燒錄進(jìn)芯片運(yùn)行,而仿真模塊編譯過后是在仿真軟件(例如modelsim)上運(yùn)行的。仿真模塊是基于可綜合模塊進(jìn)行例化,并通過仿真軟件的模擬,可以初步驗(yàn)證我們寫的可綜合模塊的實(shí)現(xiàn)現(xiàn)象。

2020-11-27 14:27:27 4454

4454 本文主要介紹verilog基礎(chǔ)模塊,夯實(shí)基礎(chǔ),對(duì)深入學(xué)習(xí)FPGA會(huì)有很大幫助。

2022-02-08 15:04:08 3315

3315

本文主要介紹verilog基礎(chǔ)模塊,夯實(shí)基礎(chǔ),對(duì)深入學(xué)習(xí)FPGA會(huì)有很大幫助。

2021-01-22 10:41:17 5

5 本教程解釋了如何在基于Verilog的設(shè)計(jì)中包含Altera的庫模塊,這些設(shè)計(jì)是使用Quartus R:II軟件實(shí)現(xiàn)的。

2021-01-22 15:34:12 4

4 開發(fā)所有可綜合Verilog的語義所選擇的方法是從過于簡(jiǎn)單的{V0{開始,然后在簡(jiǎn)單的語義中斷時(shí)使其更加復(fù)雜。這樣可以避免不必要的復(fù)雜性。計(jì)劃對(duì)越來越大的子集(V1、V2等)進(jìn)行重新排序,這些子集將收斂到劍橋VFE project2中使用的Verilog版本。

2021-02-05 16:24:05 14

14 電路“胸有成竹”; 牢記可綜合Verilog HDL與電路結(jié)構(gòu)一一對(duì)應(yīng)的關(guān)系; 確認(rèn)電路指標(biāo)是什么:性能?面積? 硬件思維方式,代碼不再是一行行的代碼而是一塊一塊的硬件模塊; 達(dá)到以上幾點(diǎn),就可以確保寫出行云流水般的高質(zhì)量代碼。 關(guān)于代碼與硬件電路的對(duì)應(yīng)關(guān)系,參見如下圖

2021-04-04 11:19:00 4854

4854

FPGA CPLD中的Verilog設(shè)計(jì)小技巧(肇慶理士電源技術(shù)有限)-FPGA CPLD中的Verilog設(shè)計(jì)小技巧? ? ? ? ? ? ? ? ?

2021-09-18 16:49:18 37

37 該FPGA項(xiàng)目旨在詳細(xì)展示如何使用Verilog處理圖像,從Verilog中讀取輸入位圖圖像(.bmp),處理并將處理結(jié)果寫入Verilog中的輸出位圖圖像。提供了用于讀取圖像、圖像處理和寫入圖像

2021-09-23 16:17:07 5361

5361 該FPGA項(xiàng)目旨在詳細(xì)展示如何使用Verilog處理圖像,從Verilog中讀取輸入位圖圖像(.bmp),處理并將處理結(jié)果寫入Verilog中的輸出位圖圖像。提供了用于讀取圖像、圖像處理和寫入圖像

2021-09-23 15:50:21 7240

7240 優(yōu)秀的 Verilog/FPGA開源項(xiàng)目介紹(一)-PCIe通信 今天開始會(huì)陸續(xù)介紹一些優(yōu)秀的開源項(xiàng)目,項(xiàng)目基本都是和FPGA或HDL相關(guān)的。對(duì)于一些找工作或者急需項(xiàng)目經(jīng)驗(yàn)的人來說,這些項(xiàng)目都有一定

2021-10-11 15:31:47 11032

11032

閱讀目錄linux/嵌入式常用開源庫列表其他資料參考資料linux下/嵌入式常用的開源庫名字及簡(jiǎn)介,使用文檔和教程可以自己百度 (自己整理,不定時(shí)完善)linux/嵌入式常用開源庫列表

2021-10-20 19:20:59 5

5 優(yōu)秀的 Verilog/FPGA開源項(xiàng)目介紹(五)- USB通信 USB是我們生活中非常非常常見的接口,鼠標(biāo)、鍵盤以及常見的U 盤等,可以說現(xiàn)在的USB設(shè)備已經(jīng)滲透到生活中的方方面面,下面就介紹幾個(gè)

2021-11-02 14:54:15 10037

10037

優(yōu)秀的 Verilog/FPGA開源項(xiàng)目介紹(七)- CAN0、CAN總線介紹《【科普】CAN總線介紹及FPGA實(shí)現(xiàn)方案簡(jiǎn)介》 1、CAN權(quán)威文檔CAN總線有兩個(gè)ISO國(guó)際標(biāo)準(zhǔn):ISO11898

2021-11-17 11:19:56 3801

3801 了解決這個(gè)復(fù)雜的問題,設(shè)計(jì)了這個(gè)庫,它可以幫助您簡(jiǎn)化設(shè)計(jì)流程。使用一些簡(jiǎn)單的 API 可以輕松地在測(cè)試臺(tái)中讀取和寫入標(biāo)準(zhǔn)位圖文件 (.BMP)。并且,使用 AXI-Stream Video

2022-05-05 09:48:09 2500

2500 ARTIX-xlinx 版本FPGA 串口通信模塊(含IP核)

2022-06-20 11:07:28 16

16 電子發(fā)燒友網(wǎng)站提供《TTL FPGA開源項(xiàng)目.zip》資料免費(fèi)下載

2022-07-28 10:18:33 3

3 電子發(fā)燒友網(wǎng)站提供《樹莓派計(jì)算模塊開源項(xiàng)目.zip》資料免費(fèi)下載

2022-08-05 09:25:58 1

1 電子發(fā)燒友網(wǎng)站提供《FPGA與MCU單片機(jī)的綜合開發(fā)板開源.zip》資料免費(fèi)下載

2022-08-09 09:41:41 2

2 電子發(fā)燒友網(wǎng)站提供《快充模塊IP6505T開源分享.zip》資料免費(fèi)下載

2022-08-10 14:33:38 10

10 電子發(fā)燒友網(wǎng)站提供《可遠(yuǎn)程監(jiān)控蜂巢的開源項(xiàng)目.zip》資料免費(fèi)下載

2022-11-17 09:24:33 0

0 Verilog 例化說明 1.什么是模塊例化?為什么要例化? 模塊例化可以理解成模塊調(diào)用。對(duì)于一個(gè) FPGA 工程,通常是由一個(gè)頂層模塊與多個(gè)功能子模塊組成,為了實(shí)現(xiàn)頂層模塊與子模塊的連接,需要進(jìn)行

2022-12-12 09:50:06 5338

5338 一個(gè)復(fù)雜電路系統(tǒng)的完整Verilog HDL模型是由若干個(gè)Verilog HDL模塊構(gòu)成的,每一個(gè)模塊又可以由若干個(gè)子模塊構(gòu)成。其中有些模塊需要綜合成具體電路,而有些模塊只是與用戶所設(shè)計(jì)的模塊有交互聯(lián)系的現(xiàn)存電路或激勵(lì)信號(hào)源。

2023-02-02 10:03:38 12464

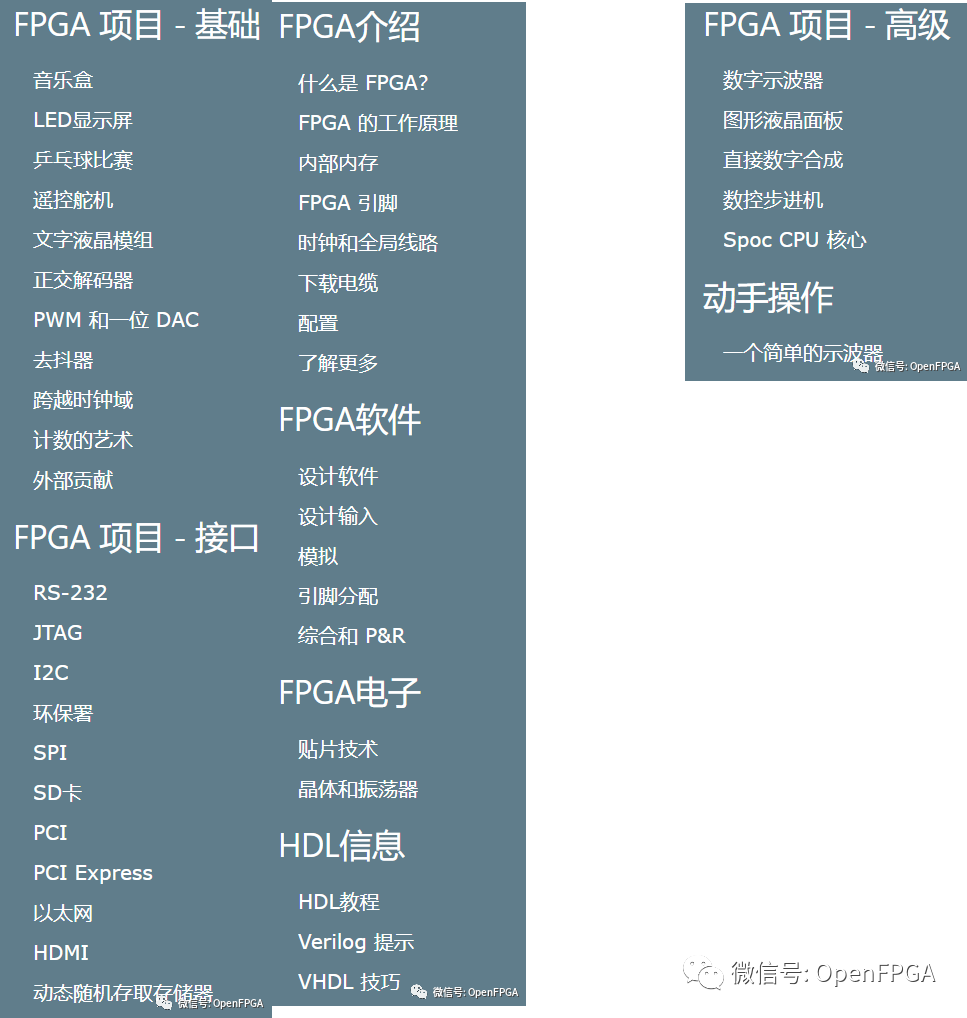

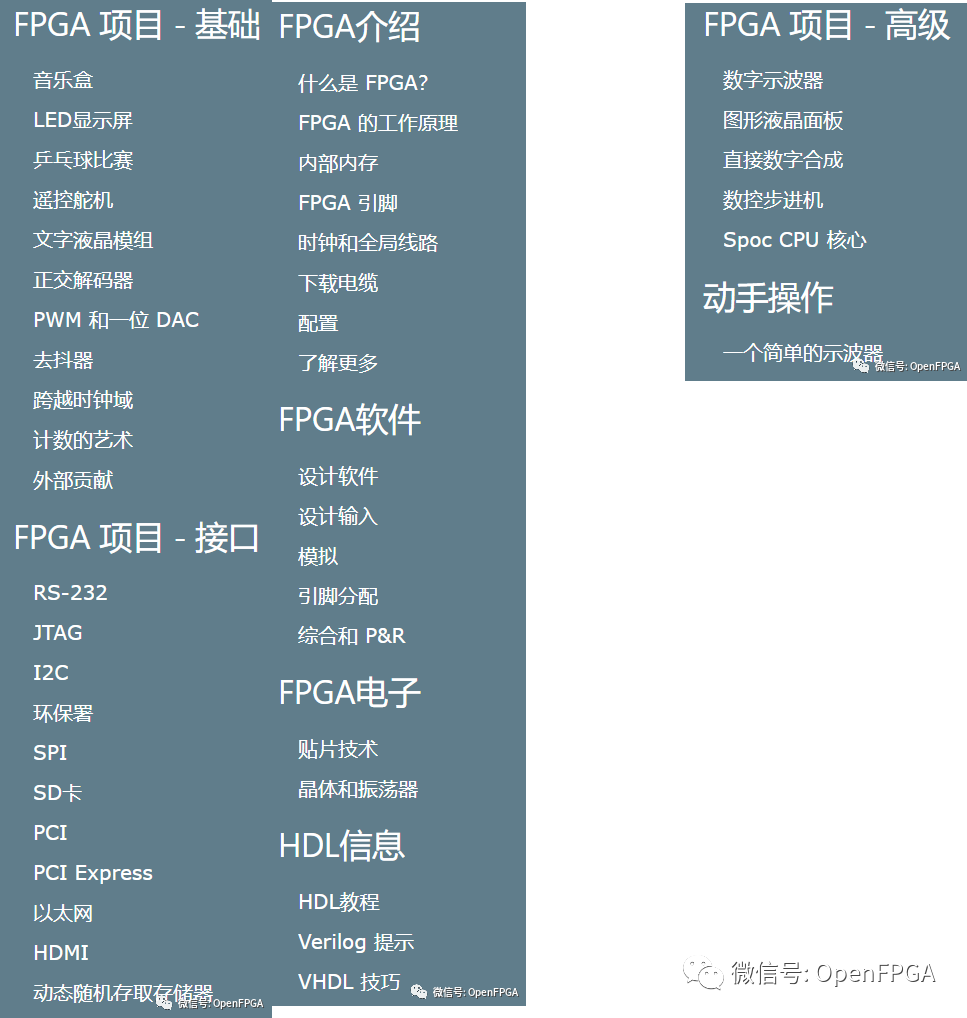

12464 FPGA 項(xiàng)目使用一種稱為 Verilog 的語言,您需要學(xué)習(xí)它才能理解項(xiàng)目。但是通過此處顯示的示例以及其他可用的在線資源,這并不太難。

2023-04-06 14:33:10 1692

1692

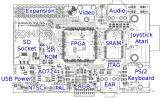

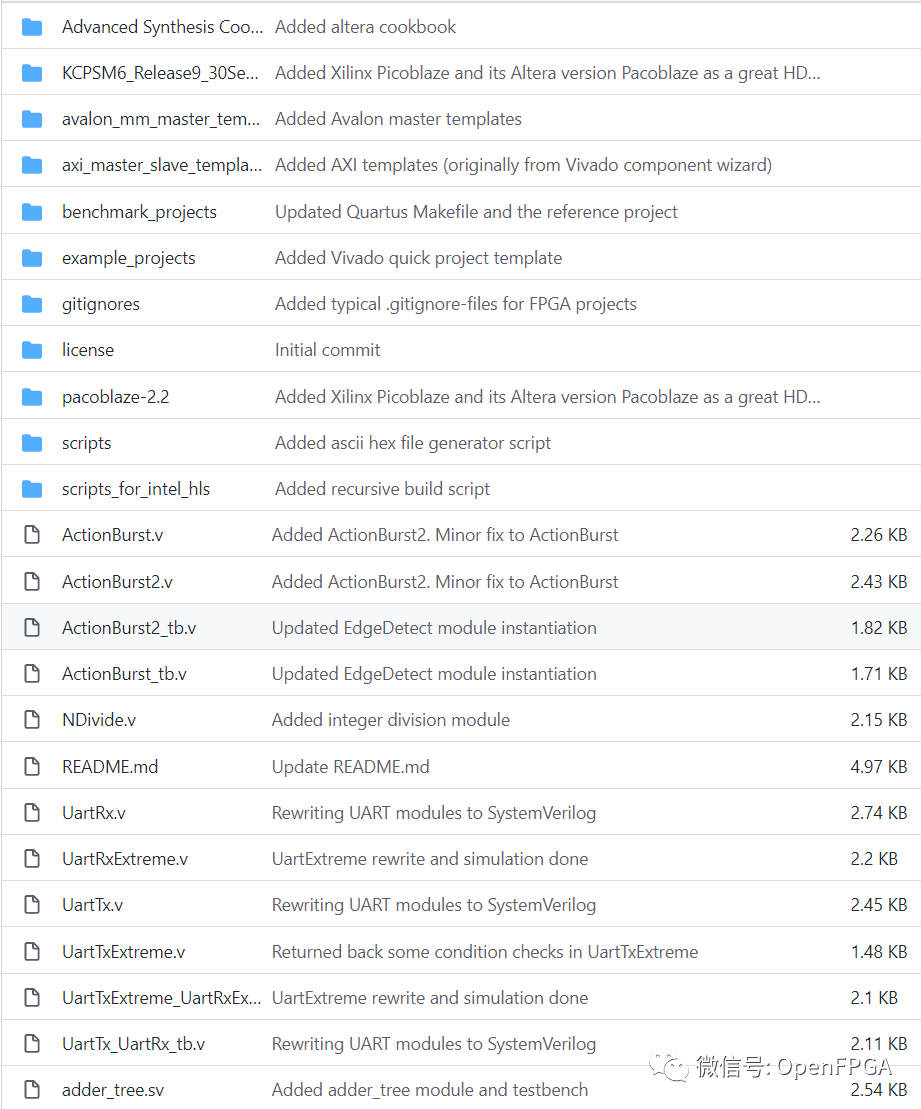

一直想做一個(gè)可以供大家學(xué)習(xí)、使用的開源IP庫,類似OpenCores,OC上IP在領(lǐng)域內(nèi)的IP很少,通用性強(qiáng)一點(diǎn),所以作為OC的“補(bǔ)充”,所以做了一個(gè)開源IP庫,

2023-05-06 09:16:08 1606

1606

本文是本系列的第三篇,本文主要介紹FPGA常用運(yùn)算模塊-乘加器,xilinx提供了相關(guān)的IP以便于用戶進(jìn)行開發(fā)使用。

2023-05-22 16:17:12 2959

2959

本文是本系列的第四篇,本文主要介紹FPGA常用運(yùn)算模塊-除法器,xilinx提供了相關(guān)的IP以便于用戶進(jìn)行開發(fā)使用。

2023-05-22 16:20:45 5431

5431

本文是本系列的第五篇,本文主要介紹FPGA常用運(yùn)算模塊-復(fù)數(shù)乘法器,xilinx提供了相關(guān)的IP以便于用戶進(jìn)行開發(fā)使用。

2023-05-22 16:23:28 4135

4135

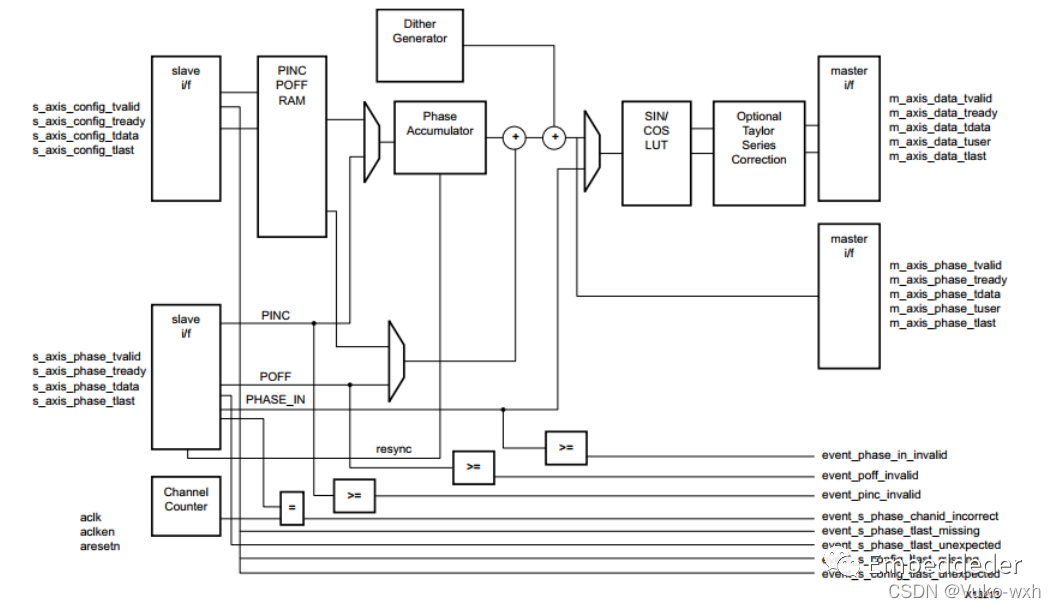

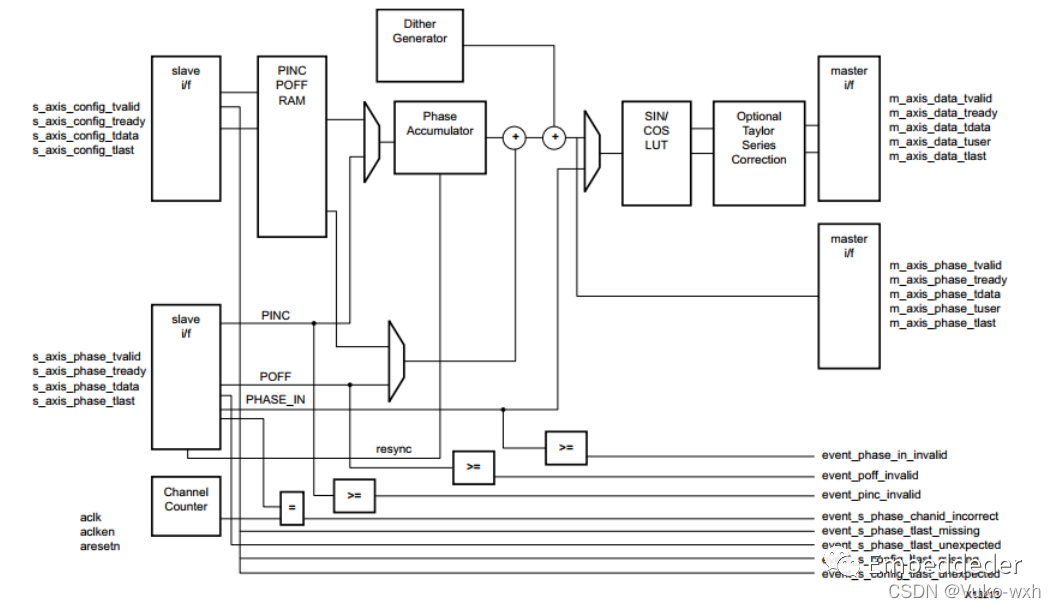

本文是本系列的第六篇,本文主要介紹FPGA常用運(yùn)算模塊-DDS信號(hào)發(fā)生器,xilinx提供了相關(guān)的IP以便于用戶進(jìn)行開發(fā)使用。

2023-05-24 10:37:18 7398

7398

建立用于RTL綜合的Verilog標(biāo)準(zhǔn)化子集。他是貝爾實(shí)驗(yàn)室所開發(fā)的ArchSyn綜合系統(tǒng)的主要設(shè)計(jì)者之一。他曾為AT&T和Lucent的許多設(shè)計(jì)師講授Verilog HDL語言和Verilog HDL綜合課程。

2023-05-26 16:59:30 2182

2182

《優(yōu)秀的IC/FPGA開源項(xiàng)目》是新開的系列,旨在介紹單一項(xiàng)目,會(huì)比《優(yōu)秀的 Verilog/FPGA開源項(xiàng)目》內(nèi)容介紹更加詳細(xì),包括但不限于綜合、上板測(cè)試等。兩者相輔相成,互補(bǔ)互充。

2023-06-09 09:42:41 3531

3531

電子發(fā)燒友網(wǎng)站提供《可緩解潮熱癥狀的開源項(xiàng)目.zip》資料免費(fèi)下載

2023-07-03 10:15:11 0

0 FPGA IP核(Intellectual Property core)是指在可編程邏輯器件(Field-Programmable Gate Array,FPGA)中使用的可復(fù)用的設(shè)計(jì)模塊或功能片段。它們是預(yù)先編寫好的硬件設(shè)計(jì)代碼,可以在FPGA芯片上實(shí)現(xiàn)特定的功能。

2023-07-03 17:13:28 8969

8969 IP(Intellectual Property)是知識(shí)產(chǎn)權(quán)的意思,半導(dǎo)體行業(yè)的IP是“用于ASIC或FPGA中的預(yù)先設(shè)計(jì)好的電路功能模塊”。一些常用的復(fù)雜的功能模塊(如FIFO、RAM、FIR

2023-08-22 15:04:43 7796

7796

Hello,大家好,之前給大家分享了大約一百多個(gè)關(guān)于FPGA的開源項(xiàng)目,涉及PCIe、網(wǎng)絡(luò)、RISC-V、視頻編碼等等,這次給大家?guī)淼氖遣豢菰锏膴蕵?b class="flag-6" style="color: red">項(xiàng)目,主要偏向老的游戲內(nèi)核使用FPGA進(jìn)行硬解,涉及的內(nèi)核數(shù)不勝數(shù),主要目標(biāo)是高的可實(shí)現(xiàn)性及復(fù)現(xiàn)性。

2024-01-10 10:54:24 2672

2672

FPGA(現(xiàn)場(chǎng)可編程邏輯門陣列)開發(fā)主要使用的編程語言是硬件描述語言(HDL),其中Verilog是最常用的編程語言之一。而C語言通常用于傳統(tǒng)的軟件編程,與FPGA的硬件編程有所區(qū)別。

2024-03-27 14:38:14 3907

3907 Verilog測(cè)試平臺(tái)設(shè)計(jì)方法是Verilog FPGA開發(fā)中的重要環(huán)節(jié),它用于驗(yàn)證Verilog設(shè)計(jì)的正確性和性能。以下是一個(gè)詳細(xì)的Verilog測(cè)試平臺(tái)設(shè)計(jì)方法及Verilog FPGA開發(fā)

2024-12-17 09:50:06 1630

1630 /prologue-the-2022-wilson-research-group-functional-verification-study/),70% 的 FPGA 項(xiàng)目落后于計(jì)劃,12% 的項(xiàng)目落后計(jì)劃 50% 以上。 為此,很多FPGA廠商都在自己EDA工具里嵌入IP減少FPGA項(xiàng)目的開發(fā)周期,使用 IP 是一種有助于實(shí)現(xiàn)按時(shí)、高質(zhì)量且經(jīng)濟(jì)高效的項(xiàng)目交付的方法。

2025-01-15 10:47:37 1246

1246

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論