1.亞穩態與設計可靠性設計數字電路時大家都知道同步是非常重要的,特別當要輸入一個信號到一個同步電路中,但是該

2017-12-18 09:53:13 9651

9651

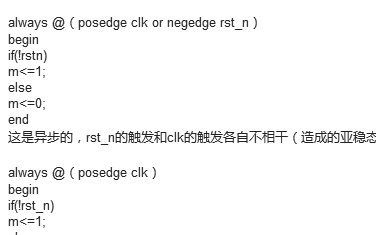

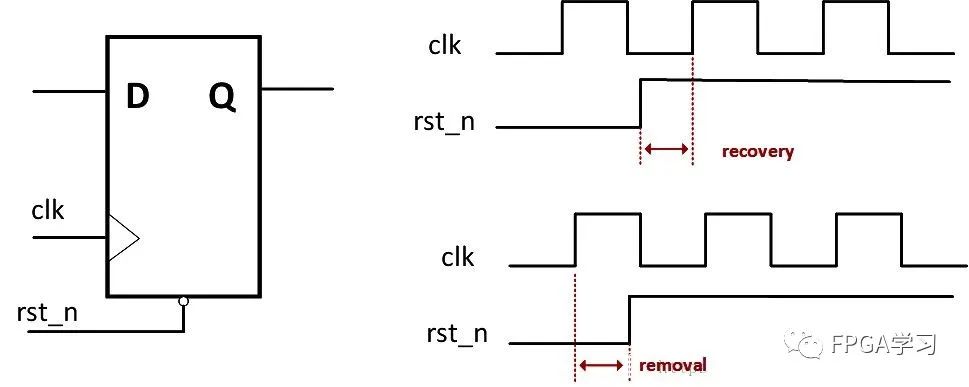

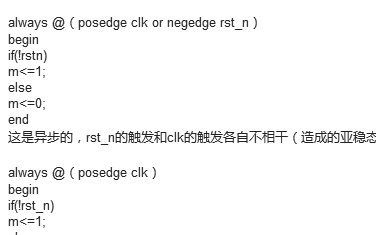

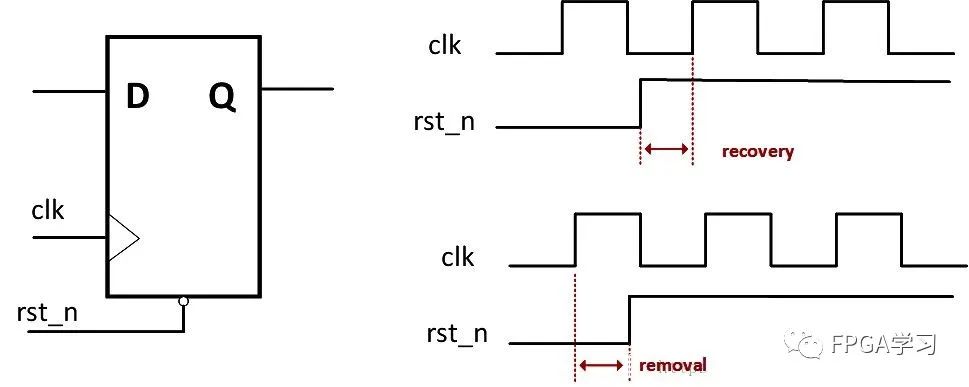

在復位電路中,由于復位信號是異步的,因此,有些設計采用同步復位電路進行復位,并且絕大多數資料對于同步復位電路都認為不會發生亞穩態,其實不然,同步電路也會發生亞穩態,只是幾率小于異步復位電路。

2020-06-26 16:37:00 1776

1776

只要系統中有異步元件,亞穩態就是無法避免的,亞穩態主要發生在異步信號檢測、跨時鐘域信號傳輸以及復位電路等常用設計中。

2020-09-30 17:08:43 4345

4345

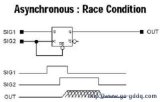

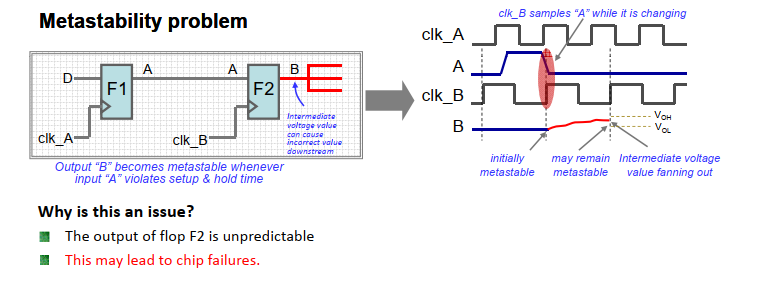

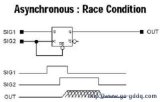

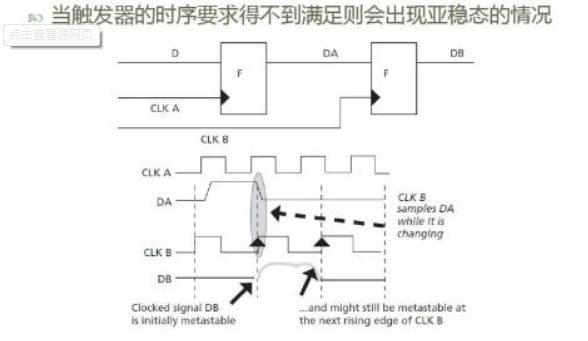

由于亞穩態的輸出在穩定下來之前可能是毛刺、振蕩、固定的某一電壓值,因此亞穩態除了導致邏輯誤判之外,輸出在0~1之間的中間電壓值還會使下一級產生亞穩態(導致亞穩態的傳播)。

2022-07-21 14:46:50 1461

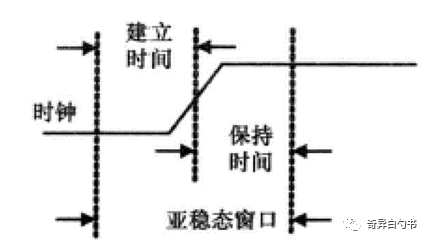

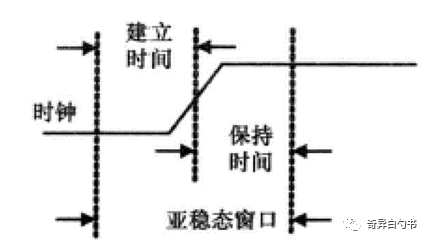

1461 發生亞穩態的原因是信號在傳輸的過程中不能滿足觸發器的建立時間和保持時間。

2023-06-20 15:29:58 2210

2210

亞穩態這種現象是不可避免的,哪怕是在同步電路中也有概率出現,所以作為設計人員,我們能做的是減少亞穩態發生的概率。

2023-08-03 09:04:49 732

732

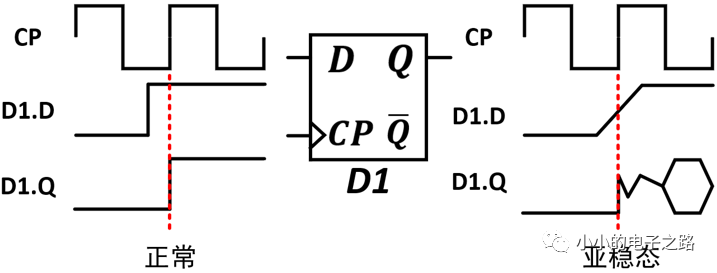

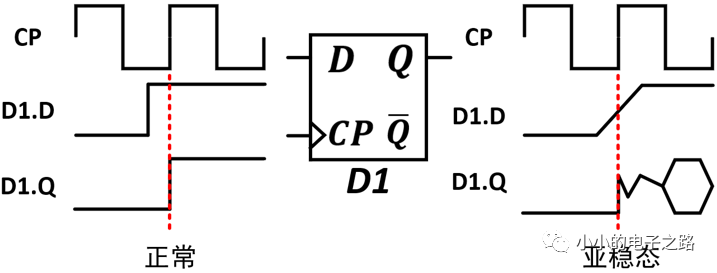

亞穩態是指觸發器的輸入信號無法在規定時間內達到一個確定的狀態,導致輸出振蕩,最終會在某個不確定的時間產生不確定的輸出,可能是0,也可能是1,導致輸出結果不可靠。

2023-11-22 18:26:09 2725

2725

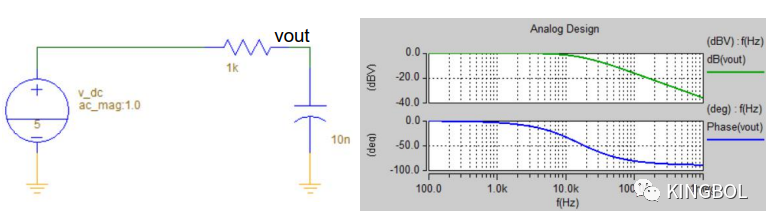

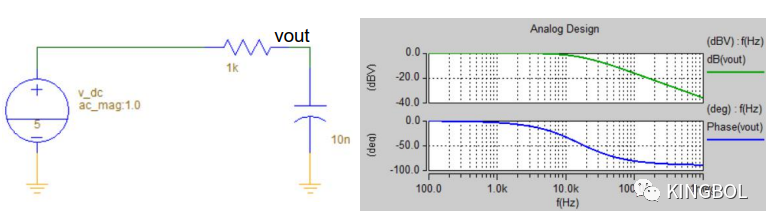

仿真可以大大減少通過測量進行穩態分析的工作量,但由于大多數電路模擬器缺乏在實際電路上進行交流分析的能力,實驗室方法仍然流行。

2023-12-06 14:07:11 1673

1673

亞穩態是數字電路設計中最為基礎和核心的理論。同步系統設計中的多項技術,如synthesis,CTS,STA等都是為了避免同步系統產生亞穩態。異步系統中,更容易產生亞穩態,因此需要對異步系統進行特殊的設計處理。學習SoC芯片設計,歡迎加入啟芯QQ群:275855756

2013-11-01 17:45:15

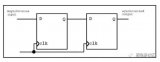

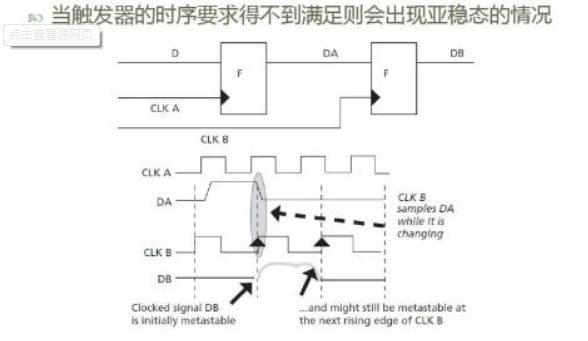

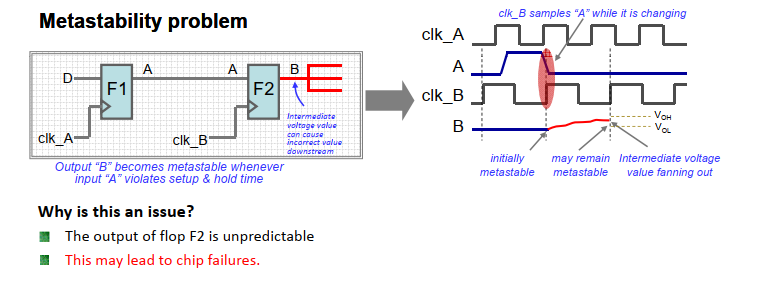

的邏輯是同步邏輯。在一個模塊中不具有相同相位和時間關系的時鐘被視為不同的時鐘域,其所驅動的邏輯是異步邏輯。亞穩態:如果數據傳輸中不滿足觸發器的建立時間和保持時間,或者復位過程中復位信號的釋放相對于有效

2021-07-26 07:03:57

FPGA 設計需要重視的一個注意事項。理論分析01 信號傳輸中的亞穩態在同步系統中,輸入信號總是系統時鐘同步,能夠達到寄存器的時序要求,所以亞穩態不會發生。亞穩態問題通常發生在一些跨時鐘域信號傳輸以及異步

2020-10-22 11:42:16

導致復位失敗。怎么降低亞穩態發生的概率成了FPGA設計需要重視的一個注意事項。2. 理論分析2.1信號傳輸中的亞穩態在同步系統中,輸入信號總是系統時鐘同步,能夠達到寄存器的時序要求,所以亞穩態不會

2012-04-25 15:29:59

部件將其作出不同的判斷,有的判斷到“1”有的判斷到“0”,有的也進入了亞穩態,數字部件就會邏輯混亂。在復位電路中產生亞穩態可能會導致復位失敗。怎么降低亞穩態發生的概率成了FPGA設計需要重視的一個

2012-01-11 11:49:18

摘要:FPGA異步時鐘設計中如何避免亞穩態的產生是一個必須考慮的問題。本文介紹了FPGA異步時鐘設計中容易產生的亞穩態現象及其可能造成的危害,同時根據實踐經驗給出了解決這些問題的幾種同步策略。關鍵詞

2009-04-21 16:52:37

說起亞穩態,首先我們先來了解一下什么叫做亞穩態。亞穩態現象:信號在無關信號或者異步時鐘域之間傳輸時導致數字器件失效的一種現象。

2019-09-11 11:52:32

可能會出現非法狀態---亞穩態。亞穩態是一種不穩定狀態,在一定時間后, 最終返回到兩個穩定狀態之一。亞穩態輸出的信號是什么樣子的? 對于系統有什么危害? 如果降低亞穩態帶來的危害? 這是下面要探討

2012-12-04 13:51:18

FPGA項目開發之同步信號和亞穩態

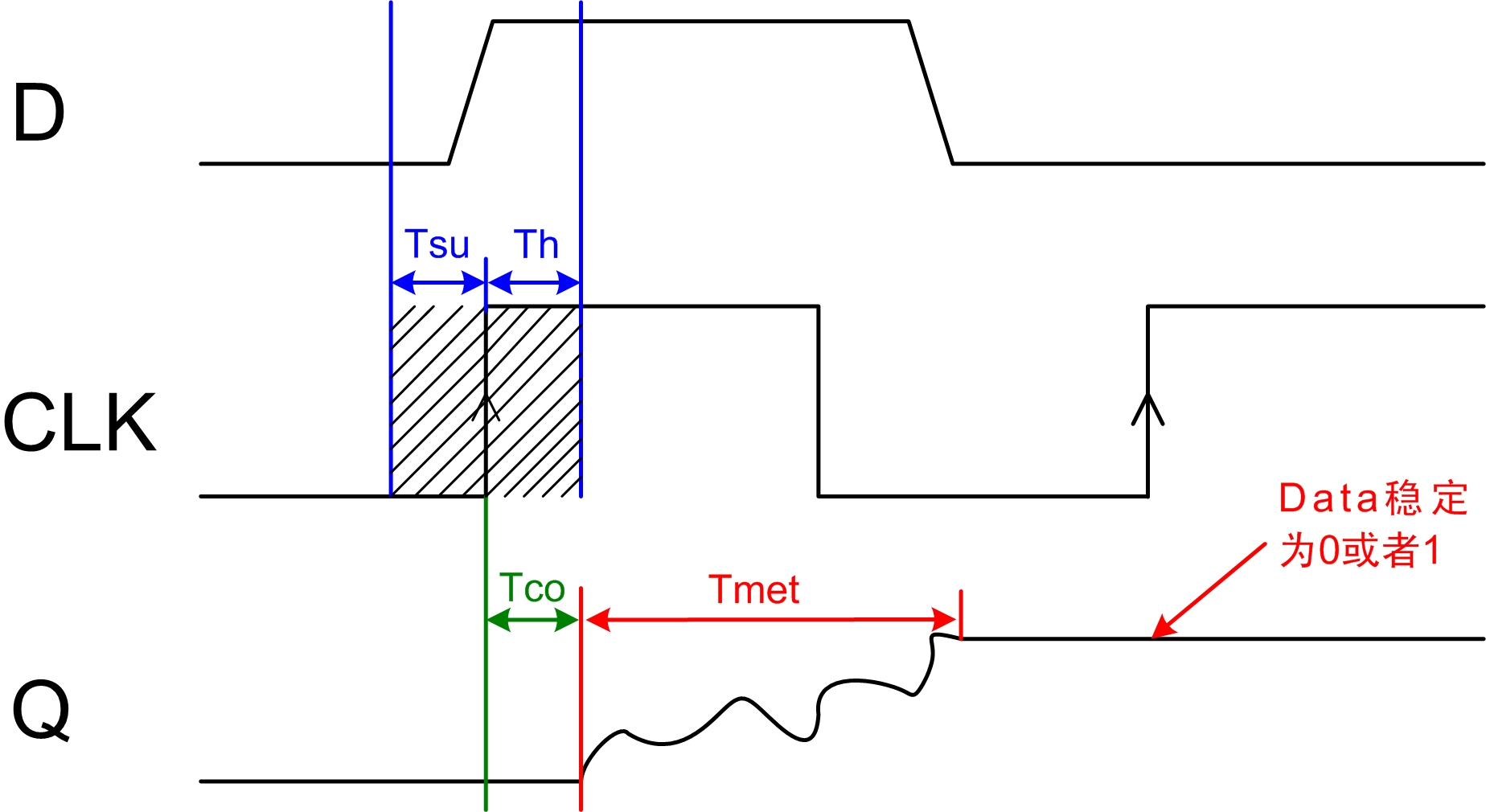

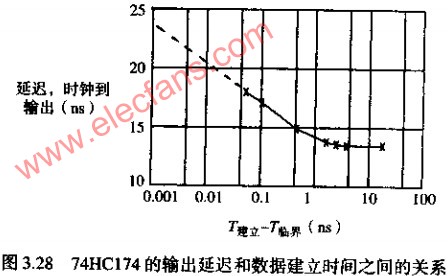

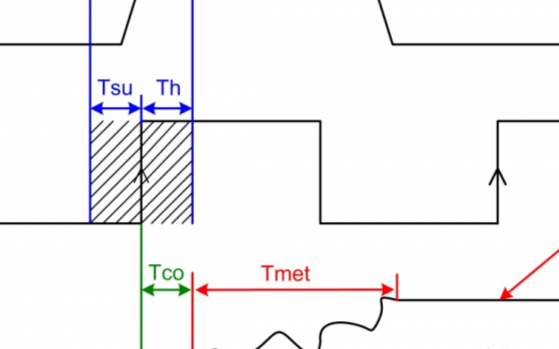

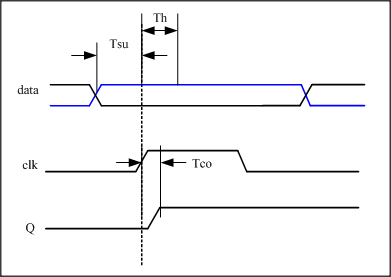

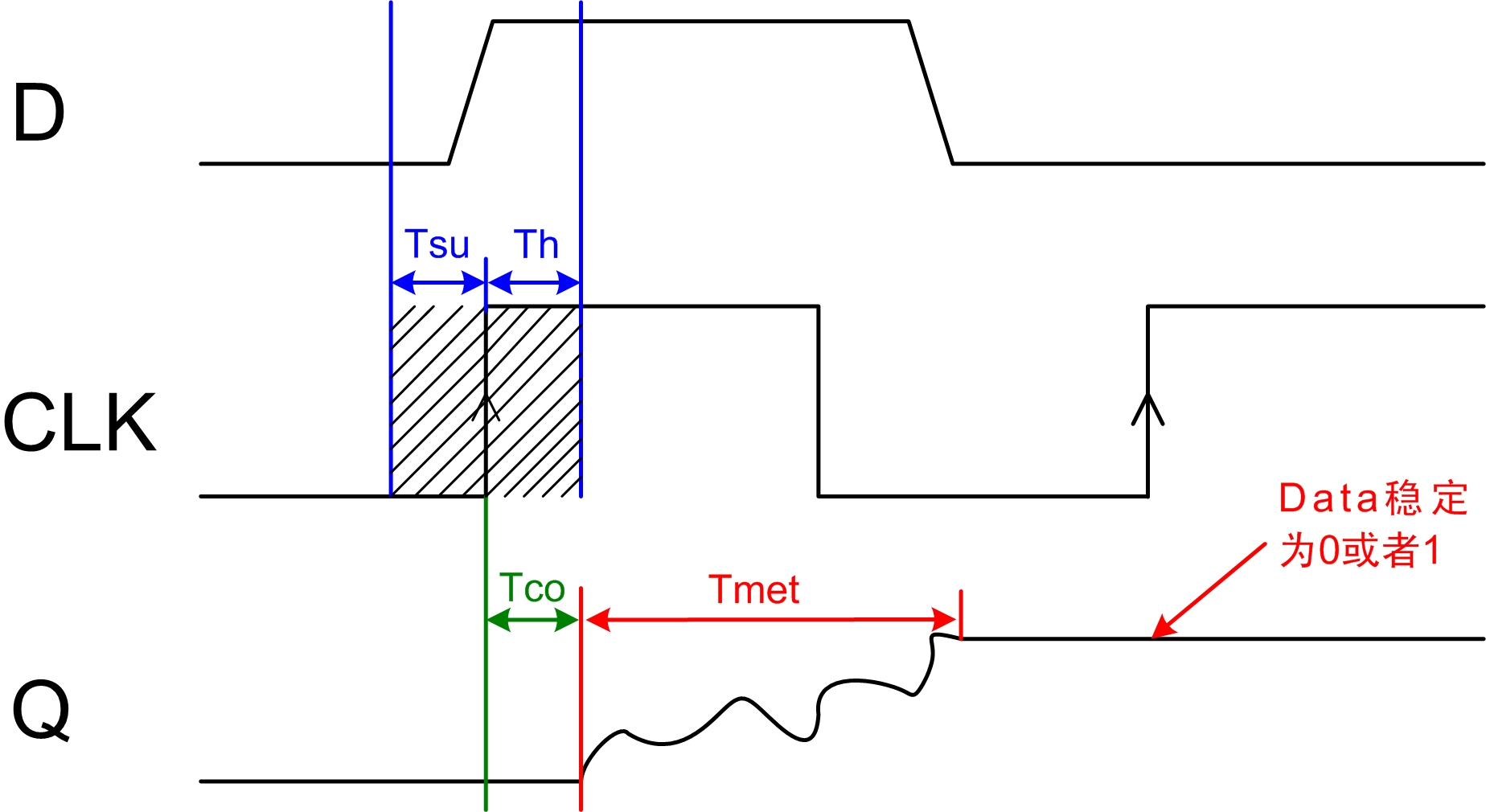

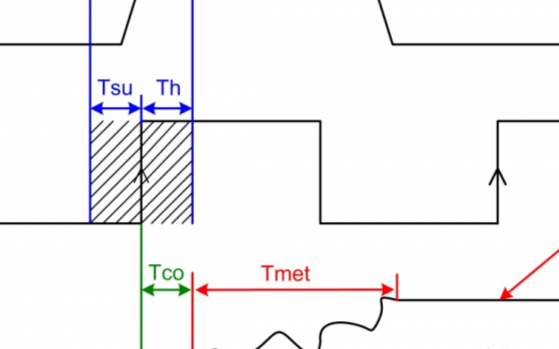

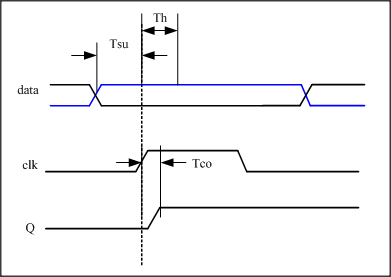

讓我們從觸發器開始,所有觸發器都有一個圍繞活動時鐘沿的建立(setup time)和保持窗口(hold time),在此期間數據不得更改。如果該窗口中的數據

2023-11-03 10:36:15

及個階段使用的工具。3.信號的跨時鐘域同步。包括單比特和多比特,對于單比特自然用兩級寄存器同步最為方便。對于多比特,常考察異步FIFO以及握手方法。要理解亞穩態的概念以及避免亞穩態的方法。...

2021-07-22 07:12:22

中找到任何最小數量的寄存器的建議。我需要有關同步器鏈長度的任何建議或任何文檔,以便針對Virtex-5器件提供更好的亞穩態保護。我還需要Virtex-6的類似信息。很抱歉,如果這不是此主題的正確論壇。提前致謝,阿姆魯

2020-06-12 09:27:03

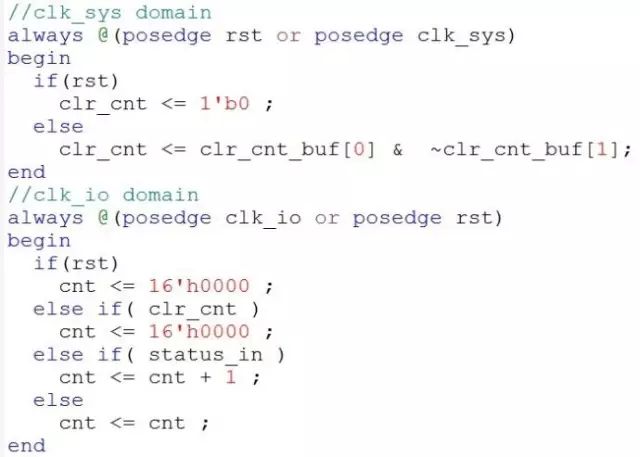

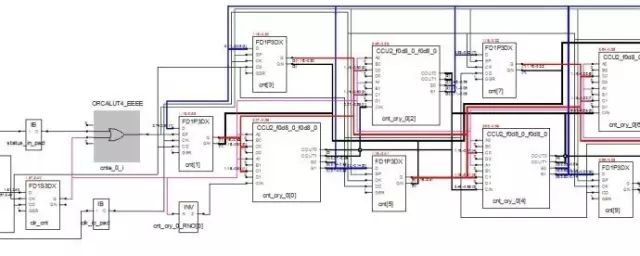

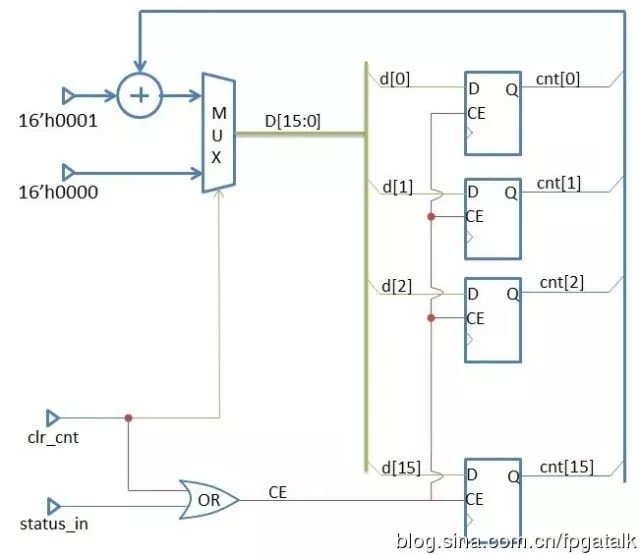

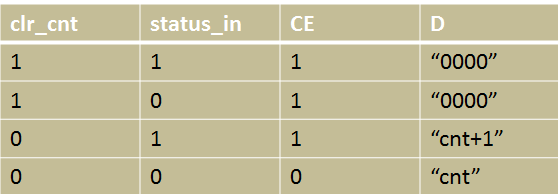

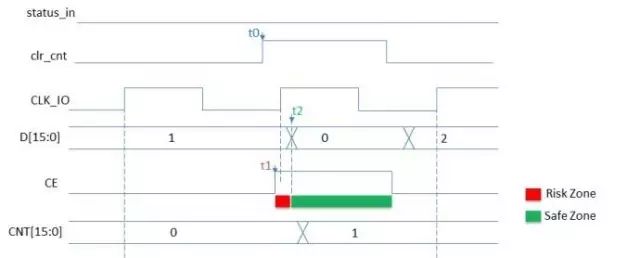

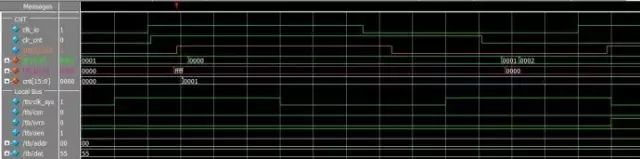

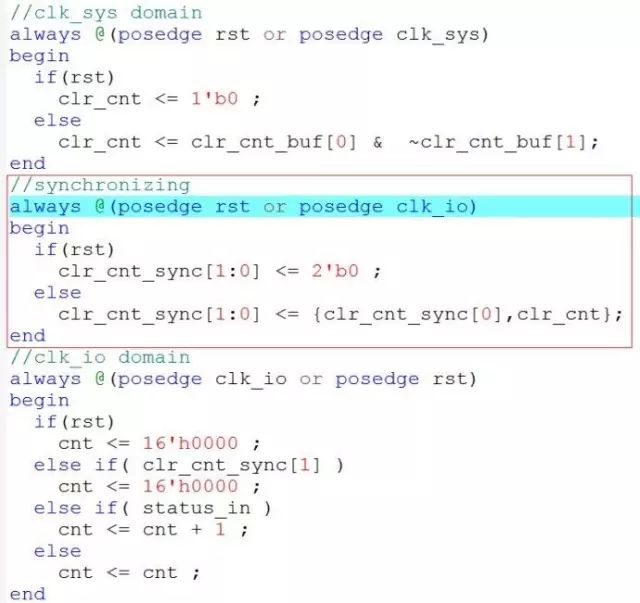

時,引起亞穩態事件,CNT才會出錯,當然這種故障的概率會低的多。 圖5.“cnt”觸發器的后仿真時序違反演示 解決措施通過以上的分析,問題是由于信號跨異步時鐘域而產生了模糊的時序關系,布局布線工具無法也不可能

2012-12-04 13:55:50

的亞穩態事件,結合實例講解,語言通俗易懂,由淺入深,特別舉了多個實例以及解決方案,非常具有針對性,讓人受益匪淺,非常適合對亞穩態方面掌握不好的中國工程師和中國的學生朋友,是關于亞穩態方面不可多得的好資料,強烈推薦哦!!![hide] [/hide]`

2012-03-05 14:11:41

通過獨立按鍵控制LED燈狀態變化這樣一個實驗,來驗證獨立按鍵消抖是否成功,另外,由于獨立按鍵作為一個外部異步輸入信號,因此借此機會剛好給大家詳細介紹了亞穩態的原理和應對策略。希望大家在觀看學習時,重點

2015-09-29 14:27:58

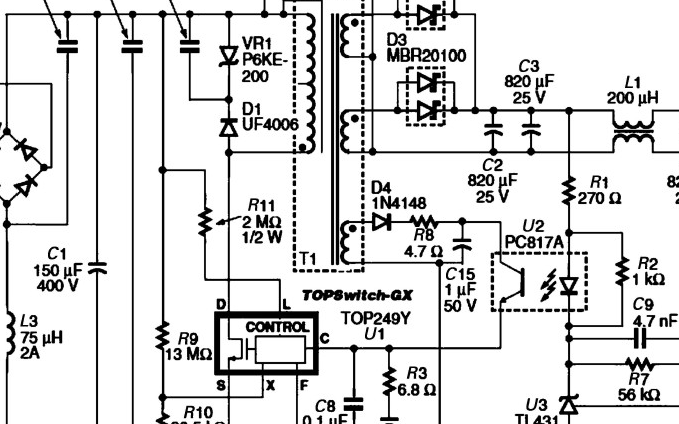

網上看到不對稱半橋后面都是加全波整流,我因為輸出電壓比較高,所以設計了不對稱半橋加倍壓整流的結構,但是在穩態分析的時候搞不清楚了,想問一下后面加全波整流和倍壓整流會影響整個拓撲結構的穩態分析嗎

2020-04-10 20:46:25

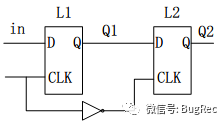

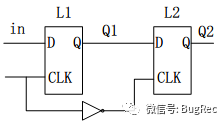

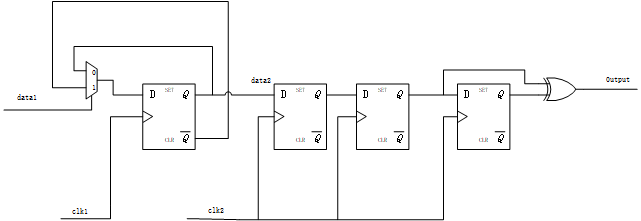

什么是同步邏輯和異步邏輯?同步電路和異步電路的區別在哪?為什么觸發器要滿足建立時間和保持時間?什么是亞穩態?為什么兩級觸發器可以防止亞穩態傳播?

2021-08-09 06:14:00

什么是壓穩態?為什么會出現壓穩態這一現象?壓穩態是怎樣導致設計失敗的?如何降低出現壓穩態失敗的概率?

2021-04-30 07:21:05

重視的一個注意事項。

理論分析

1、信號傳輸中的亞穩態

在同步系統中,輸入信號總是系統時鐘同步,能夠達到寄存器的時序要求,所以亞穩態不會發生。亞穩態問題通常發生在一些跨時鐘域信號傳輸以及異步信號采集上

2023-04-27 17:31:36

所謂亞穩態,是指“trecovery(recovery time)指的是原本有效的異步復位信號釋放(對低電平有效的復位來說就是上跳沿)與緊跟其后的第一個時鐘有效沿之間所必須的最小

2012-01-12 10:45:12

數據損壞。還需要注意recombination,這是兩個或多個靜態信號跨越時鐘域并在邏輯功能中重組的地方。由于亞穩態恢復,同步器中的延遲會導致下游邏輯受到影響。盡管我們在設計中盡最大努力減輕 CDC

2022-10-18 14:29:13

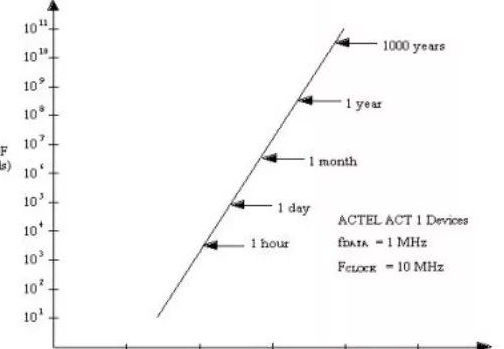

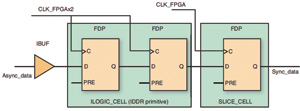

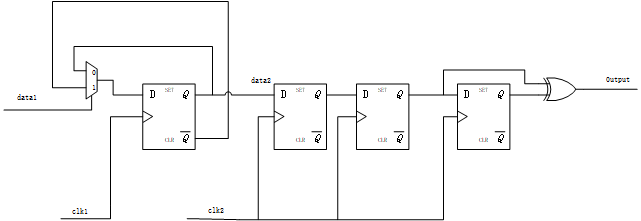

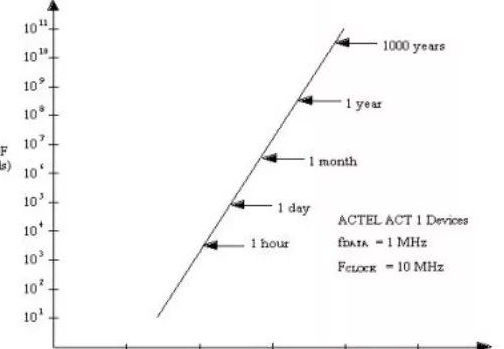

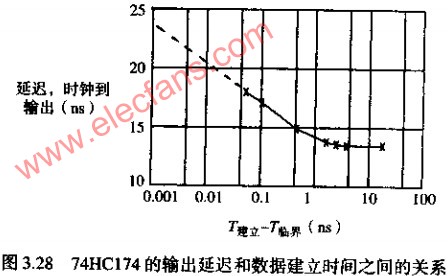

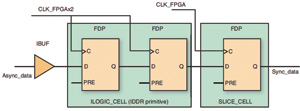

的亞穩態信號問題。亞穩態信號的穩定時間通常比一個時鐘周期要短得多,因此即便延遲半個時鐘周期,亞穩態出現的概率也會按數量級減少。為了降低亞穩態問題的出現概率,在設計中實現的一系列寄存器(連接成移位寄存器

2010-12-29 15:17:55

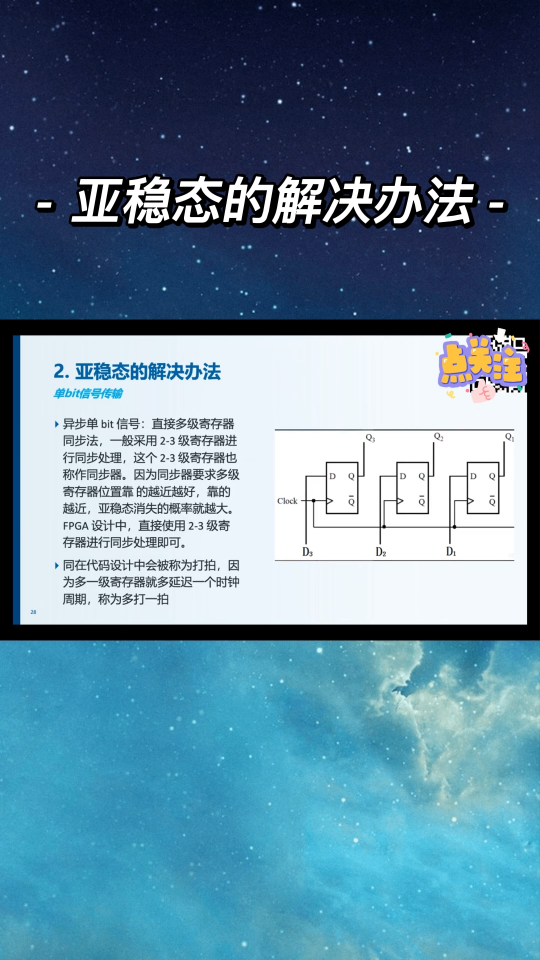

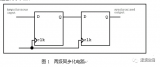

寄存器輸出,由于第一級亞穩態已經經過clk一個周期的恢復,所以在第二級寄存器輸出時,亞穩態恢復至穩態的時間T2將會縮短。T2< T1。再多級的寄存器,也無法避免亞穩態,只是級數越多,最后一級輸出亞穩態的幾率將會越低。在實際電路中,一般采用兩級或者三級即可。

2023-02-28 16:38:14

。怎么降低亞穩態發生的概率成了 FPGA 設計需要重視的一個注意事項。理論分析01 信號傳輸中的亞穩態在同步系統中,輸入信號總是系統時鐘同步,能夠達到寄存器的時序要求,所以亞穩態不會發生。亞穩態問題通常發生

2020-10-19 10:03:17

/Metastable-Delay-in-Virtex-FPGAs/ba-p/7996有Virtex4和Virtex5的測量。我正在尋找Virtex6和7Series部件的類似亞穩態參數測量。是否存在應用說明?我猜猜V6&amp; 7應該比

2020-07-18 16:58:50

微分型單穩態觸發器的Multisim分析

2012-08-06 13:13:22

新建兩個D觸發器的目的是什么?何謂亞穩態?解決亞穩態的方法是什么?

2021-11-09 07:15:01

。同樣,若通過諧振電感的耦合取出交變電壓,經整流濾波實現AC-DC的能量轉換,則稱為電感耦合型(PRC-IC)。本文給出一電感耦合型并聯諧振變換器并采用疊加的分析方法對其進行穩態分析,即將輸入方波電壓

2021-06-04 06:42:13

亞穩態現象發生的概率(只能降低,不能消除),這在FPGA設計(尤其是大工程中)是非常重要的。亞穩態的產生:所有的器件都定義了一個信號時序要求,只有滿足了這個要求,才能夠正常的在輸入端獲取數據,在輸出端

2018-08-01 09:50:52

正弦穩態電路分析8.1 正弦量與正弦穩態 8.2 相量變換 8.3電路定律和電路元件的相量形式 8.4 阻抗和導納 8.5正弦穩態電路的分析 8.6正弦穩態

2008-12-04 17:53:07 0

0 非穩態導熱的分析解視頻教程

2009-07-05 19:11:30 18

18 均勻傳輸線正弦穩態分析

一、長線復數方程的推導

在正弦激勵下,沿線各處的電壓、電流在穩態時都

2009-07-27 11:53:53 1735

1735

圖3.27所示的是一個觀察D觸發器亞穩態的電路圖。使用這個電路至少需要一個雙通道示波器。

2010-06-08 14:31:27 1490

1490

什么是亞穩態

在FPGA等同步邏輯數字器件中,所有器件的寄存器單元都需要預定義信號時序以使器件正確

2010-11-29 09:18:34 3518

3518

在本文的第一章對跨時鐘域下的同步問題和亞穩態問題做了概述。 在第二章中對時鐘同步需要考慮的基本問題做了介紹。 在第三章中仔細分析了現在常用的幾種同步方法。包括使用G

2011-09-06 15:24:12 42

42 本文分析了異步電路中亞穩態產生的原因和危害, 比較了幾種常用的降低亞穩態發生概率的設計方法, 針對這些方法不能徹底消除亞穩態的不足, 設計了一種消除亞穩態的外部邏輯控制器

2011-10-01 01:56:02 55

55 FPGA 異步時鐘設計中如何避免亞穩態的產生是一個必須考慮的問題。本文介紹了FPGA 異步時鐘設計中容易產生的亞穩態現象及其可能造成的危害,同時根據實踐經驗給出了解決這些問題的

2011-12-20 17:08:35 63

63 基于FPGA的亞穩態參數測量方法_田毅

2017-01-07 21:28:58 0

0 正弦激勵,穩態分析

2017-03-01 13:11:43 0

0 在進行FPGA設計時,往往只關心“0”和“1”兩種狀態。然而在工程實踐中,除了“0”、“1”外還有其他狀態,亞穩態就是其中之一。亞穩態是指觸發器或鎖存器無法在某個規定時間段內達到一個可確認的狀態[1]。當一個觸發器進入亞穩態時,既無法預測該單元的輸出電平,也無法預測何時輸出才能穩定在某個正確的電平上。

2019-10-06 09:42:00 1760

1760

亞穩態是指觸發器無法在某個規定時間段內達到一個可確認的狀態。當一個觸發器進入亞穩態時,既無法預測該單元的輸出電平,也無法預測何時輸出才能穩定在某個正確的電平上。在這個穩定期間,觸發器輸出一些中間級電平.

2017-12-02 10:40:12 45616

45616

通常情況下(已知復位信號與時鐘的關系),最大的缺點在于異步復位導致設計變成了異步時序電路,如果復位信號出現毛刺,將會導致觸發器的誤動作,影響設計的穩定性。同時,如果復位信號與時鐘關系不確定,將會導致 亞穩態 情況的出現。

2018-03-15 16:12:00 4610

4610

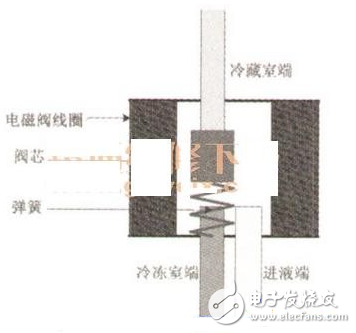

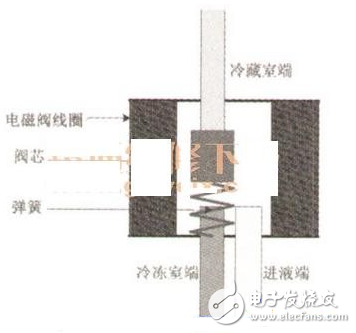

與冷藏室端連通。雙穩態電磁閥供電為脈動120V直流電,可正可負。雙穩態電磁閥:兩個線圈輪流觸發,每觸發一次,電磁閥狀態就切換(翻轉)一次。單穩態電磁閥:線圈被激勵時電磁閥是一個狀態(暫態),激勵消失時電磁閥返回到另一個狀態(常態)。

2018-04-04 11:23:18 25892

25892

種現象。 接下來主要討論在異步時鐘域之間數據傳輸所產生的亞穩態現象,以及如何降低亞穩態現象發生的概率(只能降低,不能消除),這在FPGA設計(尤其是大工程中)是非常重要的。 亞穩態的產生:所有的器件都定義了一個信號時序要

2018-06-22 14:49:49 3927

3927

在FPGA系統中,如果數據傳輸中不滿足觸發器的Tsu和Th不滿足,或者復位過程中復位信號的釋放相對于有效時鐘沿的恢復時間(recovery time)不滿足,就可能產生亞穩態,此時觸發器輸出端Q在有

2018-06-27 10:11:00 11080

11080

本文檔的主要內容詳細介紹的是正弦穩態電路的分析,重點內容有1.阻抗和導納 2. 正弦穩態電路的分析;3. 正弦穩態電路的功率分析;4.復功率 5最大功率傳輸

2018-07-25 08:00:00 7

7 亞穩態是指觸發器無法在某個規定時間段內達到一個可確認的狀態。

2018-09-22 08:25:00 10011

10011

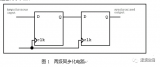

為了得到正確的空滿標志位,需要對讀寫指針進行同步。一般情況下,如果一個時鐘域的信號直接給另一個時鐘域采集,可能會產生亞穩態,亞穩態的產生對設計而言是致命的。為了減少不同時鐘域間的亞穩態問題,我們先對它進行兩拍寄存同步,如圖1所示。

2018-09-25 14:34:05 4003

4003

本文檔的主要內容詳細介紹的是控制系統的穩態特性穩態誤差分析詳細課件免費下載。

2018-11-22 08:00:00 7

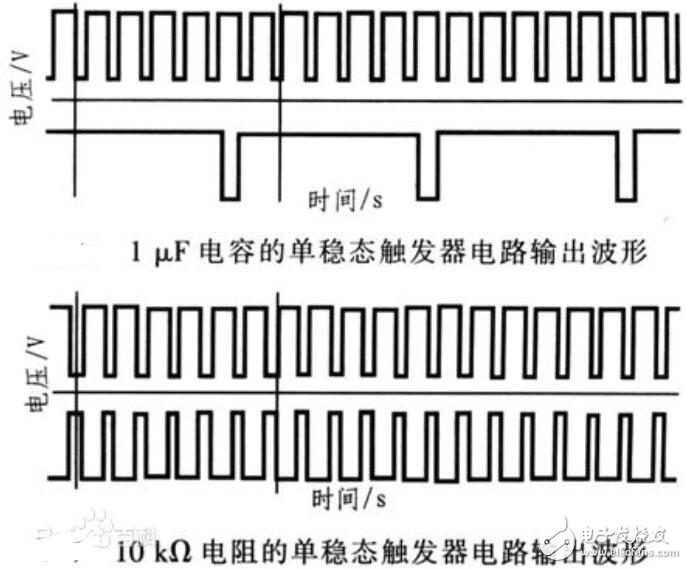

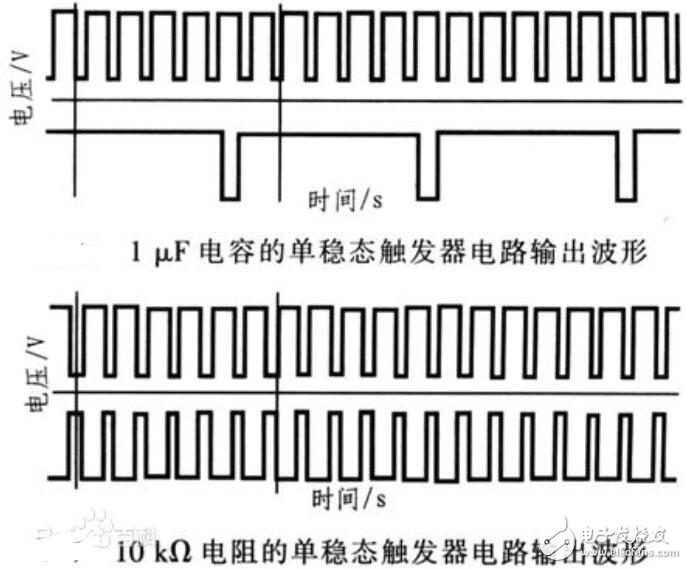

7 單穩態觸發器只有一個穩定狀態,一個暫穩態。在外加脈沖的作用下,單穩態觸發器可以從一個穩定狀態翻轉到一個暫穩態。由于電路中RC延時環節的作用,該暫態維持一段時間又回到原來的穩態,暫穩態維持的時間取決于RC的參數值。

2019-08-05 15:30:37 18165

18165

如此強調電子領域的熱條件,邏輯上必須保證特定類型的熱分析。一種這樣的分析形式稱為穩態熱分析,這是我們將要重點關注的。

2021-02-17 10:31:00 4230

4230 種這樣的分析形式稱為穩態熱分析,這是我們將要重點關注的。 什么是穩態? 在物理學領域中,穩態是不隨時間變化的穩定狀態,或者是一個方向的變化被另一方向的變化連續平衡的穩定狀態。在化學中,穩態是指盡管進行中的過程試圖更改它們

2021-01-14 14:56:28 10570

10570 硅可以通過硅的高壓金屬相-Sn 結構的Si-II在卸壓過程中發生相變而獲得,其轉變機理和相變路徑受溫度、壓強、加載速率、剪切應力、樣品尺寸等多種因素影響。然而,這些熱力學物理因素是如何耦合在一起影響到亞穩態硅的合成的

2020-10-17 10:25:26 4038

4038 本文是一篇詳細介紹ISSCC2020會議上一篇有關亞穩態解決方案的文章,該技術也使得FPGA在較高頻率下的時序收斂成為了可能。亞穩態問題是芯片設計和FPGA設計中常見的問題,隨著FPGA的發展,時序

2020-10-22 18:00:22 5277

5277

)不滿足,就可能產生亞穩態,此時觸發器輸出端 Q 在有效時鐘沿之后比較長的一段時間處于不確定的狀態,在這段時間里 Q 端在 0 和 1 之間處于振蕩狀態,而不是等于數據輸入端 D 的值。這段時間稱為決斷時間

2020-10-25 09:50:53 3120

3120

本文檔的主要內容詳細介紹的是正弦穩態電路的分析學習課件免費下載包括了:1.阻抗和導納,2電路的相量圖,3正弦穩態電路的分析,4正弦穩態電路的功率,5復功率,6最大功率傳輸

2020-11-03 17:30:47 17

17 在同步系統中,如果觸發器的setup time / hold time不滿足,就可能產生亞穩態,此時觸發器輸出端Q在有效時鐘沿之后比較長的一段時間處于不確定的狀態,在這段時間里Q端毛刺、振蕩、固定的某一電壓值,而不是等于數據輸入端D的值。

2021-03-09 10:49:23 2037

2037

電子發燒友網為你提供亞穩態的原理、起因、危害、解決辦法資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-30 08:45:27 9

9 電子發燒友網為你提供什么是亞穩態資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-16 08:43:07 24

24 今天寫一下時序問題常見的跨時鐘域的亞穩態問題。 先說明一下亞穩態問題: D觸發器有個明顯的特征就是建立時間(setup time)和保持時間(hold time) 如果輸入信號在建立時間和保持時間

2021-06-18 15:28:22 3606

3606 正弦電路的穩態分析:用相量法分析動態電路在正弦激勵下的穩態響應。

2021-06-19 16:12:10 2

2 亞穩態的概念 亞穩態是指觸發器無法在某個規定時間段內達到一個可確認的狀態。當一個觸發器進入亞穩態引時,既無法預測該單元的輸出電平,也無法預測何時輸出才能穩定在某個正確的電平上。在這個穩定期間,觸發器

2021-07-23 11:03:11 5493

5493

什么問題。 亞穩態 我們都知道數字電路中有兩個最重要的概念,建立時間和保持時間。通過滿足建立時間和保持時間,我們可以確保信號被正確的采樣,即1采到便是1,0采到便是0。但是如果不滿足建立時間和保持時間,采到的信號會進入一個不穩定的狀態,無法確定是1還是0,我們稱之

2021-08-25 11:46:25 2898

2898 電路理論的基礎知識之正弦穩態電路的分析

2022-01-13 13:53:47 0

0 可能很多FPGA初學者在剛開始學習FPGA設計的時候(當然也包括我自己),經常聽到類似于”這個信號需要打一拍、打兩拍(寄存),以防止亞穩態問題的產生“這種話,但是對這個打拍和亞穩態問題還是一知半解,接下來結合一些資料談下自己的理解。

2022-02-26 18:43:04 9404

9404

亞穩態問題是數字電路中很重要的問題,因為現實世界是一個異步的世界,所以亞穩態是無法避免的,并且亞穩態應該也是面試常考的考點。

2022-09-07 14:28:37 818

818 亞穩態問題是數字電路中很重要的問題,因為現實世界是一個異步的世界,所以亞穩態是無法避免的,并且亞穩態應該也是面試常考的考點。

2022-09-07 14:28:00 11347

11347 亞穩態是我們在設計經常遇到的問題。這個錯誤我在很多設計中都看到過。有人可能覺得不以為然,其實你現在沒有遇到問題只能說明。

2022-10-10 09:30:10 1217

1217 即使 “打兩拍”能阻止“亞穩態的傳遞”,但亞穩態導致后續FF sample到的值依然不一定是符合預期的值,那 “錯誤的值” 難道不依然會向后傳遞,從而造成錯誤的后果嗎?

2022-10-19 14:14:38 2179

2179 元器件在現實運行時,觸發器輸出的邏輯0/1需要時間跳變,而不是瞬發的。因此,若未滿足此cell的建立時間、保持時間,其輸出值則為中間態,那在logic上可能算成0也可能算成1很難講(波形顯示上可能是毛刺、振蕩、固定值等),這就是亞穩態。

2022-10-19 14:13:47 3942

3942 一個不穩定的狀態,無法確定是1還是0,我們稱之為亞穩態。這個亞穩態的信號會在一段時間內處于震蕩狀態,直到穩定,而穩定后的狀態值與被采樣值無關,可能是0也可能是1。

2022-12-12 14:27:52 1713

1713 看的東西多了,發現有些并未領會到位。單bit信號的跨時鐘域傳輸,可以使用兩級同步,但后果呢?

重復一下亞穩態,違反觸發器的時序特性,可能導致觸發器的輸出進入亞穩態,亞穩態不在0和1的電壓范圍內。數字電路的功能體現在0和1上,亞穩態可能導致功能錯誤

2023-05-11 16:24:07 1314

1314

本系列整理數字系統設計的相關知識體系架構,為了方便后續自己查閱與求職準備。對于FPGA和ASIC設計中,D觸發器是最常用的器件,也可以說是時序邏輯的核心,本文根據個人的思考歷程結合相關書籍內容和網上文章,聊一聊D觸發器與亞穩態的那些事。

2023-05-12 16:37:31 2934

2934

。

在材料制備和應用方面,亞穩態也常常是一個挑戰。如何克服亞穩態,使材料轉化為更穩定的狀態,是一個重要的問題。以下是一些克服亞穩態的方法:

2023-05-18 11:03:22 6015

6015 前面在時序分析中提到過亞穩態的概念,每天學習一點FPGA知識點(9)之時序分析并且在電路設計中如果不滿足Tsu(建立時間)和Th(保持時間),很容易就出現亞穩態;在跨時鐘域傳輸的一系列措施也是為了降低亞穩態發生的概率。

2023-05-25 15:55:43 2832

2832

? TI me)不滿足,就可能產生亞穩態,此時觸發器輸出端Q在有效時鐘沿之后比較長的一段時間處于不確定的狀態,在這段時間里Q端在0和1之間處于振蕩狀態,而不是等于數據輸入端D的值。這段時間稱為決斷時間(resoluTIon TIme)。經過resoluTIon time之后Q端將穩定到0或1上,但是穩定

2023-06-03 07:05:01 2490

2490 本文主要介紹了亞穩態的分析與處理。

2023-06-21 14:38:43 5126

5126

本系列整理數字系統設計的相關知識體系架構,為了方便后續自己查閱與求職準備。對于FPGA和ASIC設計中,D觸發器是最常用的器件,也可以說是時序邏輯的核心,本文根據個人的思考歷程結合相關書籍內容和網上文章,聊一聊D觸發器與亞穩態的那些事。

2023-07-25 10:45:39 2841

2841

亞穩態(Metastability)是由于輸入信號違反了觸發器的建立時間(Setup time)或保持時間(Hold time)而產生的。建立時間是指在時鐘上升沿到來前的一段時間,數據信號就要

2023-09-19 09:27:49 1841

1841

在《時鐘與復位》一文中已經解釋了亞穩態的含義以及亞穩態存在的危害。在單時鐘系統中,亞穩態出現的概率非常低,采用同步設計基本可以規避風險。但在實際應用中,一個系統往往包含多個時鐘,且許多時鐘之間沒有固定的相位關系,即所謂的異步時鐘域,這就給設計帶來很大的挑戰。

2023-09-19 09:32:45 4723

4723

說起亞穩態,首先我們先來了解一下什么叫做亞穩態。亞穩態現象:信號在無關信號或者異步時鐘域之間傳輸時導致數字器件失效的一種現象。

2023-09-19 15:18:05 3140

3140

停留在一個臨界狀態。這種亞穩態可能會引發一系列問題,包括設備故障和數據丟失等。因此,我們需要深入探討這個問題,并了解它的危險性。 第一部分:復位信號的作用和原理 復位信號是一種用于讓電子設備回到初始狀態的信號。

2024-01-16 16:25:56 1170

1170 兩級觸發器同步,就能消除亞穩態嗎? 兩級觸發器同步可以幫助消除亞穩態。本文將詳細解釋兩級觸發器同步原理、亞穩態的定義和產生原因、以及兩級觸發器同步如何消除亞穩態的機制。 1. 兩級觸發器同步

2024-01-16 16:29:38 2541

2541 無穩態是什么意思?單穩態是什么意思?雙穩態是什么意思?怎么區分這三種? 無穩態是指系統沒有達到穩定狀態,即系統的狀態隨時間變化而不斷變化,沒有趨于一個固定的平衡點。無穩態可以出現在許多不同的系統中

2024-02-18 16:26:21 3181

3181 在數字電路的設計與實現中,亞穩態是一個不可忽視的現象。它可能由多種因素引發,對電路的穩定性和可靠性產生嚴重影響。本文將深入探討數字電路中亞穩態的概念、產生原因、影響以及應對策略,以期為讀者提供全面而深入的理解。

2024-05-21 15:29:41 2945

2945 穩態誤差是控制系統中一個重要的性能指標,它反映了系統在達到穩態時,輸出與期望值之間的差異。在控制系統的設計和分析中,穩態誤差的分析和計算對于提高系統性能具有重要意義。 一、穩態誤差的概念 穩態誤差

2024-07-29 10:52:59 4131

4131 單穩態觸發器是一種數字邏輯電路,它具有一個穩定狀態和一個暫穩態。 單穩態觸發器的基本概念 單穩態觸發器是一種具有一個穩定狀態和一個暫穩態的數字邏輯電路。它的輸出在沒有輸入信號的情況下保持在一個穩定

2024-08-09 17:24:48 1964

1964 雙穩態觸發器(Bistable Trigger)是一種具有兩個穩定狀態的邏輯電路,廣泛應用于數字電路設計中。它具有兩個基本性質:記憶性和切換性。 一、雙穩態觸發器的基本概念 1.1 雙穩態觸發器

2024-08-11 10:08:05 1848

1848

電子發燒友App

電子發燒友App

評論