亞穩態的概念

亞穩態是指觸發器無法在某個規定時間段內達到一個可確認的狀態。當一個觸發器進入亞穩態引時,既無法預測該單元的輸出電平,也無法預測何時輸出才能穩定在某個正確的電平上。在這個穩定期間,觸發器輸出一些中間級電平,或者可能處于振蕩狀態,并且這種無用的輸出電平可以沿信號通道上的各個觸發器級聯式傳播下去。

亞穩態產生原因

在同步系統中,觸發器的建立/保持時間不滿足,就可能產生亞穩態。當信號在異步時鐘域或者不相關電路間傳輸時,往往導致亞穩態的產生。系統中有異步元件時,設計的電路要減少亞穩態導致錯誤的產生,其次要使系統對產生的錯誤不敏感。

異步時鐘域轉換的核心就是保證下級時鐘對上級時鐘數據采樣的 Setup 和 Hold 時間。如果觸發器的 Setup 和 Hold 時間不滿足,就可能產生亞穩態,此時觸發器輸出端 Q 在有效時鐘沿之后比較長的一段時間內處于不確定的狀態。

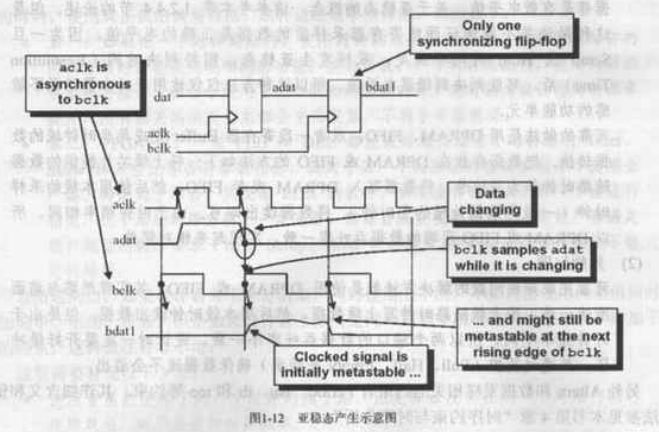

在這段時間內 Q 端產生毛刺并不斷振蕩,最終固定在某一電壓值,此電壓值并不一定等于原來數據輸入端 D 的數值,這段時間成為決斷時間(Resolution time)。經過 Resolution time 之后 Q 端將穩定到 0 或 1 上,但是究竟是0 或 1,這是隨機的,與輸入沒有必然的聯系,如下圖所示:

亞穩態的危害

亞穩態的危害主要體現在破壞系統的穩定性。由于輸出在穩定下來之前可能是毛刺,振蕩或固定的某一電壓值,因此亞穩態將導致邏輯誤判,嚴重情況下輸出 0 ~1 之間的中間電壓值還會使下一級產生亞穩態,即導致亞穩態傳播。邏輯誤判導致功能性錯誤,而亞穩態的傳播則擴大了故障面。

另外,在亞穩態狀態下,任何諸如環境噪聲、電源干擾等細微擾動豆漿導致更惡劣的狀態不穩定,這是這個系統的傳輸延遲增大,狀態輸出錯誤,在某些情況下甚至會使寄存器在兩個有效判定門限(VoL、VoH)之間長時間振蕩。

降低亞穩態發生概率的方法

只要系統中有異步元件,亞穩態就無法避免,因此設計的電路首先要減少亞穩態導致的錯誤,其次要使系統對產生的錯誤不敏感。前者要靠同步設計來實現,而后者根據不同的設計應用有不同的處理辦法。

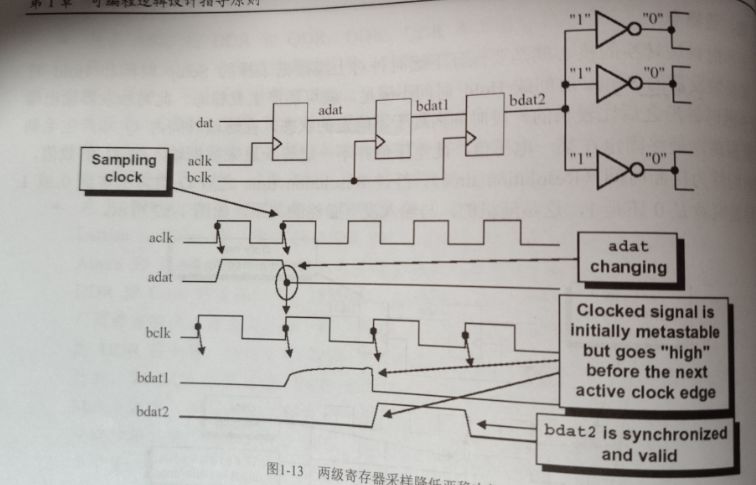

使用兩級寄存器采樣可以有效地減少亞穩態繼續傳播的概率。如下圖所示,左邊為異步輸入端,經過兩級觸發器采樣,在右邊的輸出與 bclk 同步,而且該輸出基本不存在亞穩態。其原理是及時第一個觸發器的輸出端存在亞穩態。

經過一個 Clk 周期后,第二個觸發器 D 端的電平仍未穩定的概率非常小,因此第二個觸發器 Q 端基本不會產生亞穩態。理論上如果再添加一級寄存器,使同步采樣達到 3 級,則末級輸出為亞穩態的概率幾乎為 0 。

用上圖所示的兩級寄存器采樣僅能降低亞穩態的概率,并不能保證第二級輸出的電平就是正確電平。前面說過經過 Resolution time 之后寄存器輸出的電平是一個不確定的穩定值,也就是說這種處理方法并不能排除采樣錯誤的產生,這時要求所設計的系統對采樣錯誤有一定的容忍度。

有些應用本身就對采樣錯誤不敏感,如一幀圖像編碼,一段語音編碼等;而有些系統對錯誤采樣比較敏感,這類由于亞穩態造成的采樣是一些突發的錯誤,所以可以采用一些糾錯編碼手段完成錯誤的糾正。

編輯:jq

-

FPGA

+關注

關注

1660文章

22411瀏覽量

636273

原文標題:FPGA中亞穩態的產生機理及其消除辦法

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

電力電子變換器中環流動力學:產生機理、利用策略與碳化硅(SiC) MOSFET技術的范式轉變

變頻器電磁干擾的產生機理及傳播途徑分析

淺析電源EMI產生機理

變頻器輸出端du/dt問題及其抑制措施研究

CD4047B:CMOS低功耗單穩態/無穩態多諧振蕩器的設計與應用

SiC功率模塊時代的電力電子系統共模電流產生的機理和抑制方法

隨鉆振動信號的產生機理、測量與井下處理方法

四種負電壓電源的產生原理及其應用場景

電容瞬態放電原理:大電流的產生機制

無軸承異步電機的不平衡振動補償控制

雙電機驅動攪拌器功率循環問題研究

華為面向中東中亞地區發布全新星河AI園區網絡

跨異步時鐘域處理方法大全

簡述FPGA中亞穩態的產生機理及其消除方法

簡述FPGA中亞穩態的產生機理及其消除方法

評論