表。 這4類路徑中,我們最為關心是②的同步時序路徑,也就是FPGA內部的時序邏輯。 時序模型 典型的時序模型如下圖所示,一個完整的時序路徑包括源時鐘路徑、數據路徑和目的時鐘路徑,也可以表示為觸發器+組合邏輯+觸發器的模型。 該

2020-11-17 16:41:52 3687

3687

習時把這一章分為兩節,它們分別是:§5、1 時序電路的概述§5、2 觸發器 5、1 時序電路的概述 這一節我們來學習一些關于時序電路的概念,在學習時要注意同步時序電路和異步時序電路的區別一:時序

2018-08-23 10:36:20

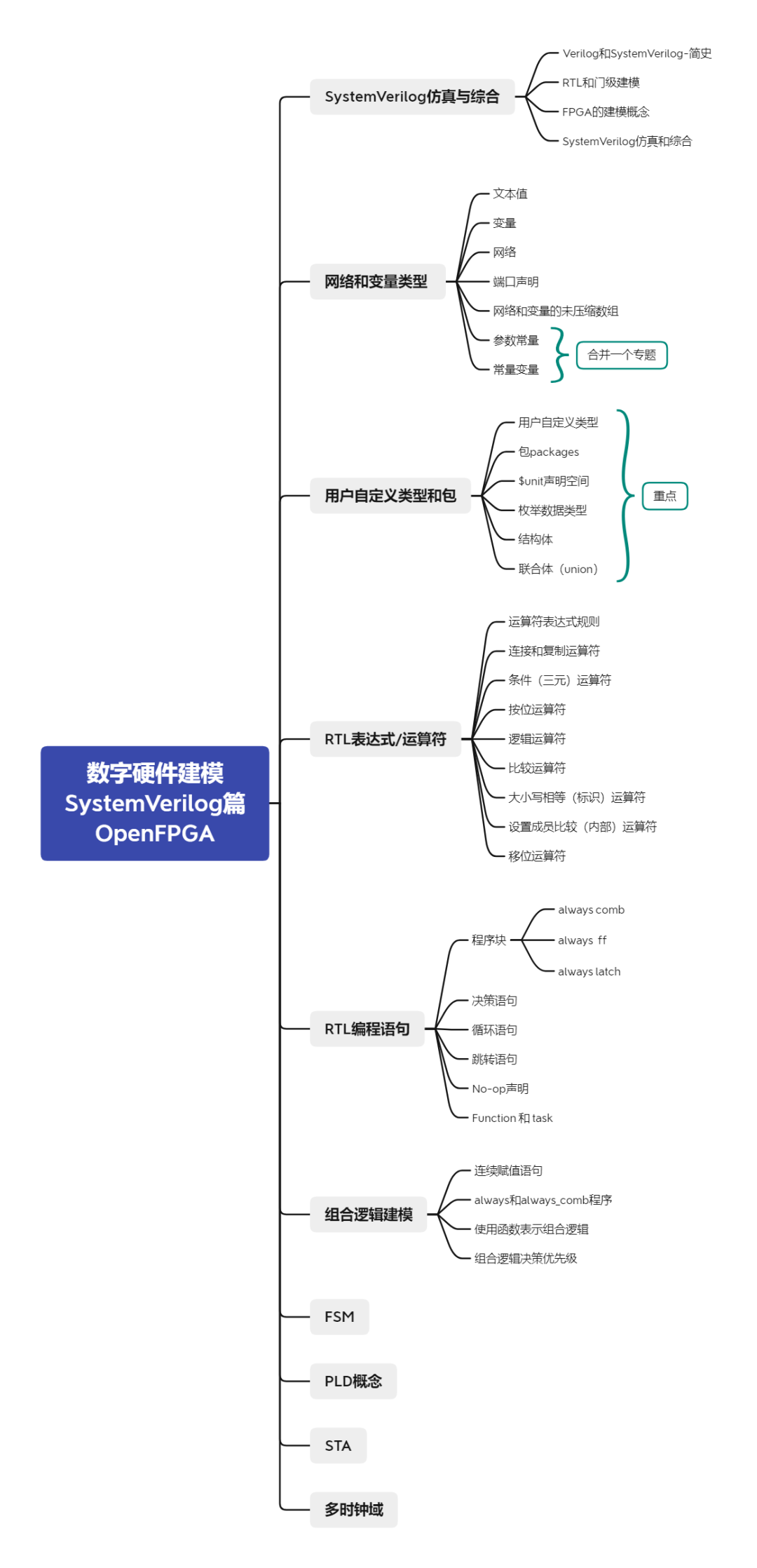

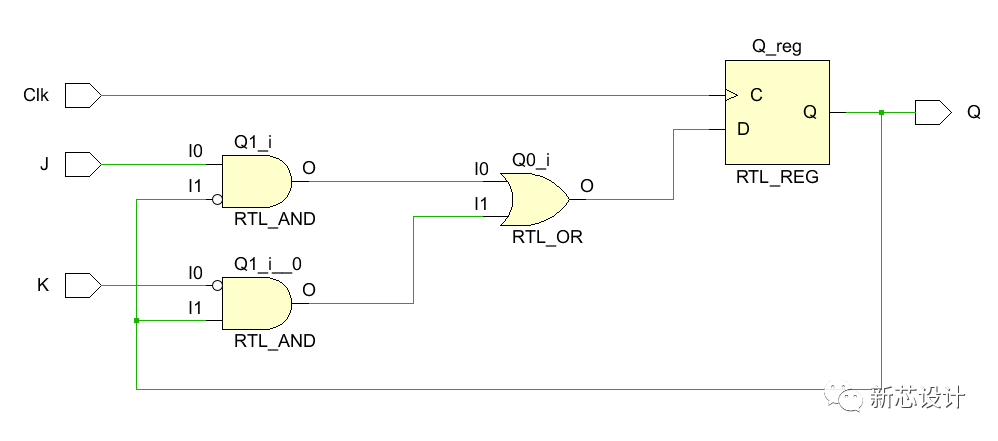

時序邏輯電路設計6.1 基本D觸發器的設計6.2 JK觸發器6.3 帶異步復位/置位端的使能T觸發器6.4 基本計數器的設計6.5 同步清零的計數器6.6 同步清零的可逆計數器6.7 同步預置數的計數器

2009-03-20 10:04:53

觸發器PPT電子教案:觸發器是構成時序邏輯電路的基本邏輯部件。? 它有兩個穩定的狀態:0狀態和1狀態;? 在不同的輸入情況下,它可以被置成0狀態或1狀態;? 當輸入信號消失后,所置成的狀態能夠保持

2009-09-16 16:06:45

觸發器實驗1)熟悉常用觸發器的邏輯功能及測試方法。2)了解觸發器邏輯功能的轉換。三.實驗內容及步驟 (1) 基本RS觸發器邏輯功能測試(2) JK觸發器邏輯功能測試(3) D觸發器邏輯功能的測試

2009-03-20 10:01:05

邊沿型觸發器的輸出有兩個穩定狀態: 高電平或者低電平。為保證可靠操作, 必須要滿足觸發器的時序要求,也就是我們熟知的建立時間和保持時間。如果輸入信號違反了觸發器的時序要求, 那么觸發器的輸出信號就有

2012-12-04 13:51:18

同步復位D觸發器復位信號在所需時鐘邊沿才有效,復位操作需要同步于時鐘故稱作同步復位。代碼如下[code]module d_ff (input clk,input rst_n,input D

2012-03-05 14:02:11

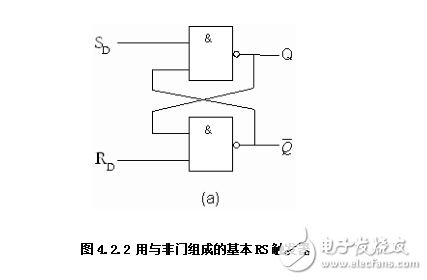

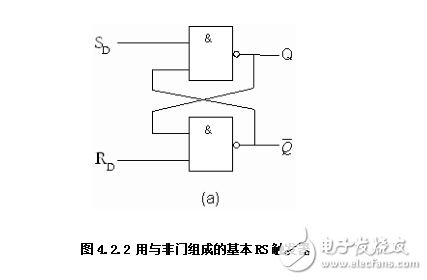

基本的SR NAND觸發器電路具有許多優點,并在順序邏輯電路中使用,但是它存在兩個基本的開關問題。1.必須始終避免設置= 0和復位= 0條件(S = R = 0)2.如果在啟用(EN)輸入為高時設置

2021-02-01 09:15:31

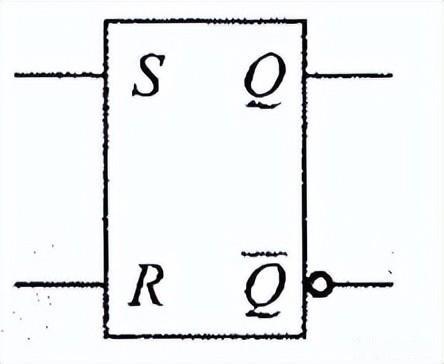

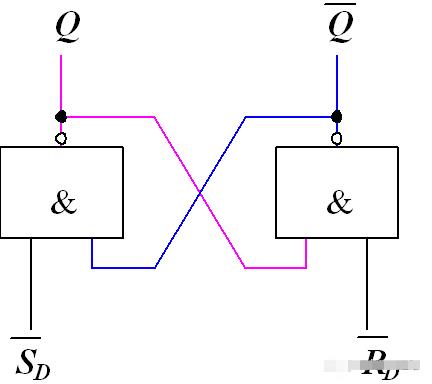

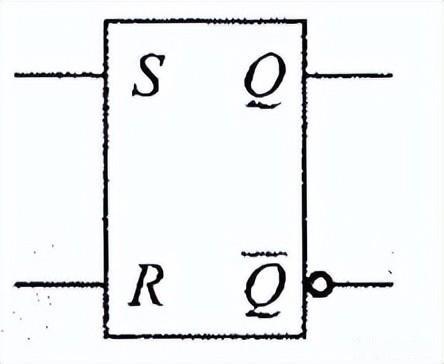

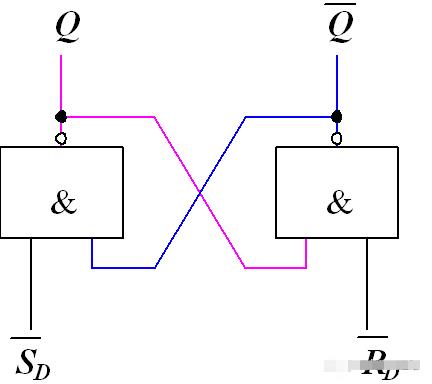

R-S觸發器是最基本的一種觸發器,它由兩個“與非”門組成。它有兩個輸入端,分別稱為置“0”端(也稱為復位端、R端)和置“1”端(也稱為置位端、S端);它有兩個輸出端,分別稱為Q端和Q端。并且規定:當

2019-12-25 17:21:56

專用的全局時鐘輸入引腳驅動單個主時鐘去控制設計項目中的每一個觸發器。同步設計時, 全局時鐘輸入一般都接在器件的時鐘端,否則會使其性能受到影響。 對于需要多時鐘的時序電路, 最好選用一個頻率是它們

2012-03-05 14:29:00

、加/減計數器,又稱可逆計數器。按計數器中觸發器翻轉是否同步可分為:異步計數器和同步計數器 。2.寄存器寄存器是存放數碼、運算結果或指令的電路,移位寄存器不但可存放數碼,而且在移位脈沖作用下,寄存器中

2016-10-25 23:03:31

什么是同步邏輯和異步邏輯?同步電路和異步電路的區別在哪?為什么觸發器要滿足建立時間和保持時間?什么是亞穩態?為什么兩級觸發器可以防止亞穩態傳播?

2021-08-09 06:14:00

本文來自芯社區,謝謝。1:什么是同步邏輯和異步邏輯? 同步邏輯是時鐘之間有固定的因果關系。異步邏輯是各時鐘之間沒有固定的因果關系。 同步時序邏輯電路的特點:各觸發器的時鐘端全部連接在一起,并接在系統

2021-07-26 08:26:57

寄存器,由寄存器又可以組成存儲器。觸發器是由基本邏輯門電路構成的,它有兩種輸出穩定狀態,稱作為“1”狀態和“0”狀態,分別代表它所寄存的代碼為“1”和“0”;它有兩個輸入端,用于接收代碼“1”和“0

2019-12-25 17:09:20

觸發器沒有使用相同的時鐘信號,需要分析哪些觸發器時鐘有效哪些無效分析步驟和同步時序電路一樣,不過要加上時鐘信號有關D觸發器的例題抄自慕課上的一個題目,注意第二個觸發器反相輸出端同時連接到復位端JK

2021-09-06 08:20:26

新課第五章 觸發器5.1 概述1、觸發器具有“記憶”功能,它是構成時序邏輯電路的基本單元。本章首先介紹基本RS觸發器的組成原理、特點和邏輯功能。然后引出能夠防止“空翻”現象的主從觸發器和邊沿觸發器。同時,較詳細地討論RS觸發器、JK觸發器、D觸發器、T觸發器、T'觸發器的邏輯功能及其描述方法。

2009-04-02 11:58:41

觸發器是構成時序邏輯電路的基本單元電路。

觸發器具有記憶功能,能存儲一位二進制數碼。

2025-03-26 14:21:19

RTL模型綜合結果。示例5-6:使用歸約運算符:使用異或的奇偶校驗//// Book, "RTL Modeling with SystemVerilog for ASIC and FPGA

2022-10-20 15:03:15

一、實驗目的1、掌握基本RS、JK、D和T觸發器的邏輯功能2、掌握集成觸發器的邏輯功能及使用方法3、熟悉觸發器之間相互轉換的方法二、實驗原理觸發器具有兩個穩

2008-12-19 00:40:23 49

49 實驗五 觸發器邏輯功能測試一、 實驗目的1、 熟悉并掌握RS、D、JL觸發器的構成、工作原理和功能測試方法2、 學會正確使用觸發器集成芯片二、 實

2009-03-20 17:56:32 108

108 同步時序邏輯電路:本章系統的講授同步時序邏輯電路的工作原理、分析方法和設計方法。從同步時序邏輯電路模型與描述方法開始,介紹同步時序邏輯電路的分析步驟和方法。然后

2009-09-01 09:06:27 0

0 提出了從狀態轉換圖中直接求得觸發器的置位和復位函數,從而確定觸發器的驅動方程這樣一種設計同步時序邏輯電路的新方法.設計原理簡單,易于理解,適合于所有同步時序

2010-02-28 19:23:02 15

15 5.1 基本RS觸發器5.2 時鐘控制的觸發器5.3 集成觸發器5.4 觸發器的邏輯符號及時序圖

2010-08-10 11:53:23 0

0 觸發器是時序邏輯電路中完成記憶功能的電路,是最基本的時序邏輯電路。

2010-08-12 16:20:24 0

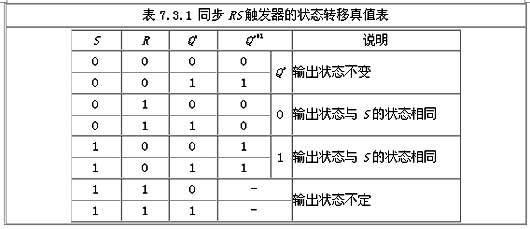

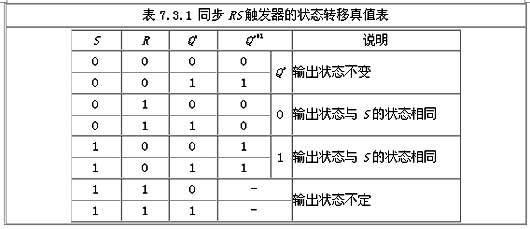

0 教學目標:1、 掌握鐘控同步RS觸發器的電路組成2、 掌握鐘控同步RS觸發器的工作原理及邏輯功能3、 了解觸發器的應用教學重難點:重點:鐘控同步 RS 觸

2010-08-18 14:57:41 16

16 一、基本要求1、理解R-S觸發器、J-K觸發器和D觸發器的邏輯功能;2、掌握觸發器構成的時序電路的分析,并了解其設計方法;3、理解計數器和寄存器的概念和功能,并掌握它

2010-08-26 11:40:22 57

57 組合電路和時序電路是數字電路的兩大類。門電路是組合電路的基本單元;觸發器是時序電路的基本單元。

2010-08-29 11:29:04 67

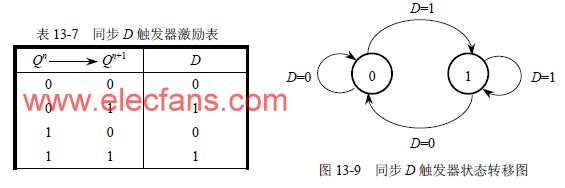

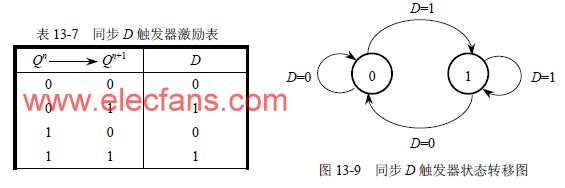

67 觸發器是時序邏輯電路的基本構成單元,按功能不同可分為 RS 觸發器、 JK 觸發器、 D 觸發器及 T 觸發器四種,其功能的描述可以使用功能真值表、激勵表、狀態圖及特性方程。

2010-09-30 16:03:26 90

90

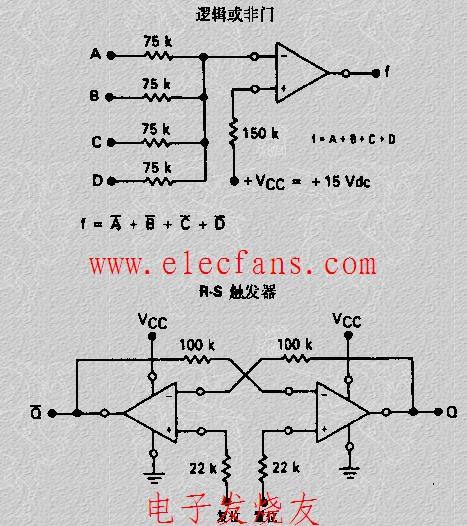

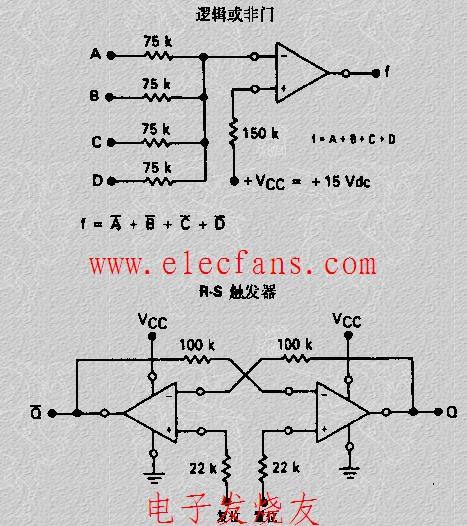

邏輯或非門-RS觸發器電路

2008-06-12 23:24:00 2898

2898

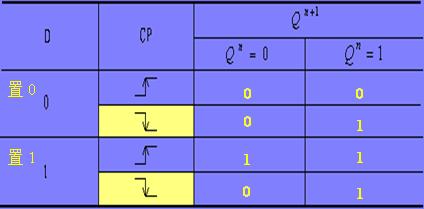

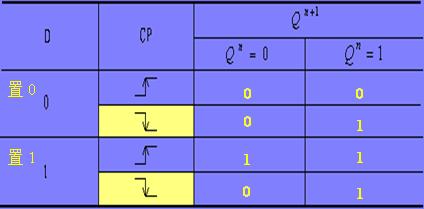

D觸發器

同步式D觸發器邏輯電路圖

D觸發器功能

2008-10-20 09:57:54 2818

2818

同步式D觸發器邏輯電路圖

2008-10-20 09:58:19 9218

9218

D觸發器邏輯功能表

同

2009-03-18 20:13:59 48810

48810

觸發器

一、 實驗目的

1. 學會測試觸發器邏輯功能的方法。 2. 進一步熟悉RS觸發器

2009-03-28 10:02:34 11216

11216

4.2.2 同步觸發器二、同步D觸發器1.電路結構2.邏輯功能3.特性方程4.狀態轉換圖三、同步JK觸發器1.電路結構2.邏輯功能3.特性方程4.狀態轉換

2009-03-30 16:17:07 5250

5250

第二十七講 同步時序邏輯電路的設計

7.5 同步時序邏輯電路的設計用SSI觸發器16進制以內7.5.1 同步時序邏輯電路的設計方法

2009-03-30 16:31:56 4192

4192

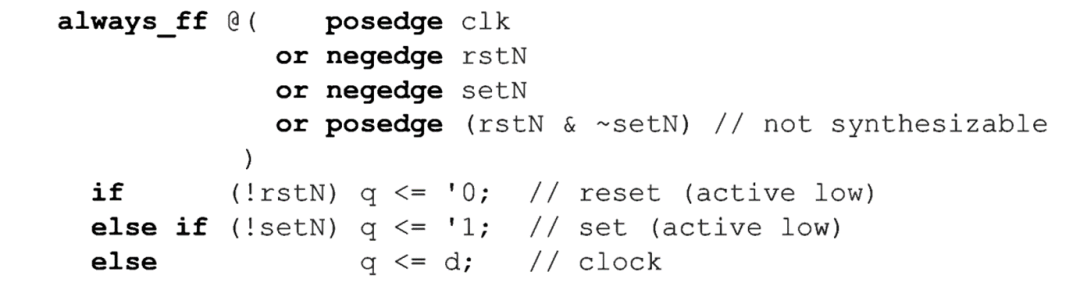

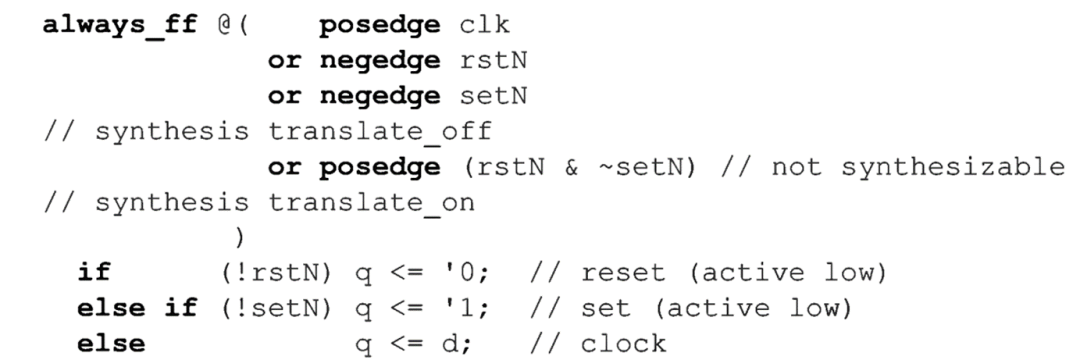

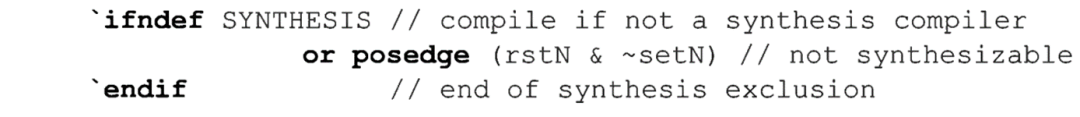

Verilog HDL語言實現時序邏輯電路

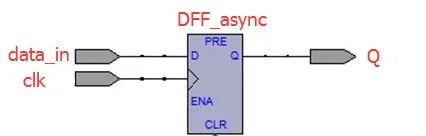

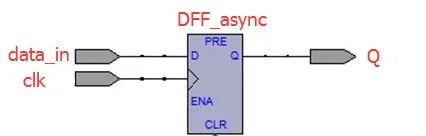

在Verilog HDL語言中,時序邏輯電路使用always語句塊來實現。例如,實現一個帶有異步復位信號的D觸發器

2010-02-08 11:46:43 5099

5099 時序邏輯電路實例解析

一、觸發器 1、電位觸發方式觸發器

2010-04-15 13:46:25 6161

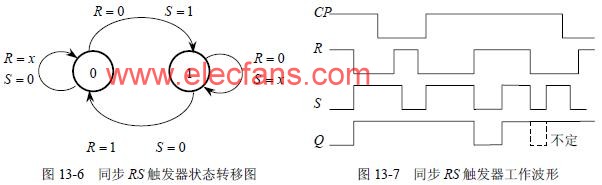

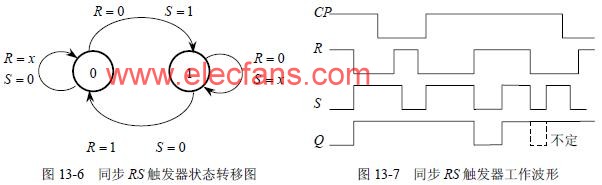

6161 由與非門構成的同步RS觸發器如圖13-5(a)所示,其邏輯符號如圖13-5(b)所示。圖中門A和B構成基本觸發器,門C和E構成觸發引導電路。由圖13-5(a)可見,基本觸發器的輸

2010-08-18 09:00:00 17146

17146

為了避免同步RS觸發器的輸入信號同時為1,可以在S和R之間接一個“非門”,信號只從S端輸入,并將S端改稱為數據輸入端D,如圖15-8所示。這種單輸入的觸發器稱為

2010-08-18 09:06:00 13148

13148

一、空翻問題由于在CP=1期間,同步觸發器的觸發引導門都是開放的,觸發器都可以接收輸入信號而翻轉,所以在CP=1期間,如果輸入信號發生多次變化,觸發器的

2010-08-18 09:08:32 22815

22815

本次重點內容:1、觸發器的概念和分類。2、同步觸發器、主從觸發器、邊沿觸發器的含義。

4.1.1 觸發器概述一、觸發

2010-08-19 08:57:47 20522

20522 0 引言 觸發器是具有存儲功能的器件,在數字電子技術中用于構成各種時序邏輯電路。觸發器有多

2010-10-11 10:20:17 15534

15534 觸發器是一個具有記憶功能的,具有兩個穩定狀態的信息存儲器件,是構成多種時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。在數字系統和計算機中有著廣泛的應用。觸發器具有兩個穩定狀態,即“0”和“1”,在一定的外界信號作用下,可以從一個穩定狀態翻轉到另一個穩定狀態。

2017-08-19 09:21:00 17038

17038

觸發器是一個具有記憶功能的,具有兩個穩定狀態的信息存儲器件,是構成多種時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。在數字系統和計算機中有著廣泛的應用。觸發器具有兩個穩定狀態.

2017-11-02 08:53:42 61658

61658 觸發器是一個具有記憶功能的,具有兩個穩定狀態的信息存儲器件,是構成多種時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。在數字系統和計算機中有著廣泛的應用。觸發器具有兩個穩定狀態

2017-12-12 17:20:40 86395

86395

按照穩定工作狀態分,可分為雙穩態觸發器、單穩態觸發器、無穩態觸發器(多諧振蕩器)等;按照邏輯功能劃分,可分為RS觸發器、D觸發器、T觸發器、JK觸發器等幾類;按照電路結構劃分,可分為基本RS觸發器、同步觸發器(時鐘控制的觸發器)、主從型觸發器、維持-阻塞型觸發器和邊沿觸發器等幾種類型。

2018-01-31 15:02:50 29042

29042

時序邏輯電路是由組合邏輯電路與記憶電路(又稱存儲電路) 組合而成的。 常見時序邏輯電路有觸發器、 寄存器和計數器等。

2019-02-26 15:25:01 52417

52417 將驅動方程代入相應觸發器的特性方程中,便得到該觸發器的次態方程。時序邏輯電路的狀態方程由各觸發器次態的邏輯表達式組成。

2019-02-28 14:06:14 25600

25600 D觸發器是一個具有記憶功能的,具有兩個穩定狀態的信息存儲器件,是構成多種時序電路的最基本邏輯單元,也是數字邏輯電路中一種重要的單元電路。

2019-12-02 07:06:00 8199

8199

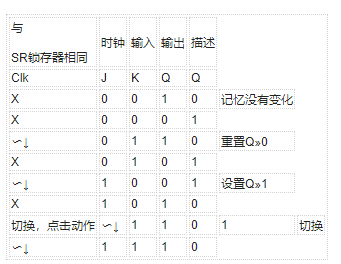

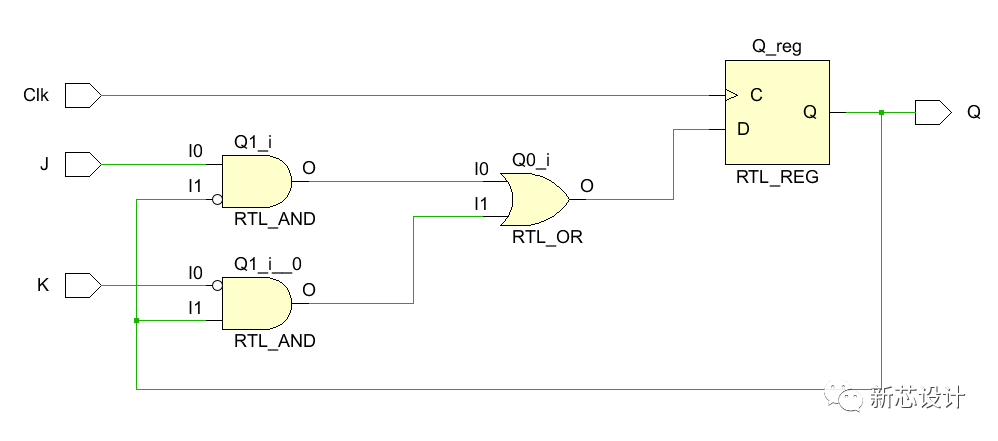

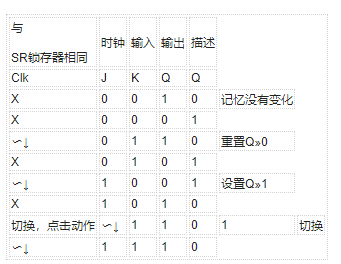

JK觸發器類似于SR觸發器,但當J和K輸入均為低電平時,狀態沒有變化,JK觸發器的順序操作與前一個具有相同“設置”和“復位”輸入的SR觸發器完全相同。這次的不同之處在于,即使 S 和 R 都處于邏輯“1”,“JK觸發器”也沒有SR Latch的無效或禁止輸入狀態。

2019-06-26 15:56:51 7221

7221

首選我們來聊聊時序邏輯中最基礎的部分D觸發器的同步異步,同步復位即復位信號隨系統時鐘的邊沿觸發起作用,異步復位即復位信號不隨系統時鐘的邊沿觸發起作用,置數同理,rst_n表示低電平復位,我們都知道D

2019-07-26 10:17:16 27982

27982

JK觸發器是數字電路觸發器中的一種基本電路單元。JK觸發器具有置0、置1、保持和翻轉功能,在各類集成觸發器中,JK觸發器的功能最為齊全。在實際應用中,它不僅有很強的通用性,而且能靈活地轉換其他類型的觸發器。由JK觸發器可以構成D觸發器和T觸發器。

2019-11-08 14:48:44 96918

96918

產生毛刺,且易受環境的影響,不利于器件的移植; 同步電路 1. 電路的核心邏輯是由各種各樣的觸發器實現的,所以比較容易使用寄存器的異步復位/置位端,以使整個電路有一個確定的初始狀態; 2. 整個電路是由時鐘沿驅動的; 3. 以觸發器為主體的同步時序電

2020-12-05 11:53:41 12647

12647 復位/置位觸發器(R、S分別是英文復位,置位的縮寫)也叫做基本R-S觸發器,是最簡單的一種觸發器,是構成各種復雜觸發器的基礎。

2021-06-30 17:13:06 116513

116513

沒有任何寄存器邏輯,RTL設計是不完整的。RTL是寄存器傳輸級或邏輯,用于描述依賴于當前輸入和過去輸出的數字邏輯。

2022-03-15 10:56:04 4623

4623 明德揚有完整的時序約束課程與理論,接下來我們會一章一章以圖文結合的形式與大家分享時序約束的知識。要掌握FPGA時序約束,了解D觸發器以及FPGA運行原理是必備的前提。今天第一章,我們就從D觸發器開始講起。

2022-07-11 11:33:10 6143

6143

復位信號在數字電路里面的重要性僅次于時鐘信號。對一個芯片來說,復位的主要目的是使芯片電路進入一個已知的,確定的狀態。主要是觸發器進入確定的狀態。在一般情況下,芯片中的每個觸發器都應該是可復位的。

2022-09-19 10:07:20 35609

35609 什么是RS觸發器 其中R、S分別是英文復位 Reset 和置位 Set 的縮寫,作為最簡單的一種觸發器,是構成各種復雜觸發器的基礎。RS觸發器的邏輯電路圖如下圖所示。 RS觸發器可以用與非門實現或者

2022-10-19 17:49:59 15092

15092

SystemVerilog有三種在可綜合RTL級別表示組合邏輯的方法:連續賦值語句、always程序塊和函數。接下來幾篇文章將探討每種編碼風格,并推薦最佳實踐編碼風格。

2022-12-07 15:31:47 2361

2361 其中R、S分別是英文復位Reset和置位Set的縮寫,作為最簡單的一種觸發器,是構成各種復雜觸發器的基礎。RS觸發器的邏輯電路圖如下圖所示。

2023-02-08 09:19:45 11327

11327 帶復位功能的雙 JK 觸發器;下降沿觸發-74HC73

2023-02-15 19:33:13 3

3 帶復位功能的雙 JK 觸發器;下降沿觸發-74HC_HCT107

2023-02-16 19:58:24 2

2 時序邏輯的代碼一般有兩種: 同步復位的時序邏輯和異步復位的時序邏輯。在同步復位的時序邏輯中復位不是立即有效,而在時鐘上升沿時復位才有效。 其代碼結構如下:

2023-03-21 10:47:07 1239

1239 在電路中,觸發器(Flip-flop)是一種組合邏輯電路,可以存儲1個二進制位的信息。 觸發器有兩個穩定的狀態:SET(置位)和RESET(復位)。 當輸入信號滿足某些條件時,觸發器可以從一個狀態轉換到另一個狀態。

2023-03-23 11:45:39 16377

16377

觸發器是構成時序邏輯電路的基本單元。它是一種具有記憶功能,能儲存1位二進制信息的邏輯電路。在之前的文章中已經介紹過觸發器了,這里再介紹一下其他類型的觸發器。

2023-03-23 15:13:26 19700

19700

本文旨在總結近期復習的數字電路D觸發器(邊沿觸發)的內容。

2023-05-22 16:54:29 22343

22343

時序邏輯電路分析和設計的基礎是組合邏輯電路與觸發器,所以想要分析和設計,前提就是必須熟練掌握各種常見的組合邏輯電路與觸發器功能,尤其是各種觸發器的特征方程與觸發模式,因此前幾文的基礎顯得尤為重要。 本文主要介紹時序邏輯電路的分析方法。

2023-05-22 18:24:31 5502

5502

異步復位觸發器則是在設計觸發器的時候加入了一個復位引腳,也就是說**復位邏輯集成在觸發器里面**。(一般情況下)低電平的復位信號到達觸發器的復位端時,觸發器進入復位狀態,直到復位信號撤離。帶異步復位的觸發器電路圖和RTL代碼如下所示:

2023-05-25 15:57:17 1867

1867

RS觸發器是一種常見的數字邏輯門電路元件,它由兩個相互反饋的邏輯門組成。RS觸發器的邏輯功能可以描述為存儲器元件或雙穩態開關。

2023-08-07 16:17:32 18971

18971 zabbix觸發器表達式 基本RS觸發器表達式 rs觸發器的邏輯表達式? Zabbix是一款開源的監控軟件,它能通過監控指標來實時監測服務器和網絡的運行狀態,同時還能提供警報和報告等功能來幫助管理員

2023-08-24 15:50:08 2335

2335 觸發器(Flip-Flop)是數字電路中的一種時序邏輯元件,用于存儲二進制位的狀態。它是數字電路設計中的基本構建塊之一,常用于存儲數據、實現狀態機、控制信號的生成等。觸發器可以看作是一種特殊

2023-08-31 10:50:19 20343

20343

在數字電路中,RS觸發器(也稱為RS鎖存器)是一種基本的雙穩態觸發器,它可以通過特定的輸入信號來實現置位(Set)和復位(Reset)操作。

2023-09-28 16:31:07 11269

11269 D觸發器,是時序邏輯電路中必備的一個基本單元,學好 D 觸發器,是學好時序邏輯電路的前提條件,其重要性不亞于加法器,二者共同構成數字電路組合、時序邏輯的基礎。

2023-10-09 17:26:57 6026

6026

JK 觸發器的 Verilog 代碼實現和 RTL 電路實現

2023-10-09 17:29:34 6642

6642

的邏輯功能及其應用。 首先,RS觸發器的邏輯功能包括兩個主要部分:設置和復位。設置輸入(S)用于設置觸發器的輸出為“1”,即存儲1的功能;復位輸入(R)用于復位觸發器的輸出為“0”,即清零的功能。RS觸發器的邏輯功能可以通過其

2023-11-17 16:01:56 7552

7552 RS觸發器是一種經典的數字邏輯電路元件,用于存儲和控制信息流。它是由兩個反饋作用的邏輯門組成,常用于時序電路和數據存儲。 RS觸發器由兩個互補的輸出Q和~Q組成,其中Q表示觸發器的狀態為"1",~Q

2023-11-17 16:14:28 4298

4298 端的狀態。在本文中,我將詳細介紹置位和復位的含義、功能和應用。 首先,讓我們來解釋置位和復位的意思。在RS觸發器中,置位就是將輸出端Q置為高電平(邏輯1),而復位則是將輸出端Q置為低電平(邏輯0)。當R和S輸入均為邏輯0時,無論之前輸出是什么,觸發器

2023-11-17 16:19:45 10681

10681 電子發燒友網站提供《rs觸發器的邏輯功能.zip》資料免費下載

2023-11-20 14:18:26 0

0 回路。在RS觸發器中,R和S分別代表復位(Reset)和設置(Set)輸入。當RS觸發器處于不穩定狀態時,這兩個輸入可以控制其狀態改變。 以下是RS觸發器的邏輯表達式: Q(t+1) = (S' * Q(t)) + (R * Q'(t)) 其中,Q(t+1)是觸發器的下一個狀態,表示在時間

2024-01-12 14:09:48 4551

4551 如果只做一級觸發器同步,如何? 一級觸發器同步是指只考慮最基礎的觸發信息進行同步,而不考慮更高層次的關聯觸發信息。在這篇文章中,我將詳細介紹一級觸發器同步的概念、原理、應用和局限性,以及一些相關

2024-01-16 16:29:35 1027

1027 RS觸發器是一種基本的數字邏輯電路,它由兩個互補的反饋連接組成。RS觸發器可以用作其他高級邏輯電路的構建模塊,如計數器、移位寄存器和內存單元等。本文將詳細介紹RS觸發器的實現原理、功能和應用。 一

2024-01-17 14:24:17 5885

5885 RS觸發器與SR觸發器都是基本的數字邏輯電路元件,常用于存儲、控制和時序電路中。

2024-01-29 14:15:08 8676

8676 D觸發器是一種常見的數字邏輯電路,它在數字系統和計算機中扮演著重要的角色。本文將詳細探討D觸發器的邏輯功能、工作原理以及RD(Reset-D)觸發器和SD(Set-D)觸發器的作用。 首先,我們先來

2024-02-06 13:52:14 52523

52523 觸發器是數字電路中常用的組合邏輯電路,在現代電子系統中有著廣泛的應用。其中,最常用的兩種觸發器是T觸發器和JK觸發器。本文將詳細介紹T觸發器和JK觸發器的區別和聯系。 一、T觸發器 T觸發器是一種單

2024-02-06 14:04:55 7821

7821 的觸發器,其輸入信號作用于觸發器,觸發器將根據輸入信號進行狀態切換。本文將詳細介紹如何使用JK觸發器構成T觸發器,并介紹T觸發器的邏輯功能。 一、JK觸發器的邏輯功能 JK觸發器具有四種基本的邏輯功能,分別是保持、復位、設置和反轉。 保持:

2024-02-06 14:11:11 12517

12517 在數字電路設計中,觸發器和時序邏輯電路是構建復雜數字系統不可或缺的基礎元素。觸發器(Flip-Flop)作為基本的存儲單元,能夠存儲一位二進制信息,并在特定的時鐘信號控制下更新其狀態。而時序邏輯

2024-07-18 17:43:41 4403

4403 JK觸發器的置位(Set)和復位(Reset)是其在數字電路中的兩種基本狀態控制功能,它們在操作原理、輸入條件以及觸發器輸出狀態的變化上有所區別。以下是對JK觸發器置位和復位的詳細分析。

2024-07-27 14:50:54 4926

4926 定義: 主從觸發器(Master-Slave Trigger)是一種用于實現時鐘同步的觸發器結構,它由兩個觸發器組成,一個為主觸發器(Master Trigger),另一個為從觸發器(Slave

2024-08-11 09:21:38 2229

2229 在數字電路設計中,觸發器是一種非常重要的基本邏輯元件,用于存儲一位二進制信息。觸發器的種類繁多,但主要分為兩大類:主從觸發器(Master-Slave Flip-Flop)和邊沿觸發器

2024-08-11 09:35:02 4850

4850 RS觸發器是一種常見的數字邏輯門電路元件,其邏輯功能可以描述為存儲器元件或雙穩態開關。它由兩個相互反饋的邏輯門組成,通常是非門或與非門的組合,具有兩個輸入端(R和S)和兩個輸出端(Q和Q')。這里的R和S分別代表“Reset”(復位)和“Set”(置位),它們共同控制觸發器的輸出狀態。

2024-08-12 10:19:04 13909

13909 同步觸發器和邊沿觸發器是數字電路中兩種常見的觸發器類型,它們在觸發方式、工作原理、性能特點以及應用場景等方面存在顯著的差異。

2024-08-12 11:26:01 3572

3572 是一種具有記憶功能的數字電路元件,可以存儲一位二進制信息。它通常由邏輯門、觸發器存儲元件和反饋回路組成。觸發器的輸出狀態取決于輸入信號和當前狀態。 1.2 觸發器的分類 觸發器按照功能和結構的不同,可以分為多種類型,如SR觸發器、JK觸

2024-08-22 10:33:51 3765

3765 引言 數字電路是現代電子技術的基礎,廣泛應用于計算機、通信、控制等領域。觸發器是數字電路中的一種基本邏輯元件,具有存儲和傳遞信息的功能。 觸發器的基本概念 觸發器是一種具有記憶功能的數字電路元件

2024-08-22 10:37:33 5059

5059 JK觸發器 :具有四種基本的邏輯功能,分別是保持、復位、設置和反轉。這些功能由J和K兩個輸入端口的信號共同決定。 T觸發器 :具有單一的輸入端口T,用于控制觸發器的狀態翻轉。當T=1時,觸發器在時鐘信號的觸發下翻轉狀態;當T=0時,觸發器保持當

2024-08-28 09:41:19 6044

6044 邊沿JK觸發器是一種數字邏輯電路,廣泛應用于數字電路設計中。它具有多種功能,包括同步操作、存儲數據、實現時序邏輯等。以下是對邊沿JK觸發器功能的分析: 同步操作 邊沿JK觸發器是一種同步觸發器,它在

2024-08-28 09:50:12 2291

2291 時序邏輯電路是數字電路中的一種重要類型,它具有存儲和處理信息的能力。時序邏輯電路的結構特點主要包括以下幾個方面: 存儲元件 時序邏輯電路中最基本的存儲元件是觸發器(Flip-flop)。觸發器是一種

2024-08-28 11:07:26 1505

1505 狀態信息和當前的輸入信號來產生輸出。 具體來說,時序邏輯電路中的存儲電路通常由觸發器(Flip-flops)組成,觸發器是時序邏輯電路的基本存儲單元。觸發器可以存儲一位二進制信息,并在時鐘信號的控制下根據輸入信號的變化改變其

2024-08-28 14:12:09 1490

1490 RS觸發器(也稱為置位/復位觸發器)是一種基本的數字邏輯電路,用于存儲一位二進制信息。它有兩個輸入端:置位(Set)和復位(Reset),以及兩個輸出端:Q和Q'(Q的反相輸出)。 RS觸發器

2024-10-21 10:03:07 2198

2198 RS觸發器(Reset-Set觸發器)是一種基本的數字邏輯電路,用于存儲一位二進制信息。它由兩個輸入端(R和S)和一個輸出端(Q)組成,其中R代表復位(Reset),S代表置位(Set)。RS觸發器

2024-10-21 10:04:23 7434

7434

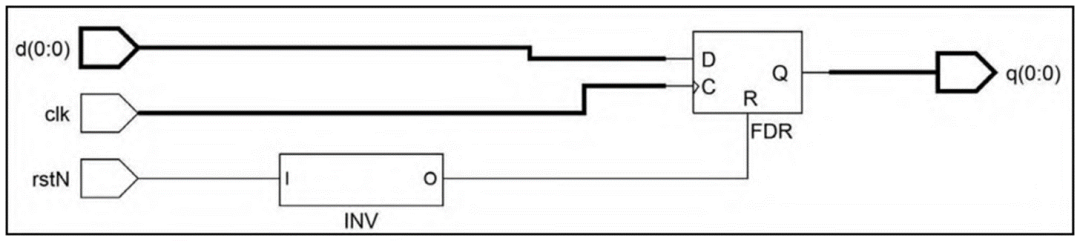

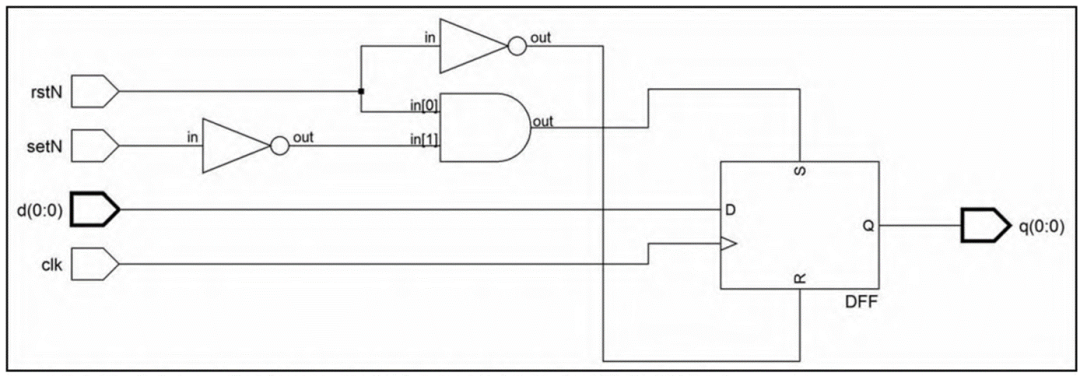

圖 8-7: 綜合結果。異步復位DFF映射到Xilinx Virtex -7 FPGA中

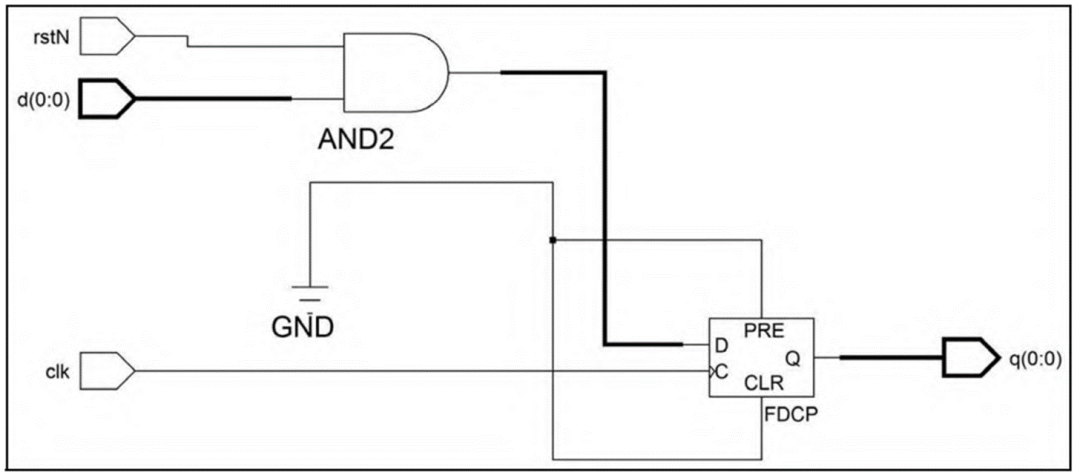

圖 8-7: 綜合結果。異步復位DFF映射到Xilinx Virtex -7 FPGA中 圖8-8:綜合結果。映射到Xilinx CoolRunner-11 CPLD的異步復位

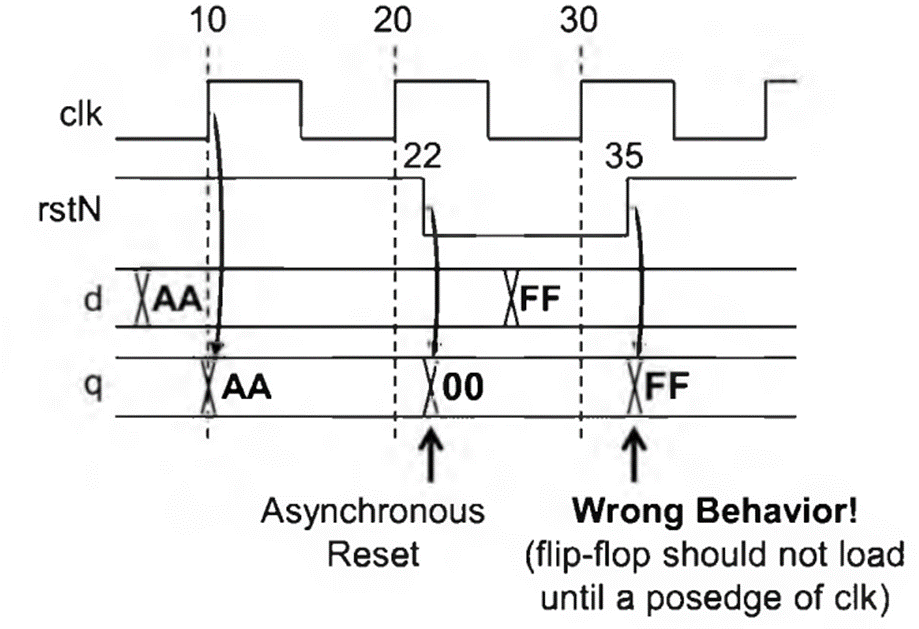

圖8-8:綜合結果。映射到Xilinx CoolRunner-11 CPLD的異步復位 圖8-9:不正確建模的異步復位結果的波形

圖8-9:不正確建模的異步復位結果的波形

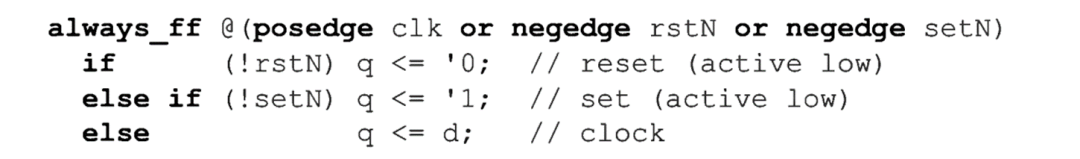

圖8-12:一個異步置位-復位觸發器的綜合結果

圖8-12:一個異步置位-復位觸發器的綜合結果

電子發燒友App

電子發燒友App

評論