本文主要介紹的是FPGA的片上資源使用情況,分別是從組合邏輯及時序邏輯來詳細的分析。

2018-04-18 09:06:24 18789

18789

關注FPGA,那么世界將拋棄你,時代將拋棄你。本公眾號作者ALIFPGA,多年FPGA開發經驗,所有文章皆為多年學習和工作經驗之總結。 邏輯寫多了,有時候一些基本的錯誤忘了避免了。 昨天設計邏輯的時候就不小心觸雷了,有個信號有激勵沒響應,后來看

2018-05-08 10:27:30 2342

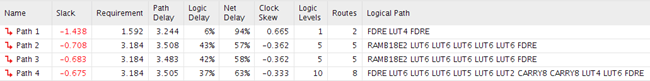

2342 信號在FPGA器件中通過邏輯單元連線時,一定存在延時。延時的大小不僅和連線的長短和邏輯單元的數目有關,而且也和器件的制造工藝、工作電壓、溫度等有關。

2020-03-29 10:27:00 4067

4067 前邊寫了很多關于板上外圍器件的評測文章,這篇是FPGA純邏輯設計,是FPGA的另一部分——算法實現,上篇文章做了HDC1000傳感器的使用,當時說FPGA是不支持小數的,本篇記述的是FPGA如何去做

2020-06-17 10:17:27 8274

8274

和性能。? 由于硬件復雜性不斷增加,需要驗證的相關軟件數量不斷增加,因此它今天的使用范圍更加廣泛。? 為什么公司使用FPGA原型?? FPGA已經被用于驗證相對成熟的RTL,因為它們可以代表一個近乎精確的以高速運行的設計的復制品。這些復制品通常也足夠便攜,可用于現

2022-07-19 16:27:29 2400

2400 只有在腦海中建立了一個個邏輯模型,理解FPGA內部邏輯結構實現的基礎,才能明白為什么寫Verilog和寫C整體思路是不一樣的,才能理解順序執行語言和并行執行語言的設計方法上的差異。在看到一段簡單程序的時候應該想到是什么樣的功能電路。

2022-08-25 11:12:00 1318

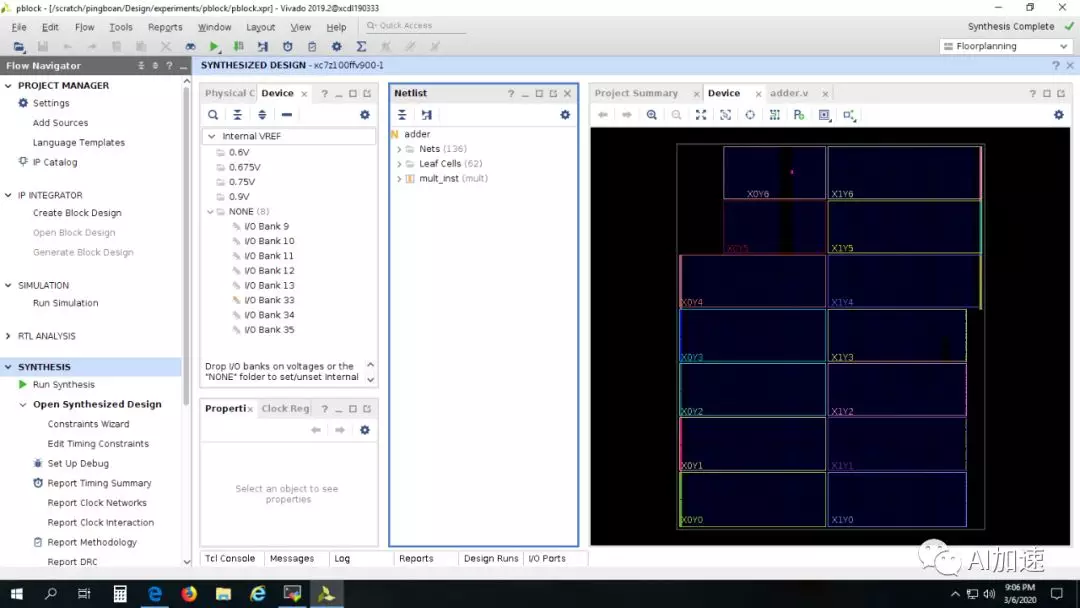

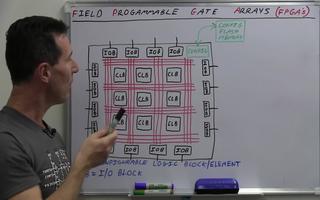

1318 輸入輸出端口 從Implemented Design中可以看到FPGA中資源大致分布如下。中間藍色是CLB可編程邏輯塊、DSP或BRAM,兩側的彩色矩形塊是I/O接口和收發器,劃分的方塊是不同的時鐘域 Configurable Logic Block (CLB)可編程邏

2022-12-27 15:54:52 3346

3346 數字邏輯電路分為組合邏輯電路和時序邏輯電路。時序邏輯電路是由組合邏輯電路和時序邏輯器件構成(觸發器),即數字邏輯電路是由組合邏輯和時序邏輯器件構成。

2023-03-21 09:49:49 1443

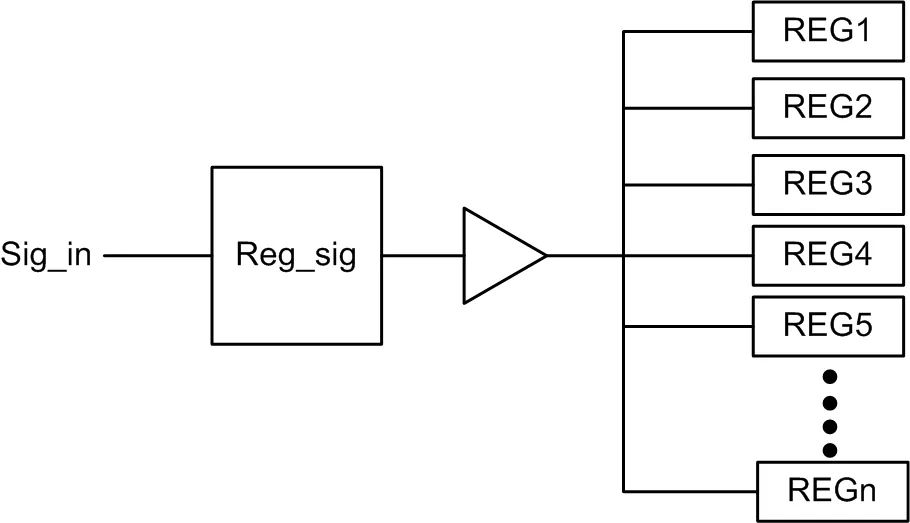

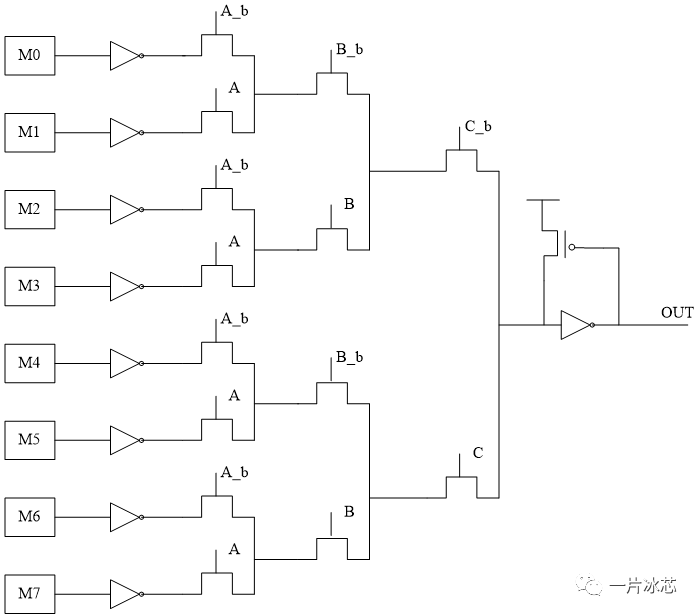

1443 在進行FPGA原型驗證的過程中,當要把大型的SoC進行FPGA原型驗證時,有時候會遇到一種情況,同樣的接口分兩組出去到不同的模塊,而這兩個模塊規模較大,又需要分割在兩片FPGA中,這時候就會像下圖一樣:

2023-04-25 11:15:20 2534

2534

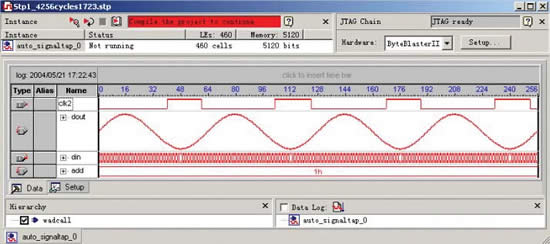

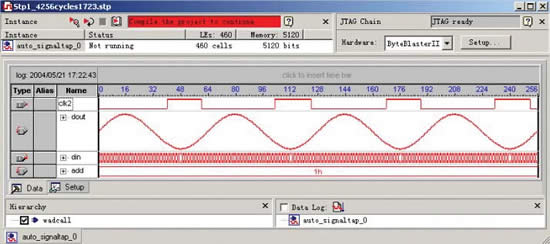

其中待測設計就是我們整個的邏輯設計模塊,在線邏輯分析儀也同樣是在FPGA設計中。通過一個或多個探針來采集希望觀察的信號。然后通過JTAG接口,將捕獲到的數據通過下載器回傳給我們的用戶界面,以便我們進行觀察。

2023-07-25 09:52:58 1764

1764

邏輯單元在FPGA器件內部,用于完成用戶邏輯的最小單元。

2023-10-31 11:12:12 3300

3300

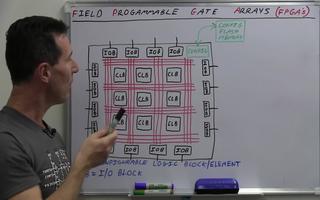

可編程邏輯功能塊(Configurable Logic Blocks, CLB),顧名思義就是可編程的數字邏輯電路,可以實現各種邏輯功能。

2023-10-31 18:24:09 2475

2475

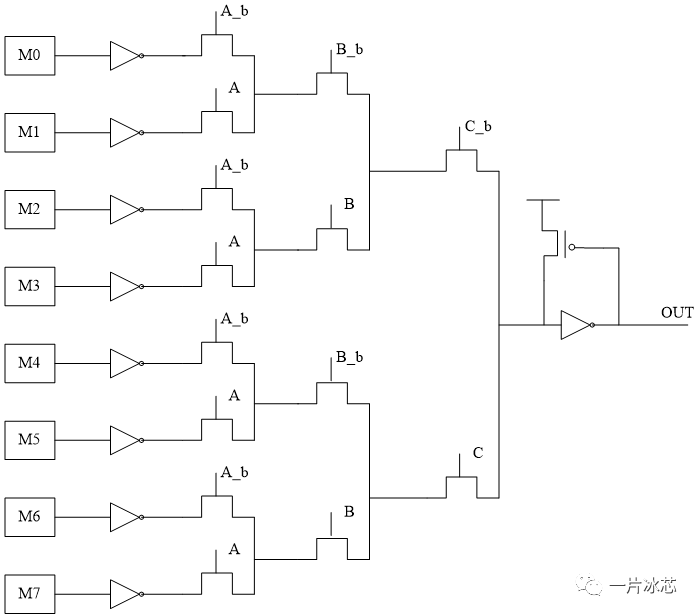

`在FPGA中,實現邏輯的基本單元是查找表(LUT)而非基本門電路。目前的FPGA中,單一LE或者Cell通常能實現至少4輸入查找表的邏輯功能。4輸入查找表可以看成是具有4位地址1位數據的存儲器

2018-07-30 18:11:19

FPGA中組合邏輯門占用資源過多怎么降低呢?有什么方法嗎?

2023-04-23 14:31:17

請問FPGA邏輯加載方式有哪些?例如flash等

2024-01-26 10:05:13

崗位職責:簡歷請發郵箱:3406289213@qq.com1、負責產品 FPGA 中通信信號處理單元的開發、仿真與在線測試;2、參與產品技術成果管理,編制FPGA設計各階段文檔,并為專利、技術條件

2017-06-13 16:23:01

本文采用FPGA和ARM結合設計,很好地完成了多通道高精度的數據采集與處理,并且還詳細介紹了FPGA邏輯的設計方法。

2021-05-06 06:21:48

圖像采集系統的結構及工作原理是什么FPGA邏輯設計中的常見問題有哪些

2021-04-29 06:18:07

FPGA中等效邏輯門概念數的計算方法有兩種,一是把FPGA基本單元(如LUT+FF,ESB/BRAM)和實現相同功能的標準門陣列比較,門陣列中包含的門數即為該FPGA基本單元的等效門數,然后乘以

2012-08-10 14:05:35

FPGA小白一枚,個人理解的FPGA本質上或者核心就是查找表(LUT),即將所有的函數/方法 轉換為固定的查找表(使用DSP除外)。但是為什么所有的文章提到FPGA全部都注重邏輯門呢?其實FPGA本身內部也沒有多少物理的邏輯門吧?

2019-05-30 10:53:46

及路線圖詳見報到通知)四、 課程簡介本課程為期三天,旨在幫助已經掌握一定設計基礎的工程師進一步了解FPGA邏輯設計的方法與優化技巧。講述了邏輯設計的驗證、高級狀態機的設計、基于FPGA的DSP設計方法

2009-07-24 13:13:48

` 本帖最后由 rousong1989 于 2015-3-9 18:57 編輯

FPGA是什么(特權同學版權所有)本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》(特權同學版權所有

2015-03-08 17:46:44

FPGA與CPLD(特權同學版權所有)本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》(特權同學版權所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-12 13:54:42

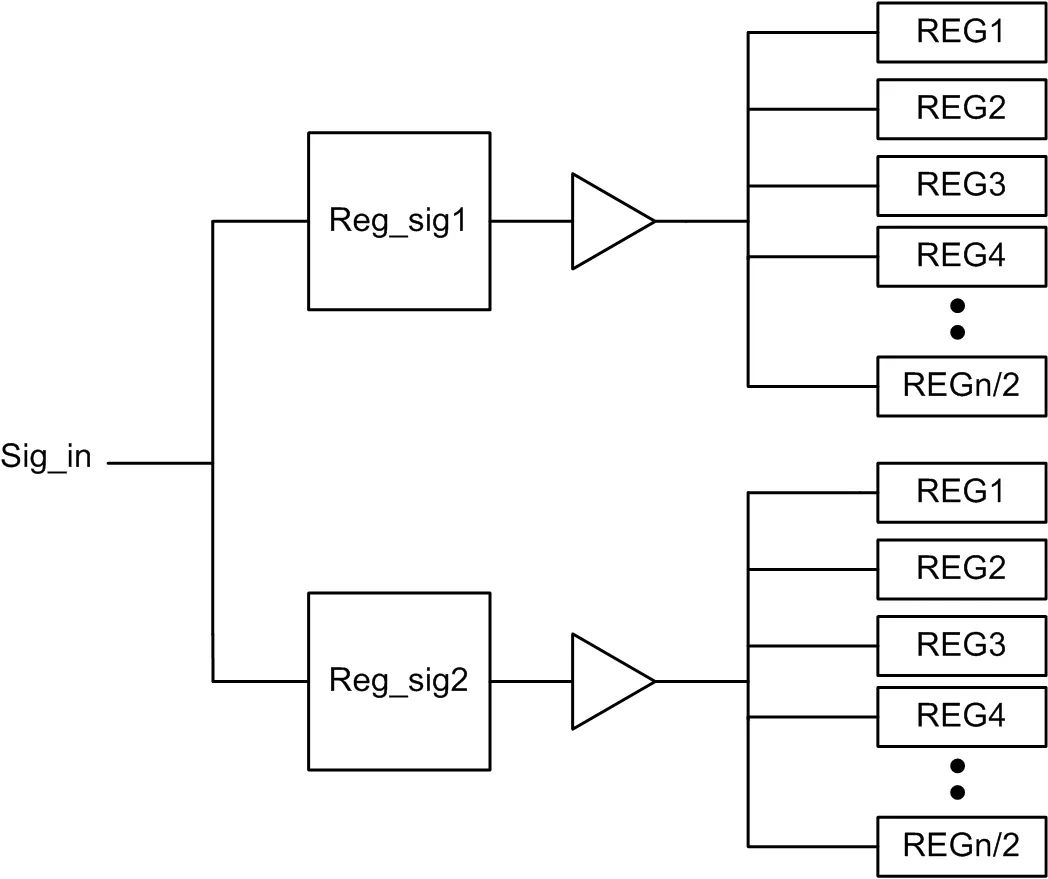

邏輯復制與資源共享本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 邏輯復制是一種通過增加面積來改善時序條件

2015-07-05 19:54:33

消除組合邏輯的毛刺本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt 在章節3.2的最后部分對于組合邏輯和時序

2015-07-08 10:38:02

在線調試方式大都是通過FPGA器件引出的JTAG接口,同時使用了一些FPGA片內固有的邏輯、存儲器或布線資源就能夠實現的。這些調試功能通常也只需要隨著用戶設計所生產的配置文件一同下載到目標FPGA器件中

2015-09-02 18:39:49

`FPGA應用領域(特權同學版權所有)本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》(特權同學版權所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-24 11:09:11

FPGA的優勢(特權同學版權所有)本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》(特權同學版權所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-26 11:00:19

FPGA開發流程(特權同學版權所有)本文節選自特權同學的圖書《FPGA設計實戰演練(邏輯篇)》(特權同學版權所有)配套例程下載鏈接:http://pan.baidu.com/s/1pJ5bCtt

2015-03-31 09:27:38

FPGA實現邏輯函數用的什么電路結構?

2017-01-01 21:49:23

實戰應用,這種快樂試試你就會懂的。話不多說,上貨。 數字電路中的邏輯代數基礎 在數字邏輯電路中,用1位二進制數碼的“0”和“1”表示一個事物的兩種不同邏輯狀態。例:一件事情的是和非、真和偽、有和無、好

2023-02-20 17:24:56

實戰應用,這種快樂試試你就會懂的。話不多說,上貨。 數字電路中的組合邏輯 根據邏輯功能的不同特點,可以將數字電路分為兩大類,一類稱為組合邏輯電路(簡稱組合電路),另一類稱為時序邏輯電路(簡稱

2023-02-21 15:35:38

;nbsp; 同時隨著FPGA在整個系統中開始扮演越來越重要的角色,FPGA的接口技術,以及與外部處理器、功能芯片之間甚至是其他系統之間的接口技術也成為FPGA

2010-03-10 17:52:19

;nbsp; 同時隨著FPGA在整個系統中開始扮演越來越重要的角色,FPGA的接口技術,以及與外部處理器、功能芯片之間甚至是其他系統之間的接口技術也成為FPGA

2010-03-10 17:58:29

fpga時序邏輯電路的分析和設計 時序邏輯電路的結構及特點時序邏輯電路——任何一個時刻的輸出狀態不僅取決于當時的輸入信號,還與電路的原狀態有關。[hide][/hide]

2012-06-20 11:18:44

fpga通過什么實現邏輯功能,以超級馬里奧為例子講述FPGA有些制作。1、FPGA游戲目標沒有CPU,單純用 FPGA 的verilog硬件語言來實現一個游戲,而這個游戲還得符合老師要求,由于沒有

2021-07-22 07:07:25

MPEG-2編碼復用器中的FPGA邏輯設計,看完你就懂了

2021-04-29 06:13:34

本文和設計代碼由FPGA愛好者小梅哥編寫,未經作者許可,本文僅允許網絡論壇復制轉載,且轉載時請標明原作者。OV5640提供了一個DVP接口用來輸出采集到的圖像數據流,本文提供了一個將DVP接口的圖像

2020-02-18 19:56:10

本文由FPGA愛好者小梅哥編寫,未經作者許可,本文僅允許網絡論壇復制轉載,且轉載時請標明原作者。 10路邏輯分析儀實例基于芯航線FPGA學習套件進行開發,實例使用到了芯航線FPGA學習套件的FPGA

2020-02-17 18:16:57

連接到I/O模塊。FPGA的邏輯是通過向內部靜態存儲單元加載編程數據來實現的,存儲在存儲器單元中的值決定了邏輯單元的邏輯功能以及各模塊之間或模塊與I/O間的聯接方式,并最終決定了FPGA所能實現的功能

2019-08-11 04:30:00

FPGA設計中,如何通過編寫VerilogHDL代碼達到預期的設計要求。2 設計技巧5 c) l5 |% xB% v: y+ D/ _& L$ a9 m2.1 如何減少關鍵路徑上的組合邏輯單元數

2020-08-31 18:49:10

為什么FPGA可以用來實現組合邏輯電路和時序邏輯電路呢?

2023-04-23 11:53:26

可編程邏輯芯片 FPGA 中的CYCLONE IV系列的芯片·主要指標中的速度級數代表什么意思?

2012-09-13 21:29:48

的。話不多說,上貨。 在FPGA中何時用組合邏輯或時序邏輯 在設計FPGA時,大多數采用Verilog HDL或者VHDL語言進行設計(本文重點以verilog來做介紹)。設計的電路都是利用

2023-03-06 16:31:59

FPGA設計中,如何通過編寫VerilogHDL代碼達到預期的設計要求。2 設計技巧5 c) l5 |% xB% v: y+ D/ _& L$ a9 m2.1 如何減少關鍵路徑上的組合邏輯單元數

2020-09-25 11:11:30

一定難度。而且要更改FPGA內部的邏輯也不是十分靈活。本文探討一種在嵌入式系統中,靈活,方便地動態配置FPGA 的方法。 具有FPGA 設計能力的硬件工程師可以設計各種F...

2021-12-21 06:13:49

脈沖重新置于FPGA邏輯中,然后將此時鐘輸入PLL以生成系統時鐘。這是一個學校項目,但我不確定這是否會奏效。誰能給我建議這個想法是否有效?如果沒有,你能說出理由嗎?

2020-08-26 15:09:45

推動FPGA調試技術改變的原因是什么外部邏輯分析儀受到的限制是什么如何用內部邏輯分析儀調試FPGA

2021-04-30 06:44:08

我想在CF卡中存儲一些圖像,因此它們可以被FPGA邏輯讀取,但我不知道該怎么做。有沒有關于它的教程?謝謝

2019-08-26 06:42:33

邏輯門控無法映射到Vivado中的一個時鐘區域時,BUFHCTRL能夠復制自身并將邏輯映射到多個時鐘區域嗎?謝謝,雨翔

2020-07-27 14:26:34

2GHz)的傳輸速率運行。NoC為FPGA設計提供了幾項重要優勢,包括:提高設計的性能。減少邏輯資源閑置,在高資源占用設計中降低布局布線擁塞的風險。減小功耗。簡化邏輯設計,由NoC去替代傳統的邏輯去做高速

2020-05-12 08:00:00

針對實時CORBA與容錯CORBA模型融合在分布式實時嵌入式系統(DRE)中存在的問題,提出基于半主動復制策略的容錯模型,應用到DRE中并進行相關測試。實驗結果表明,采用半主動復制策

2009-04-09 08:56:36 11

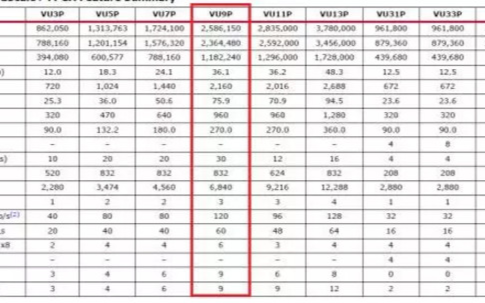

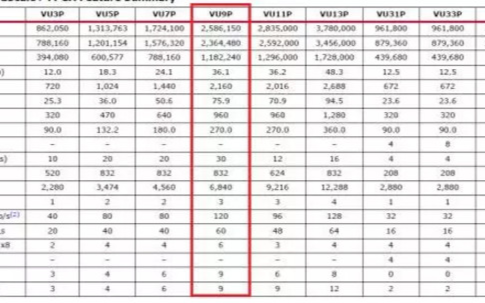

11 Xilinx?7系列FPGA由四個FPGA系列組成,可滿足各種系統要求,從低成本、小尺寸、成本敏感的高容量應用到超高端連接帶寬、邏輯容量和信號處理能力,以滿足最苛刻的高性能應用

2022-08-30 17:04:09

用VHDL 語言在FPGA 內部編程實現組播復制。本文介紹其實現方法,并給出了時序仿真波形。通過擴展,該設計可以支持多位寬、多路復制,因而具有較好的應用前景。關鍵詞:FP

2009-08-26 08:48:25 10

10 隨著FPGA設計復雜度的增加,傳統測試方法受到限制。在高速集成FPGA測試中,其內部信號的實時獲取和分析比較困難。介紹了Quartus II中SingalTap II嵌入式邏輯分析器的使用,并給出一個

2010-12-17 15:25:17 16

16 摘要:簡要介紹了現場可編程門陣列(FPGA)的特性,并結合MPEG-2編碼復用器開發過程中的經驗,給出了在MAX+ PLUS II提供的設計環境下FPGA邏輯設計的

2006-05-26 21:52:22 1039

1039

虛擬FPGA邏輯驗證分析儀的設計

隨著FPGA技術的廣泛使用,越來越需要一臺能夠測試驗證FPGA芯片中所下載電路邏輯時序是否正確的儀器。目前,雖然Agilent、Tektronix 等大公司生

2008-10-15 08:56:31 704

704

邏輯分析儀測試在基于FPGA的LCD顯示控制中的應用

摘要:邏輯分析儀作為基礎儀器,應該在基礎數字電路教學中得到廣泛應用。本文介紹了

2008-11-27 09:38:24 1176

1176

摘 要 :本文介紹了可編程邏輯器件開發工具Quartus II 中SingalTap II 嵌入式邏輯分析器的使用,并給出一個具體的設計實例,詳細介紹使用SignalTap II對FPGA調試的具體方

2009-06-20 10:42:18 1909

1909

摘要:簡要介紹了現場可編程門陣列(FPGA)的特性,并結合MPEG-2編碼復用器開發過程中的經驗,給出了在MAX+ PLUS II提供的設計環境下FPGA邏輯設計的一些方法和技巧。設計的邏

2009-06-20 14:40:35 784

784

邏輯分析儀自1973年問世以來,在短短幾十年的時間內得到了迅速的發展。傳統邏輯分析儀利用芯片的引腳對信號采樣,并送到顯示部分對系統進行分析,但對于無引腳的封裝類型,傳統邏輯分析儀很難有效的監測系統內部信號。而在FPGA測試中,嵌入式邏輯分析儀(ELA

2011-03-15 14:52:53 38

38 低功耗時鐘門控算術邏輯單元在不同FPGA中的時鐘能量分析

2015-11-19 14:50:20 0

0 FPGA項目應用之邏輯程序和sdram程序

2016-01-21 11:24:00 18

18 可編程邏輯器件FPGA/CPLD結構與應用

2016-12-11 23:38:39 0

0 PLD可以是低邏輯密度器件,采用被稱為復雜可編程邏輯器件(CPLD)的非易失元件構建;也可以是高密度器件,基于現場可編程門陣列(FPGA)的SRAM查找表(LUT)搭建。在可配置邏輯陣列中,除了

2017-09-12 17:08:30 14

14 現場可編程邏輯門陣列器件 FPGA原理及應用設計

2017-09-19 11:26:26 17

17 數字電路根據邏輯功能的不同特點,可以分成兩大類,一類叫組合邏輯電路(簡稱組合電路),另一類叫做時序邏輯電路(簡稱時序電路)。組合邏輯電路在邏輯功能上的特點是任意時刻的輸出僅僅取決于該時刻的輸入

2017-11-20 12:26:21 9235

9235 本文檔的主要內容詳細介紹的是FPGA視頻教程之FPGA設計中時序邏輯設計要點的詳細資料說明免費下載。

2019-03-27 10:56:04 20

20 FPGA的用量比較大,基站最適合使用FPGA,基站幾乎每一塊板子都需要使用FPGA芯片,而且型號比較高端,可以處理復雜的物理協議,實現邏輯控制。同時,由于基站的邏輯鏈路層,物理層的協議部分需要定期更新,也比較適合采用FPGA技術。

2019-12-27 07:07:00 2389

2389

FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個概念,內部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸入輸出模塊IOB(Input Output Block)和內部連線(Interconnect)三個部分。

2019-12-02 07:05:00 2215

2215

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-05 07:08:00 3476

3476

本課程以目前流行的Xilinx 7系列FPGA的開發為主線,全面講解FPGA的原理及電路設計、Verilog HDL語言及VIVADO的應用,并循序漸進地從組合邏輯、時序邏輯的開發開始,深入到FPGA的基礎應用、綜合應用和進階應用。

2019-12-03 07:04:00 3009

3009

CLB(Configurable Logic Block):FPGA最基本的組成單元,可以實現基本的組合邏輯和時序電路。其中,LUT(Lookup Tables)是實現組合邏輯的部分,可以實現n個輸入的任意組合邏輯運算(不同型號的FPGA有所不同,下圖的例子中為6個輸入)。

2019-09-27 15:18:06 9068

9068

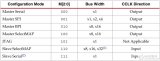

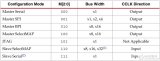

今天咱們聊聊xilinx7系列FPGA配置的相關內容。總所周知FPGA上電后,其工作的邏輯代碼需要從外部寫入FPGA,FPGA掉電后其邏輯代碼就丟失,因此FPGA可以被無限次的配置不同的邏輯代碼,但

2019-10-20 09:02:00 3778

3778

英特爾 Stratix 10 GX 10M FPGA共有 1020 萬個邏輯單元,是第一款使用 EMIB 技術將兩個 FPGA構造晶片在邏輯和電氣上實現整合的英特爾 FPGA

2019-11-26 15:46:53 4574

4574 了革命性的新型二維片上網絡(2D NoC)。2D NoC如同在FPGA可編程邏輯結構上運行的高速公路網絡一樣,為FPGA外部高速接口和內部可編程邏輯的數據傳輸提供了超高帶寬(~27Tbps)。 圖1

2020-03-04 15:59:39 2167

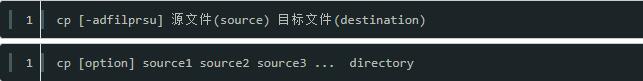

2167 linux中如何復制文件?

2020-06-03 09:17:20 2497

2497

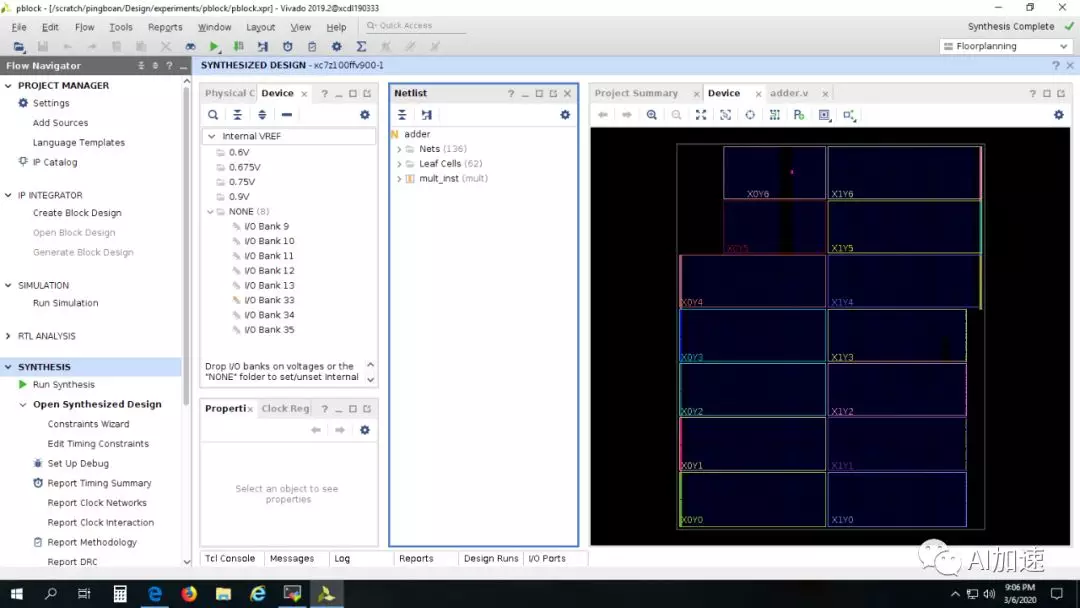

的位置限定了邏輯單元在FPGA中的位置。通常一個pblock大小不要超過總設計資源的20%。如果pblock占比資源很大,就要將一個pblock劃分給更底層的邏輯。 打開綜合后的設計,我們切換到floorplanning選項,這個時候我們可以看到綜合后的模塊以及device視圖。 從netlist中可以看到有兩個

2020-10-10 16:03:18 9661

9661

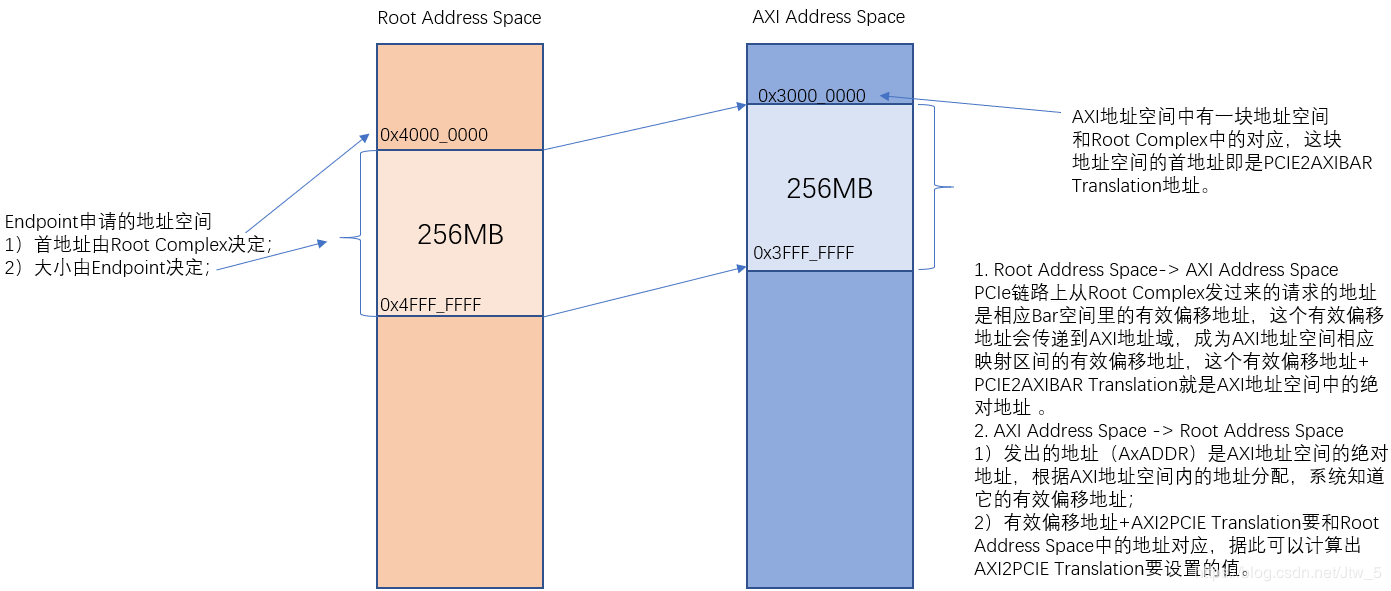

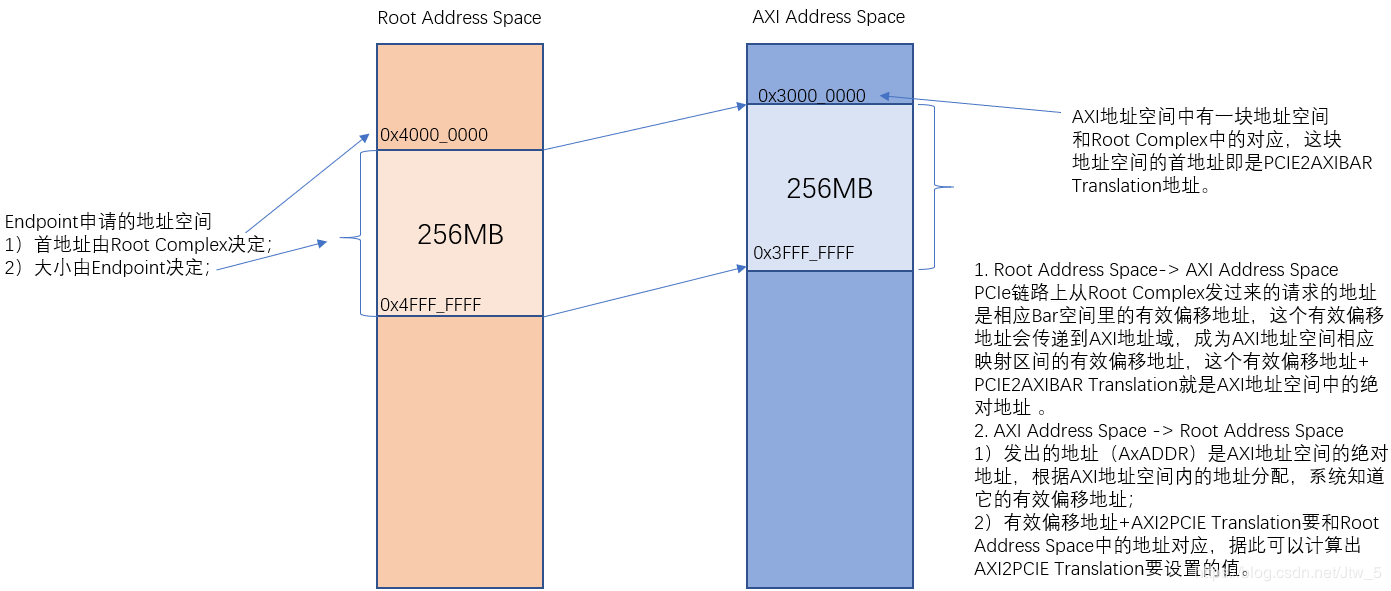

背景與問題 CPU+FPGA架構,CPU做RC、FPGA做EP; FPGA邏輯(Vivado -BD - Address Editor)中如何設置PCIe to AXI Translation

2020-11-20 15:28:52 8159

8159

本文檔的主要內容詳細介紹的是FPGA硬件基礎知識FPGA的邏輯單元工程文件免費下載。

2020-12-10 15:00:31 16

16 本文檔的主要內容詳細介紹的是FPGA硬件基礎之FPGA的邏輯單元的工程文件免費下載。

2020-12-10 15:00:28 20

20 在FPGA中,實現邏輯的基本單元是查找表(LUT)而非基本門電路。目前的FPGA中,單一LE或者Cell通常能實現至少4輸入查找表的邏輯功能。

2020-12-29 17:27:22 14

14 可編程邏輯陣列fpga和cpld說明。

2021-03-30 09:30:05 25

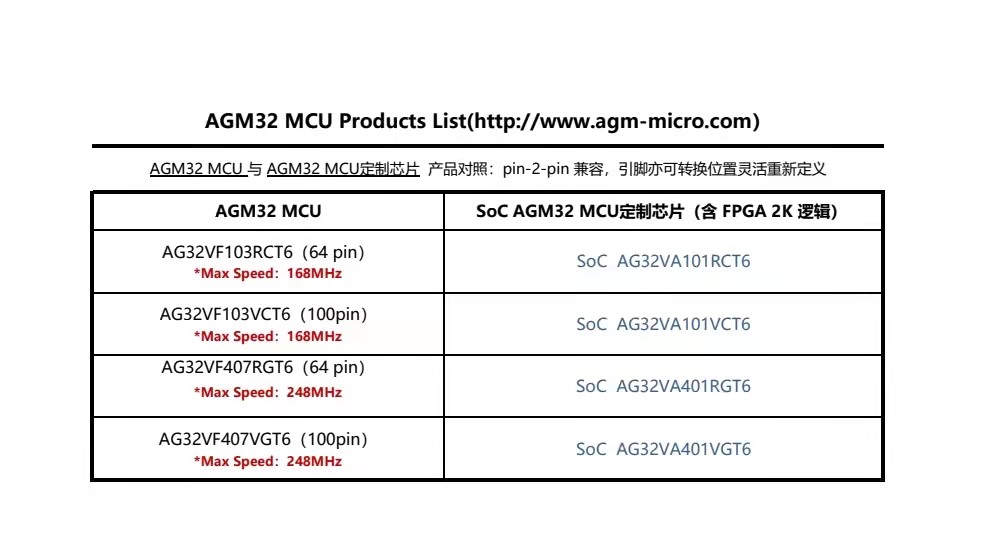

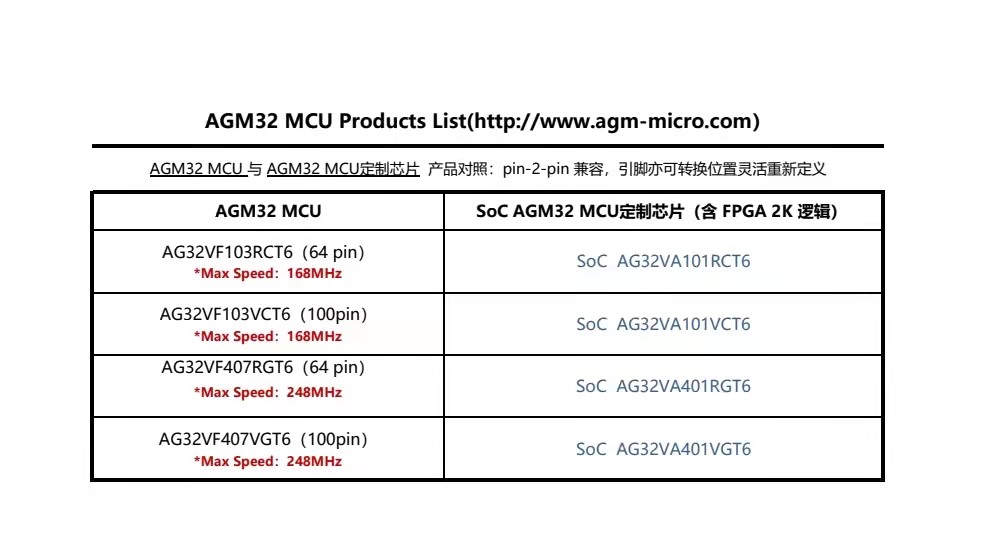

25 國產MCU中唯一內置FPGA邏輯的產品

2022-03-08 10:47:39 5728

5728

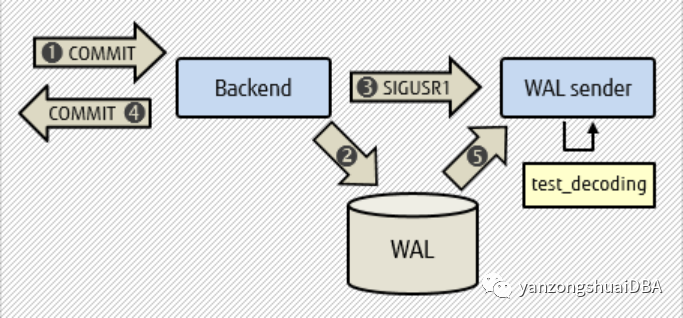

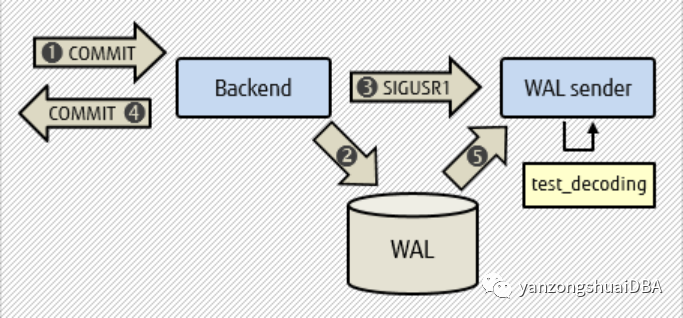

PG在8.0版本已經支持了兩階段提交,10.0版本支持邏輯復制。但是邏輯復制中一直都不支持兩階段提交。單實例中已經支持了PREPARE TRANSACTION、COMMIT PREPARED和ROLLBACK PREPARED命令

2022-03-29 15:54:36 2214

2214

Achronix Speedster7t FPGA除了在外圍Hard IP上都采用目前業內領先的大帶寬高速率IP,在內部的可編程邏輯的架構中也做了大量的優化去進一步提高內部可編程邏輯的性能,從而適配

2022-07-05 15:37:41 1777

1777 在數字化時代的今天,我們都認同數據會創造價值。為了最大化數據的價值,我們不停的建立著數據遷移的管道,從同構到異構,從關系型到非關系型,從云下到云上,從數倉到數據湖,試圖在各種場景挖掘數據的價值。而在這縱橫交錯的數據網絡中,邏輯復制扮演著極其重要的角色。

2022-09-22 10:11:43 2595

2595 在進行FPGA原型驗證的過程中,當要把大型的SoC進行FPGA原型驗證時,有時候會遇到一種情況,同樣的接口分兩組出去到不同的模塊,而這兩個模塊規模較大,又需要分割在兩片FPGA中,這時候就會像下圖一樣。

2023-05-04 16:21:34 1331

1331

電子發燒友網站提供《在Artix 7 FPGA上使用Vivado的組合邏輯與順序邏輯.zip》資料免費下載

2023-06-15 09:14:49 0

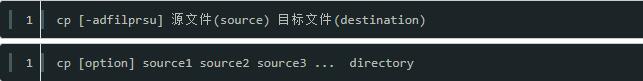

0 復制目錄是Linux中的一項基本任務,它允許我們復制目錄、創建備份或在不同位置之間傳輸數據。在Linux中復制文件和目錄最常用的命令之一是cp。 在本教程中,我們將探討如何使用cp命令有效地復制目錄

2023-06-26 17:14:07 1418

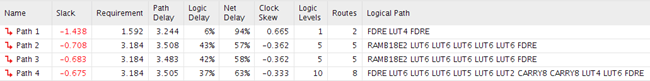

1418 在FPGA邏輯電路設計中,FPGA設計能達到的最高性能往往由以下因素決定。

2023-09-26 11:31:03 3164

3164

MySQL主從復制是一種常用的數據復制技術,可以實現數據從一個MySQL服務器(主服務器)復制到另一個MySQL服務器(從服務器)。在主從復制中,混合類型的復制是一種較為靈活的復制模式,它可以同時

2023-11-16 14:20:42 1089

1089

?

?

電子發燒友App

電子發燒友App

評論