本文首先介紹了FPGA的特點與FPGA芯片結構,其次分析了FPGA與ASIC及CPLD對比,最后介紹了FPGA基礎入門到高手相關知識與FPGA下載配置學習心得。

2018-05-30 08:39:29 37049

37049

我們需要學會區分PCB封裝里面的元器件引腳,并在PCB文件中標出來,然后學習創建元件庫里面沒有的器件封裝,通過老師的分步演示從原理圖導入PCB的步驟,最后學習電路的連線,完成PCB的封裝。

2019-04-18 14:15:40 19195

19195 時鐘網絡反映了時鐘從時鐘引腳進入FPGA后在FPGA內部的傳播路徑。

2019-09-10 15:12:31 7150

7150

01、如何決定FPGA中需要什么樣的時鐘速率 設計中最快的時鐘將確定 FPGA 必須能處理的時鐘速率。最快時鐘速率由設計中兩個觸發器之間一個信號的傳輸時間 P 來決定,如果 P 大于時鐘周期 T,則

2020-11-23 13:08:24 4644

4644

當我剛開始我的FPGA設計生涯時,我對明顯更小、更不靈活的 FPGA(想想 XC4000XL / Clcyone3/4和 Spartan)和工具的非常簡單的時鐘規則之一是盡可能只使用單個時鐘。當然,這并不總是可能的,但即便如此,時鐘的數量仍然有限。

2022-09-30 08:49:26 2145

2145 “全局時鐘和第二全局時鐘資源”是FPGA同步設計的一個重要概念。合理利用該資源可以改善設計的綜合和實現效果;如果使用不當,不但會影響設計的工作頻率和穩定性等,甚至會導致設計的綜合、實現過程出錯

2023-07-24 11:07:04 1443

1443

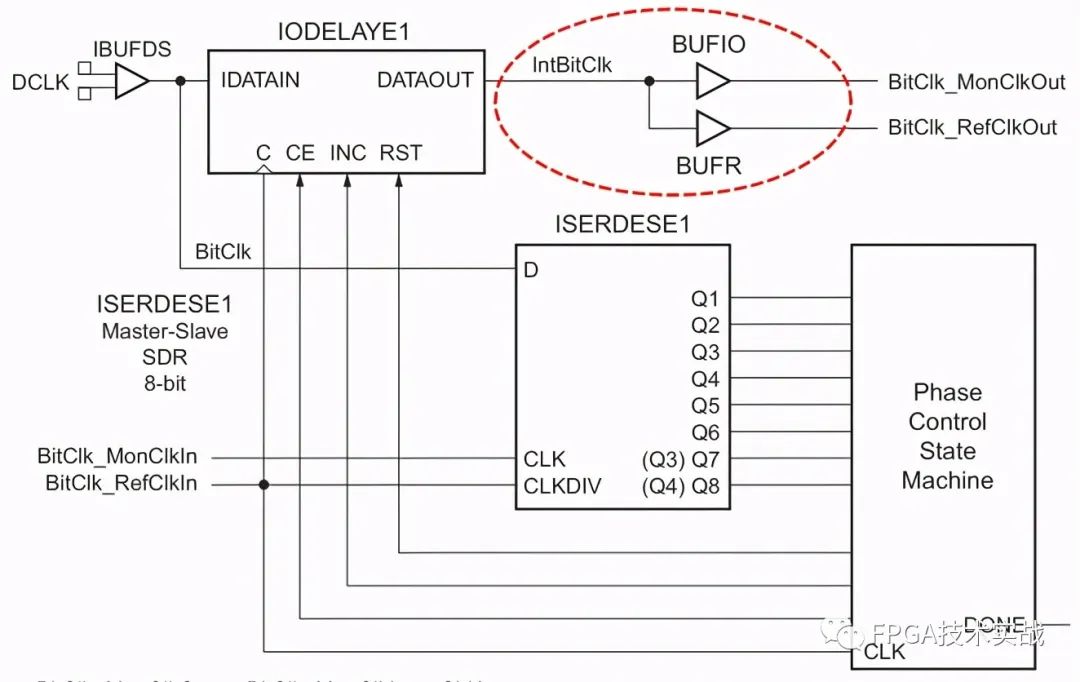

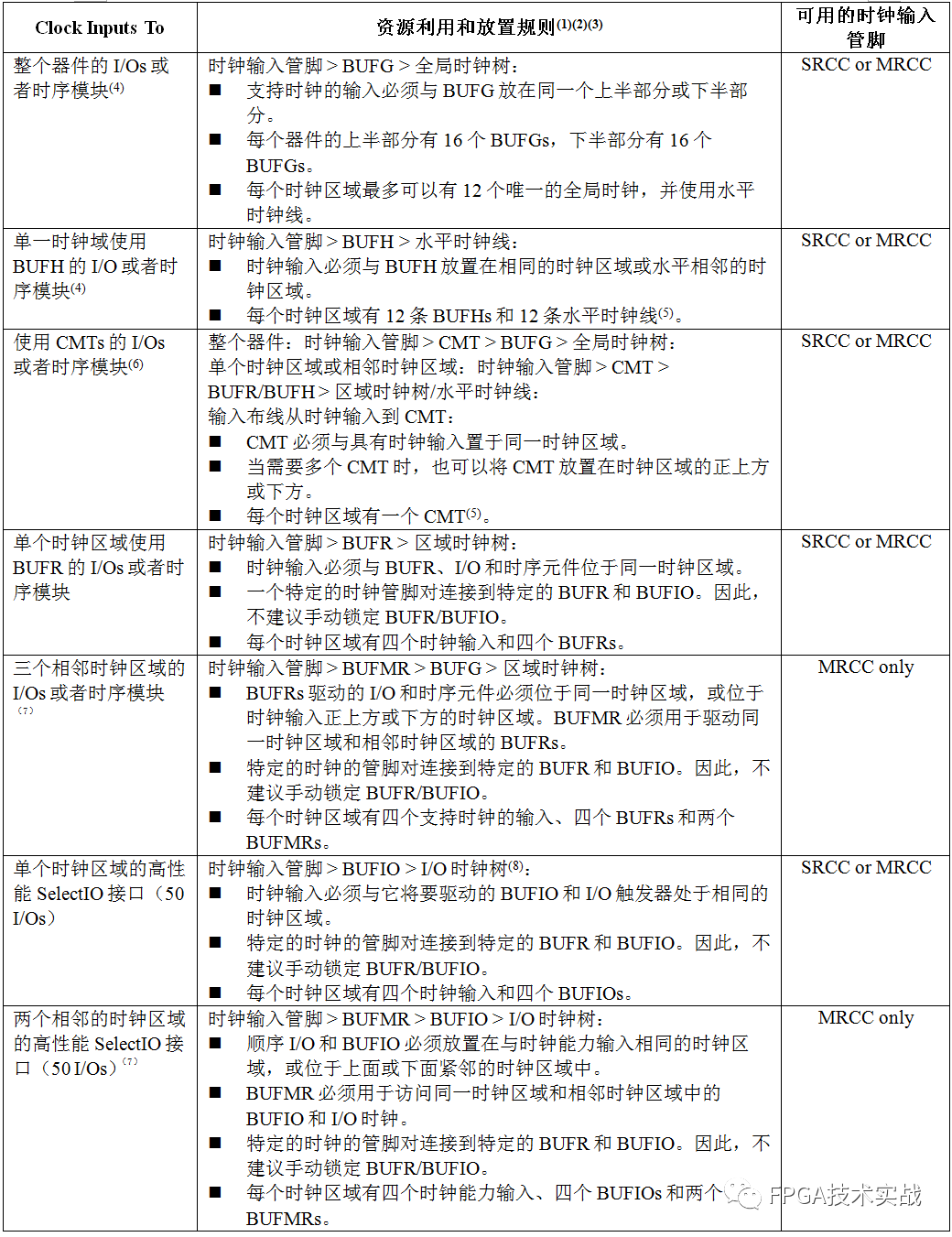

通過上一篇文章“時鐘管理技術”,我們了解Xilinx 7系列FPGA主要有全局時鐘、區域時鐘、時鐘管理塊(CMT)。 通過以上時鐘資源的結合,Xilinx 7系列FPGA可實現高性能和可靠的時鐘分配

2023-08-31 10:44:31 4432

4432

本文主要介紹Xilinx FPGA的GTx的參考時鐘。下面就從參考時鐘的模式、參考時鐘的選擇等方面進行介紹。

2023-09-15 09:14:26 5117

5117

生成時鐘包括自動生成時鐘(又稱為自動衍生時鐘)和用戶生成時鐘。自動生成時鐘通常由PLL或MMCM生成,也可以由具有分頻功能的時鐘緩沖器生成如7系列FPGA中的BUFR、UltraScale系列

2024-01-11 09:50:09 3808

3808

設計流程緊密集成,在項目的任何階段均可訪問。原理圖、PCB Layout 和FPGA 數據庫始終保持同步,以便用戶控制項目的設計數據流。另外,原理圖用戶可決定何時將 FPGA 數據(新數據或更新數據

2018-09-20 11:11:16

畢業后,從一個嵌入式硬件狗轉做FPGA工程師,從中兜兜轉轉繞了不少彎路,為了給后人避坑,所以今天開始寫有關FPGA從入門到精通的教程吧,這也算是給我國集成電路的發展做出微薄的貢獻吧。 本門課程主要

2020-06-23 23:52:00

使用的時鐘信號往往不只是供給單個寄存器使用,因為在實際應用中,成百上千甚至更多的寄存器很可能共用一個時鐘源,那么從時鐘源到不同寄存器間的延時也可能存在較大偏差(我們通常稱為時鐘網絡延時),而我們知道

2019-04-12 01:15:50

Tc2t;時鐘到達目的寄存器,即ADV7123芯片的引腳輸入端,其路徑延時為Tc2r,這個延時包括了時鐘從PLL輸出到FPGA引腳的延時以及時鐘從FPGA的引腳到ADV7123引腳的延時,后者的延時

2015-07-30 22:07:42

FPGA時鐘問題 2010-06-11 15:55:39分類: 嵌入式1.FPGA的全局時鐘是什么?FPGA的全局時鐘應該是從晶振分出來的,最原始的頻率。其他需要的各種頻率都是在這個基礎上利用PLL或者其他分頻手段得到的。

2021-07-29 09:25:57

那個商業行為背后的動機,只是想以此為契機從技術的角度,略略討論下這次收購背后的關鍵因素——FPGA和ASIC的在AI計算中銜接關系。因為并不是專家,所以如有錯誤理解請指出。 從FPGA到ASIC

2023-03-28 11:14:04

本來剛開始從原理圖畫起,到pcb都正常,但是在pcb中,我重新標注了幾次,原理圖也重新標注了,現在問題是,兩邊的元件對不上了,updata不起作用,反標也不行,該怎么做才能讓原理圖和pcb元件能對應上呢

2011-03-04 21:40:20

從ASIC到FPGA的轉換系統時鐘設計方案

2011-03-02 09:37:37

從MCU到FPGA

2021-02-02 07:36:46

包含.bit文件,而不包括VHDL源代碼。有沒有辦法獲得最簡單的源代碼,這將允許我從FPGA獲取數據流到PC上的COM端口。我只需要來自FPGA-> PC的3.2Kbps數據。

2019-09-11 12:18:49

嗨, 我正在開發一種設計,我們的主板有1個virtex5 fpga和9個從屬卡,每個都有1個V5 fpga。我想同步所有9個從卡的操作。我還希望主卡和從卡之間的數據傳輸速率為300-400Mbps

2019-01-30 06:52:36

在設計中想用上AD9254作為ADC,在設計過程中發現datasheet內部提供了多種時鐘設計方案,由于設計的限制,想要省去所有方案中均推薦使用的AD951x芯片,請問是否有曾經使用過該款AD的同仁,使用直接從FPGA差分時鐘引腳引出的時鐘信號,是否能夠滿足設計的要求?

2018-11-02 09:14:32

我現在做一個數據采集板子,用的zyqn7000 soc FPGA,ADC用的ADC08DL502 ,采樣率最高到500M,想請問下這么高的采樣率的時鐘是否可以直接從FPGA輸出給ADC,還是要用

2024-12-26 06:37:42

橋接器和一些簡單的UART VHDL代碼通過HyperTerm從FPGA到PC獲取數據?我在ML605上看到,Xilinx表示需要實現UART IP,例如XPS UART Lite或UART16550

2019-09-09 06:23:26

必須適當地與所有數據位的到達保持同步。如果接收器使用發射時鐘,可能會要求延遲從發送端到接收端的時鐘信號。 有時設計可能需要一個更高的時鐘頻率來運行FPGA上的邏輯。但是,只有低頻率輸出的時鐘源可以用

2020-04-25 07:00:00

1、Audio codec時鐘源從BCLK1獲取 Platform: RK3399 OS: Android 7.1 Kernel: v4.4.83 需求: 默認codec的clock

2022-11-15 17:36:45

的問題是,我可以在FPGA內部使用這個時鐘作為FPGA和電路板的主時鐘嗎?我有一個應用程序,我想在板上盡可能少的部件,我不關心主時鐘頻率是什么,只要它是1-50MHz時鐘。要使用CCLK我必須有一個PCB

2019-05-07 13:40:54

數字信號處理[3]已經成為FPGA的一個重要課題,高速的采樣頻率帶來的是大容量的存儲數據。在存儲芯片領域,DDR3以較低的功耗,較快的存儲速度,較高的存儲容量和較低的價格迅速占領市場;同時在繪制PCB板圖

2018-08-30 09:59:01

一部追蹤器,這又是怎么回事呢?由于目前安卓手機大都自帶GPS定位功能,很多移動廣告公司為了做到更精準的廣告投放,在軟件里就惡意插入獲取用戶位置信息的代碼。記者在暗訪一家名為“贏告無限”的廣告公司時,一位

2012-12-01 17:36:51

大家好,設備:xc7vx485tffg1761-2我需要從FPGA提供外部時鐘。所以我使用了OBUFDS,輸入時鐘來自clock_wizard。我想知道OBUFDS是否是正確的選擇,還是有任何提供輸出差分時鐘的方法。謝謝,Musthafa V.

2020-04-15 08:30:14

嗨,有誰知道如何從fpga(斯巴達3)中讀出用戶代碼?干杯約翰以上來自于谷歌翻譯以下為原文Hi, Anybody knows how to readout the usercode from within the fpga (spartan3)? cheers John

2019-07-26 10:53:31

嗨,我正在嘗試從FPGA向另一個設備輸出一個時鐘信號(10MHz)來驅動一個50歐姆的端接負載。我試著用DDR來輸出這個時鐘。我從主振蕩器時鐘輸入(50MHz)到virtex板生成此信號。我使用DCM以5來獲得10Mhz。然后我把它運行到DDR。到目前為止,我沒有運氣。有人可以給我指點嗎?謝謝。

2020-06-15 08:40:22

先生/女士, 我們如何從virtex 5(XC5VLX110T)獲取時鐘信號?我們已經參考了用戶手冊并嘗試從d手冊中提到的幾個引腳獲取信號。針腳:AH17,AG18。通過AH17引腳的輸出是17

2019-03-04 10:10:13

我知道在接入點模式下我們可以設置用戶和密碼,但我看到另一種方式(如我附上的圖表)ESP8266 可以從路由器獲取用戶和密碼,這怎么可能?

2023-05-16 08:49:35

大家好

我正在使用 FX2 設備,以前也使用過 FX3 設備。 使用 FX3 設備 SDK,當我下載它時,我在安裝文件夾中獲得了許多示例源代碼,但是它沒有 FX2 的示例源代碼,我如何獲取用于開發 fx2 的 sdk 和示例源代碼?

2025-05-07 07:25:05

“Drago,William @NARDAEAST”寫道:>全部,>>任何人都可以告訴我如何在VEE 6.xx中獲取用戶名(System.Environment.UserName

2019-08-29 11:03:45

我想知道如何通過 wifi 從 C329 相機獲取圖像到用戶的屏幕,是直接 wifi 鏈接,還是通過互聯網?

IMAGE 命令要求是:“圖像文件應使用文件管理器上傳到設備”,因此不是動態的。

是否有

2023-05-10 09:44:29

我們正在使用St 分發源代碼,我們在buildroot工具中編譯源代碼。但是我們無法獲取用戶登錄頁面。我怎樣才能得到用戶登錄頁面。

2022-12-26 10:41:39

周期嗎?3.FPGA做加減法之類的運算時間要耗費多少時鐘周期?比如我定義輸入變量A、B、C、D都是8位,輸出變量E是16位,使E的前八位存入A+B,后八位存入C+D,那么從輸入到輸出需要多少個時鐘周期?謝謝!

2015-05-11 19:17:21

考慮的是在SDRAM端口的時鐘延時,也就是說還沒有考慮SDRAM時鐘從PLL輸出,經過FPGA內部走線,和外部PCB的延時,我們想一下,是不是有一個這樣的關系 就是,PLL的時鐘偏移 + 時鐘從PLL

2015-03-31 10:35:18

的值,由于我們的時鐘是總PLL發出的,時鐘從FPGA管腳輸出后再送給SDRAM,因此這個值一定是負值,而且也是時鐘在PCB上的走線延時,這個值我們估算為-0.1ns好了,因為真的沒法算我覺得。 然后

2015-03-31 10:20:00

具有DCO輸出,可將DAC輸入時鐘轉發至FPGA。我在想,這與ADC情況非常相似。但現在我意識到,對DCO信號的引用并沒有給我帶來任何好處。首先,DCO信號經歷從DAC到FPGA的傳播延遲,然后數據

2020-03-12 11:12:21

詳細接入體驗可參考Account Kit提供的SampleCode示例工程。

典型場景:

1、元服務需要完善用戶頭像信息,參見獲取頭像。

2、元服務提供的服務依賴用戶手機號,需要獲取用戶手機號,參見獲取

2025-04-02 11:10:42

、Client Secret、Authorization Code從華為服務器獲取Access Token,再使用Access Token請求獲取用戶信息。

從用戶信息中獲取到手機號、UnionID

2025-04-08 16:14:04

pcb Layout 設計從基礎到實踐多媒體教程

2006-05-28 01:11:23 0

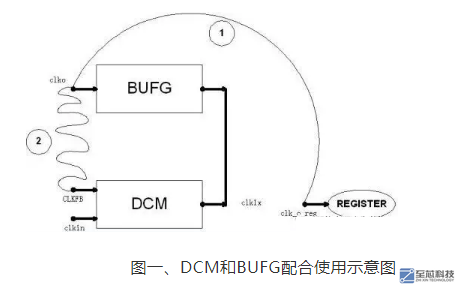

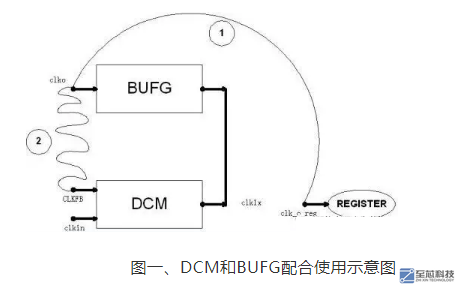

0 DLL在FPGA時鐘設計中的應用:在ISE集成開發環境中,用硬件描述語言對FPGA 的內部資源DLL等直接例化,實現其消除時鐘的相位偏差、倍頻和分頻的功能。時鐘電路是FPGA開發板設計中的

2009-11-01 15:10:30 33

33 最初,FPGA 只是用于膠合邏輯,從膠合邏輯到算法邏輯再到數字信號處理、高速串行收發器和嵌入式處理器,FPGA 真正地從配角變成了主角。

2009-11-30 16:25:14 17

17 本文闡述了用于FPGA的可優化時鐘分配網絡功耗與面積的時鐘布線結構模型。并在時鐘分配網絡中引入數字延遲鎖相環減少時鐘偏差,探討了FPGA時鐘網絡中鎖相環的實現方案。

2010-08-06 16:08:45 12

12 Printf:讀取用戶輸入

前面的程序很好,但要是如果能從用戶那里讀入值5和7而不是使用固定的值的話,那就更好了。可以改為下面的程序: #include

2009-07-29 10:42:21 2234

2234 PCB板完整電磁信息的獲取及應用

調試PCB的傳統工具包括:時域的示波器

2009-12-26 14:44:40 751

751 大型設計中FPGA的多時鐘設計策略

利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率

2009-12-27 13:28:04 827

827

在FPGA設計中,為了成功地操作,可靠的時鐘是非常關鍵的。設計不良的時鐘在極限的溫度、電壓下將導致錯誤的行為。在設計PLD/FPGA時通常采用如下四種類型時鐘:全局時鐘、門控時鐘

2011-09-21 18:38:58 4131

4131

在Quartus Ⅱ開發環境下,用Verilog HDL硬件描述語言設計了一個可以在FPGA芯片上實現的數字時鐘. 通過將設計代碼下載到FPGA的開發平臺Altera DE2開發板上進行了功能驗證. 由于數字時鐘的通用

2011-11-29 16:51:43 184

184 利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數

2012-05-21 11:26:10 1591

1591

DLL在_FPGA時鐘設計中的應用,主要說明DLL的原理,在Xilinx FPGA中是怎么實現的。

2015-10-28 14:25:42 1

1 基于FPGA的數字時鐘設計,可實現鬧鐘的功能,可校時。

2016-06-23 17:15:59 71

71 實現了基于FPGA與USB的CMOS圖像獲取與采集系統的設計。介紹了成像系統的結構、CMOS圖像獲取時序的VHDL程序實現、包含FPGA控制及USB固件與VC接口界面程序等在內的數據傳輸通路設計以及Direct Draw數字圖像的顯示等。實驗結果表明,成像系統工作正常,數據傳輸滿足USB接口規范與設計要求。

2016-09-22 16:53:46 23

23 如何正確使用FPGA的時鐘資源

2017-01-18 20:39:13 22

22 有些FPGA學習者,看Xilinx的Datasheet會注意到Xilinx的FPGA沒有PLL,其實DCM就是時鐘管理單元。 1、DCM概述 DCM內部是DLL(Delay Lock Loop結構

2018-05-25 15:43:53 8952

8952

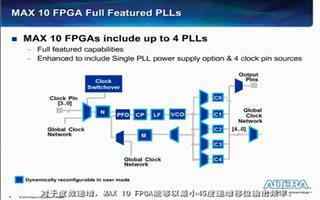

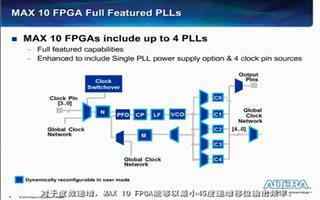

MAX 10 FPGA PLL和時鐘培訓,此次培訓涉及到器件系列的時鐘特性和選項。有20個全局時鐘網絡,全局CLK輸入引腳數量也可以加倍,用作通用IO引腳。并且采用動態用戶控制進行各種選擇和電源控制,構建魯棒的時鐘網絡源。它所有4個PLL都是全功能的。

2018-06-20 08:00:00 3327

3327

本文檔的主要內容詳細介紹的是spartan-6 FPGA的時鐘資源的用戶指南資料免費下載。

2019-02-15 16:39:07 28

28 時鐘是FPGA設計中最重要的信號,FPGA系統內大部分器件的動作都是在時鐘的上升沿或者下降沿進行。

2019-09-20 15:10:18 6055

6055

偏斜 時鐘偏斜是一種現象,其中時鐘信號以不同的間隔到達不同的目的地。時鐘信號通常用于 PCB 設計中的同步通信。例如,串行外設接口( SPI )使用時鐘信號在設備之間發送和接收數據。 在理想的主機到多個從機組件的配置中,時鐘信號的傳播時間沒有延遲

2020-09-16 22:59:02 2876

2876 時鐘網絡反映了時鐘從時鐘引腳進入FPGA后在FPGA內部的傳播路徑。 報告時鐘網絡命令可以從以下位置運行: A,VivadoIDE中的Flow Navigator; B,Tcl命令

2020-11-29 09:41:00 3695

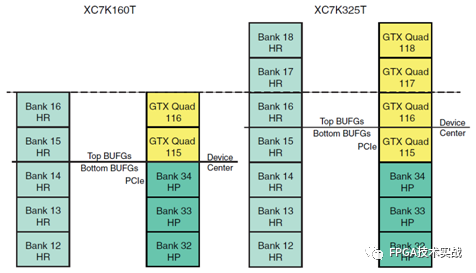

3695 區域(Region):每個FPGA器件被分為多個區域,不同的型號的器件區域數量不同。

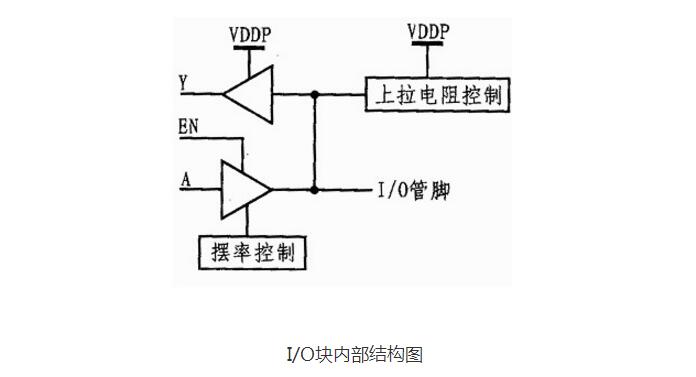

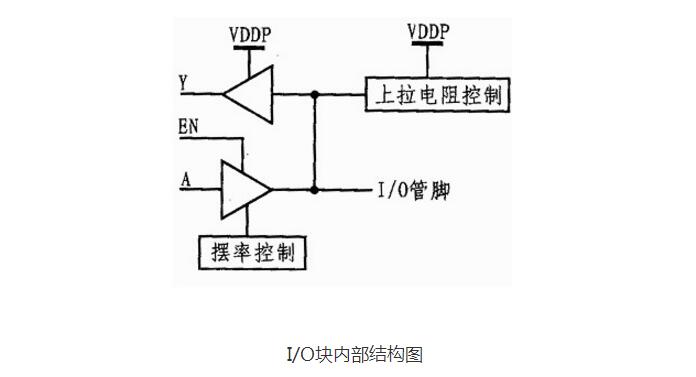

FPGA時鐘資源主要有三大類:時鐘管理模、時鐘IO、時鐘布線資源。

時鐘管理模塊:不同廠家及型號的FPGA中

2020-12-09 14:49:03 21

21 本文檔的主要內容詳細介紹的是FPGA硬件基礎之FPGA時鐘資源的工程文件免費下載。

2020-12-10 15:00:29 16

16 前些時候,共享充電寶漲價問題引起了消費者熱議,現在,新的問題又來了。根據有關媒體的消息,共享充電寶存在著一個安全隱患問題,那就是竊取用戶的個人隱私。

2020-12-15 15:33:09 5166

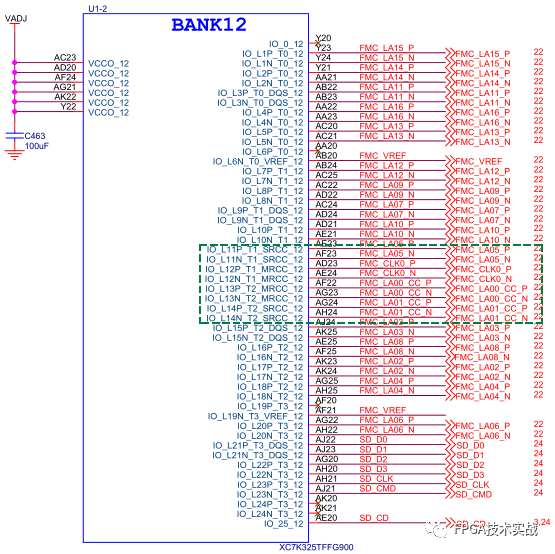

5166 引言:7系列FPGA具有多個時鐘路由資源,以支持各種時鐘方案和要求,包括高扇出、短傳播延遲和極低的偏移。為了最好地利用時鐘路由資源,必須了解如何從PCB到FPGA獲取用戶時鐘,確定哪些時鐘路由資源

2021-03-22 10:16:18 6115

6115

引言:從本文開始,我們陸續介紹Xilinx 7系列FPGA的時鐘資源架構,熟練掌握時鐘資源對于FPGA硬件設計工程師及軟件設計工程師都非常重要。本章概述7系列FPGA時鐘,比較了7系列FPGA時鐘

2021-03-22 10:25:27 6070

6070 從電池中獲取更多能量

2021-04-24 15:45:54 6

6 1. STM32獲取系統時鐘第一步在main函數開頭添加如下代碼:RCC_ClocksTypeDef RCC_Clocks;RCC_GetClocksFreq(&RCC_Clocks

2021-12-24 19:35:25 11

11 (08)FPGA時鐘概念1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA時鐘概念5)結語1.2 FPGA簡介FPGA(Field Programmable Gate

2021-12-29 19:41:17 2

2 (12)FPGA時鐘設計原則1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA時鐘設計原則5)結語1.2 FPGA簡介FPGA(Field Programmable

2021-12-29 19:41:27 17

17 (29)FPGA原語設計(差分時鐘轉單端時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(差分時鐘轉單端時鐘)5)結語1.2 FPGA簡介FPGA

2021-12-29 19:41:38 5

5 (30)FPGA原語設計(單端時鐘轉差分時鐘)1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA原語設計(單端時鐘轉差分時鐘)5)結語1.2 FPGA簡介FPGA

2021-12-29 19:41:48 10

10 經過了前面的開胃菜,項目正式開始。一步步講解這個模型怎么玩起來的。從C 到 matlab 到 FPGA ,三個平臺聯合起來完成這個 由 RTL 實現 CNN 的項目。

2022-03-15 17:13:24 3087

3087 ?xilinx 的 FPGA 時鐘結構,7 系列 FPGA 的時鐘結構和前面幾個系列的時鐘結構有了很大的區別,7系列的時鐘結構如下圖所示。

2022-07-03 17:13:48 4699

4699 電子發燒友網站提供《Logos系列FPGA時鐘資源(Clock)用戶指南.pdf》資料免費下載

2022-09-26 10:15:21 11

11 電子發燒友網站提供《從云端獲取數據到您的Arduino.zip》資料免費下載

2022-11-08 15:12:44 6

6 ASIC 和FPGA芯片的內核之間最大的不同莫過于時鐘結構。ASIC設計需要采用諸如時鐘樹綜合、時鐘延遲匹配等方式對整個時鐘結構進行處理,但是 FPGA設計則完全不必。

2022-11-23 16:50:49 1249

1249

電子發燒友網站提供《從Web獲取濕度/溫度.zip》資料免費下載

2022-12-14 09:21:01 0

0 設計開發過程高質量、順暢地進行呢?“PCB系統設計——從原理圖到投產”系列將通過實例演示,在5期直播網課中與大家探討PCB系統設計理念與方法,從概念階段到物理實現

2022-12-19 11:29:14 1123

1123

之前在玩FPGA時,對于一個系統工程,當邏輯電路設計完成之后,一般會先拿給Vivado/Quartus先去跑一般綜合,然后去獲取所有的跨時鐘路徑,在ASIC里,基本也是拿EDA工具去分析獲取。今兒個搞個小demo,看在SpinalHDL當設計做完后,如何一鍵提取整個工程里所有的跨時鐘路徑。

2023-09-15 14:06:56 1464

1464 Altera的FPGA中,只有從專用時鐘管腳(Dedicated clock)進去的信號,才能接片內鎖相環(PLL)嗎?? 在Altera的FPGA中,專用時鐘管腳是經過特殊處理的單獨管腳,其用途

2023-10-13 17:40:00 1292

1292 fpga跨時鐘域通信時,慢時鐘如何讀取快時鐘發送過來的數據? 在FPGA設計中,通常需要跨時鐘域進行數據通信。跨時鐘域通信就是在不同的時鐘域之間傳輸數據。 當從一個時鐘域傳輸數據到另一個時鐘域

2023-10-18 15:23:51 1901

1901 fpga與dsp通訊怎樣同步時鐘頻率?dsp和fpga通信如何測試? 在FPGA與DSP通訊時,同步時鐘頻率非常重要,因為不同的設備有不同的時鐘頻率,如果兩者的時鐘頻率不同步,會導致通訊數據的錯誤或

2023-10-18 15:28:13 2793

2793 FPGA為什么有時候還需要一個時鐘配置芯片提供時鐘呢? FPGA(Field Programmable Gate Array)是一種可編程邏輯器件,可以根據不同需要編程,實現不同的功能。在FPGA中

2023-10-25 15:14:20 2400

2400 CADENCE從原理圖到PCB步驟(精)

2022-12-30 09:19:46 35

35 從設計到生產,PCB小批量生產解密

2023-12-20 11:15:47 6627

6627 據悉,黑客可借助此漏洞獲取加密密鑰,進而盜取用戶個人信息。DMP作為內存系統中的角色,負責推測當前運行代碼所需訪問的內存地址。黑客則借此可預測下一步需獲取的數據位,以此干擾數據的預取過程,進而獲悉用戶敏感數據。此類攻擊行為被稱為“Go Fetch”操作。

2024-03-22 10:30:53 1529

1529 FPGA 中包含一些全局時鐘資源。以AMD公司近年的主流FPGA為例,這些時鐘資源由CMT(時鐘管理器)產生,包括DCM、PLL和MMCM等。

2024-04-25 12:58:30 3304

3304

在FPGA(現場可編程門陣列)設計中,消除時鐘抖動是一個關鍵任務,因為時鐘抖動會直接影響系統的時序性能、穩定性和可靠性。以下將詳細闡述FPGA中消除時鐘抖動的多種方法,這些方法涵蓋了從硬件設計到軟件優化的各個方面。

2024-08-19 17:58:54 3753

3753 爬蟲數據獲取實戰指南:從入門到高效采集 ? ? 在數字化浪潮中,數據已成為驅動商業增長的核心引擎。無論是市場趨勢洞察、競品動態追蹤,還是用戶行為分析,爬蟲技術都能助你快速捕獲目標信息。然而,如何既

2025-03-24 14:08:23 1331

1331

電子發燒友App

電子發燒友App

評論