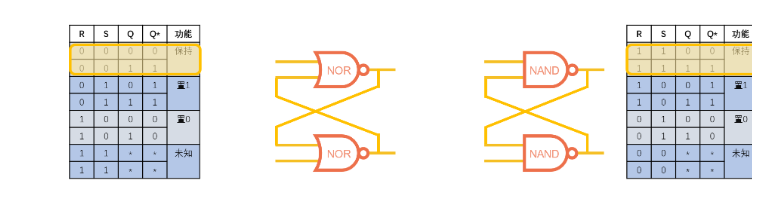

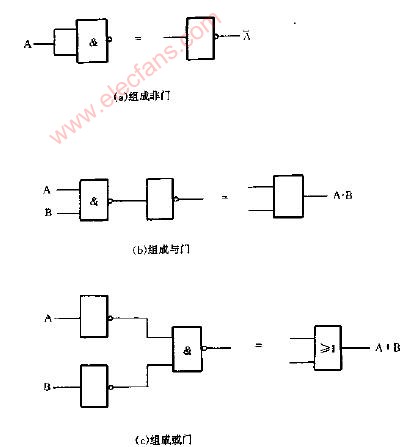

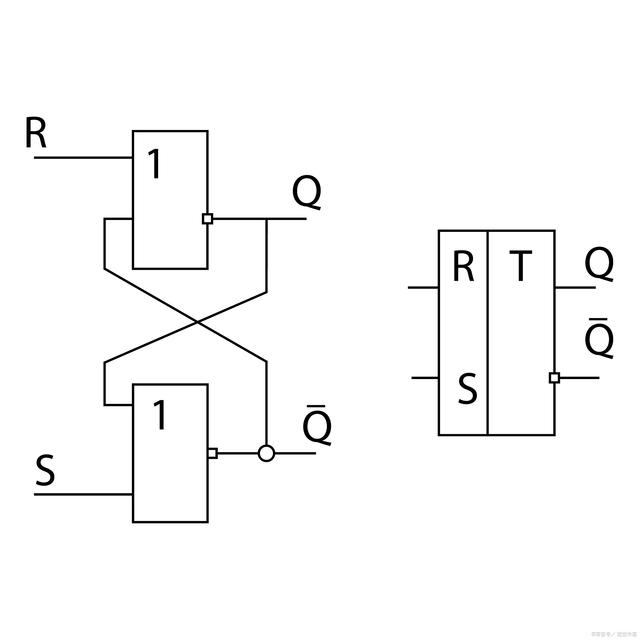

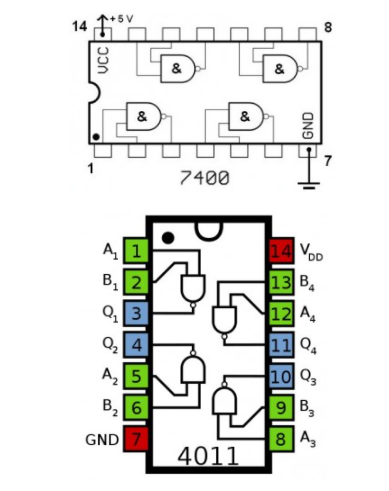

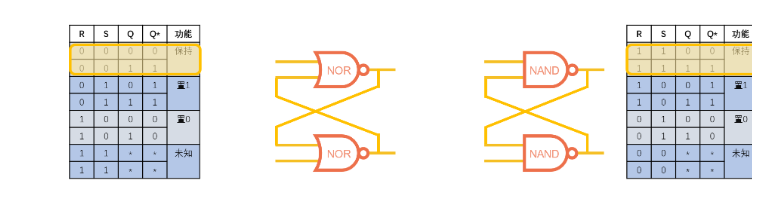

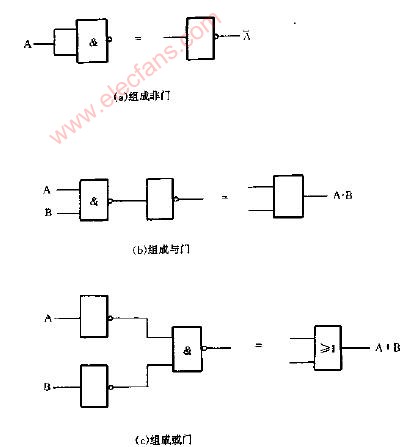

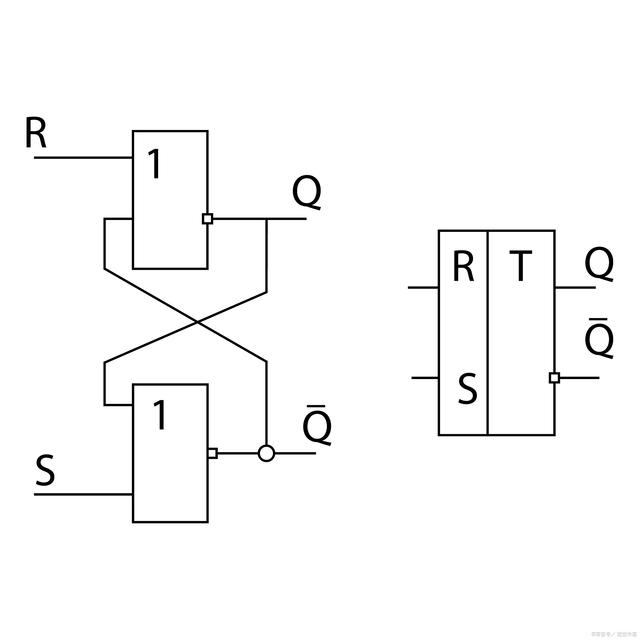

基本的RS觸發器是一種使用與非門和或非門構成的存儲器元件,它可以存儲一個比特的信息并在觸發信號的控制下改變狀態。與非門和或非門則是用于邏輯運算的基本門電路,它們執行邏輯“與”和“或”運算并輸出相應的結果。

2024-03-01 17:22:21 11972

11972

了解半加器、全加器的邏輯功能及三變量表決電路的邏輯功能。實驗儀器設備1. 數字集成電路實驗板 1塊2. 直流穩壓電源 1A,5V 1臺3. 函數信號發生器 1臺4. 示波器 1臺5. 附加集成器件雙

2008-09-25 17:28:34

串行時鐘發生器用來產生 I2C 通信的波特率時鐘 SCL。串行時鐘發生器采用 PCLK 作為輸入時鐘,通過 1 個 8bit的計數器計數,輸出所需波特率的 I2C 時鐘信號。

SCL 時鐘頻率計

2025-12-15 07:26:02

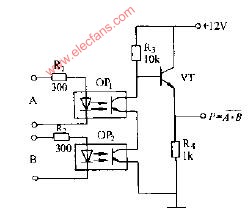

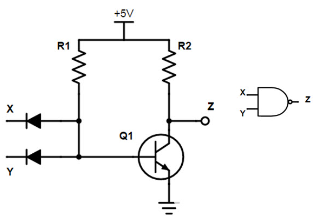

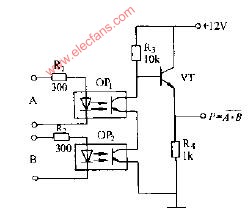

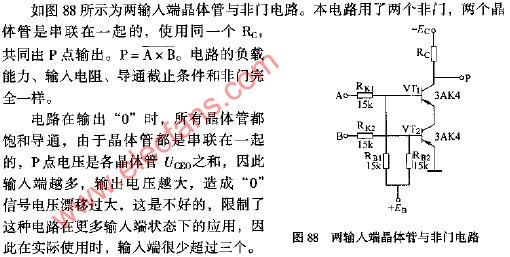

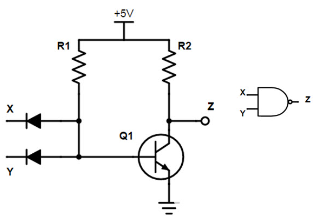

邏輯取反,從而使我們得到布爾值的表達式:AB= Q。然后,我們可以將2輸入數字邏輯與非門的操作定義為:“如果A和B都為真,則Q不為真”晶體管與非門可以使用如下所示連接在一起的RTL電阻-晶體管開關構建

2021-01-22 08:00:00

串行時鐘發生器用來產生 I2C 通信的波特率時鐘 SCL。串行時鐘發生器采用 PCLK 作為輸入時鐘,通過 1 個 8bit的計數器計數,輸出所需波特率的 I2C 時鐘信號。

SCL 時鐘頻率計

2025-12-08 08:16:31

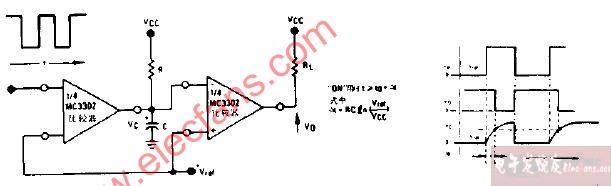

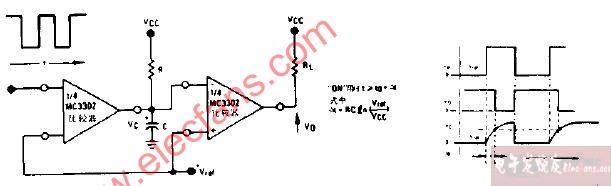

為什么我的pwm波信號一接到與非門上,幅值就會降一半(附電路圖)

2018-02-02 21:20:33

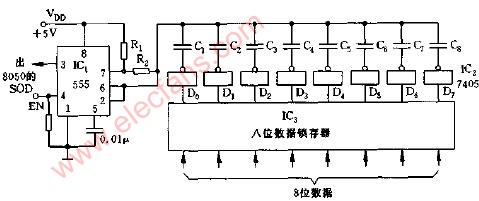

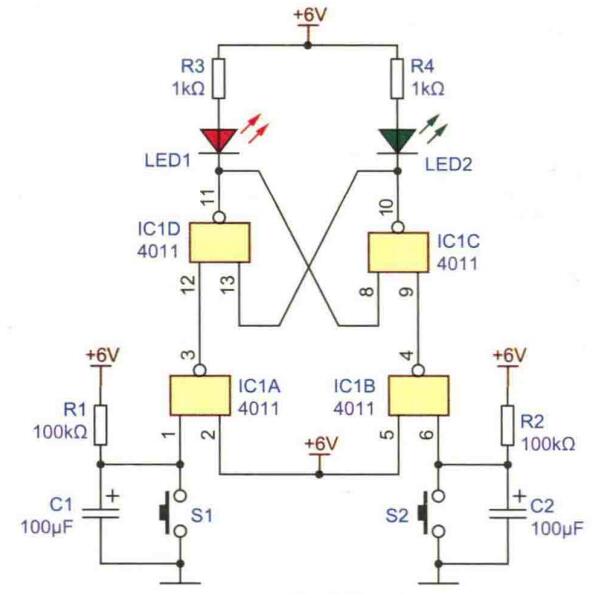

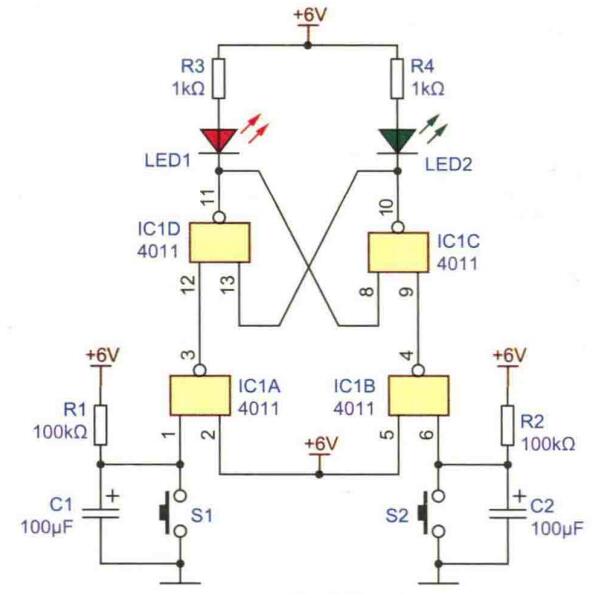

電路圖

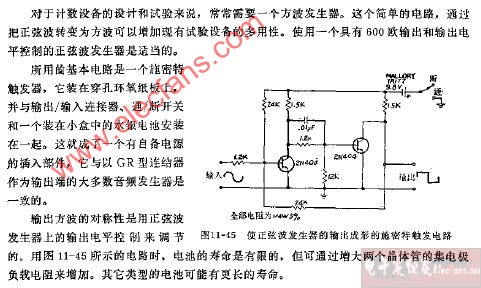

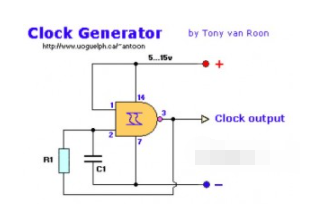

1、使用施密特觸發器的方波發生器

施密特觸發器方波發生器電路的工作與與非門的實現非常相似。 施密特觸發器電路如圖所示。這里也由 RC 網絡提供時序。 逆變器將其反饋形式的輸出作為輸入之一

2024-04-02 14:24:15

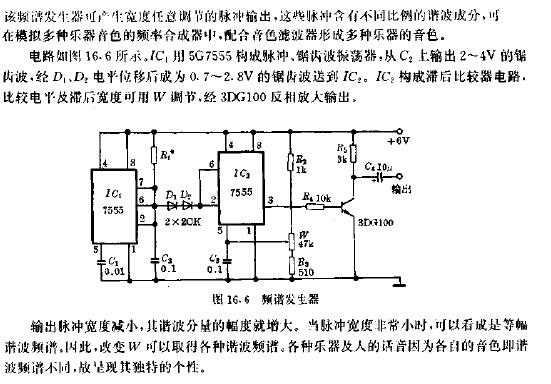

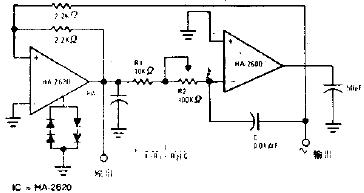

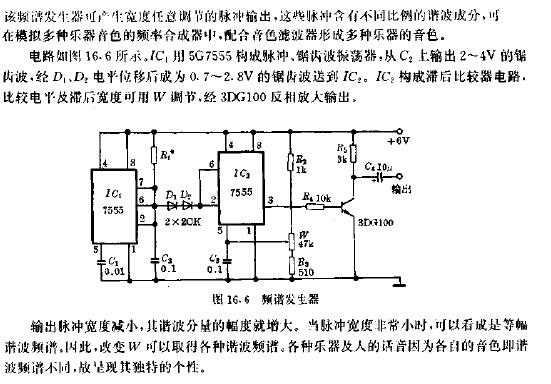

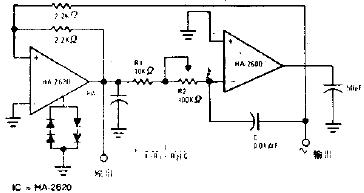

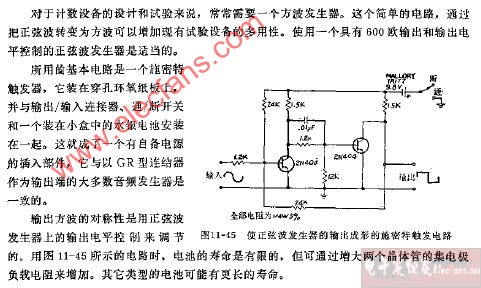

信號發生器電路圖

2019-10-09 09:11:01

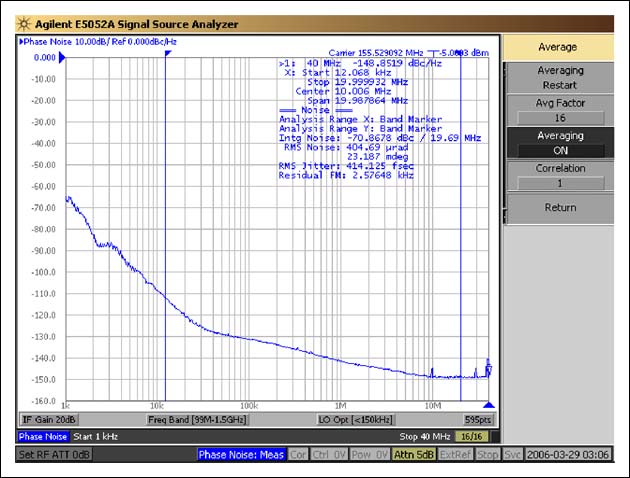

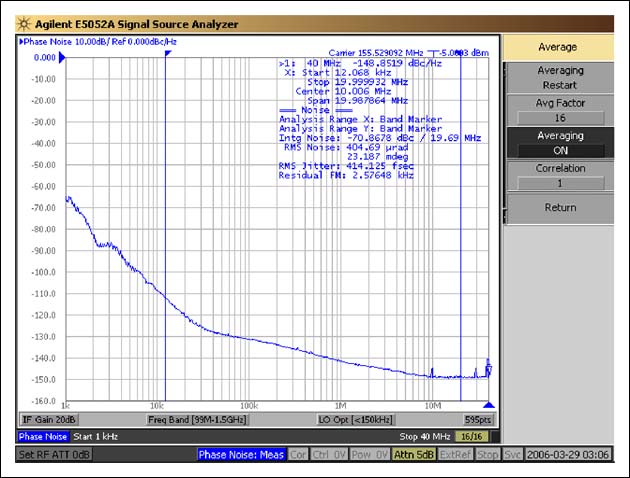

時鐘發生器芯片廠家 時鐘芯片是一種基于PLL的時鐘發生器,采用ADPLL(全數字鎖相環)技術,以實現的高頻低相噪性能,并具備低功耗和高PSNR能力,可實現小于0.3ps RMS的相位抖動性能

2023-12-29 09:29:50

時鐘發生器芯片廠家 時鐘芯片是一種基于PLL的時鐘發生器,采用ADPLL(全數字鎖相環)技術,以實現的高頻低相噪性能,并具備低功耗和高PSNR能力,可實現小于0.3ps RMS的相位抖動性能

2024-02-04 11:41:14

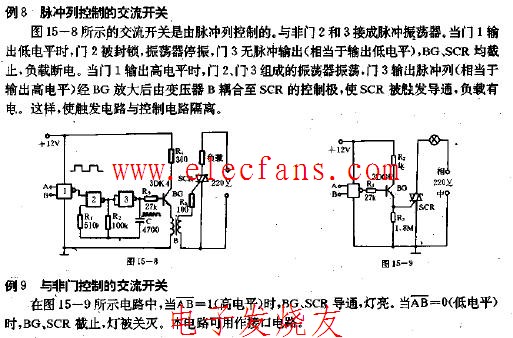

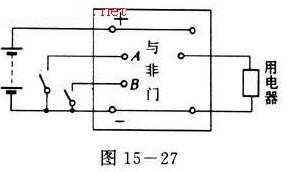

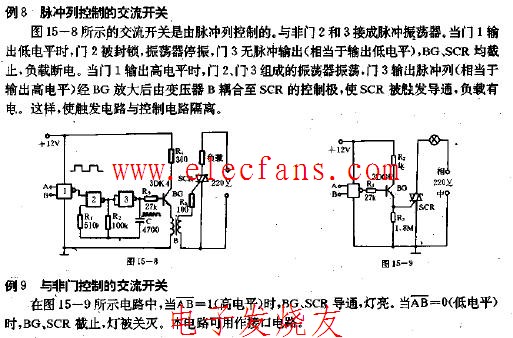

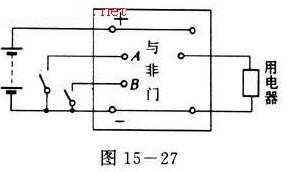

與非門控制的交流開關電路圖

2007-12-16 01:26:06 1395

1395

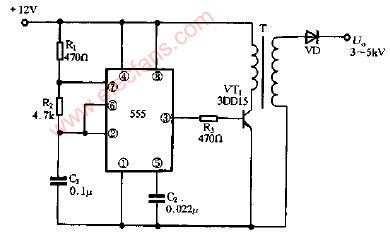

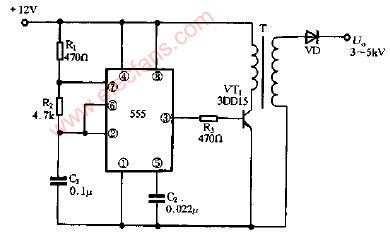

高壓發生器電路圖,這種高壓發生器適用于需要高電壓,小電流的場合,可獲得數千

2007-12-26 20:27:10 3229

3229

函數發生器電路圖,電路由MAX038,EL2001,TL072等元件組成,帶電源電路。

2007-12-26 20:57:43 3231

3231

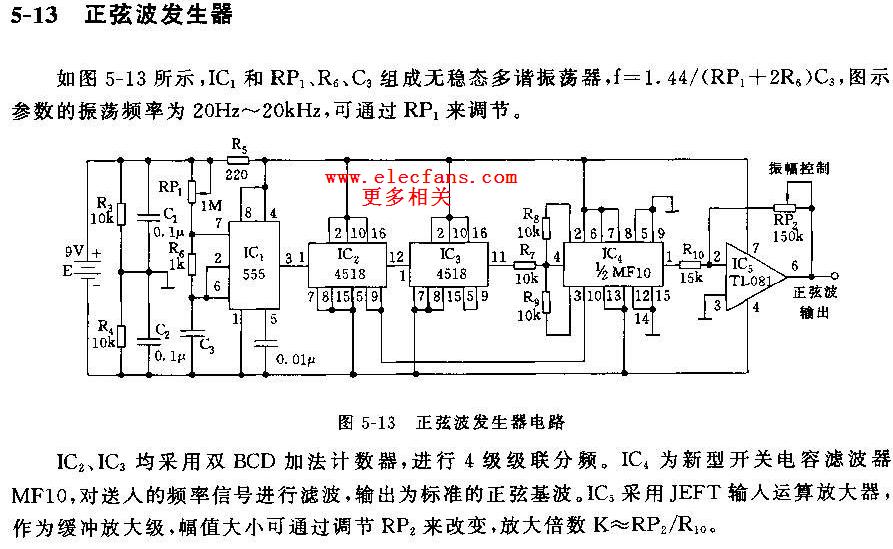

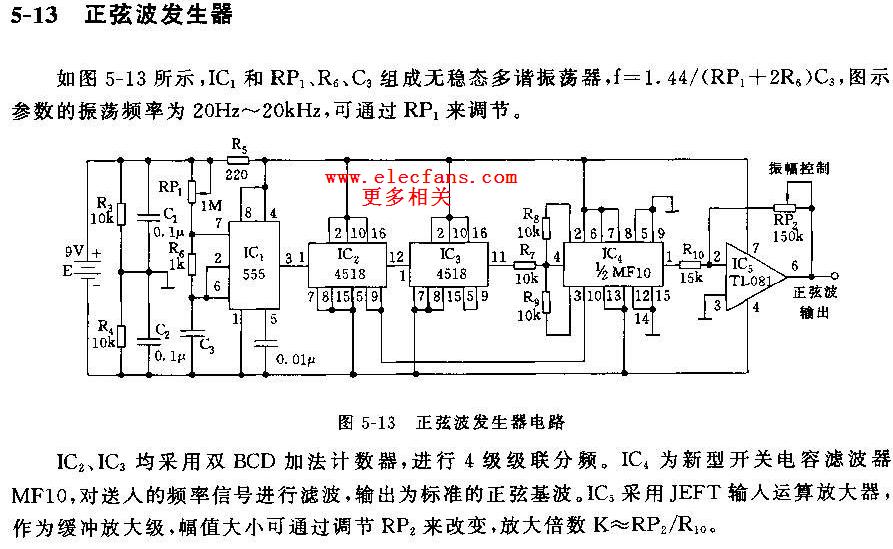

正弦波發生器電路圖,電路由IC,TL082組成。

圖二:正弦波信號發生器電路圖

2008-01-02 19:16:06 4256

4256

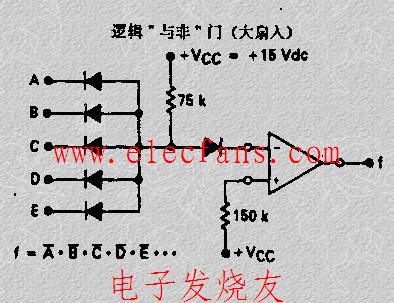

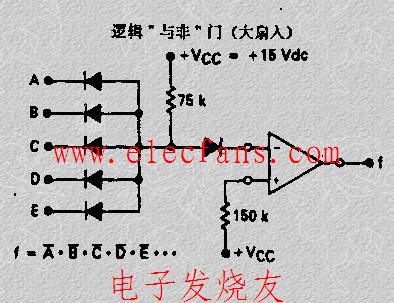

邏輯與非門

2008-06-12 23:24:21 2017

2017

MAX9489/MAX9471多輸出時鐘發生器構建集成時鐘源

摘要:與典型的“本地”時鐘方案相比,集成的多輸出時鐘發生器有許多優勢。本文探討了集中時鐘發生器(如

2008-10-04 20:43:25 1179

1179

Si5338 業界首個任意頻率、任意輸出的時鐘發生器

高性能模擬與混合信號領導廠商Silicon Laboratories日前發表全新的時鐘發生器和緩沖器系列,可為業

2008-11-10 09:39:44 2208

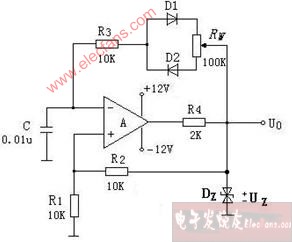

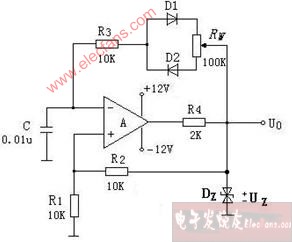

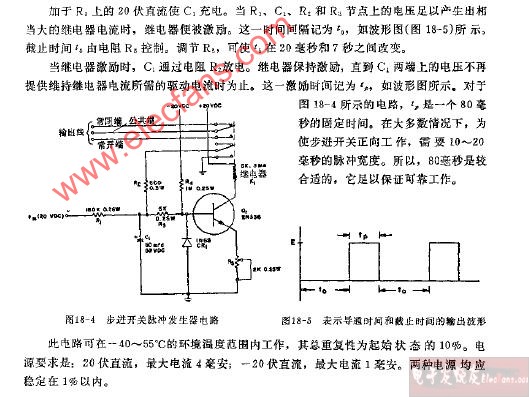

2208 方波發生器電路圖

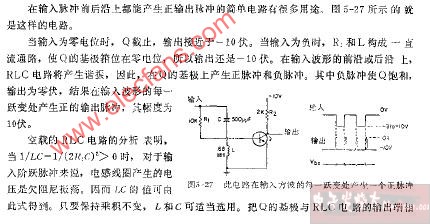

方波發生器電路圖如圖2所示:由反相輸入的滯回比較器

2009-03-15 17:13:35 12292

12292

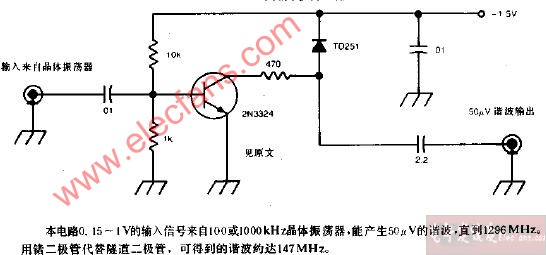

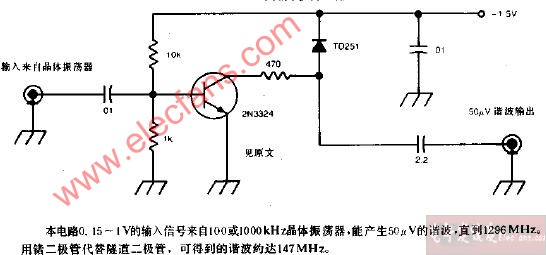

諧波發生器電路圖

2009-03-21 08:49:39 3879

3879

精密時鐘發生器電路圖

2009-03-25 09:35:22 1456

1456

延時發生器電路圖

2009-03-28 09:01:14 678

678

與非門邏輯符號

2009-04-06 01:12:18 2929

2929 與非門電路圖

2009-04-06 23:12:46 10460

10460

與非門邏輯符號圖

2009-04-06 23:13:21 43791

43791

與非門電路原理

(1)電路結構及工作原理 TTL與非門是TTL邏輯門的基本形式,典型的TTL與非門電路結構如圖8-16所示。該電路由

2009-04-06 23:14:15 20333

20333

與非門電路介紹圖15-26甲是我們實驗用的與非門,它也有兩個輸入瑞A、B,圖乙是它在電路中的接法。

2009-04-06 23:17:48 18020

18020

頻譜發生器電路圖

2009-04-09 12:01:31 1380

1380

振蕩器時鐘發生器電路圖

2009-04-13 08:54:22 934

934

函數發生器電路圖

2009-04-15 09:30:41 1773

1773

摘要:MAX9450/MAX9451/MAX9452是集成了VCXO,具有相同PLL內核和三種不同輸出(LVPECL, HSTL,LVDS)的高精度時鐘發生器。MAX945x時鐘發生器具有四個主要的特點:集成VCXO,工作頻率范圍寬,PLL

2009-04-22 09:42:01 1345

1345

摘要:與典型的“本地”時鐘方案相比,集成的多輸出時鐘發生器有許多優勢。本文探討了集中時鐘發生器(如MAX9489和MAX9471)的優點,如:降低系統成本、良好的信號完整性、抑制干

2009-04-22 10:11:53 538

538

摘要:與典型的“本地”時鐘方案相比,集成的多輸出時鐘發生器有許多優勢。本文探討了集中時鐘發生器(如MAX9489和MAX9471)的優點,如:降低系統成本、良好的信號完整性、抑制干

2009-05-03 11:07:05 852

852

方波發生器電路圖

2009-05-08 14:33:27 4632

4632

利用與非門組成的一些門電路圖

2009-05-08 14:35:10 20348

20348

高壓發生器電路圖

2009-05-08 14:52:45 3506

3506

繼電器與非門電路圖

2009-05-08 15:35:18 2483

2483

聲控發生器電路圖

2009-05-08 15:37:12 671

671

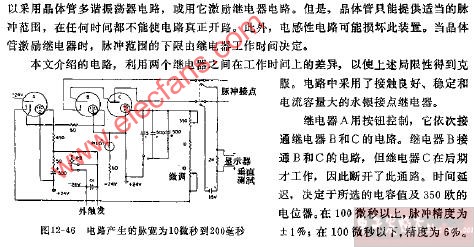

脈沖發生器電路圖

2009-05-18 15:57:26 1995

1995

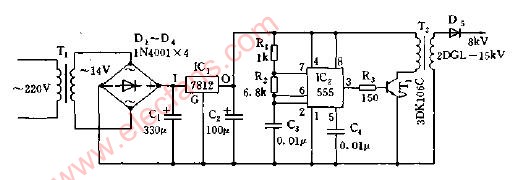

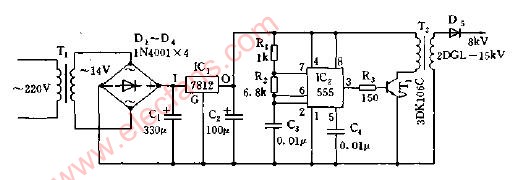

8kV高壓發生器電路圖

2009-05-30 13:42:17 2564

2564

數控音調發生器電路圖

2009-05-30 15:59:04 1192

1192

光耦合器構成的與非門電路圖

2009-06-04 16:25:53 5960

5960

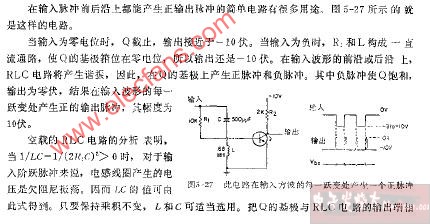

正脈沖發生器電路圖

2009-06-26 13:44:58 1246

1246

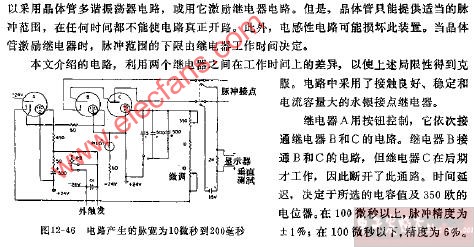

信號發生器的方波插入裝置電路圖

2009-06-30 13:46:04 767

767

單脈沖方波發生器電路圖

2009-07-01 11:47:00 2958

2958

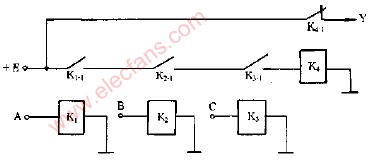

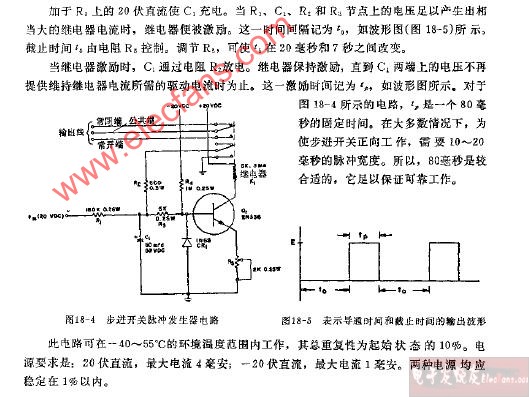

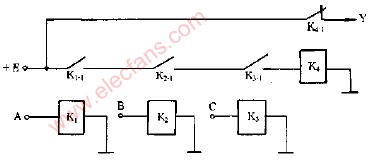

步進開關脈沖發生器電路圖

2009-07-03 14:11:08 1141

1141

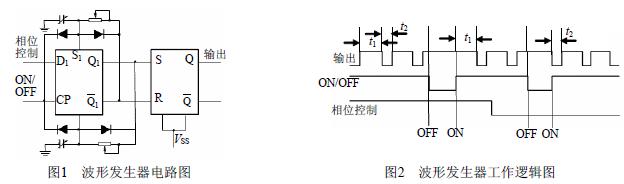

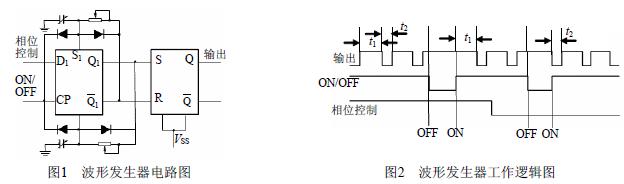

波形發生器電路圖

交流驅動電

2009-07-17 18:48:05 5340

5340

評估低抖動PLL時鐘發生器的電源噪聲抑制性能

本文介紹了電源噪聲對基于PLL的時鐘發生器的干擾,并討論了幾種用于評估確定性抖動(DJ)的技術方案。推導出的關系式提

2009-09-18 08:46:32 1853

1853

MAX3625B 抖動僅為0.36ps的PLL時鐘發生器

概述

MAX3625B是一款低抖動、精密時鐘發生器,優化用于網絡設備。器件內置晶體振蕩器和鎖相環(PLL)

2010-03-01 08:56:18 1615

1615

與非門,與非門是什么意思

DTL與非門電路:

常將二極管與門和或門與三極管非門組合起來組成與非門和或非門電路,以消除在串接時產生的電

2010-03-08 11:41:15 12493

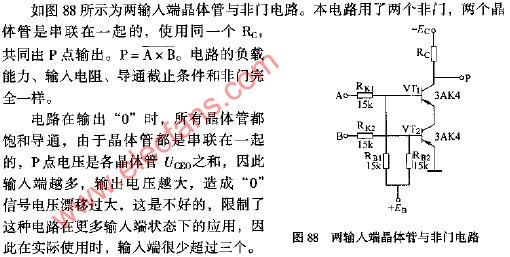

12493 兩輸入端晶體管與非門電路圖

2010-03-29 17:03:19 5168

5168

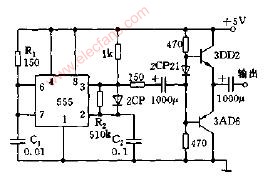

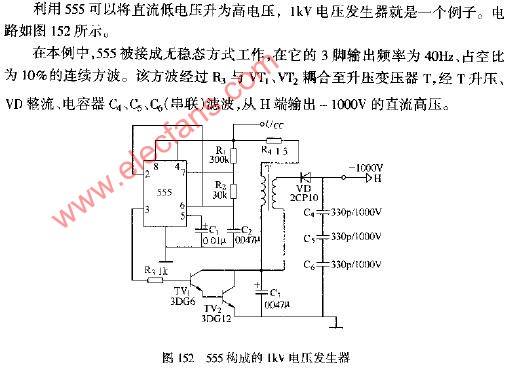

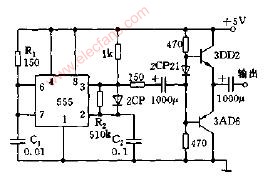

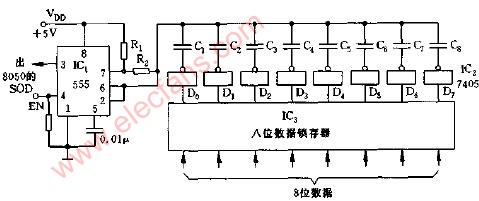

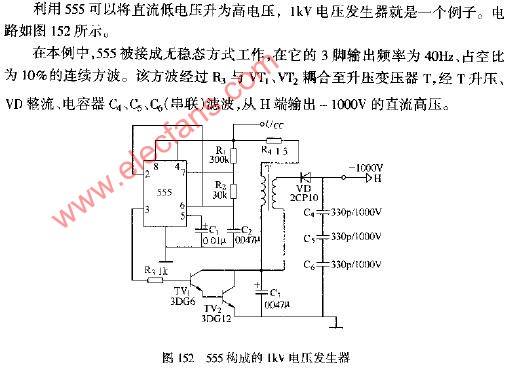

555構成的LKV電壓發生器電路圖

2010-03-30 15:08:05 1295

1295

MAX3679A高性能四路輸出時鐘發生器(Maxim)

Maxim推出用于以太網設備的高性能、四路輸出時鐘發生器MAX3679A。器件采用低噪聲

2010-04-14 16:51:49 1150

1150 如何利用GPS OEM來進行二次開發,產生高精度時鐘發生器是一個研究的熱點問題。在電力系統、CDMA2000、DVB、DMB等系統中,高精度的GPS

2010-07-24 15:45:26 944

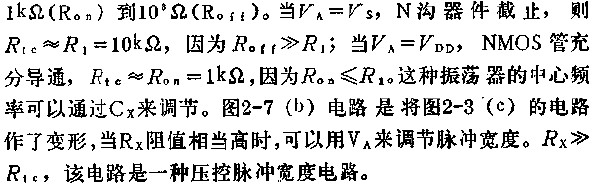

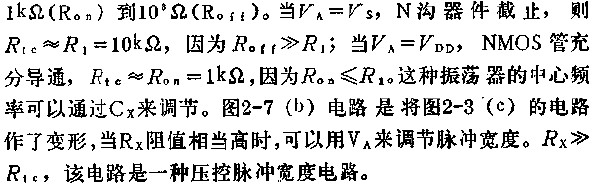

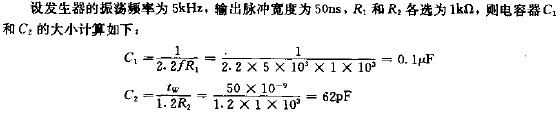

944 圖是用CMOS與非門組成的壓控振蕩器電路。

圖示線路類似圖C的電路,C由可調的CX代替

2010-09-13 22:26:59 1987

1987

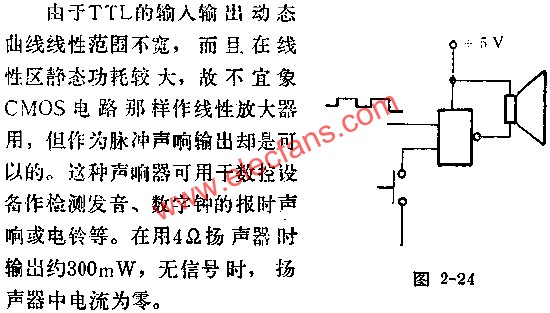

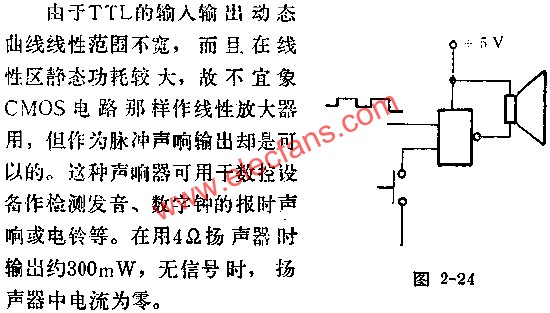

TTL與非門可以直接帶動一只4歐或8歐的小揚聲器,不用添加任何元件,只需將揚聲器由與非門輸出接至地端或電

2010-09-14 01:29:45 1012

1012

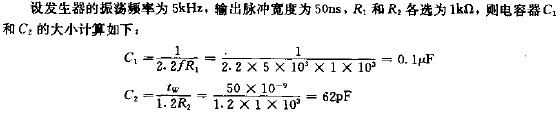

實際上,自激多諧振蕩器(圖1)和單穩電路可以由集成電路來實現.采用兩片四-2輸入與非門74LS00的驅動信號發生器,

2010-11-14 12:16:07 1271

1271

MAX3636是一個高度靈活,高精度鎖相環(PLL)時鐘發生器為下一代網絡設備的要求低抖動時鐘發生器和強大的高速數據傳輸的分布進行了優化。

2011-10-11 11:15:22 1699

1699

雙環路時鐘發生器可清除抖動并提供多個高頻輸出

2016-01-04 17:41:13 0

0 10GHz擴頻時鐘發生器的設計_胡帥帥

2017-01-07 21:28:58 1

1 系統設計師通常側重于為應用選擇最合適的數據轉換器,在向數據轉換器提供輸入的時鐘發生器件的選擇上往往少有考慮。然而,如果不慎重考慮時鐘發生器、相位噪聲和抖動性能,數據轉換器、動態范圍和線性度性能可能受到嚴重的影響。

2017-11-17 02:00:58 1248

1248

波形發生器原理圖+電路圖+程序

2017-11-23 09:13:31 34

34 Microchip基于MEMS的時鐘發生器

2018-06-07 13:46:00 5525

5525

Microchip基于MEMS的時鐘發生器

2018-07-08 01:23:00 4892

4892 關鍵詞:發生器 , 負電源 , 與非門 在電子設備中有時需用一組功率不大的負電源,可用三個與非門按圖所示方法連接,即可進行電源極性變換。圖示電路中A1、A2組成約4kHz的自激多諧振蕩器,A3起

2018-09-16 09:07:01 778

778 據麥姆斯咨詢報道,Microchip推出了業界尺寸最小的MEMS時鐘發生器DSC613。這款新器件可在電路板上最多替換掉三個晶振和振蕩器,從而減少高達80%的時鐘元件布板空間。

2018-11-15 16:38:26 4925

4925 AD9523:14路LVPECL/LVDS/HSTL輸出 或29路LVCMOS輸出 低抖動時鐘發生器

2019-07-04 06:18:00 4964

4964 邏輯與非門是數字邏輯與門和非門串聯連接在一起的組合,NAND (非與)門具有當輸入的ALL處于邏輯電平“1”時,輸出通常處于邏輯電平“1”并且僅“低”到邏輯電平“0”。邏輯與非門是我們之前看到的AND門的反向或“互補”形式。

2019-06-26 14:20:46 11836

11836

這是一個由與非門組成的、具有自動復位功能的搶答器實驗電路,電路原理圖見圖4-121-1所示。

2019-09-27 09:21:03 11699

11699

本文檔的主要內容詳細介紹的是使用Multisim實現與非門測試的實驗電路圖免費下載。

2020-09-04 16:55:00 20

20 本文檔的主要內容詳細介紹的是與非門邏輯電路功能測試的原理圖免費下載。

2020-10-12 16:18:48 25

25 本文檔的主要內容詳細介紹的是與非門搭接的邏輯電路原理圖免費下載。

2020-10-12 16:18:48 7

7 系統設計師通常側重于為應用選擇最合適的數據轉換器,在向數據轉換器提供輸入的時鐘發生器件的選擇上往往少有考慮。然而,如果不慎重考慮時鐘發生器的相位噪聲和抖動性能,數據轉換器動態范圍和線性度性能可能受到嚴重的影響。

2020-11-22 11:34:38 3554

3554

AD9525: 8路LVPECL輸出低抖動時鐘發生器

2021-03-21 15:00:20 0

0 AD9540:655 MHz低抖動時鐘發生器數據表

2021-03-22 19:57:57 0

0 AD9571:以太網時鐘發生器,10個時鐘輸出

2021-04-16 10:21:56 3

3 AD9520-5:12 LVPECL/24 CMOS輸出時鐘發生器數據表

2021-04-27 21:31:55 2

2 AD9516-5:14-輸出時鐘發生器數據表

2021-04-27 21:41:19 5

5 AD9551:多業務時鐘發生器數據表

2021-04-28 10:30:52 0

0 AD9522-5:12 LVDS/24 CMOS輸出時鐘發生器數據表

2021-04-28 10:53:01 0

0 AD9573:PCI-Express時鐘發生器IC,PLL內核,分頻器,雙輸出數據表

2021-05-08 20:05:05 5

5 AD9575:網絡時鐘發生器,雙輸出數據表

2021-05-09 11:06:44 1

1 AD9531:3通道時鐘發生器,24輸出數據表

2021-05-15 15:24:07 11

11 AD9576:雙鎖相環異步時鐘發生器數據表

2021-05-16 12:57:55 0

0 時鐘發生器AD9516-0技術手冊

2022-01-25 15:59:42 8

8 Cypress時鐘發生器應用在車輛、工業生產、消費品和網絡服務的EMI降低和非EMI降低時鐘發生器。 Cypress具有廣泛的時鐘發生器組合,兼容700MHz的頻率和不超過0.7PS的RMS相位抖動

2022-04-22 09:02:09 1314

1314 這是帶有板上芯片(COB)的1Hz時鐘發生器電路。通常,為數字時鐘和計數器電路應用產生1Hz時鐘的電路將IC與晶體和微調電容器等結合使用。

2022-06-07 10:43:50 3854

3854

邏輯門是數字世界中的基本元素,之前已經介紹過基本的邏輯門。這些基本的邏輯門可以由通用門構成。數字邏輯中有兩個通用門,即與非門(NAND Gate)和或非門(NOR Gate)。

2022-09-12 14:50:00 13786

13786

超低抖動時鐘發生器如何優化串行鏈路系統性能

2022-11-04 09:50:15 0

0 9ZXL1951D PCIe 時鐘發生器評估板用戶指南

2023-03-21 19:21:13 1

1 本文討論電源噪聲干擾對基于PLL的時鐘發生器的影響,并介紹幾種用于評估由此產生的確定性抖動(DJ)的測量技術。派生關系顯示了如何使用頻域雜散測量來評估時序抖動行為。實驗室臺架測試結果用于比較測量技術,并演示如何可靠地評估參考時鐘發生器的電源噪聲抑制(PSNR)性能。

2023-04-11 11:06:39 2462

2462

9ZXL1951D PCIe 時鐘發生器評估板用戶指南

2023-07-07 19:19:11 0

0 與非門(NAND Gate)是數字電路中的基本邏輯門之一,它實現了邏輯AND(與)操作后再進行邏輯NOT(非)操作。

2023-09-04 15:31:07 7040

7040

時鐘發生器由哪些部分組成?鎖相環pll的特點是什么?如何用硬件配置pll? 時鐘發生器是指通過特定的電路設計產生適合各種電子設備使用的時鐘信號的器件。時鐘發生器由多個部分組成,其中最核心的是鎖相環

2023-10-13 17:39:50 2233

2233 時鐘合成器和時鐘發生器是兩種用于產生時鐘信號的電子器件,它們在功能和應用上有一些區別。

2023-11-09 10:26:56 1541

1541 的時鐘發生器件的選擇上往往少有考慮。目前市場上有性能屬性大相徑庭的眾多時鐘發生器。然而,如果不慎重考慮時鐘發生器、相位噪聲和抖動性能,數據轉換器、動態范圍和線性度性能可能受到嚴重的影響。...

2023-11-28 14:33:57 0

0 TTL與非門的電壓傳輸特性 TTL與非門的靜態輸入與輸出特性 TTL與非門的動態特性? TTL與非門是一種基本的邏輯門電路,用于將兩個輸入信號進行邏輯與運算,并輸出結果。TTL(雙晶體管邏輯)是一種

2024-01-23 13:52:51 7603

7603 時鐘發生器,作為一種關鍵的電子設備,負責生成精確且穩定的時鐘信號。這些信號在各類電子系統中作為時間基準,確保系統的正常運行和性能。本文將深入探討時鐘發生器的定義、工作原理、特點及其在實際應用中的廣泛案例,以期為相關領域的研究者和工程師提供全面的技術參考。

2025-02-05 17:17:34 1706

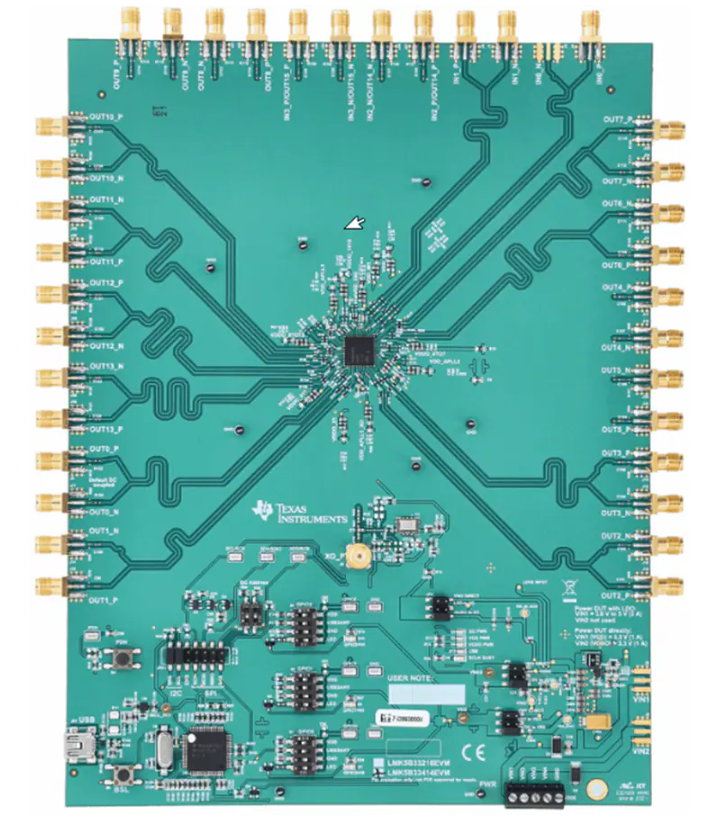

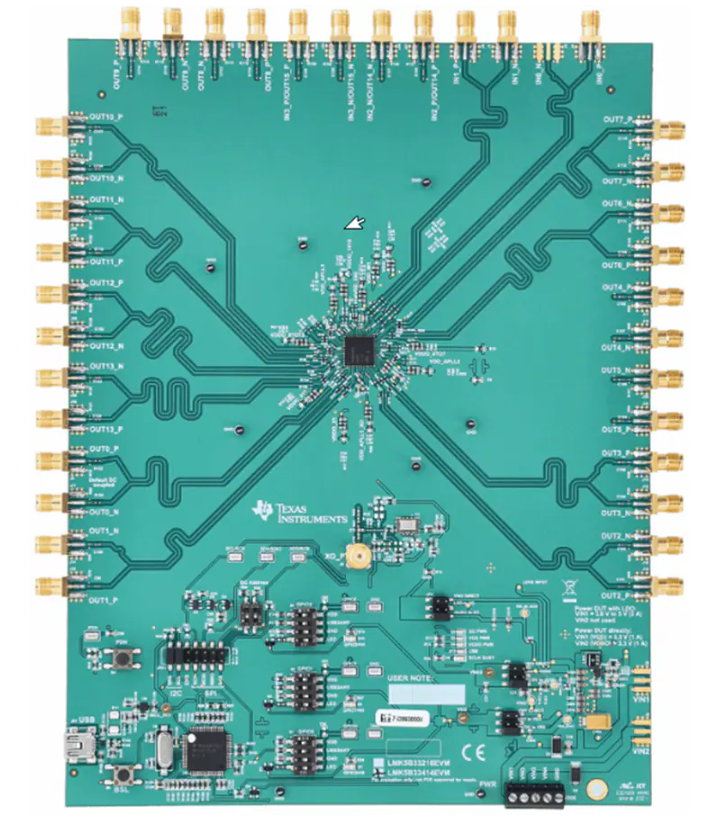

1706 Texas Instruments LMK5B33414EVM時鐘發生器和合成器評估模塊 (EVM) 是一個用于對LMK5B33414網絡時鐘發生器和同步器進行器件評估、合規性測試和系統原型設計的平臺。

2025-09-08 15:03:16 680

680

的關鍵因素。技術創新的先鋒時鐘發生器技術的不斷創新是其保持競爭力的首要因素。通過采用前沿的半導體材料和先進的電路設計,現代時鐘發生器能夠實現更高的頻率穩定性和更低

2025-10-23 17:20:30 493

493

電子發燒友App

電子發燒友App

評論