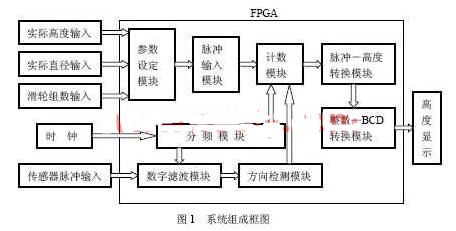

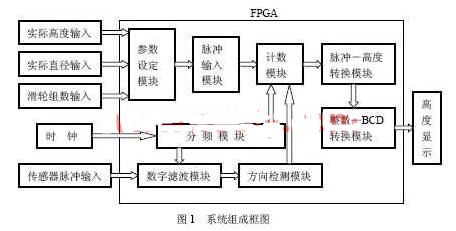

本文采用的是ALTERA公司的EP1C6Q240C8型號的FPGA,整個體統采用模塊化設計的思想,將各個模塊用VHDL語言描述出來再進行連接。

2020-08-04 09:39:44 2332

2332

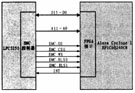

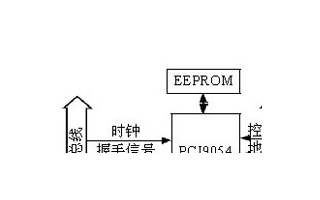

為了方便對1553B設備進行測試,介紹了一種基于ARM9平臺和FPGA的1553B總線測試系統的設計與實現方法。該系統以LPC3250作為微處理器,以CYCLONE I系列的EP1C6Q240C8芯片實現ARM與1553B協議芯片的接口邏輯。

2015-04-21 14:49:08 4605

4605

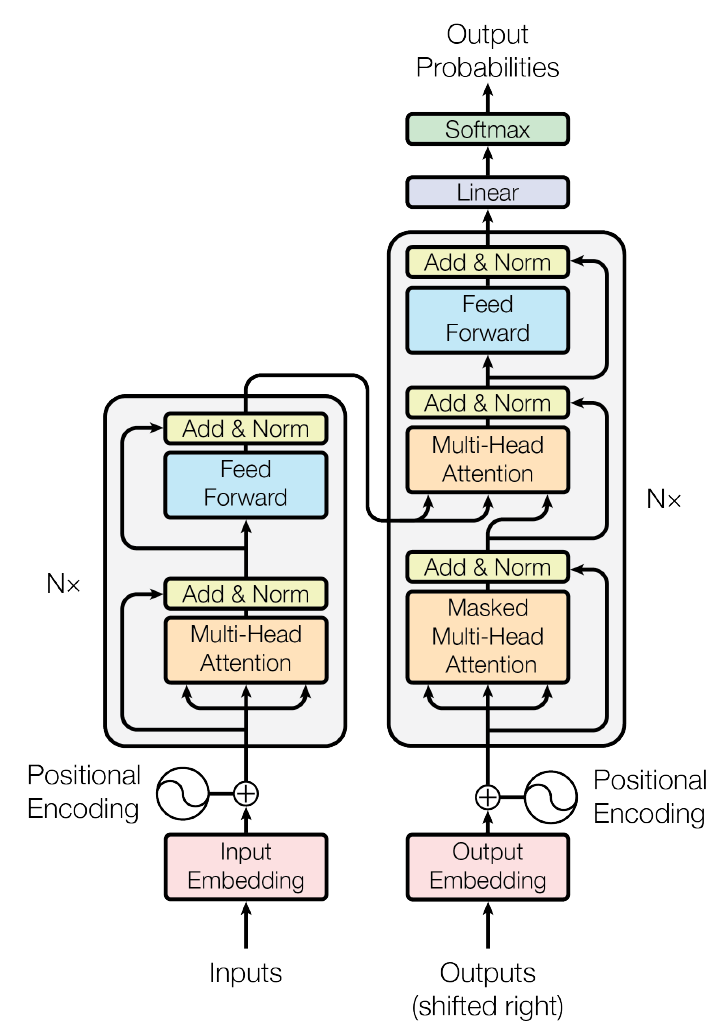

前言 AI芯片(這里只談FPGA芯片用于神經網絡加速)的優化主要有三個方面:算法優化,編譯器優化以及硬件優化。算法優化減少的是神經網絡的算力,它確定了神經網絡部署實現效率的上限。編譯器優化和硬件優化

2020-09-29 11:36:09 5773

5773

現在Altera的網頁已經下載不到支持EP1C6Q240元件的開發軟件,求各位網友大力支持!

2025-06-11 06:15:28

本帖最后由 mr.pengyongche 于 2013-4-30 02:58 編輯

EP1C6Q240C6開發板原理

2012-08-11 10:10:06

EP1C6Q240C6開發板原理圖

2012-08-20 15:21:25

本資料為EP1C6Q240C6開發板原理圖

2012-04-19 11:19:41

EP2C5T144C8、EP2C8T144C8、EP2C8Q208C8這三種芯片的區別,用哪種芯片較好?買哪種芯片的學習開發板較好? 謝謝大家的求解!!!

2013-07-21 19:46:34

EP2C5T144C8、EP2C8T144C8、EP2C8Q208C8這是三種芯片的區別,用哪種芯片較好?買哪種芯片的開發板較好?謝謝大家的求解啊!!!

2013-07-21 19:58:40

一、FPGA核心板:多種核心板供選擇,所采用的FPGA分別有:(1)Cyclone核心:EP1C12Q240C8、EP1C6Q240C8;(2)CycloneII核心

2009-11-02 18:55:54

有:(1)Cyclone核心:EP1C12Q240C8、EP1C6Q240C8;(2)CycloneII核心:EP2C8Q208C8、EP2C5Q208C8、EP2C20Q208C8;(3)SDRAM

2009-10-23 15:15:24

畢業設計得做與FPGA有關的論文 ,現在正在用***畫 FPGA EP1C6Q240C8 外圍電路圖,請教各位高手,本人不會,謝謝~!

2009-04-07 09:15:55

board manual.pdfEP1C6Q240C6開發板原理圖.pdfEPM1270F256C5 MAX_II_board_schematics.pdf

2012-04-19 11:12:40

第1章 概述 1.1 人工神經網絡研究與發展 1.2 生物神經元 1.3 人工神經網絡的構成 第2章人工神經網絡基本模型 2.1 MP模型 2.2 感知器模型 2.3 自適應線性

2012-03-20 11:32:43

如題,Altera的FPGA芯片EP2C8Q208開發板沒驅動,u***驅動不了,怎么辦呀,求助

2013-10-28 12:18:14

;nbsp;核心是DSP 處理器TMS320VC5416,最高工作頻率160M2、 擴展一片Altera 15萬門Cyclone FPGA EP1C6Q240C8,給

2009-11-27 15:49:35

是一臺包含GPU的服務器或高性能PC,Device從機是一個ZYNQ/FPGA開發板。另一方面,通常情況下,當落地到具體場景解決某個具體問題時,神經網絡算法通常僅是整體解決方案的一小部分,其他的算法和流程

2020-05-18 17:13:24

FPGA加速的關鍵因素是什么?EdgeBoard中神經網絡算子在FPGA中的實現方法是什么?

2021-09-28 06:37:44

NMSIS NN 軟件庫是一組高效的神經網絡內核,旨在最大限度地提高 Nuclei N 處理器內核上的神經網絡的性能并最??大限度地減少其內存占用。

該庫分為多個功能,每個功能涵蓋特定類別

2025-10-29 06:08:21

CY7C68013A-128AXC、FPGA芯片EP1C6Q240C8和SDRAM芯片IS61LV25616AL-10T共同組合完成,實現USB2.0的高速傳輸。本USB+FPGA開發板的實際傳輸速度

2010-03-25 16:01:56

請問:我在用labview做BP神經網絡實現故障診斷,在NI官網找到了機器學習工具包(MLT),但是里面沒有關于這部分VI的幫助文檔,對于”BP神經網絡分類“這個范例有很多不懂的地方,比如

2017-02-22 16:08:08

習神經神經網絡,對于神經網絡的實現是如何一直沒有具體實現一下:現看到一個簡單的神經網絡模型用于訓練的輸入數據:對應的輸出數據:我們這里設置:1:節點個數設置:輸入層、隱層、輸出層的節點

2021-08-18 07:25:21

《 AI加速器架構設計與實現》+第一章卷積神經網絡觀感

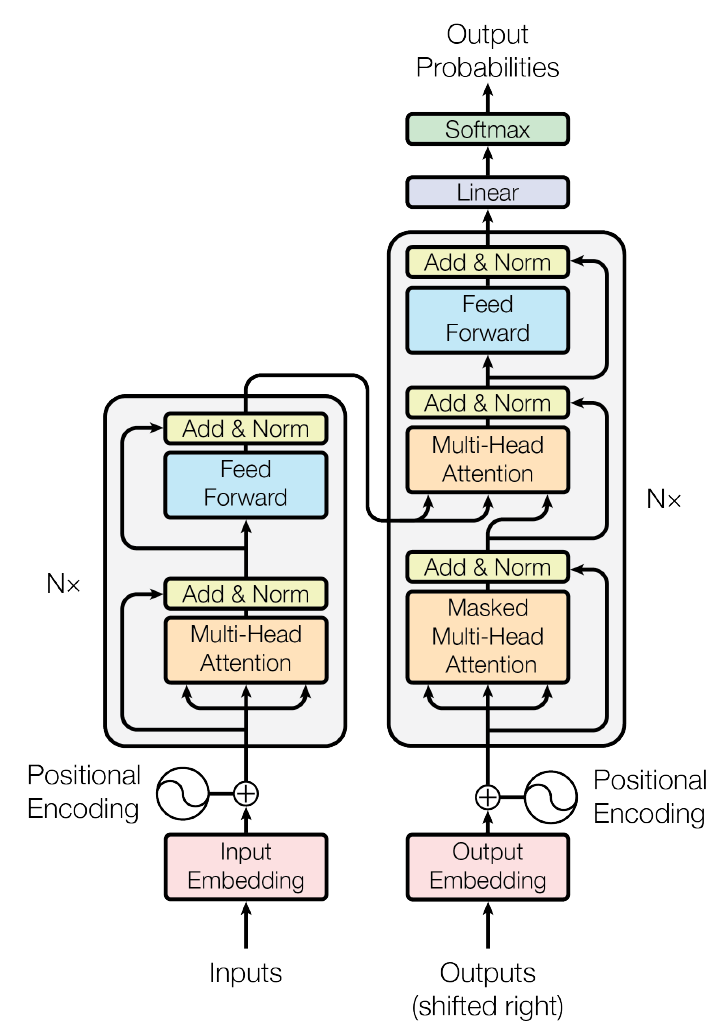

? ?在本書的引言中也提到“一圖勝千言”,讀完第一章節后,對其進行了一些歸納(如圖1),第一章對常見的神經網絡結構進行了介紹,舉例了一些結構

2023-09-11 20:34:01

的神經網絡編程,想基于此開發板,進行神經網絡的學習,訓練和測試神經網絡。項目計劃:1.基于官方的文檔及資料,熟悉此開發板。2.測試官方demo,學習ARM內核和FPGA如何協調工作。3.基于自己最近

2019-01-09 14:48:59

項目名稱:基于PYNQ的神經網絡自動駕駛小車試用計劃:一、本人技術背景本人有四年以上的嵌入式開發和三年以上的機器視覺領域項目實踐經驗,在計算機視覺與FPGA數字圖像處理方面有較多的理論研究與項目實踐

2018-12-19 11:36:24

,得到訓練參數2、利用開發板arm與FPGA聯合的特性,在arm端實現圖像預處理已經卷積核神經網絡的池化、激活函數和全連接,在FPGA端實現卷積運算3、對整個系統進行調試。4、在基本實現系統的基礎上

2018-12-19 11:37:22

,神經網絡技術的第三次發展浪潮仍在繼續,在其背后,高性能CPU、GPU和FPGA、ASIC以強大的算力為技術的應用落地提供了有力的支持。然而目前基于FPGA平臺搭建神經網絡作為控制器,適合我們自己動手實現

2019-03-02 23:10:52

人工神經網絡(Artificial Neural Network,ANN)是一種類似生物神經網絡的信息處理結構,它的提出是為了解決一些非線性,非平穩,復雜的實際問題。那有哪些辦法能實現人工神經網絡呢?

2019-08-01 08:06:21

簡單理解LSTM神經網絡

2021-01-28 07:16:57

我們可以對神經網絡架構進行優化,使之適配微控制器的內存和計算限制范圍,并且不會影響精度。我們將在本文中解釋和探討深度可分離卷積神經網絡在 Cortex-M 處理器上實現關鍵詞識別的潛力。關鍵詞識別

2021-07-26 09:46:37

FPGA實現神經網絡關鍵問題分析基于FPGA的ANN實現方法基于FPGA的神經網絡的性能評估及局限性

2021-04-30 06:58:13

FPGA 上實現卷積神經網絡 (CNN)。CNN 是一類深度神經網絡,在處理大規模圖像識別任務以及與機器學習類似的其他問題方面已大獲成功。在當前案例中,針對在 FPGA 上實現 CNN 做一個可行性研究

2019-06-19 07:24:41

不確定因素影響,并且隨著可編程片上系統SoPC和大規模現場可編程門陣列FPGA的出現,為神經網絡控制器的硬件實現提供了新的載體。

2019-08-12 06:25:35

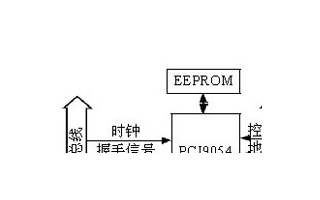

某人工神經網絡的FPGA處理器能夠對數據進行運算處理,為了實現集數據通信、操作控制和數據處理于一體的便攜式神經網絡處理器,需要設計一種基于嵌入式ARM內核及現場可編程門陣列FPGA的主從結構處理系統滿足要求。

2021-05-21 06:35:27

訓練一個神經網絡并移植到Lattice FPGA上,通常需要開發人員既要懂軟件又要懂數字電路設計,是個不容易的事。好在FPGA廠商為我們提供了許多工具和IP,我們可以在這些工具和IP的基礎上做

2020-11-26 07:46:03

(Digital Signal Processor)相比,現場可編程門陣列(Field Programma-ble Gate Array,FPGA)在神經網絡的實現上更具優勢。DSP處理器在處理時采用指令順序執行

2019-08-08 06:11:30

FPGA的嵌入式應用。某人工神經網絡的FPGA處理器能夠對數據進行運算處理,為了實現集數據通信、操作控制和數據處理于一體的便攜式神經網絡處理器,需要設計一種基于嵌入式ARM內核及現場可編程門陣列FPGA的主從結構處理系統滿足要求。

2019-09-20 06:15:20

學生做創新實驗 學校提供的EP1C6Q240C8N芯片 但是沒有給芯片的資料。自己去找的又全是英文版的 看不懂還不知道哪些有用。哪位用過的前輩麻煩指導一下,特別是AD轉換那 如果有引腳介紹什么的就最好了 可以聯系我QQ1428685070 萬分感謝了

2013-09-17 23:15:57

小弟最近在設計一款雙核采集系統使用ep1c6q240c8和tms320vc5509a雙核,兩塊芯片使用外部雙口RAM進行數據傳輸,請教各位大神ep1c6q240c8怎么和雙口RAM連接啊???????????????????????

2012-11-05 10:42:41

FPGA型號為:EP1C6Q240C8

2016-09-17 15:46:18

1、加速神經網絡的必備開源項目 到底純FPGA適不適合這種大型神經網絡的設計?這個問題其實我們不適合回答,但是FPGA廠商是的實際操作是很有權威性的,現在不論是Intel還是Xilinx都沒有在

2022-10-24 16:10:50

脈沖耦合神經網絡(PCNN)在FPGA上的實現,實現數據分類功能,有報酬。QQ470345140.

2013-08-25 09:57:14

采用EP1C6Q240C8和VHDL的定時器的設計

2012-08-17 09:53:38

基FPGA Cyclone II_EP2C5 EP2C8的頻率計

基FPGA_Cyclone_II_EP2C5/EP2C8的頻率計

功能描述:按4*4鍵盤上的1,2,3...號按鍵可依次測出 25000000Hz ,12500000Hz ....的分

2008-11-30 12:17:01 87

87 斑梨電子FPGA CycloneII EP2C5T144 學習板 開發板產品參數1. 采用ALTERA公司的CyclonellEP2C5T144芯片作為核心最小系統,將FPGA

2023-02-03 15:14:29

此套開發板采用altera公司的CYCLONE II系列芯片EP2C5Q208C8 和 EP2C8 Q208C8作為核心處理器設計,CYCLONE II系列芯片可以說是目前市場上性價比最高的芯片,比第一代的EP1C6 或者 EP1C12等

2010-08-11 16:42:56 47

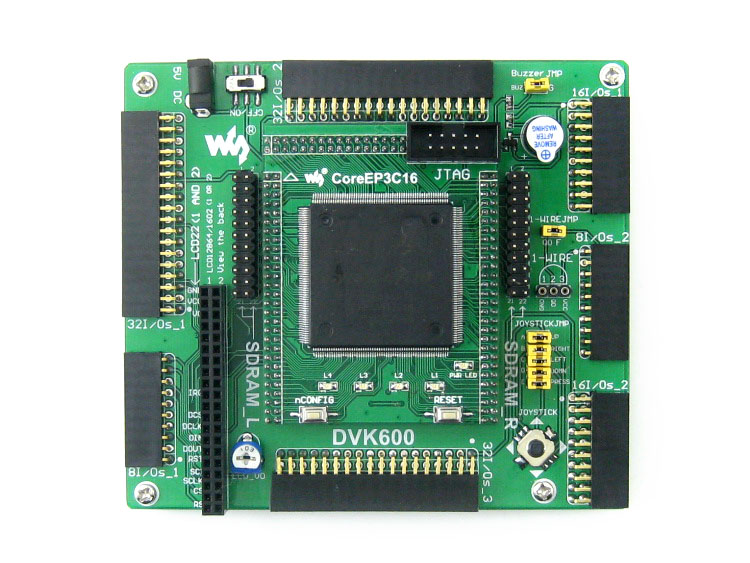

47 設計和實現了一個以Altera FPGA的Cyclone器件EP1C6Q240C8為核心的多功能實驗板.它分為核心板和擴展板, 用戶可以結合QuartusII集成開發環境, 使用VHDL語言、Verilog HDL語言或原理圖, 進行編

2010-09-14 16:38:06 12

12 以89S52單片機和EP1C6Q240C8型FPGA為控制核心的多功能計數器,是由峰值檢波、A/D轉換、程控放大、比較整形、移相網絡部分組成,可實現測量正弦信號的頻率、周期和相位差的功能。多

2010-12-27 15:21:44 78

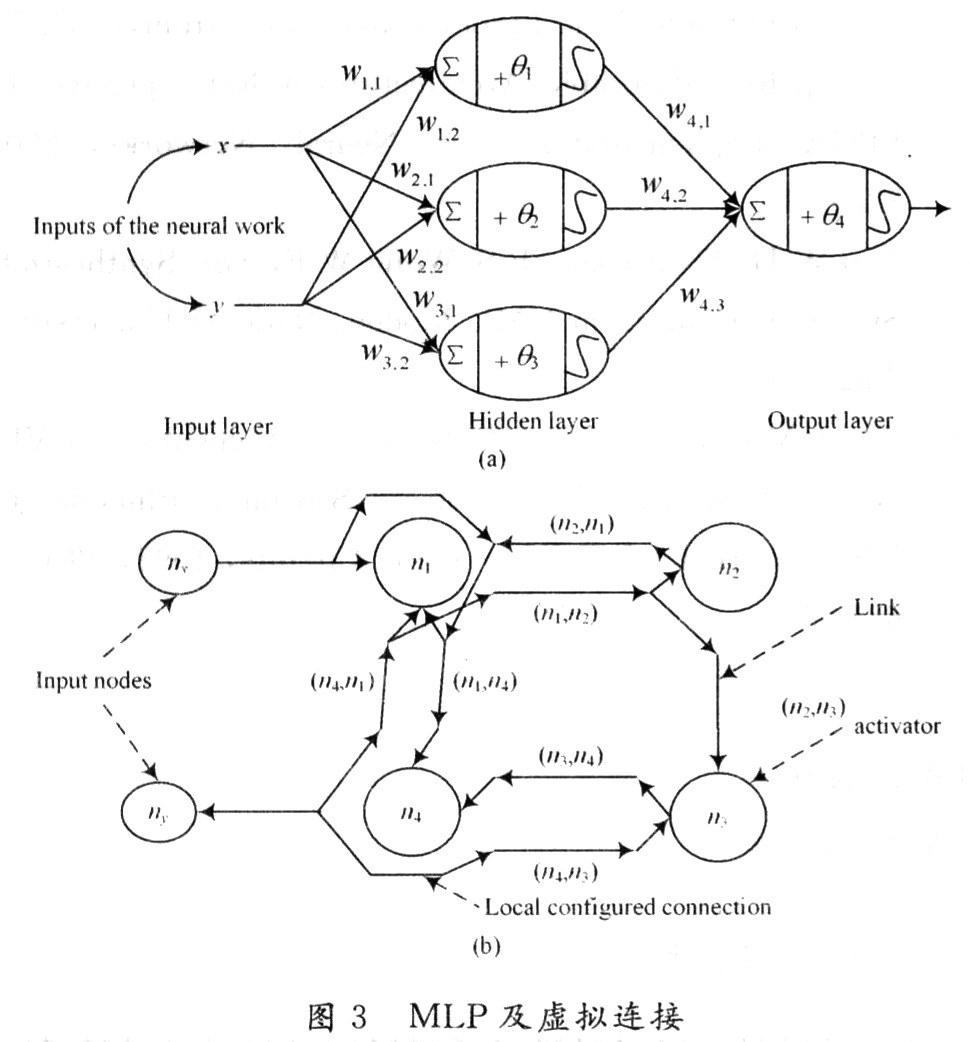

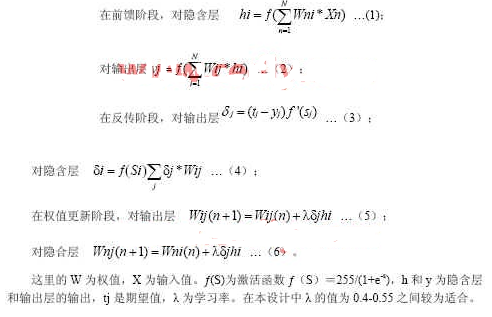

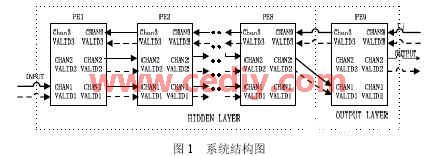

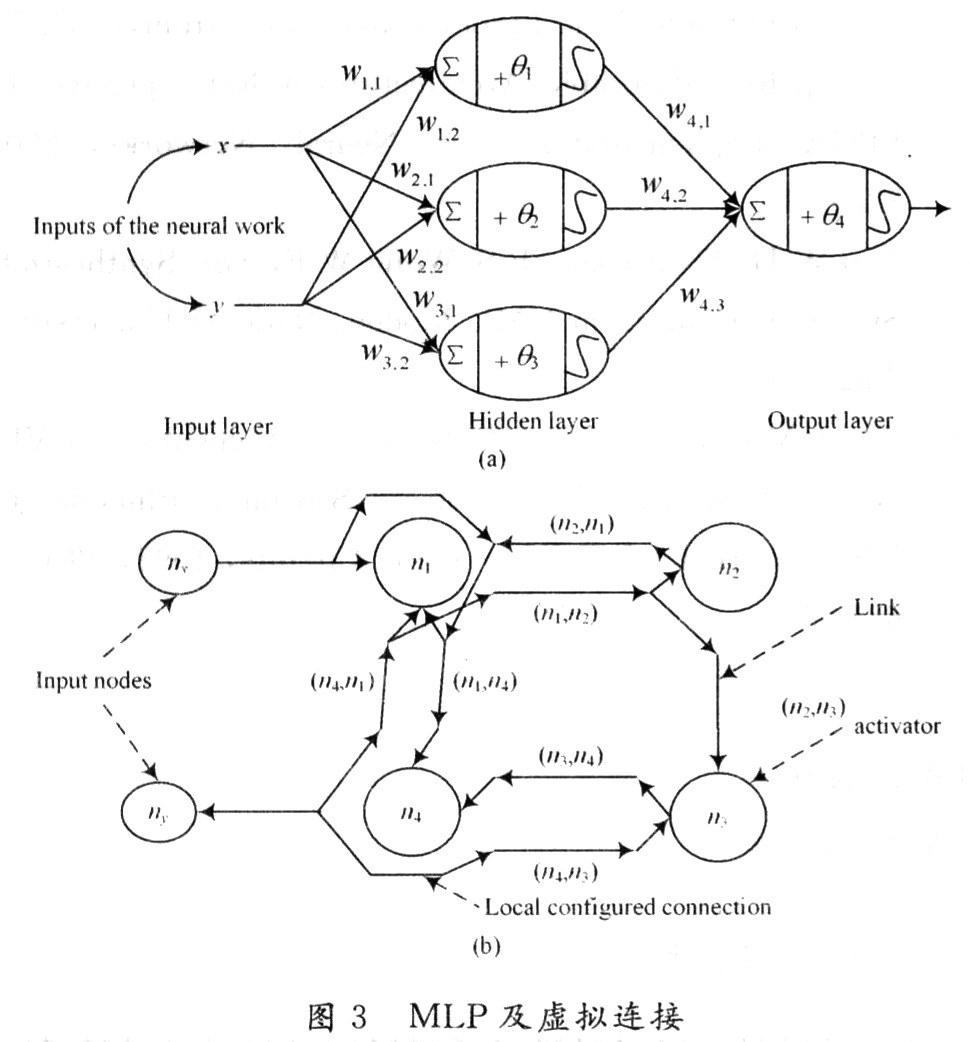

78 基于FPGA的人工神經網絡實現方法的研究

引 言 人工神經網絡(Artificial Neural Network,ANN)是一種類似生物神經網絡的信息處理結構,它的提出是為了

2009-11-17 17:17:20 1428

1428

基于FPGA的人工神經網絡實現方法的研究

引言

人工神經網絡(ArtificialNeuralNetwork,ANN)是一種類似生物神經網絡的信息處理結構,它的提出是為了解決一些非線

2009-11-21 16:25:24 5007

5007

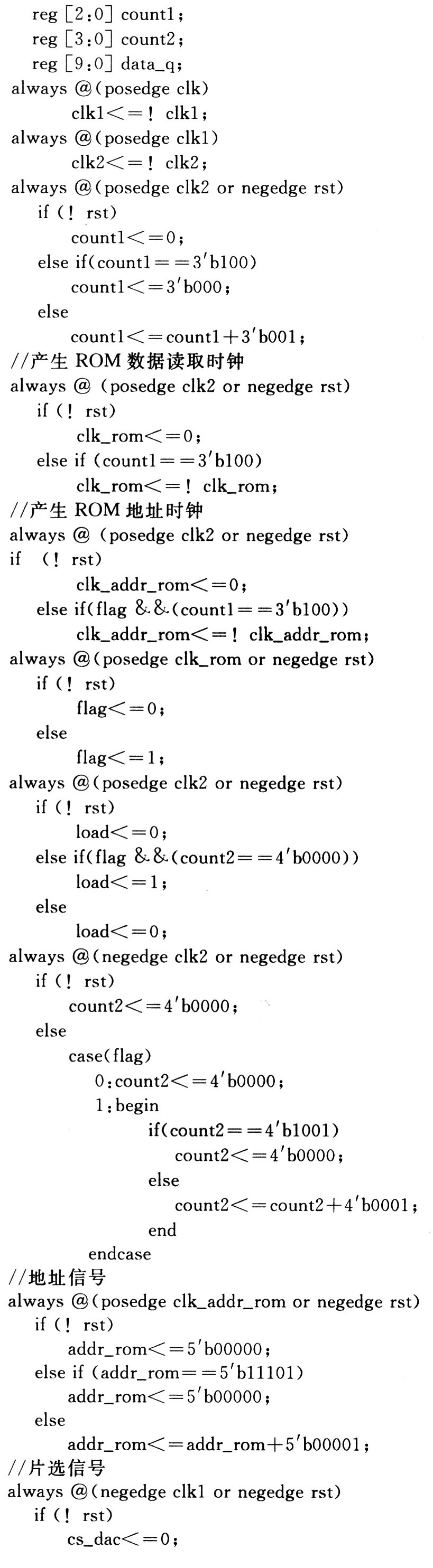

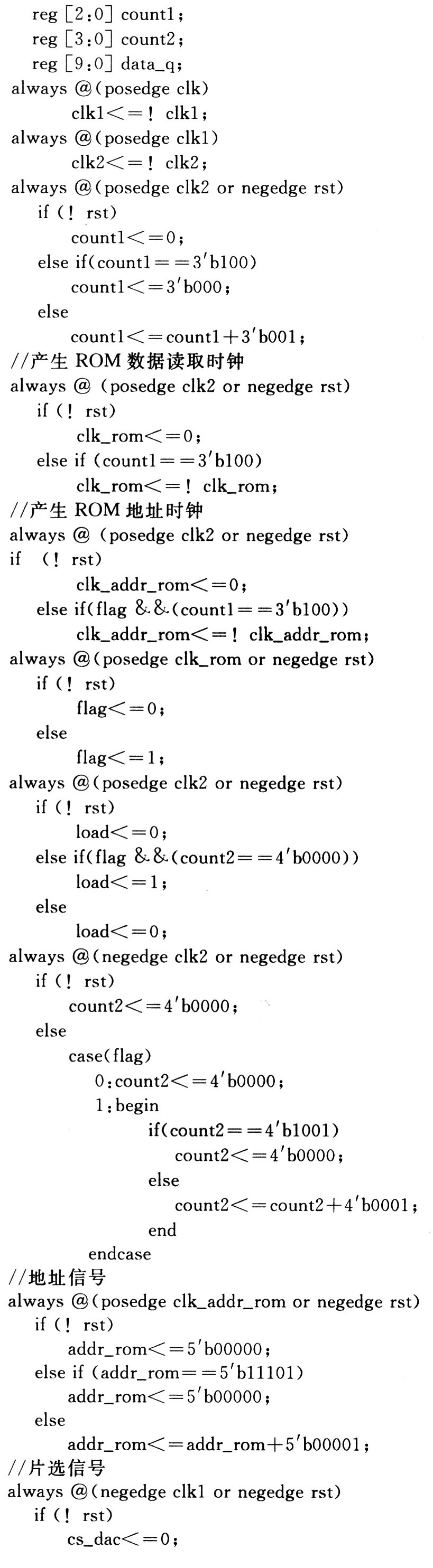

1 系統設計

采用Altera公司Cyclone系列EP1C6Q240C8為控制芯片。通過Altera的IP工具MegaWizard管理器定制LPM_ROM宏功能模塊,用.mif格式文件存放產生電壓的數據;利用硬件描述

2010-08-20 11:14:55 1502

1502

本內容展示了EP1C6Q240C6開發板的原理圖,詳細列出了開發板的原理圖

2011-02-23 15:43:10 156

156 列舉了EP2C8開發板原理圖,詳細說明了各版塊的原理圖

2011-02-23 15:45:23 279

279 設計和實現了一個以Altera FPGA的Cyclone器件EP1C6Q240C8為核心的多功能實驗板.它分為核心板和擴展板, 用戶可以結合QuartusII集成開發環境, 使用VHDL語言、Verilog HDL語言或原理圖, 進行編輯、綜

2011-06-27 15:58:37 95

95 介紹一種基于SOPC的基本信號產生器的設計技術,以Altera公司EP1C6Q240C8為硬件核心,把軟核CPU嵌入到FPGA之中構成片上系統,以此實現基本信號產生器

2011-07-23 11:07:21 1292

1292

EP2C5T144C8-FPGA開發板采用Altera公司推出的CYCLONEⅡ系列芯片EP2C5T144C8芯片作為核心處理器進行設計,CYCLONEⅡ系列芯片可以說是目前市場上性價比較高的芯片,比第一代的EP1C6或者EP1C12等芯片

2011-12-06 10:24:54 671

671 本開發板采用 Altera 公司CycloneII 系列EP2C8Q208 芯片而設計的。幫助用戶降低學習成本和加快用戶快速進入可編程邏輯器件的設計開發領域。提供一個幫助用戶快速學習可編程邏輯器件的硬

2011-12-06 10:29:14 799

799 文章以T6963C控制的240×128LCD液晶顯示屏模塊闡述了一種基于EP1C6Q240C8處理器的液晶顯示屏的滾屏顯示的軟硬件控制方法。

2012-02-28 10:33:51 2570

2570 介紹一種基于SOPC的基本信號產生器的設計技術,以Altera公司EP1C6Q240C8為硬件核心,把軟核CPU嵌入到FPGA之中構成片上系統(SOPC),并結合存儲電路、高速DAC電路、LCD電路、鍵盤電路、JTAG配置電路

2012-03-09 14:55:15 14

14 開發板EP1C6Q240C6開發板原理圖

2017-03-20 08:00:00 26

26 開發板EP1C3T144_FPGA_develop_board_manual

2017-03-20 11:38:00 32

32 EP4CE6E22C8N開發板原理圖

2017-04-22 09:11:44 890

890 本文檔的主要內容詳細介紹的是FPGA EP1C3開發板原理圖的詳細資料免費下載。

2018-09-26 16:35:00 63

63 設計和實現了一個以Altera FPGA的Cyclone器件EP1C6Q240C8為核心的多功能實驗板。它分為核心板和擴展板, 用戶可以結合QuartusII集成開發環境, 使用VHDL語言

2018-11-16 16:48:05 8

8 3T144 FPGA開發板手冊,EP1C6Q240C6開發板原理圖,EP2C5原理圖,EP2C8開發板原理圖,EPM1270F256C5 MAX II板示意圖,EPM7128最小系統,MAX7000等等。

2019-03-04 08:00:00 91

91 本文檔的主要內容詳細介紹的是FPGA視頻教程之使用SF-EP1C開發板實現DIY數碼相框的實驗資料說明。

2019-03-06 14:02:07 4

4 本視頻的主要內容詳細介紹的是FPGA視頻教程之SF-EP1C開發板256色VGA顯示實驗的詳細資料說明。

2019-03-07 14:53:55 3658

3658 SF-EP1C開發板有著比較豐富的外設,也給用戶預留了一些可擴展的接口。FPGA使用EP1C3T144C8,硬件電路充分考慮了可升級性,該板子同樣適用于EP1C6T144。

2019-12-16 07:04:00 2662

2662

1、FPGA使用EP1C3T144C8,硬件電路充分考慮了可升級性,該板子同樣適用于EP1C6T144

2019-12-12 07:10:00 3502

3502

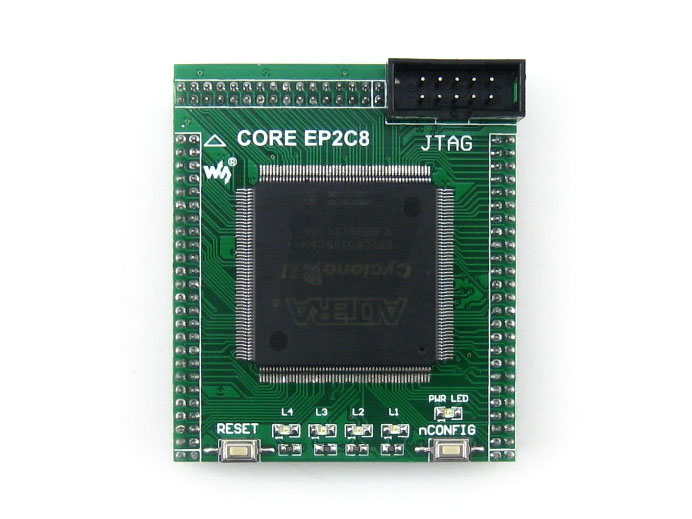

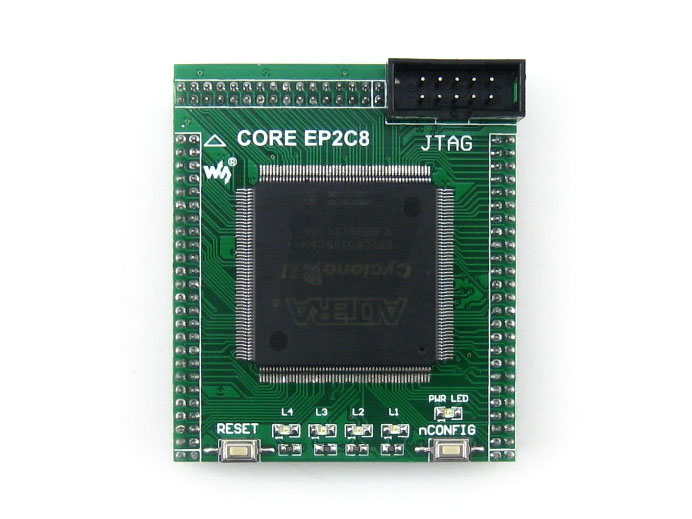

CoreEP2C8是一款基于EP2C8Q208C8N為主控芯片的核心板

2019-12-19 14:26:33 3126

3126

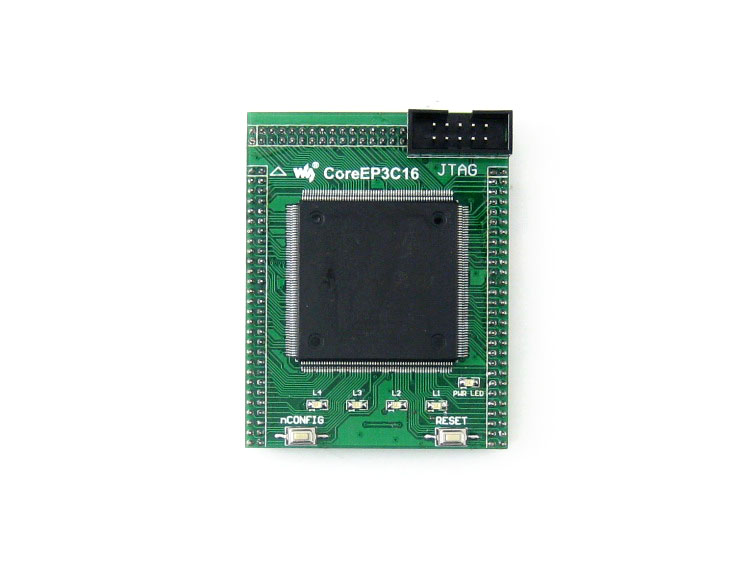

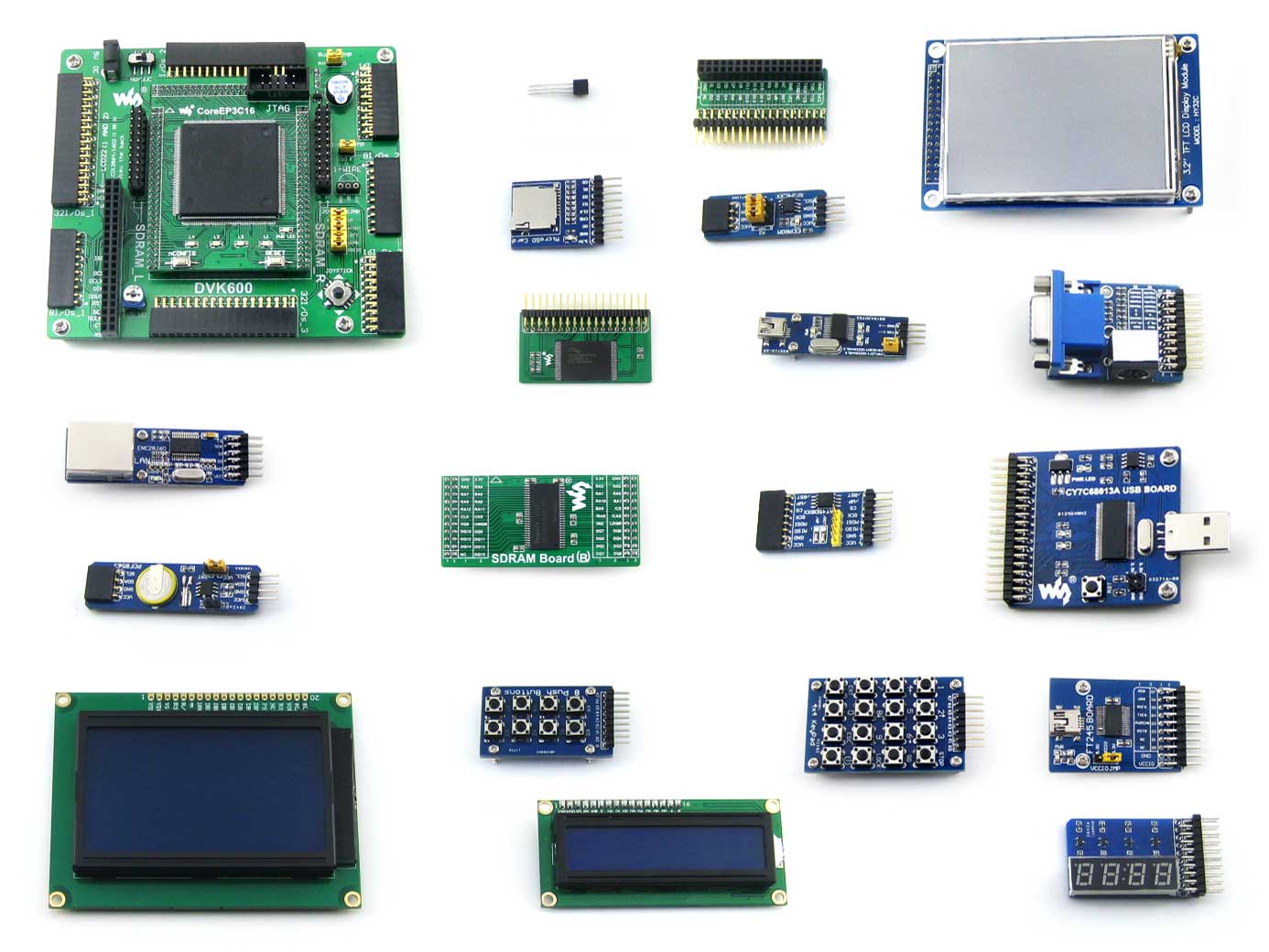

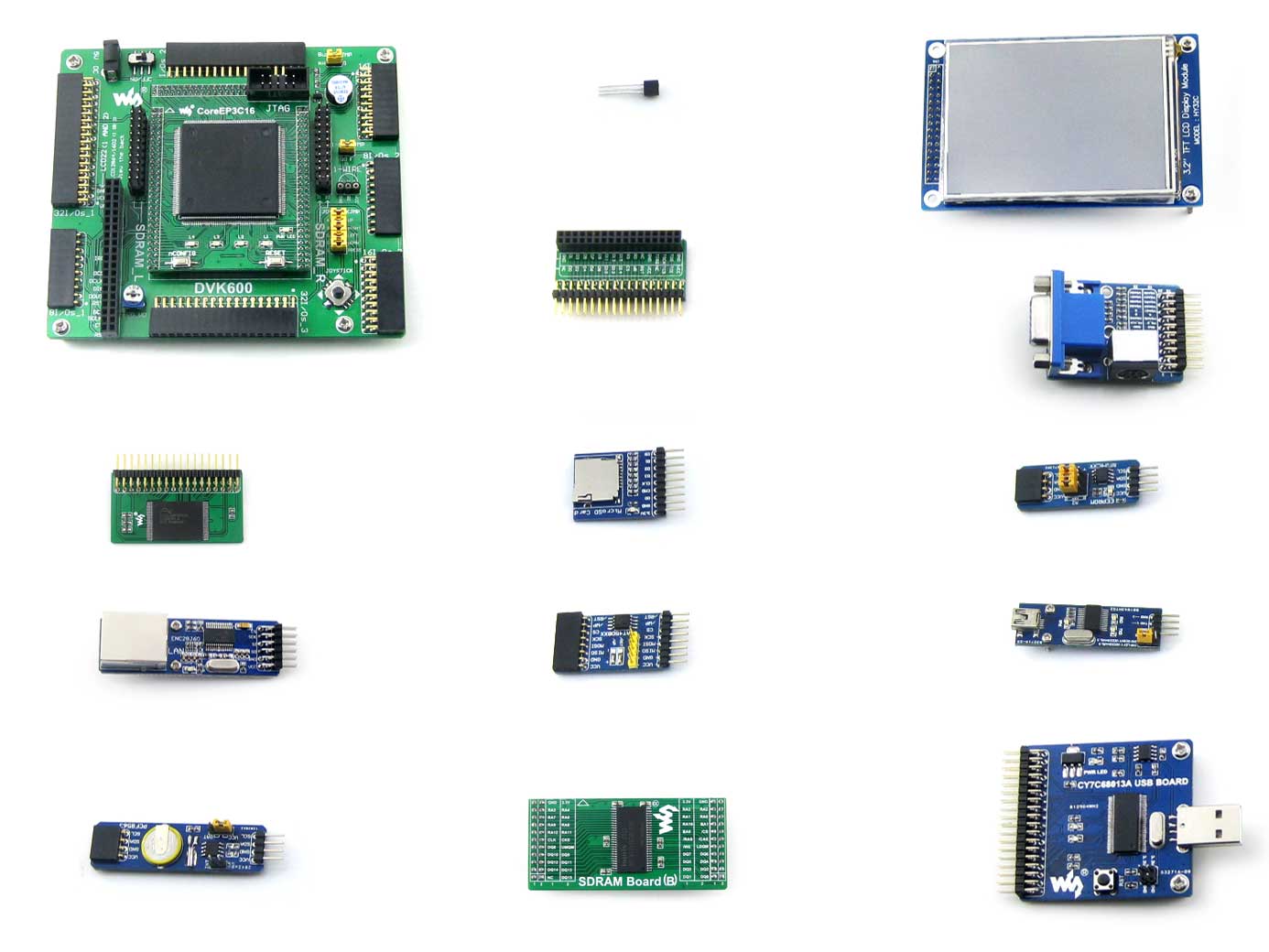

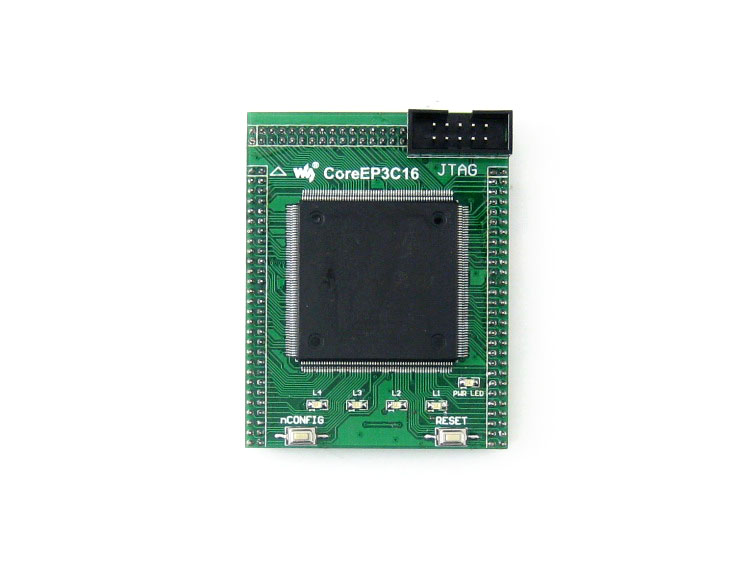

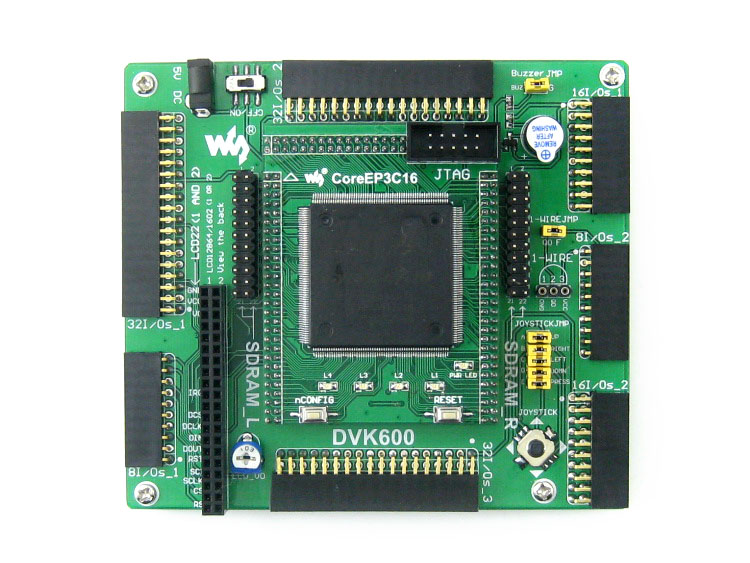

EP3C16Q240C8N 核心板 最小系統板

引出了所有I/O資源 帶JTAG調試下載接口

型號 CoreEP3C16

2019-12-19 14:29:36 2496

2496

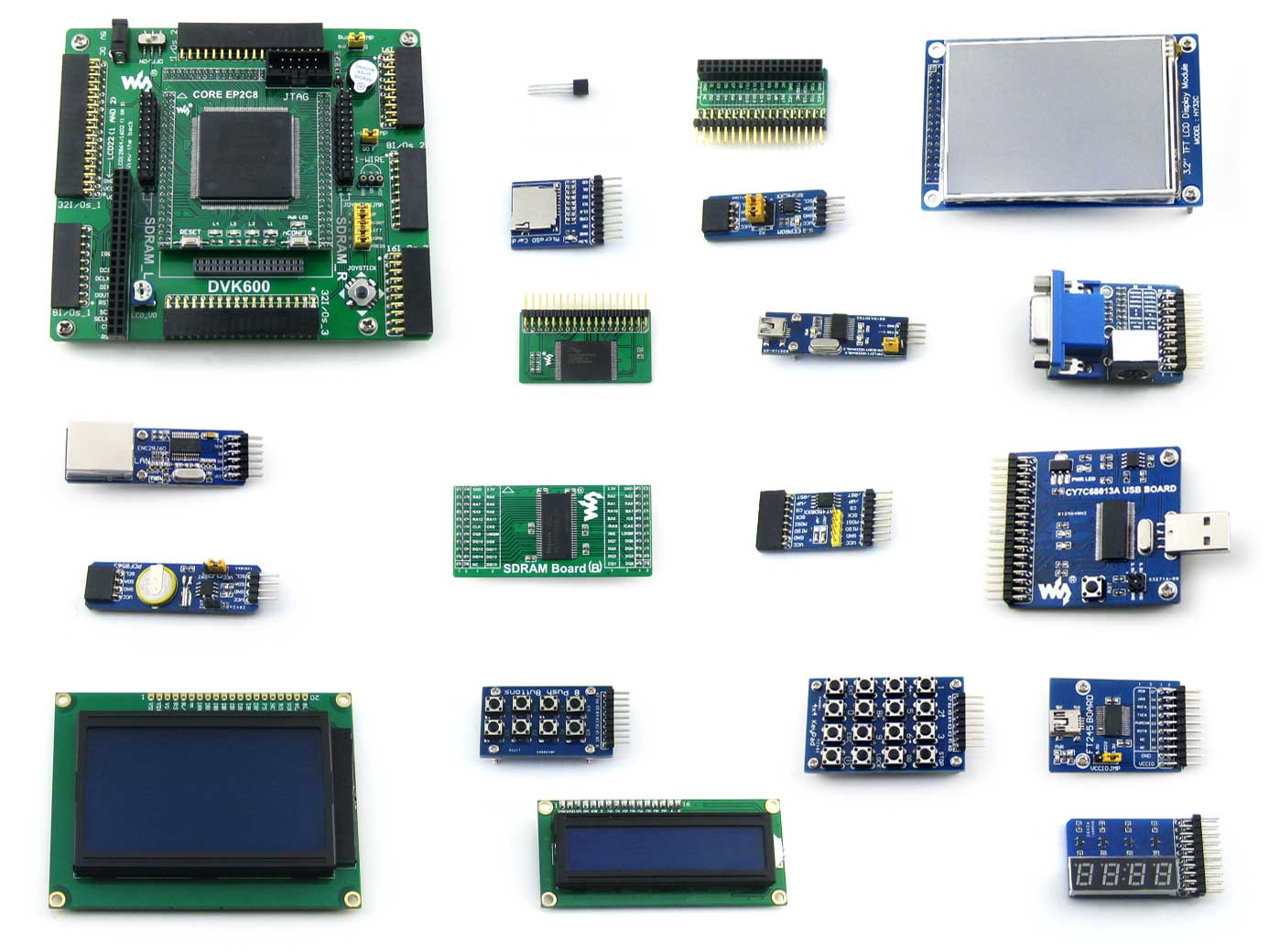

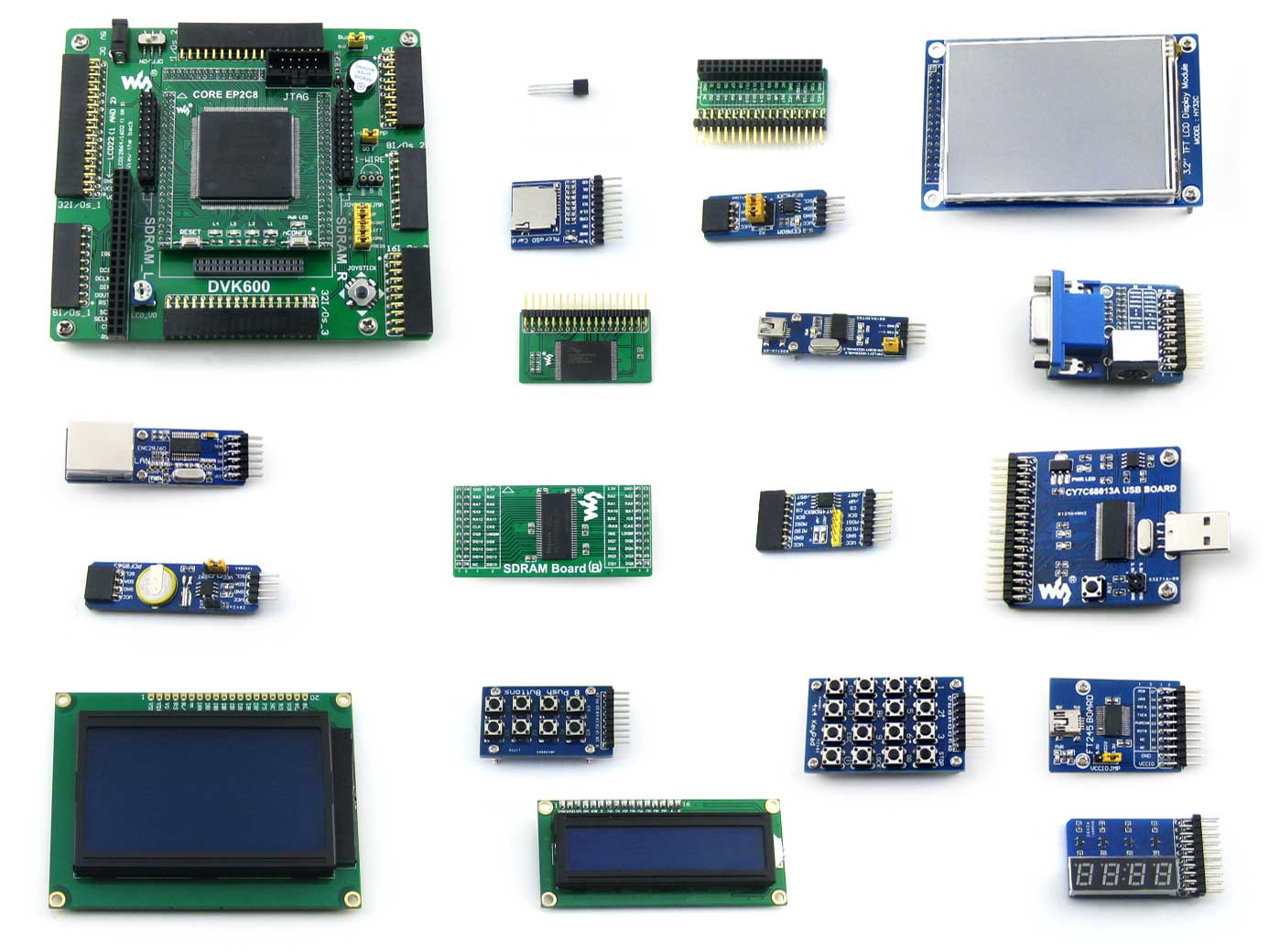

EP2C8Q208C8N開發板 學習板 套餐B 含18款模塊

引出常用接口,含LCD、串口、按鍵、USB通信等模塊

型號 OpenEP2C8-C (套餐B)

2019-12-20 15:04:27 2564

2564

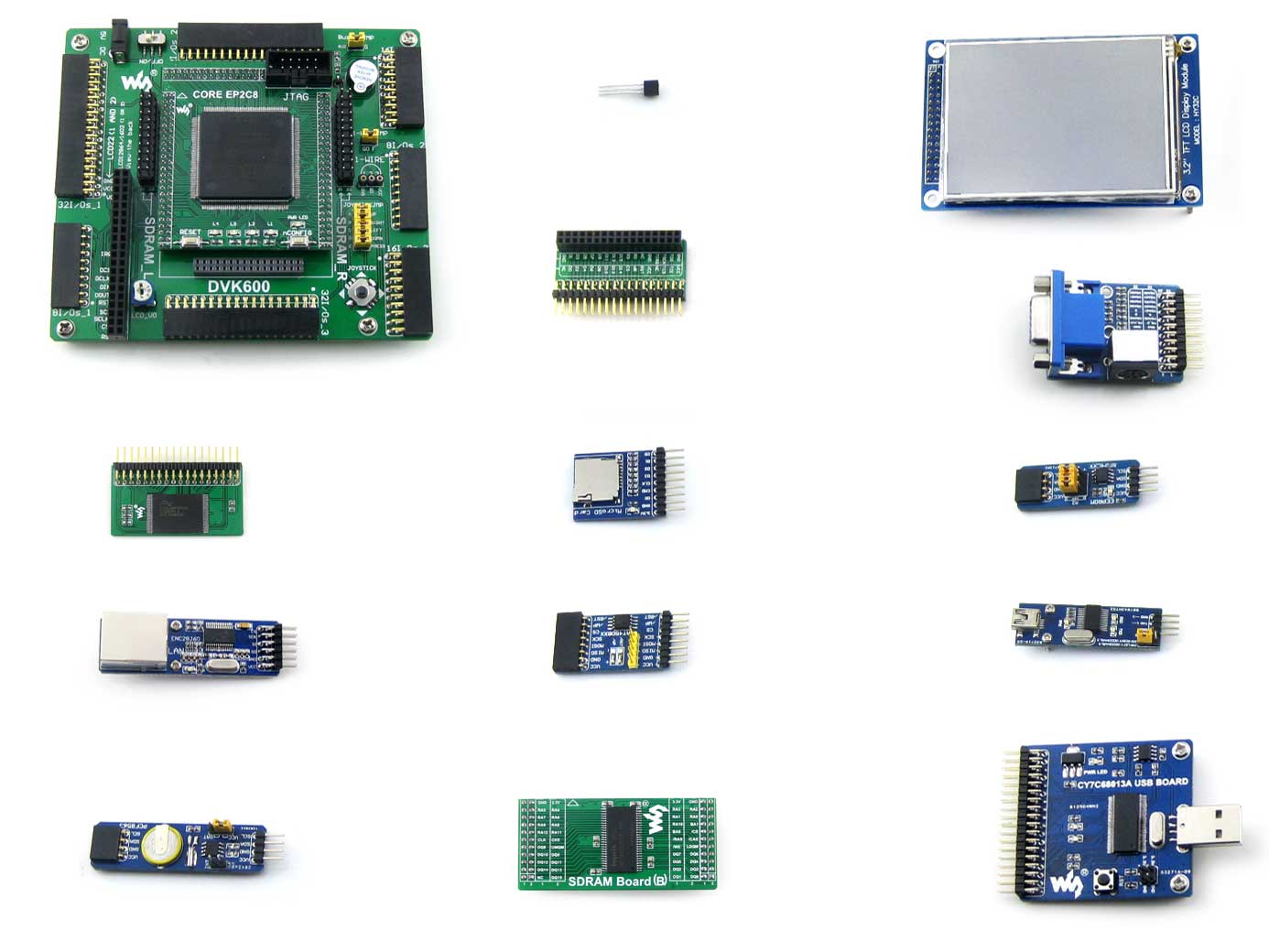

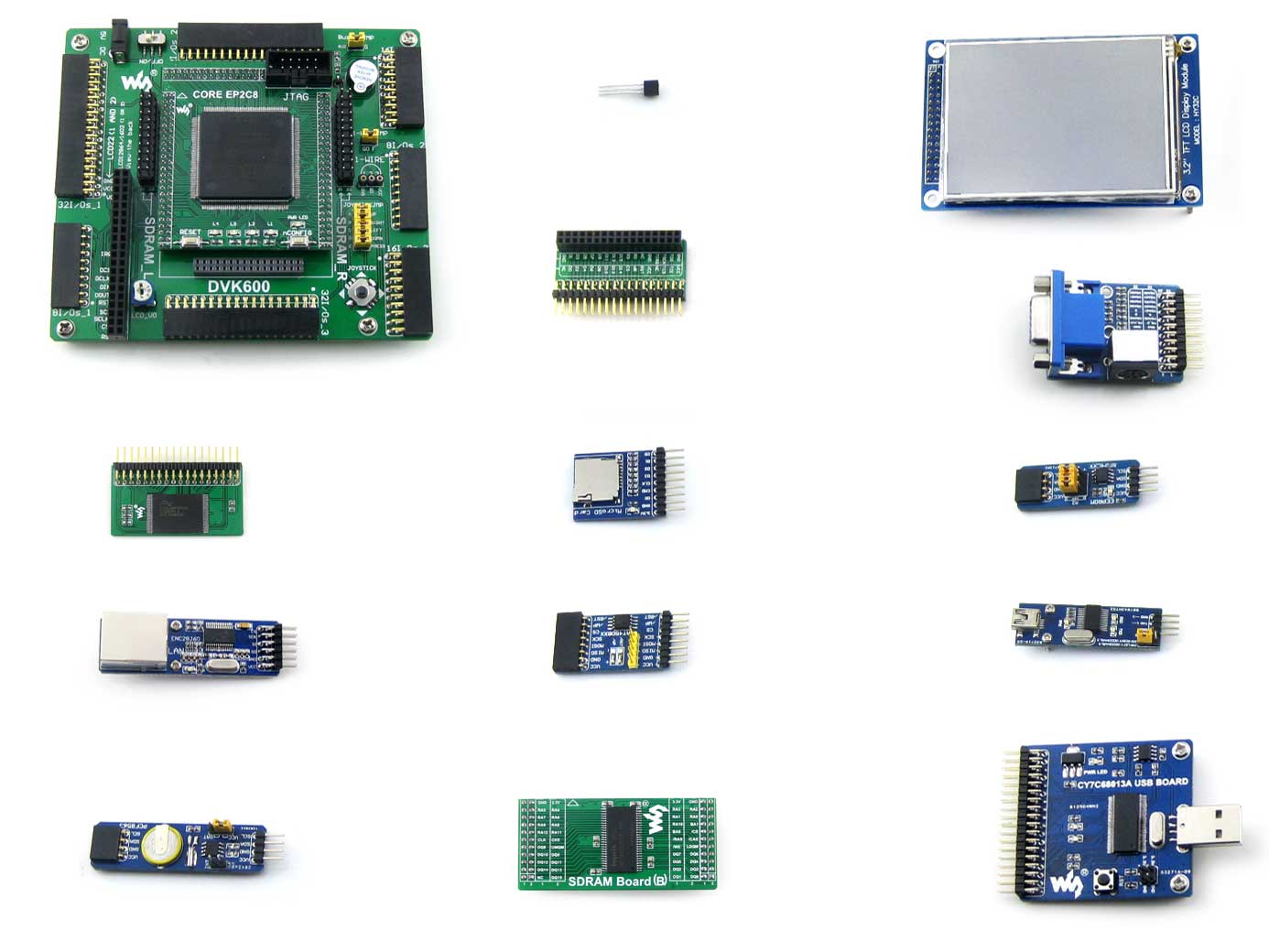

EP2C8Q208C8N開發板 學習板 套餐A 含12款模塊

引出常用接口,含LCD、串口、按鍵、USB通信等模塊

型號 OpenEP2C8-C (套餐A)

2019-12-20 15:14:19 2342

2342

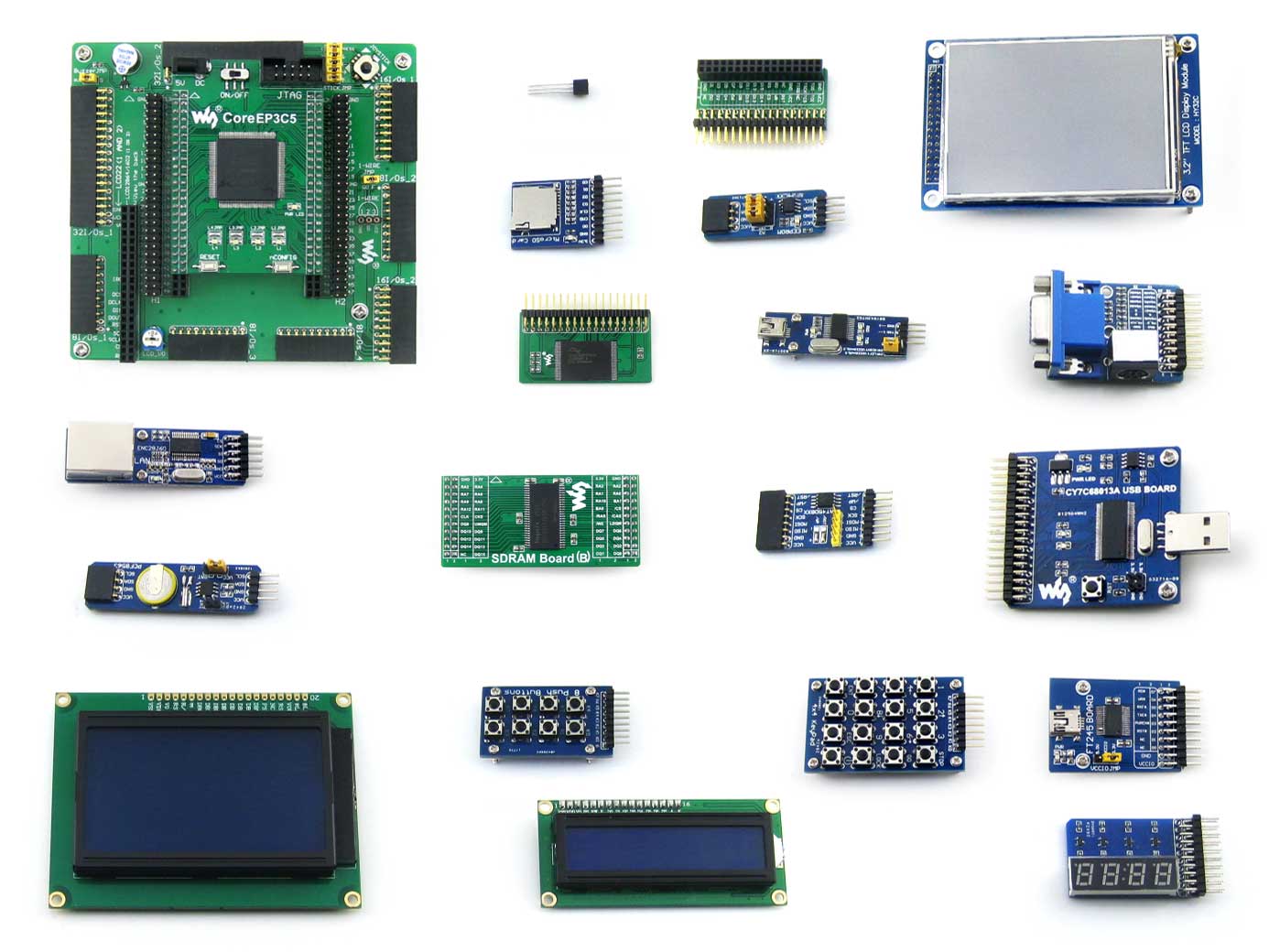

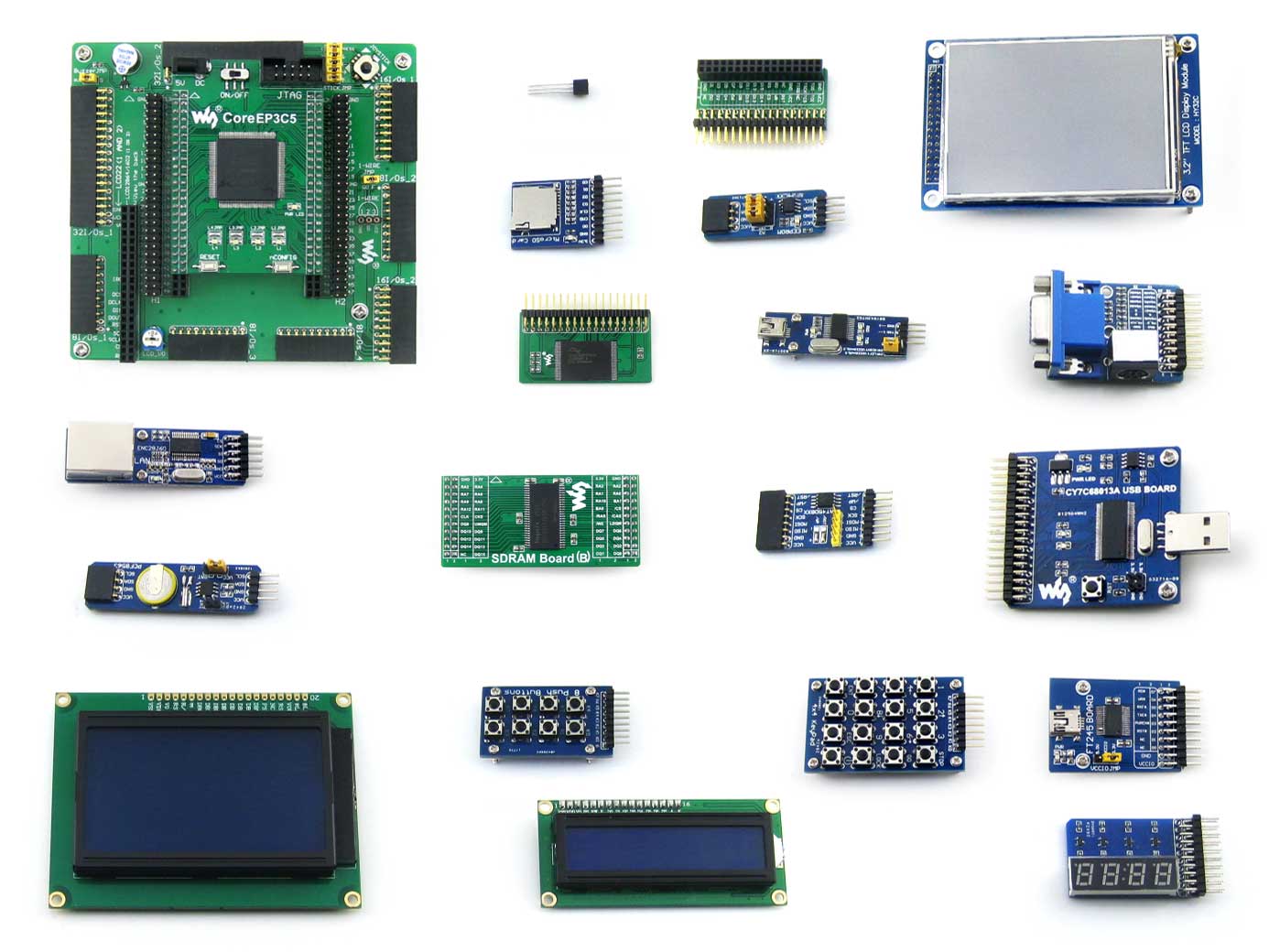

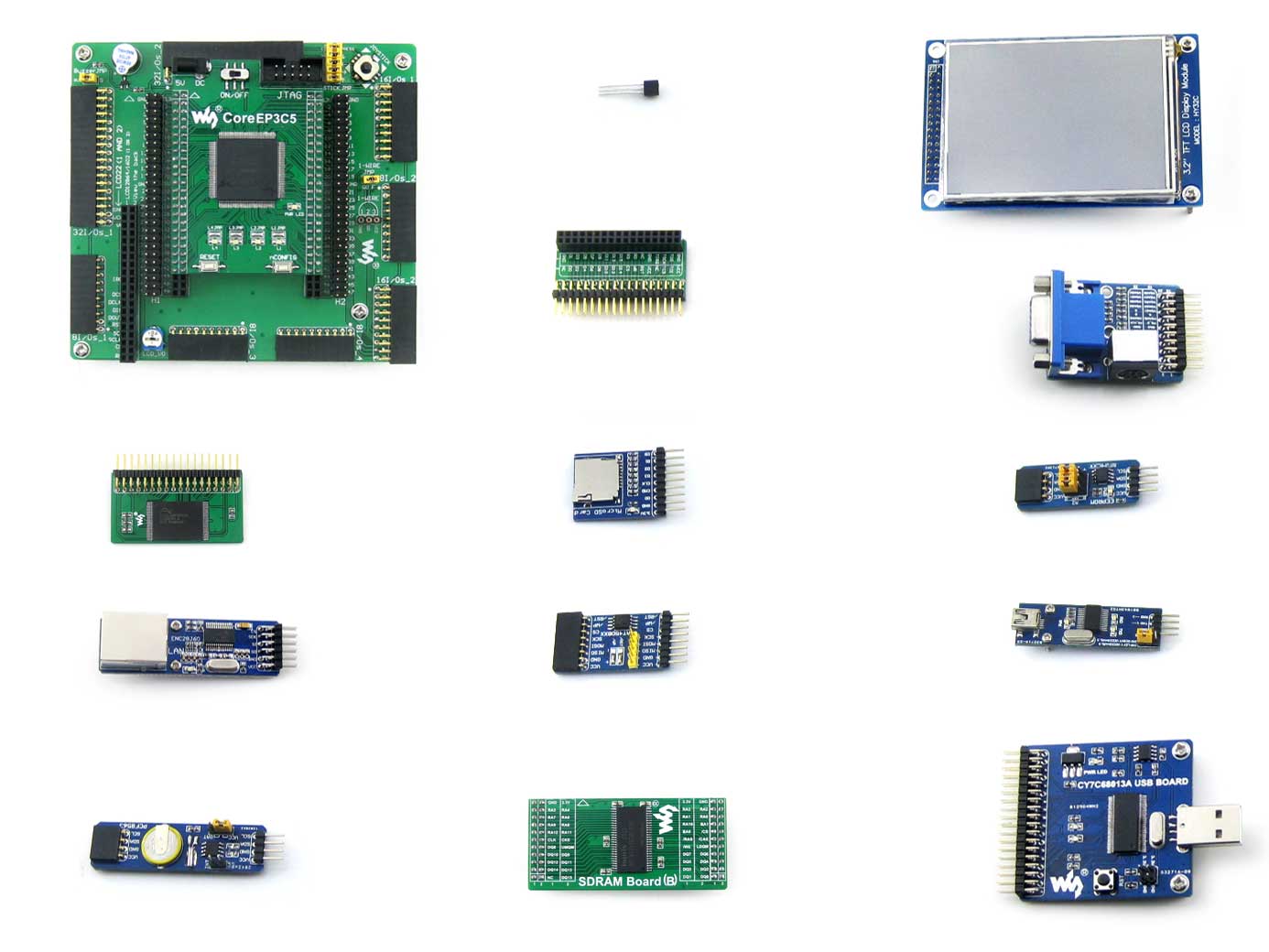

,包括實用新型專利及外觀專利,仿造必追究其法律責任! FPGA開發板OpenEP3C5-C是一塊以Cyclone III EP3C5為主控芯片的開發板,它帶有豐富的擴展接口,支持各類外圍模塊的接入

2019-12-23 11:23:08 2483

2483

FPGA開發板OpenEP3C5-C是一塊以Cyclone III EP3C5為主控芯片的開發板,它帶有豐富的擴展接口,支持各類外圍模塊的接入。

2019-12-23 11:30:13 1776

1776

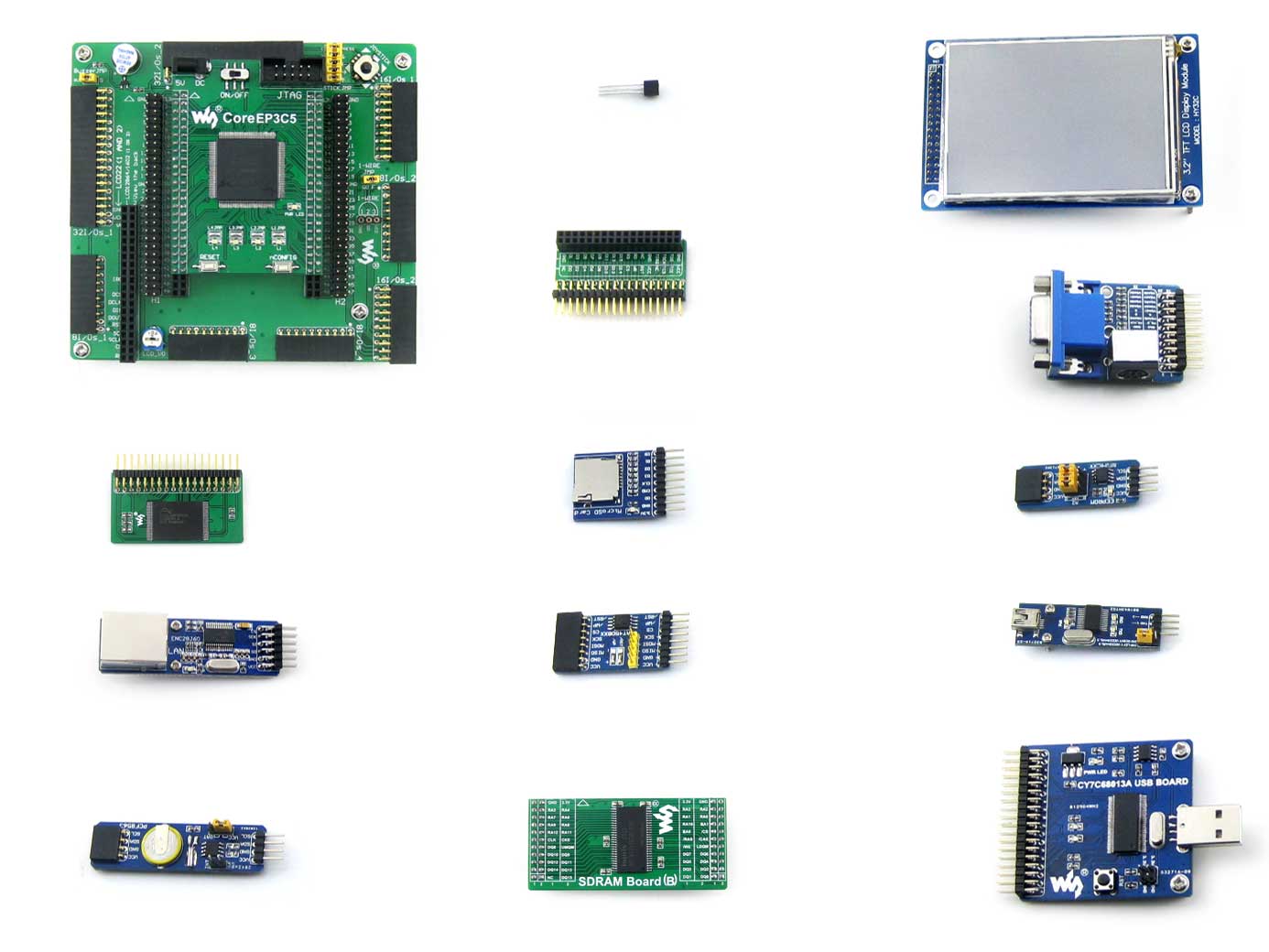

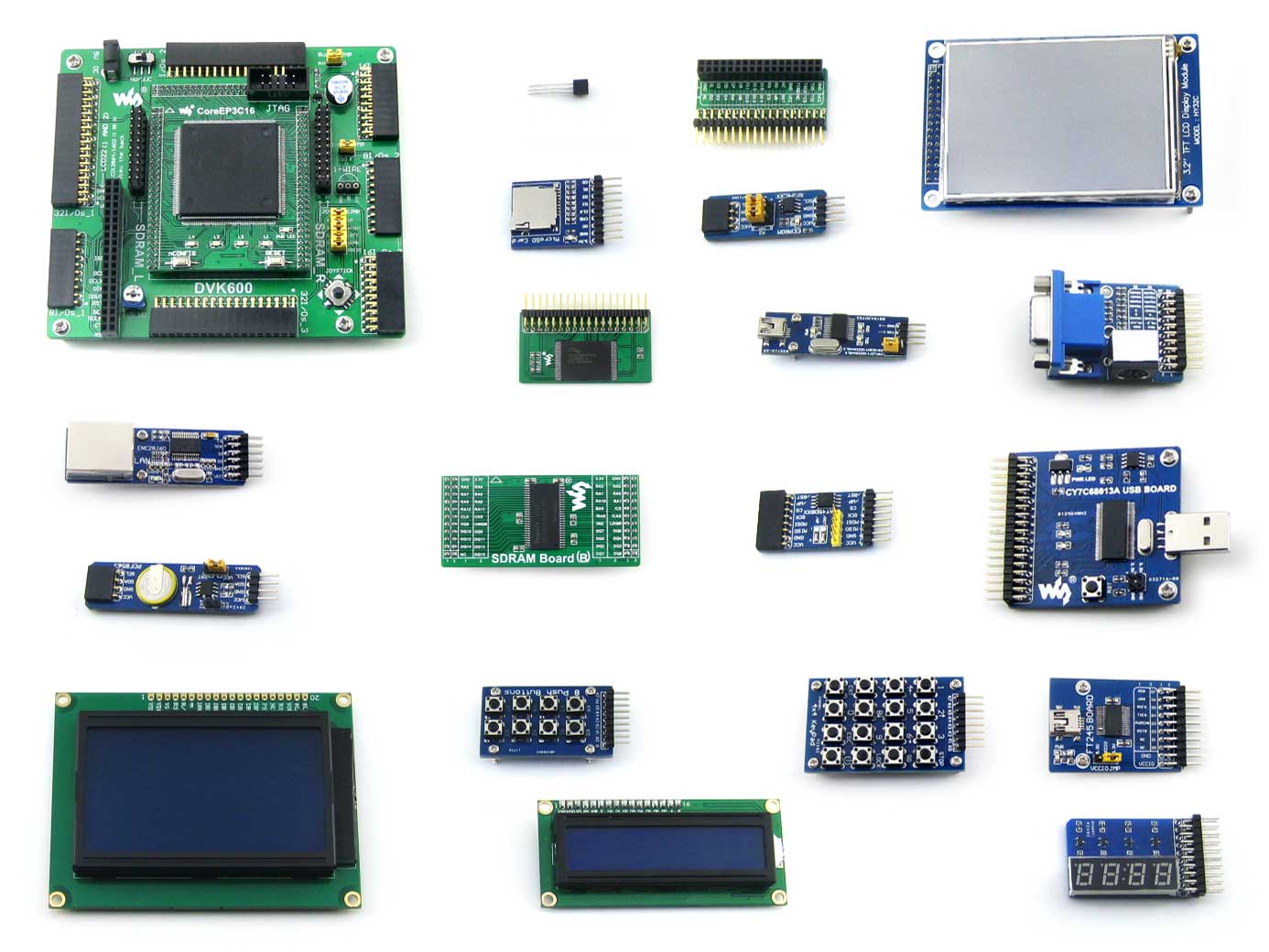

EP3C16Q240C8N開發板 學習板 套餐B 含18款模塊

引出常用接口,含LCD、串口、按鍵、USB通信等模塊

型號 OpenEP3C16-C (套餐B)

2019-12-23 11:32:24 1908

1908

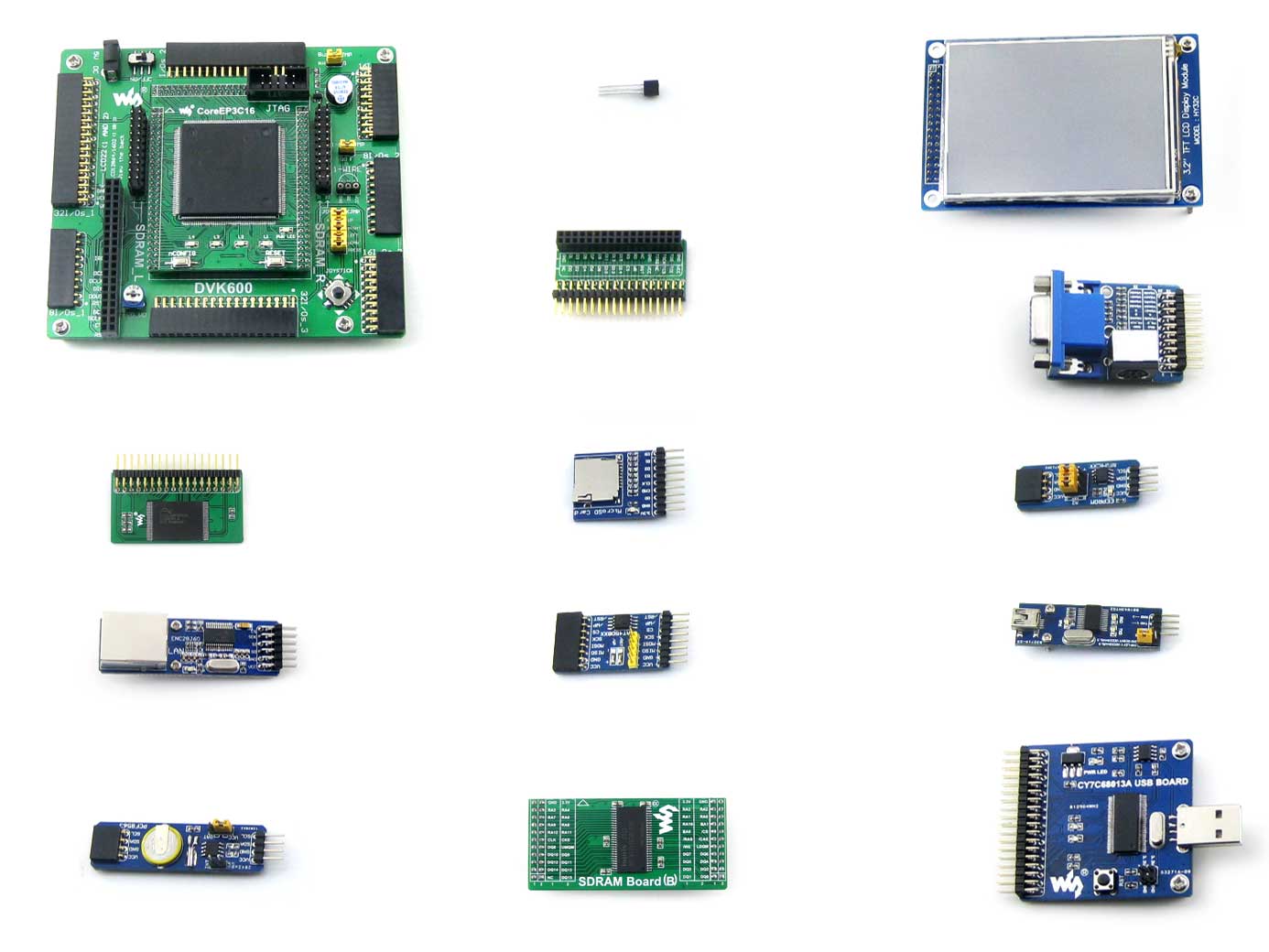

EP3C16Q240C8N開發板 學習板 套餐A 含12款模塊

引出常用接口,含LCD、串口、按鍵、USB通信等模塊

型號 OpenEP3C16-C (套餐A)

2019-12-23 11:28:08 2065

2065

EP2C8Q208C8N開發板 學習板 核心板 標準版本 引出常用接口,可接微雪外圍模塊 型號 OpenEP2C8-C (標準版) FPGA開發板OpenEP2C8-C是一塊以Cyclone II

2019-12-23 14:17:24 2878

2878

FPGA開發板OpenEP3C16-C是一塊以Cyclone III EP3C16Q240C8N為主控芯片的開發板,它帶有豐富的擴展接口,支持各類外圍模塊的接入。

2019-12-23 14:26:41 2004

2004

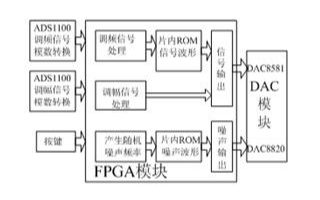

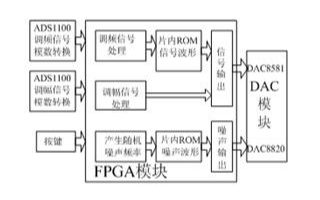

利用FPGA開發振動模擬器研制開發費用低,不承擔投片風險,通過開發工具在計算機上完成設計,電路設計周期短。所以本文采用FPGA實現振動模擬器設計,由ADC模塊接收調頻和調幅信號,傳給FPGA模塊

2020-08-05 14:29:16 1694

1694

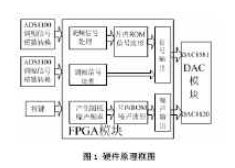

振動模擬器的原理框圖如圖1所示,圖中由ADC模塊分別接收調頻和調幅信號給FPGA模塊,FPGA模塊將串行的調頻和調幅信號,經串并轉換,分別變成一個16位的并行調頻信號和一個16位的并行調幅信號

2020-08-06 17:42:11 2724

2724

傳統的運動控制卡多采用單片機作為微處理器, 通過一些大規模集成電路實現對伺服電機的控制。由于其結構較為復雜,因此在工作時,存在高頻響應慢、控制精度低等缺點。本文提出一種以FPGA

2020-08-12 17:02:03 2814

2814

,進而用FPGA和D/A轉換器進行硬件實現。文中基于FPGA對長度為10000m,特性阻抗為55Q的同軸電纜進行了仿真線的硬件實現,實驗結果驗證了該方法的有效性。該方法可以推廣到傳遞函數未知的傳輸網絡的仿真應用中。

2021-02-03 16:26:00 14

14 基于FPGA的RBF神經網絡硬件實現說明。

2021-04-28 11:24:23 27

27 基于FPGA的神經網絡硬件實現方法說明。

2021-06-01 09:35:16 51

51 FPGA開發板EP4CE22F17C8原理圖及封裝

2021-08-10 09:31:21 183

183 電子發燒友網站提供《基于FPGA的RBF神經網絡的硬件實現.pdf》資料免費下載

2023-10-23 10:21:25 0

0 可編程門陣列(FPGA)作為一種靈活、高效的硬件實現方式,為神經網絡的加速提供了新的思路。本文將從FPGA實現神經網絡的基本原理、關鍵技術、實現流程以及應用前景等方面進行詳細闡述。

2024-07-10 17:01:42 4397

4397 今天我們分享幾個用FPGA實現的小型神經網絡,側重應用。

2024-07-24 09:30:16 2389

2389

電子發燒友App

電子發燒友App

評論