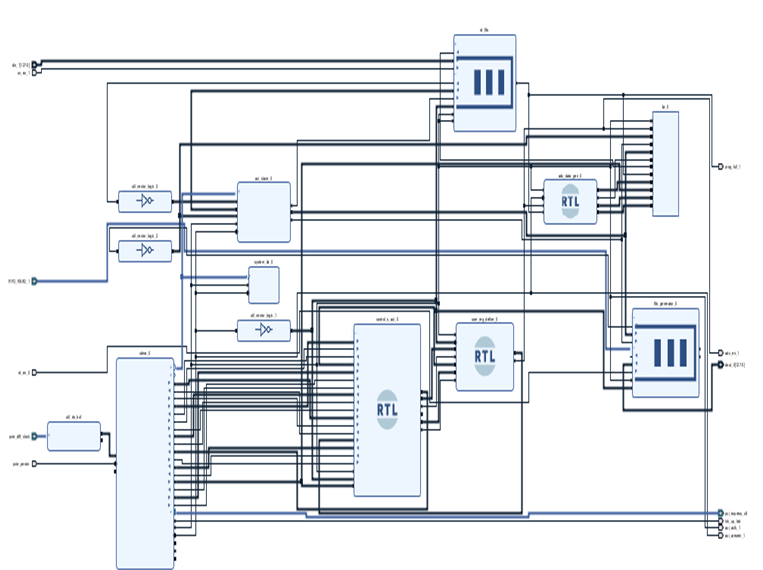

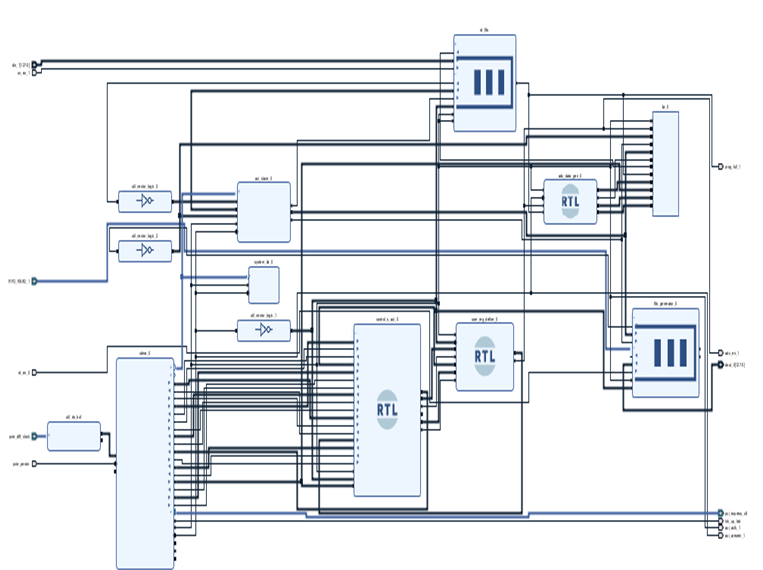

本工程的目的是在XC7K325tffg的平臺上實現pcie的數據發送和接收,速率8通道2.5GB/s,首先看下本工程的PCIE部分的結構。

2022-04-21 09:36:14 4672

4672

在高速系統中FPGA時序約束不止包括內部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現PCB板級的時序收斂。因此,FPGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 2392

2392 的傳輸單元將高速數據及相關的時序信號一起發送至接收器電路。這些模塊中的接收單元擁有時序調整的功能,以便在很高的速度下能可靠地采集數據。此外,這些模塊通過增加數據的寬度來減緩數據傳輸速率,從而使FPGA

2018-11-26 11:17:24

。 FPGA與RGMII接口的PHY芯片之間的時序關系按照數據接口同步和數據采樣方式屬于源同步DDR采樣。input delay約束對應接收方向,時序關系是中心對齊。output delay約束對應發送方向

2023-06-06 15:43:13

FPGA。

實現時,需要確保FPGA能夠正確地發送命令并接收SD卡的響應,同時能夠解析響應碼以判斷操作是否成功。

讀寫操作:

在讀取數據時,FPGA需要向SD卡發送讀命令,并等待SD卡返回數據。寫入數據

2024-06-27 08:38:12

2、系統同步輸入1、所謂的源同步輸入指的是輸入的數據和其對應的同步時鐘,類似ADC和FPGA的相連接,對于這一類的約束比較典型的是DDR傳輸模式:如圖所示:我們要做的約束是對接口相關的輸入時鐘,定義

2015-09-05 21:13:07

、LxCLKIN均以FPCA的角度來敘述),該接口由接收、控制和發送三部分組成。本設計FPGA時鐘為40MHz,TS101核時鐘上作在250MHz,鏈路口時鐘設定為DSP核時鐘的8分頻,FPGA與DSP的實際

2018-12-04 10:39:29

、LxCLKIN均以FPCA的角度來敘述),該接口由接收、控制和發送三部分組成。本設計FPGA時鐘為40MHz,TS101核時鐘上作在250MHz,鏈路口時鐘設定為DSP核時鐘的8分頻,FPGA與DSP的實際

2019-06-19 05:00:08

使能這兩個配置也能在一定程度上改善時序收斂。 FPGA工程師的工作不只是將電路功能實現,由于器件和工具不是理想的,所以還需要研究器件特性和工具的局限,尤其是在如今算法結構越來越成熟的背景下,不斷被工具折磨,也許這也是FPGA工程師的悲哀吧。

2020-12-23 17:42:10

數據發送模塊,FPGA波特率發生控制模塊,FPGA總體接口模塊以及單片機數據接收模塊。本文著重對FPGA數據發送模塊實現進行說明。2FPGA數據發送模塊的設計根據RS232 異步串行通信來的幀格式,在

2018-12-10 10:16:38

FPGA1中,其中FPGA1中的配置模塊負責接收來自PC方軟件發送的配置數據,并產生對被測FPGA的配置時序,完成配置步驟,測試模塊負責發送測試激勵和回收被測FPGA的響應數據,等待PC方軟件的回收。系統

2020-05-14 07:00:00

,發送端是FPGA,而接收端是ADV7123芯片。如果傳輸的速率比較高,那么數據和時鐘上升沿的嚴格對齊則要依靠PLL產生可調相位的時鐘信號來保證。不過,我們這個25MHz或者50MHz的時鐘通過較好的時序分析和約束后,則不必動用PLL。(特權同學,版權所有)圖8.25 源同步接口寄存器模型

2015-07-29 11:19:04

adapt layer,信令ATM適配層)的CP(公共部分),即對高層產生的信令信息進行AAL5適配,經UTOPIA接口將ATM信元發送到路由及業務管理模塊,然后再送至交換單元。3 中心控制單元的設計與實現

2009-05-25 16:38:13

5個連“1”則在其后插入1個“0”,數據發送結束后發送幀尾“7E”。FPGA設計FPGA中實現的主要是鏈路層協議完成HDLC數據接口的收發,并完成與DSP的數據交互,該電路由接口模塊interface

2011-03-17 10:23:56

FPGA處理數據的時間,所以整個系統實現了流水線操作。1 系統的總體設計系統硬件主要由信號采集模塊、FIFO、FPGA和SEP3203處理器組成。信號采集模塊主要包括信號接收器和A/D轉換模塊。接收

2019-04-26 07:00:06

STM32F7開啟讀保護Level2之后,還能擦除重新燒錄程序嗎?

2024-04-01 07:38:01

低電平)、8 位數據位、偶校驗、停止位(1 b 高電平) , 波特率可調。 2 波特率發生模塊 設計的UART 的接收和發送按照相同的波特率進行,波特率可以通過接口模塊的總線接口進行設置

2015-02-05 15:33:30

This is a Product Note on how to use the HP E4829B custom / UTOPIA Level 1 implementation for real-time bit error rate (BER) measurements.

2019-02-18 17:09:23

Implementation of UTOPIA level 2 with Keysight E4829B

2019-02-22 13:36:05

?以保證FPGA發送過去的數據能被外部芯片正確接收的。

FPGA通過某種通用接口(如SPI)和外部芯片通信時,FPGA如何實現才能滿足芯片手冊給出的時序要求呢?

2023-04-23 11:35:02

的接口,有固定的引腳和通信協議。使用FPGA實現串口通信,可分為“計算機發送數據給FPGA”和“FPGA發送數據給計算機”兩部分。本節為串口接收實驗,使用FPGA接收從計算機發來的數據。進行串口接收實驗

2022-07-19 11:09:48

模塊

字節傳輸控制模塊以字節為單位控制 I2C 總線的數據傳輸。這個模塊按照命令寄存器設置的內容將數據傳輸寄存器內容傳遞到 I2C 總線的接收端,或者從 I2C 總線發送端接收數據并保存到數據接收寄存器

2023-08-14 18:21:26

摘要:RS 232接口是現在最常用的一種通信接口。隨著FPGA技術的高速發展,一些常見的接口電路的時序電路可以通過FPGA實現,通過這種設計可減少電路系統元件的數量,提高系統集成度和可靠性。詳細闡述

2019-06-19 07:42:37

適用于該背景的控制狀態機,并對控制時序作了詳盡的分析。系統測試結果表明,該設計滿足大容量數據的高速率存儲和讀取要求。一、引言隨著軟件無線電[1]思想的提出和FPGA技術[2]的不斷發展,高速實時

2018-08-30 09:59:01

語言,他可以用來進行各種級別的邏輯設計,可以用來進行數字邏輯系統的仿真驗證、時序分析和邏輯綜合等,應用十分廣泛。本文使用Verilog設計 SPI接口模塊,實現可IP復用的通用結構。根據SPI總線

2019-05-28 05:00:05

發送到MISO 上。當CPHA=1 時,MOSI 和MISO 的時序完全相同。2 SPI 主機模塊的設計本文設計的SPI 主機模塊主要完成以下工作:(1) 將主機收到的8 位并行數據轉換為串行

2015-01-28 14:09:51

數據流發送,通過DVI-I端口發送給顯示終端顯示。本設計方案中,MT9M111輸出圖像的分辨率為1280×960。 圖1 系統采集與顯示過程 在現實景物的采集與顯示過程中,視頻轉換接口功能的實現通過以下

2018-12-11 10:59:36

。2 緩沖區接口軟件設計 為了設計ARM和FPGA的緩沖區接口,首先要利用圖1中的信號線實現ARM對FPGA的基本讀寫操作,這需要雙方遵循擬定的接口時序相互配合進行,這可以通過參考相應的ARM內核

2019-05-30 05:00:03

寄存器(IR-InstruetionRegister)和數據寄存器(DR-DataRegister)中。JTAG接口模塊在接收到上位機軟件發送的指令后,相應的解釋如表1所列。2FIash控制器和FPGA

2019-06-06 05:00:38

FPGA中實現。具體實現(1)PC/104接口邏輯:負責對PC/104的地址總線和控制總線進行譯碼以產生相應的命令。由于設備地址可能產生沖突,故需在接口模塊中設定跳線以便靈活地改變地址空間。(2)接收

2019-04-16 07:00:04

其它設備,又可將計算機或其它設備發出的數字信號轉換為429信號輸出。本文介紹的總線接口板采用FPGA和DSP實現四路429信號接收通道和四路429信號發送通道,且每路通道之間相互獨立。在這個接口板中

2019-06-13 05:00:06

HSDI接口的硬件結構以及接口信號的時序和功能操作基于FPGA實現HSDI接口的設計

2021-04-09 06:40:16

大家好,我想知道如何實現硬件(FPGA)中的時序報告給出的時序。我的意思是,如何測量FPGA和FPGA中輸入信號的建立或保持時間與靜態時間報告給出的值進行比較。FPGA怪胎以上來自于谷歌翻譯以下

2019-01-15 11:07:15

)發送沿(Launch Edge):前級寄存器發送數據對應的時鐘沿,是時序分析的起點;(2)捕獲沿(Latch Edge):后記寄存器捕獲數據對應的時鐘沿,是時序分析的終點。相對于launch

2018-04-03 11:19:08

如何利用STM32接口接收和探測去實現數據的接收和發送呢?其代碼是如何去實現的?

2021-11-17 07:12:00

設計方案。EMA的設計自動化工具--TimingDesigner,允許創建交互式時序圖來獲取接口規范,分析組件接口時序的特點,在項目工程師團隊中溝通設計要求3002 2. 導 言FPGA的設計與高速

2009-04-14 17:03:52

請問如何采用Altera公司Cyclom系列FPGA來實現ATM層UTOPIA LEVEL2主接口,與物理層UTOPIA從接口連接?

2021-04-08 06:32:34

之后需要進行寫數據操作,如下圖所示是背靠背模式下的寫時序示意圖,在寫數據的過程中,首先需要檢測app_wdf_rdy信號,該信號為高表明此時IP核數據接收處于準備完成狀態,可以接收用戶發送的數據,在當

2025-10-21 08:43:39

控制方案。 成幀器、網絡處理器與相關器件間通常使用的接口包括Utopia接口、POS-PHY接口、SPI接口和Flexbus接口。每個接口的后綴為 level X,其級別表明標稱數據速率。Level 2

2019-05-15 07:00:10

,使用FPGA實現SPI通信接口是切實可行的,本文作者創新點:1、將總線控制信號封裝成指令,使用者只需通過發送指令的方式操作,避免了復雜的時序邏輯設計問題。2、可以在SPI工作過程中隨時調整配置參數。3

2019-05-05 09:29:34

) 232接口模塊 該模塊用于實現串口數據輸出,它包含 2個子模塊:一、串口波特率模塊 串口通信協議要求數據收發雙方有相同的波特率。該模塊用于設定串口通信波特率。二、串口發送模塊雙口 RAM模塊將數據存儲

2020-08-19 09:29:48

DVI和HDMI標準是什么?采用FPGA實現DVI/HDMI接口具有什么優點?基于ECP2M的接收/發送功能怎么實現?

2021-05-07 07:00:06

芯片提供視頻數據的模擬通道,共同匯集到DVI-I輸出接口,傳送到數字顯示器或模擬顯示器上顯示。 圖2 硬件構架框圖 輸出圖像的分辨率要求FPGA與TMDS發送芯片之間傳送數據的帶寬在100M

2019-05-05 09:29:33

驅動模塊對WM8731寫控制字的時序仿真如圖8所示。圖中各引腳定義如表2所示。 4 結 語 利用FPGA對音頻編解碼芯片WM8731進行接口電路的設計,實現了控制接口與數字音頻接口的統一控制,簡化

2019-05-22 05:01:13

設計中對集成到SOPC系統上的VGA接口的地址賦值為0x1后,數據寫入0x1,VGA接口控制器接收到數據,就會根據設計產生VGA時序信息及RGB信號,在屏幕上顯示圖像。圖3為整個一維信號VGA顯示系統

2019-06-04 05:00:12

USB數據與并行I/O口數據的交換緩沖區。FIFO實現與外界(微控制器、FPGA或其它器件)的接口,主要通過8根數據線D0~D7、讀寫控制線RD#和WR#以及FIFO發送緩沖區空標志TXE#和FIFO接收

2019-04-22 07:00:07

USB數據與并行I/O口數據的交換緩沖區。FIFO實現與外界(微控制器、FPGA或其它器件)的接口,主要通過8根數據線D0~D7、讀寫控制線RD#和WR#以及FIFO發送緩沖區空標志TXE#和FIFO接收

2019-04-26 07:00:12

和更低的實現成本。1 JTAG接口模塊的設計為了將配置碼流寫入Flash存儲器,上位機軟件通過JTAG下載線與JTAG接口模塊連接。JTAG接口模塊接收上位機軟件發送的JTAG信號,從中提取出JTAG

2019-05-30 05:00:05

和配置統計兩大功能:第一、接收MAC層處理子模塊發送過來的數據片,完成MAC幀重組和十路數據合路處理,再根據MAC幀封裝的三層協議類型實現數據包的分類處理,按照不同的處理要求把數據包分別送B接口、F接口

2019-04-29 07:00:07

每個處理幀將預觀測的變量結果以DMA的方式打包向上位機發送。FPGA實現ADSP-TS101的Linkport接口與CY7C68013A之間的雙向數據緩沖和接口協議轉換。考慮到CY7C68013A中

2019-05-31 05:00:04

提出了一種采用現場可編程門陣列器件FPGA 實現802.16 接收端MIMO(多輸入多輸出)2×2 檢測的方案。在C 語言平臺對基于并行干擾消除的最小均方誤差的算法進行研究和仿真后,使用Ver

2009-06-17 10:00:17 23

23 為了使計算機能夠通過串口控制FPGA 的輸出信號,筆者根據異步串行通信的原理,設計了簡便易行的FPGA 串行通信接口系統,并應用VHDL 語言在FPGA 內部集成了串行接收模塊,具有較強

2009-09-24 15:52:56 18

18 基于FPGA的SPI自動發送模塊的設計:一、摘要:SPI 接口應用十分廣泛,在很多情況下,人們會用軟件模擬的方法來產生SPI 時序或是采用帶SPI 功能模塊的MCU。但隨著可編程邏輯技

2009-10-04 08:44:40 25

25 本實驗是基于EasyFPGA030的I2C總線接口模塊設計,用EasyFPGA030開發套件通過I2C協議實現對二線制I2C串行EEPROM的讀寫操作,先把數據寫入EEPROM,然后再讀取出來顯示在數碼管上

2009-11-02 17:01:45 41

41 本實驗是基于EasyFPGA030的I2C總線接口模塊設計,用EasyFPGA030開發套件通過I2C協議實現對二線制I2C串行EEPROM的讀寫操作,先把數據寫入EEPROM,然后再讀取出來顯示在數碼管上。

2010-03-11 15:37:32 29

29 摘 要:介紹了基于現場可編程門陣列(FPGA)的以太網MAC子層協議的硬件實現方法.硬件結構上由控制模塊、發送模塊和接收模塊3個部分組成,發送模塊和接收模塊采用狀態機控制數據發

2010-07-15 11:27:29 24

24 本文詳細分析了ADSL系統中ATM層和物理層之間的UTOPIA LEVEL2接口時序,采用FPGA實現了UTOPIA接口設計,應用在ADSL系統中,數據收發正確,工作穩定;該方案的實現對解決現有專門通信芯

2010-07-28 16:54:10 19

19 介紹了一種利用FPGA實現DVB—ASI視頻傳輸流發送系統的組成原理和實現方法。不同于使用Cypress公司的CY7B923的方法,使用FPGA編程實現ASI接口轉換與發送功能,具有更大的靈活性,且接

2010-07-28 17:45:32 22

22 為解決ARCNET協議器件COM20020應用于列車通信網絡時,與中央控制單元(CCU)處理器PXA270之間時序不匹配的問題,提出一種基于FPGA的PXA270外設時序轉換接口設計方案。此外,還

2010-12-28 10:29:40 14

14 摘 要: 本文采用Altera的CPLD實現了PCI總線至UTOPIA接口的邏輯轉換控制,為低成本實現ATM終端奠定了基礎。

2006-03-11 13:16:50 1194

1194

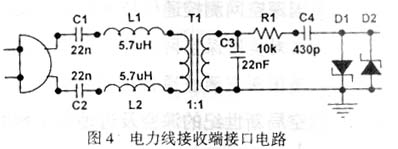

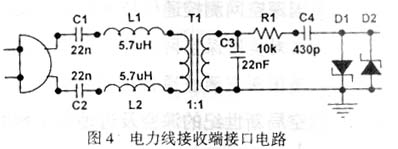

接口電路的實現 根據上述的理論分析與建立的數學模型,可設計出低壓電力線通信發送端的接口電路,如圖2所示。?

2008-10-13 13:54:52 2438

2438

如何有效的管理FPGA設計中的時序問題

當FPGA設計面臨到高級接口的設計問題時,EMA的TimingDesigner可以簡化這些設計問題,并提供對幾乎所有接口的預先精確控制。從簡單

2009-04-15 14:19:31 947

947

在本文工作的基礎上,可以進一步發揮FPGA的靈活性。如可以利用FPGA實現DSP功能,從而提供音頻DSP處理或編碼解碼;也可以與SoPC相結合,作為音頻接口模塊,為片上系統提供音頻接口

2011-06-24 10:38:33 7982

7982

為實現某專用接口裝置的接口功能檢測,文中詳細地介紹了一種34位串行碼的編碼方式,并基于FPGA芯片設計了該類型編碼的接收、發送電路。重點分析了電路各模塊的設計思路。電路采

2012-06-18 12:37:09 41

41 本文設計一個通信接口模塊,通過光纖接口與中心機連接,實現對前端受控模塊的遠程控制和狀態監測。

2012-09-03 15:59:18 5848

5848

FPGA與SPI接口程序:使用xc3s400,時鐘50Mhz,串行DA 使用max544,max544使用的是SPI接口,所以要模擬SPI發送方式。其實最重要的就是精確的模擬出發送數據的時序圖。有用的就下吧。

2012-10-23 12:35:09 194

194 電子發燒友網核心提示 :RS 232接口是現在最常用的一種通信接口。隨著FPGA技術的高速發展,一些常見的接口電路的時序電路可以通過FPGA實現,通過這種設計可減少電路系統元件的數量

2012-11-27 10:28:11 11595

11595 當你的FPGA設計不能滿足時序要求時,原因也許并不明顯。解決方案不僅僅依賴于使用FPGA的實現工具來優化設計從而滿足時序要求,也需要設計者具有明確目標和診斷/隔離時序問題的能力。

2014-08-15 14:22:10 1476

1476 Xilinx FPGA工程例子源碼:用FPGA模擬VGA時序PS_2總線的鍵盤接口VHDL源代碼

2016-06-07 15:11:20 33

33 基于FPGA技術的RS232接口時序電路設計方案

2017-01-26 11:36:55 30

30 本篇應用說明中,主要描述通過使用串行通信接口IICA,實現單主系統中主發送/接收通信(地址發送、數據發送與接收)的方法。 IIC通信概要

2017-09-13 10:24:11 3

3 本篇應用說明介紹了通過使用串行接口IICA 實現從發送和接收。單主系統使用IICA 實現從操作(地址接收、數據發送和接收)。 硬件配置

2017-09-13 11:00:03 10

10 SPI 接口應用十分廣泛,在很多情況下,人們會用軟件模擬的方法來產生SPI 時序或是采用帶SPI 功能模塊的MCU。但隨著可編程邏輯技術的發展,人們往往需要自己設計簡單的SPI 發送模塊。本文介紹

2017-10-19 10:33:01 19

19 基于FPGA的高速DSP與液晶模塊接口的實現

2017-10-19 13:46:23 3

3 系統之間的數據通信提到日程上,得到人們的急切關注。本文介紹利用VHDL語言實現 FPGA與單片機的串口異步通信電路。 整個設計采用模塊化的設計思想,可分為四個模塊:FPGA數據發送模塊,FPGA波特率發生控制模塊,FPGA總體接口模塊以及單片機數據接收模塊。

2017-11-01 16:27:56 5

5 一個好的FPGA設計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設計中不可或缺的一部分,已發揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現時序收斂。時序收斂作為

2017-11-17 07:54:36 2967

2967

針對八通道采樣器AD9252的高速串行數據接口的特點,提出了一種基于FPGA時序約束 的高速解串方法。使用Xilinx公司的FPGA接收高速串行數據,利用FPGA內部的時鐘管理模塊DCM、位置約束

2017-11-17 12:27:01 7352

7352

現有的工具和技術可幫助您有效地實現時序性能目標。當您的FPGA 設計無法滿足時序性能目標時,其原因可能并不明顯。解決方案不僅取決于FPGA 實現工具為滿足時序要求而優化設計的能力,還取決于設計人員指定前方目標,診斷并隔離下游時序問題的能力。

2017-11-18 04:32:34 3842

3842 數字存儲示波器采用ARM 與FPGA 雙處理器結合的嵌入式系統設計方案,重點介紹在FPGA 中如何實現對外圍芯片的通信與驅動,采用VHDL 語言,以逐層描述的設計模式,分成ARM 接口通信控制模塊

2017-11-18 05:47:29 3203

3203

設計,詳述了各子模塊的設計思路和方法,給出了它們的仿真時序圖。綜合實現后,將程序下載到FPGA芯片中,運行正確無誤。又經長時間發送和接收測試,運行穩定可靠。

2017-11-18 11:33:01 6257

6257 SPI接口應用十分廣泛,在很多情況下,人們會用軟件模擬的方法來產生SPI時序或是采用帶SPI功能模塊的MCU。但隨著可編程邏輯技術的發展,人們往往需要自己設計簡單的SPI發送模塊。本文介紹一種基于FPGA的將并行數據以SPI串行方式自動發送出去的方法。

2017-11-24 15:32:02 2659

2659

作為賽靈思用戶論壇的定期訪客(見 ),我注意到新用戶往往對時序收斂以及如何使用時序約束來達到時序收斂感到困惑。為幫助 FPGA設計新手實現時序收斂,讓我們來深入了解時序約束以及如何利用時序約束實現

2017-11-24 19:37:55 5955

5955

某魚雷聲自導的硬件系統使用了百兆網絡交換機實現DSP之間的互聯。交換機在MAC和PHY之間的接I=I是RMII,但DSP沒有相應的外圍設備與它匹配。因此必須在FPGA中設計RMII的通訊模塊,完成DSP數據格式向RMII數據格式的轉化。在設計中將該通訊模塊分為發送狀態機和接收狀態機兩部分

2018-10-18 16:46:51 64

64 2018年以來,因為駕駛員高估了特斯拉Autopilot功能,特斯拉車主在啟用Autopilot功能后,發生過一些備受關注的事故,包括駕駛員致死事故。雖然我們都知道嚴重依賴Level2功能的Autopilot是很危險,但確切的風險很難量化。

2018-11-06 11:35:55 1590

1590 的UART的實現方法,具體描述了發送、接收等模塊的設計,恰當使用了有限狀態機,實現了FPGA上的UART的設計,給出仿真結果。

2020-07-07 15:51:05 12

12 的實現方法,具體描述了發送、接收等模塊的設計,恰當使用了有限狀態機,實現了FPGA上的UART的設計,給出仿真結果。

2020-07-07 17:28:03 10

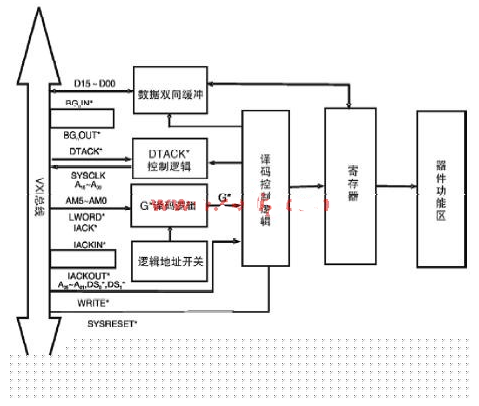

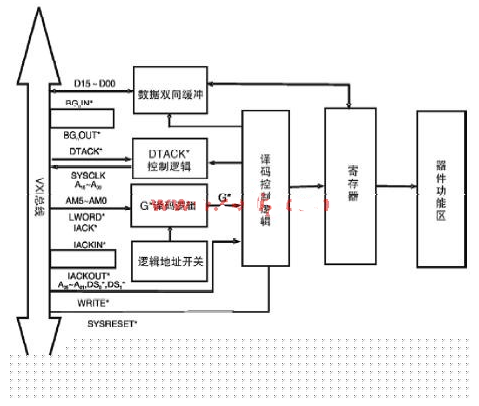

10 采用;另一種是利用中、小規模電路基PAL、GAL、CPLD和FPGA實現。通過利用FPGA實現模塊與VXI總線接口的設計過程中,總結出一些通用的設計思路。

2020-07-27 18:11:22 1417

1417

FPGA完成ARINC429總線數據的接收。重點介紹接口電路設計和FPGA中的軟件開發,與傳統的ARINC429總線數據接收系統相比,具有接口電路簡單、具備一定的抗干擾能力、不受協議芯片速率限制等優點.此方法已成功應用于產品中。并對其他串行總線數據接收具有借鑒意義。

2021-02-03 15:53:00 45

45 基于FPGA的GPS接收機實現說明。

2021-04-09 14:01:04 56

56 2. 接收模塊函數七.資料獲取一. 實現功能上電后接收端顯示接收到的數據并串口打印出來注:接收模塊數據口是輸出,相對單片機就是輸入,用51單片機的話盡量用P0口,因為P0口本身無上拉,接其它口315數據口下拉能力太弱,接其它口要接一個大概10K下拉電阻。二. 硬件清單315(或者433)發送和接收模塊

2021-12-23 19:28:39 17

17 433模塊是一種常用的無線通信模塊,用于實現短距離無線通信。在433模塊中,一般有發送和接收兩種模式。

2023-06-12 17:41:01 16374

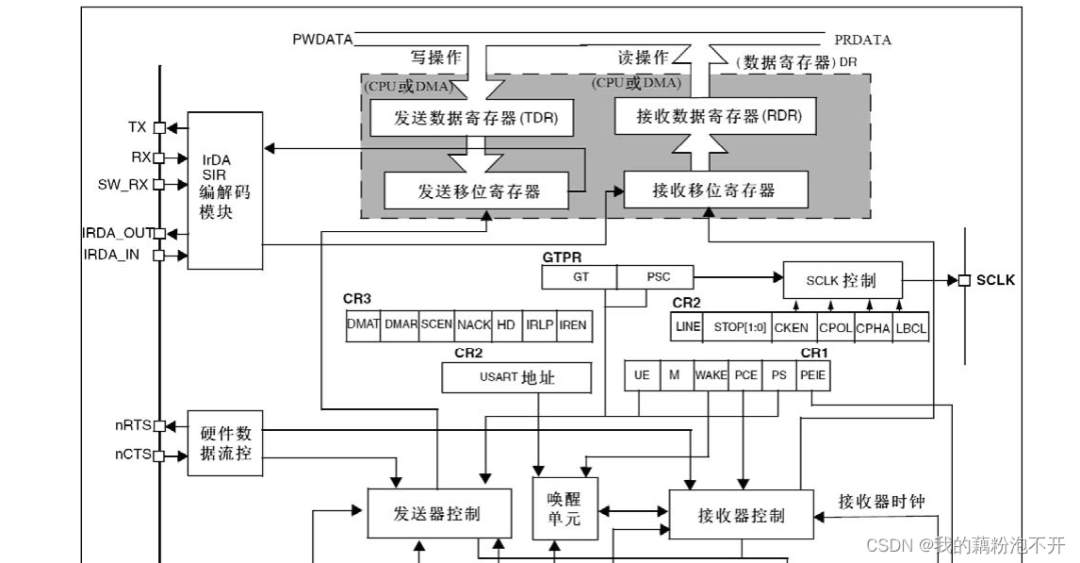

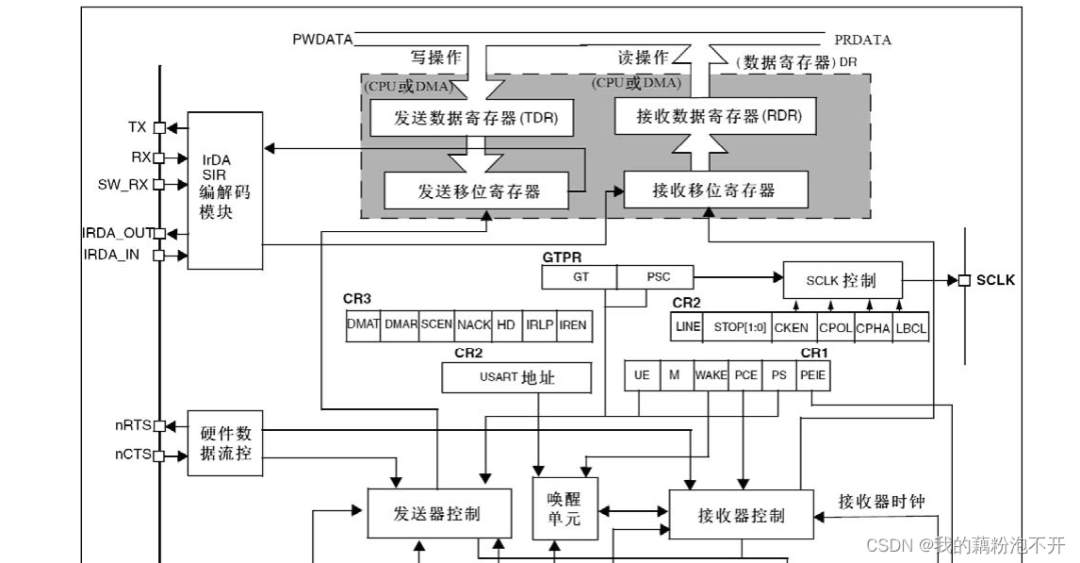

16374 USART是STM32內部集成的硬件外設,可以根據數據寄存器的一個字節數據自動生成數據幀時序,從TX引腳發送出去,也可以自動接收RX引腳的數據幀時序,拼接成一個字節數據,存放在數據寄存器里。 當配置

2023-11-10 16:04:53 2525

2525

通過用戶接口管理配置,控制CAN寄存器的尋址。向位時序模塊、can發送模塊和can接收模塊提供配置信息和操作指令,并接收來自can接收模塊的狀態信息。

2024-04-10 12:18:24 1191

1191

電子發燒友App

電子發燒友App

評論