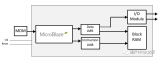

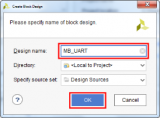

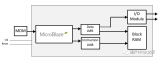

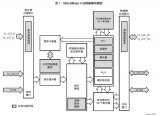

本系統(tǒng)中,Basys3的MicroBlaze模塊調(diào)用基于AXI協(xié)議的UART IP核,通過AXI總線實(shí)現(xiàn)MicroBlaze-UART之間的通信,完成串口打印。

2023-08-02 09:32:06 2459

2459

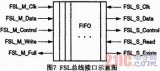

FSL總線IP核及其在MicroBlaze系統(tǒng)中的應(yīng)用

2015-01-18 21:01:20

你好我正在嘗試將microblaze連接到一個(gè)新的custimized IP。我可以使用FSL總線嗎?我可以使用vivado連接它們嗎?我應(yīng)該在IP HDL代碼和微網(wǎng)格中做什么樣的更改以及它們的接口?有什么文件可以幫助我?

2020-04-21 10:19:36

`光子計(jì)數(shù)探測(cè)器混合像素探測(cè)器,為您的實(shí)驗(yàn)室精心準(zhǔn)備PILATUS混合像素探測(cè)器的設(shè)計(jì)是X射線探測(cè)領(lǐng)域的一次革命性成果,其能夠實(shí)現(xiàn)最好的數(shù)據(jù)質(zhì)量。該探測(cè)器將單光子計(jì)數(shù)和混合像素技術(shù)這兩項(xiàng)關(guān)鍵技術(shù)

2014-03-03 19:21:07

[url=]ISE中應(yīng)用MicroBlaze軟核[/url]

2015-12-14 13:22:42

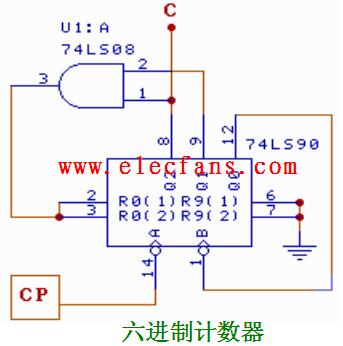

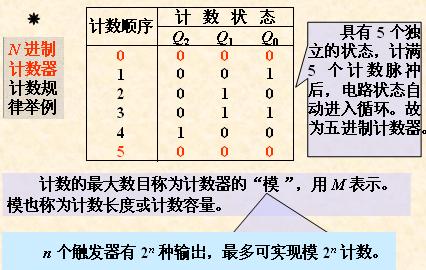

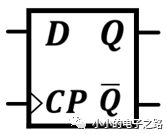

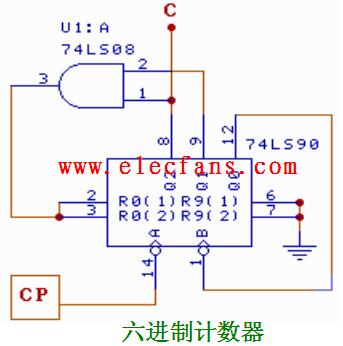

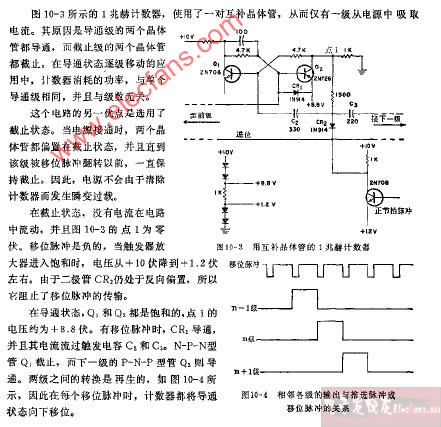

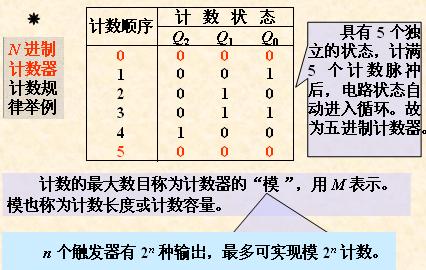

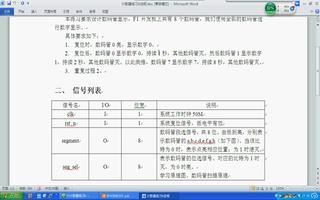

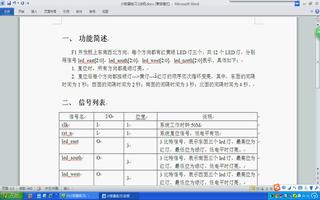

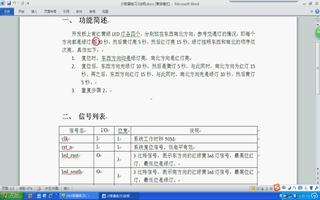

N進(jìn)制計(jì)數(shù)器的實(shí)現(xiàn) 一、用集成計(jì)數(shù)器可以實(shí)現(xiàn)任意進(jìn)制的計(jì)數(shù)器二、集成計(jì)數(shù)器控制功能的歸類三、集成計(jì)數(shù)器的級(jí)聯(lián)擴(kuò)展四、復(fù)位法組成任意進(jìn)制加法計(jì)數(shù)器五、置位法組成任意進(jìn)制加法計(jì)數(shù)器六

2008-07-05 13:41:26

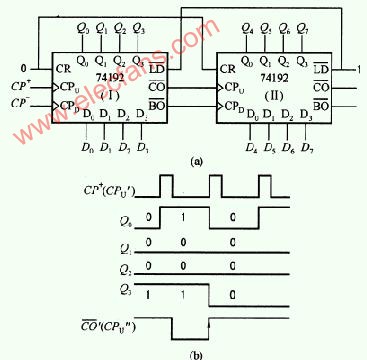

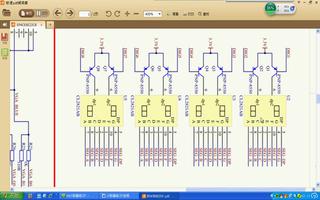

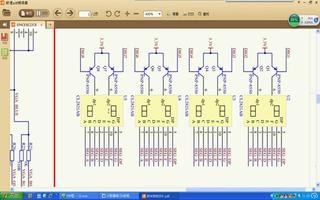

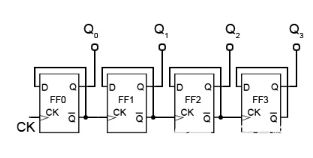

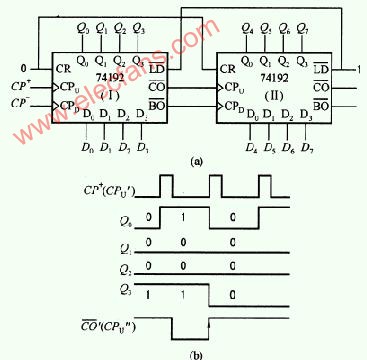

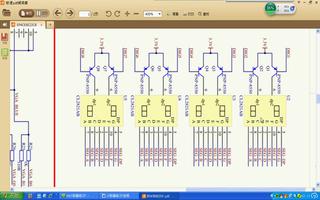

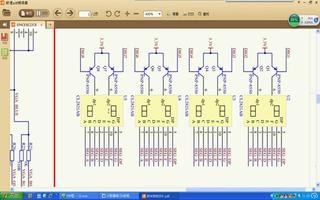

。這里實(shí)現(xiàn)了例化設(shè)計(jì)好的計(jì)數(shù)器IP核,且將其進(jìn)行兩級(jí)級(jí)聯(lián)。分析綜合無誤后點(diǎn)擊RTL viewer可以看如圖5-15所示的原理圖。圖5-15 兩級(jí)級(jí)聯(lián)的計(jì)數(shù)器原理圖為了測(cè)試仿真編寫測(cè)試激勵(lì)文件,新建

2016-12-22 23:37:00

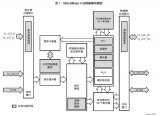

Insrtction System Computer)優(yōu)化結(jié)構(gòu)和Harvard總線結(jié)構(gòu),廣泛適用于Spartan、Virtex和Artix等系列的FPGA。MicroBlaze軟核嵌入式處理器是高度可定制的IP核

2020-10-16 16:28:50

。這里實(shí)現(xiàn)了例化設(shè)計(jì)好的計(jì)數(shù)器IP核,且將其進(jìn)行兩級(jí)級(jí)聯(lián)。分析綜合無誤后點(diǎn)擊RTL viewer可以看如圖5-15所示的原理圖。圖5-15 兩級(jí)級(jí)聯(lián)的計(jì)數(shù)器原理圖為了測(cè)試仿真編寫測(cè)試激勵(lì)文件,新建

2019-03-04 06:35:13

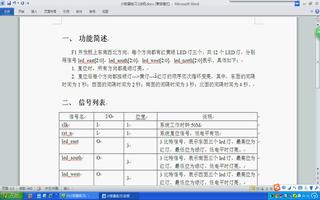

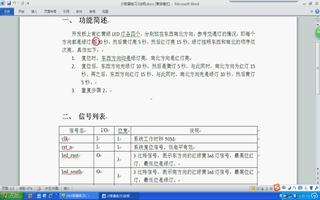

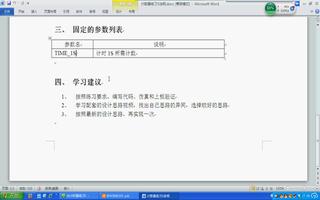

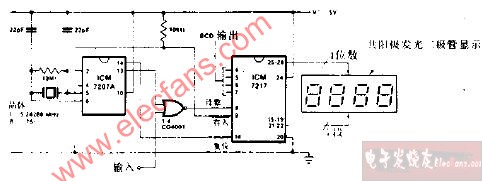

1、實(shí)現(xiàn)一個(gè)24進(jìn)制加法計(jì)數(shù)器的設(shè)計(jì)本實(shí)驗(yàn)設(shè)計(jì)實(shí)現(xiàn)一個(gè)24進(jìn)制的加法計(jì)數(shù)器,它由晶體振蕩器、分頻器、計(jì)數(shù)器和數(shù)碼管顯示器組成,圖6.1是該加法計(jì)數(shù)器的示意圖。晶體振蕩器產(chǎn)生穩(wěn)定的50MHz的脈沖信號(hào)

2022-07-05 15:14:27

大家好!我目前正在研究的項(xiàng)目需要一個(gè)計(jì)數(shù)器,該計(jì)數(shù)器具有基于兩個(gè)非周期時(shí)鐘/計(jì)數(shù)方向信號(hào)的增量或遞減其值的能力(與只需要與一個(gè)時(shí)鐘/計(jì)數(shù)方向?qū)σ黄鸸ぷ鞯耐ㄓ?b class="flag-6" style="color: red">計(jì)數(shù)器形成對(duì)比)。我可以想到幾種在ARM核

2019-10-25 12:47:24

怎么實(shí)現(xiàn)加減計(jì)數(shù)器?想要一個(gè)電路圖加上說明本人初學(xué)者 請(qǐng)大家多多指教

2015-03-08 20:19:38

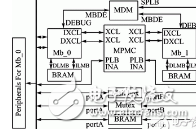

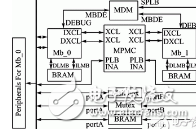

處理器間通信和中斷方面仍需進(jìn)一步的研究。本文在處理器間通信和中斷控制方面進(jìn)行了深入的研究。MicroBlaze是一個(gè)被優(yōu)化過的可以在Xilinx公司FPGA中運(yùn)行的軟核處理器,可以和其他外設(shè)IP核一起完成

2021-03-16 07:44:35

求解大神,如何用基本邏輯門和觸發(fā)器實(shí)現(xiàn)6進(jìn)制加法計(jì)數(shù)器等...還有12進(jìn)制加法計(jì)數(shù)器

2012-11-29 18:40:22

我們調(diào)用ip核生成一個(gè)4位計(jì)數(shù)器后想用該計(jì)數(shù)器模塊生成一個(gè)8位的計(jì)數(shù)器,這里就需要級(jí)聯(lián)兩個(gè)計(jì)數(shù)器這個(gè)是counter模塊:module counter ( cin, clock, cout, q

2021-11-11 07:41:25

15-1.實(shí)現(xiàn)定時(shí)的方法15-2.定時(shí)器/計(jì)數(shù)器的結(jié)構(gòu)和工作原理 15-3.定時(shí)器/計(jì)數(shù)器的控制15-4.定時(shí)器/計(jì)數(shù)器的工作方式 15-5.定時(shí)器/計(jì)數(shù)器應(yīng)用 軟件定時(shí)軟件延時(shí)不占用硬

2009-03-23 12:17:51 48

48 分析軟處理器MicroBlaze 的體系結(jié)構(gòu), 給出MicroBlaze 內(nèi)核在軟件無線電系統(tǒng)中的應(yīng)用, 實(shí)現(xiàn)SOPC(可編程系統(tǒng)芯片)。

2009-04-15 10:16:09 22

22 分析軟處理器MicroBlaze 的體系結(jié)構(gòu),給出MicroBlaze 內(nèi)核在軟件無線電系統(tǒng)中的應(yīng)用,實(shí)現(xiàn)SOPC

2009-11-30 15:02:14 31

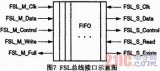

31 本文對(duì) MicroBlaze 的幾種主要總線接口摘要進(jìn)行比較,詳細(xì)分析、介紹FSL 總線的結(jié)構(gòu)、特點(diǎn)、工作原理和配置方法。通過一個(gè)矢量漢字還原的應(yīng)用實(shí)例,具體描述在FPGA片上系統(tǒng)設(shè)

2009-11-30 15:08:04 11

11 近紅外單光子探測(cè)器 SPD4近紅外單光子探測(cè)器SPD4是基于InGaAs雪崩光電二極管的超靈敏探測(cè)儀器。可以探測(cè)范圍覆蓋900 nm~1700 nm波段的光子,最高可達(dá)30%的量子效率,最低至1.0

2023-03-16 13:48:40

計(jì)數(shù)器的級(jí)連使用

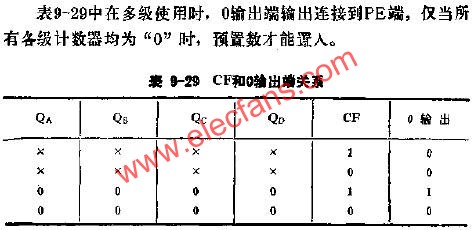

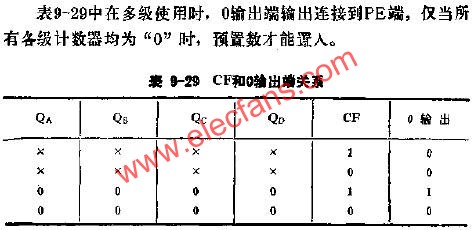

一個(gè)十進(jìn)制計(jì)數(shù)器只能顯示0~9十個(gè)數(shù),為了擴(kuò)大計(jì)數(shù)器范圍,常用多個(gè)十進(jìn)制計(jì)數(shù)器級(jí)連使用。

2007-11-22 12:53:25 4240

4240

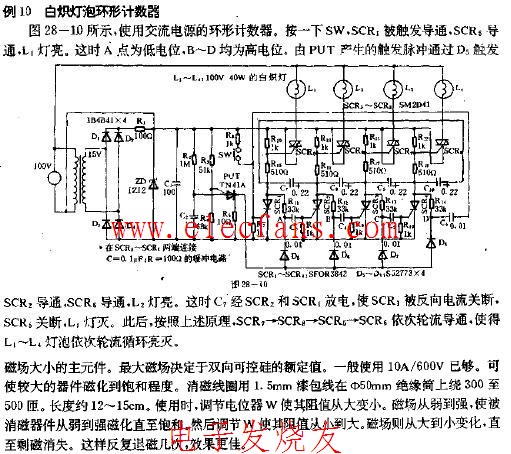

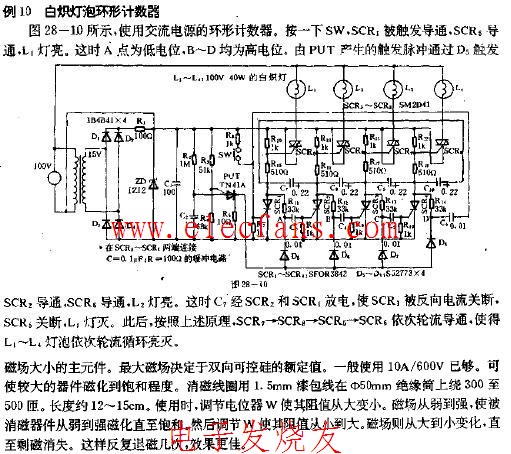

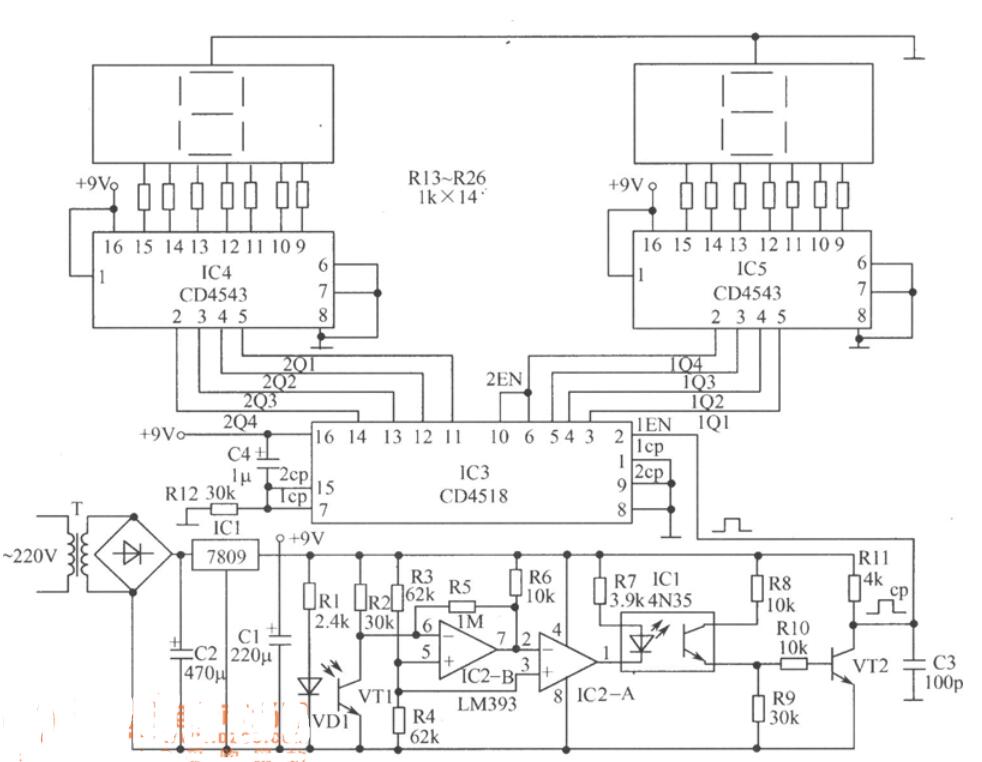

白熾燈泡環(huán)形計(jì)數(shù)器電路圖,使用交流電源的環(huán)形計(jì)數(shù)器.

2017-06-30 17:12:26 2019

2019

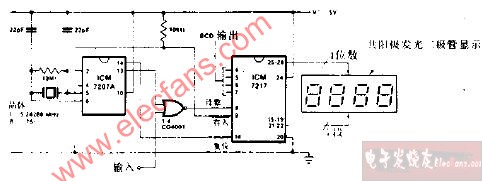

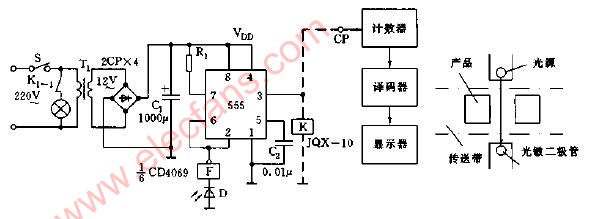

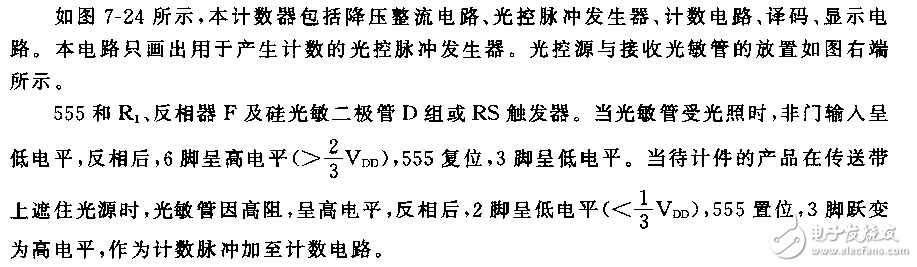

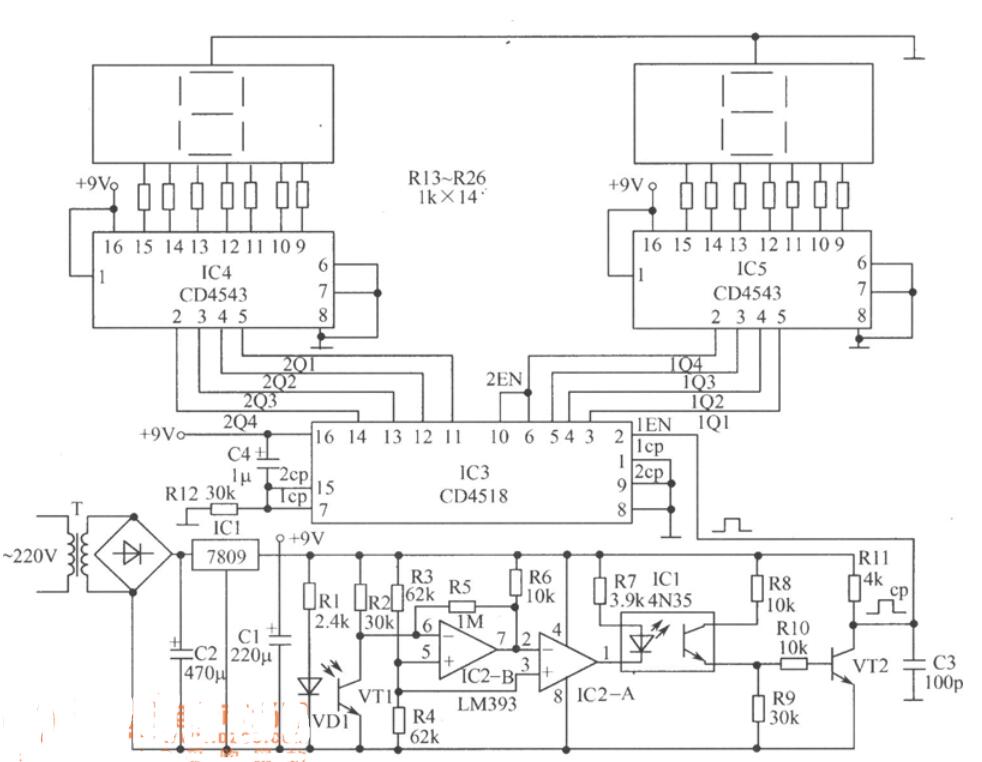

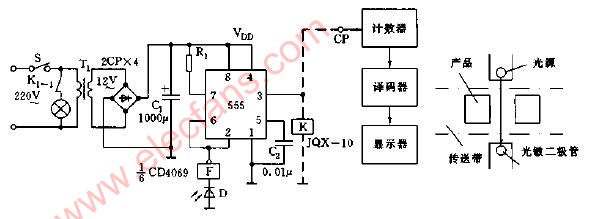

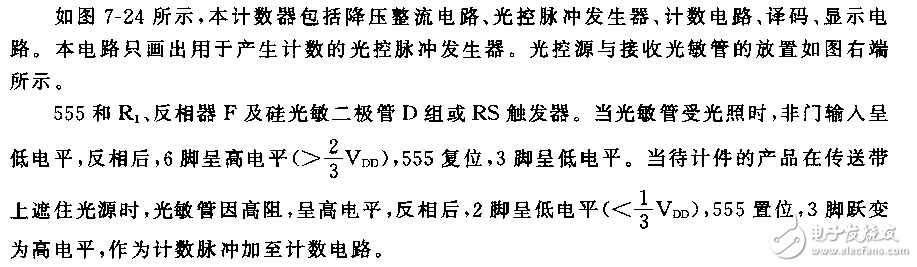

脈沖計(jì)數(shù)器電路圖,本計(jì)數(shù)器包括降整流電路,光控脈沖發(fā)生器,計(jì)數(shù)電路,譯碼,顯示電路。

2008-04-03 13:37:11 3906

3906

60進(jìn)制計(jì)數(shù)器,由于24進(jìn)制、60進(jìn)制計(jì)數(shù)器均由集成計(jì)數(shù)器級(jí)聯(lián)構(gòu)成,且都包含有基本的

2008-06-30 00:00:41 16804

16804

此計(jì)數(shù)器電路圖用到的芯片有

2008-06-30 00:09:28 9982

9982

精密頻率計(jì)數(shù)器電路圖

2009-03-29 09:50:32 1219

1219

白熾燈環(huán)形計(jì)數(shù)器電路圖

2009-03-31 08:37:12 1033

1033

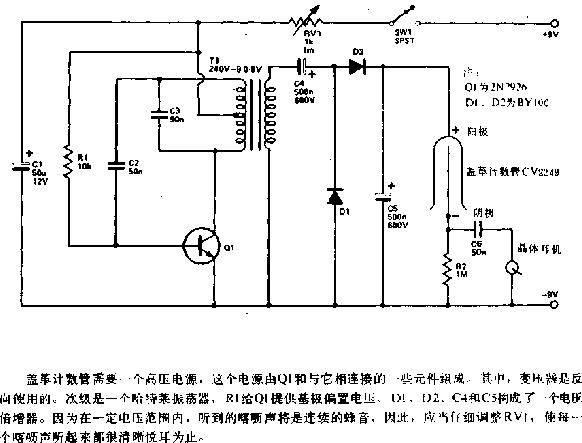

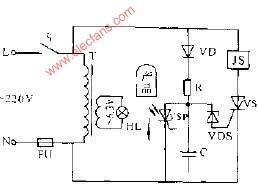

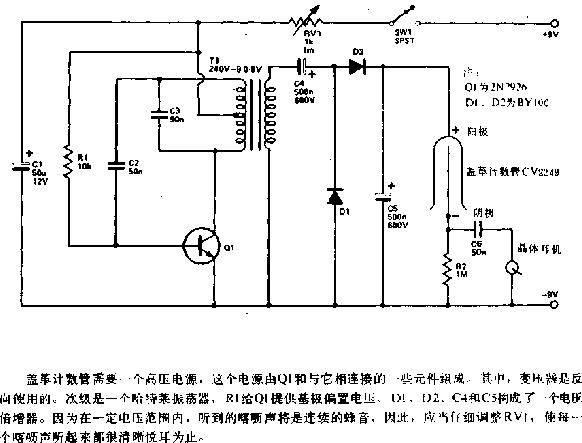

蓋革計(jì)數(shù)器電路圖

2009-04-08 08:39:19 2855

2855

靈敏的蓋革計(jì)數(shù)器電路圖

2009-04-08 08:40:24 2074

2074

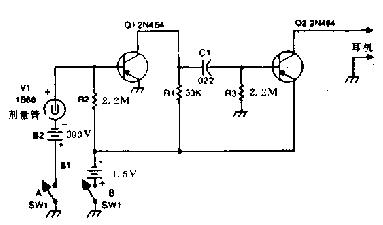

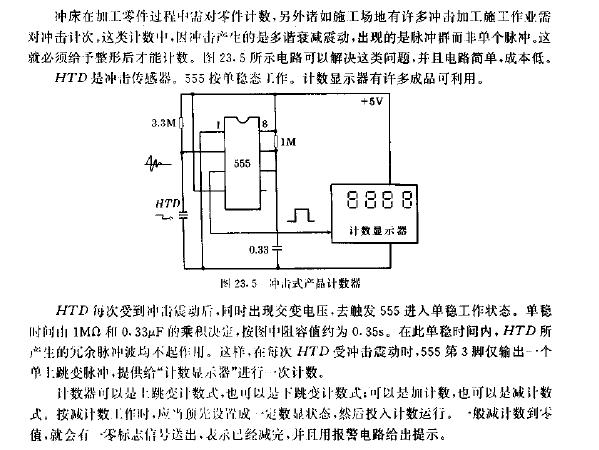

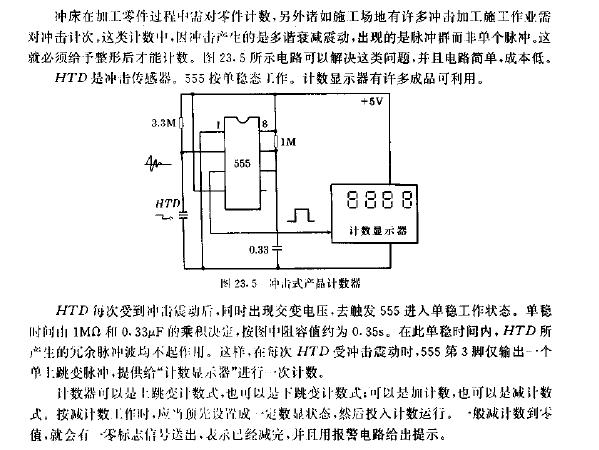

沖擊式產(chǎn)品計(jì)數(shù)器電路圖

2009-04-11 11:59:32 622

622

實(shí)驗(yàn) 計(jì)數(shù)器測(cè)試

一、 實(shí)驗(yàn)?zāi)康?、 學(xué)習(xí)8031內(nèi)部定時(shí)∕計(jì)數(shù)器的使用方法。2、 學(xué)習(xí)計(jì)數(shù)器各種工作方

2009-05-16 02:08:09 1998

1998

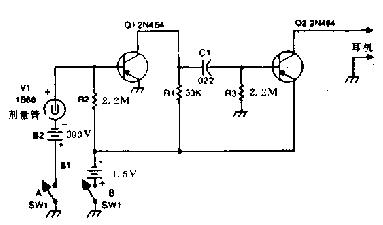

簡(jiǎn)易光控脈沖計(jì)數(shù)器電路圖

2009-05-19 13:31:42 1586

1586

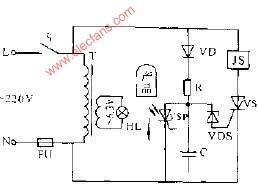

光控晶閘管計(jì)數(shù)器電路圖

2009-06-04 14:12:31 622

622

摘要: 分析軟處理器MicroBlaze的體系結(jié)構(gòu),給出MicroBlaze內(nèi)核在軟件無線電系統(tǒng)中的應(yīng)用,實(shí)現(xiàn)SOPC(可編程系統(tǒng)芯片)。

關(guān)鍵詞: FPGA IP Core SOP

2009-06-20 10:47:52 3592

3592

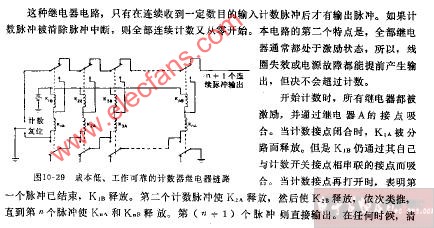

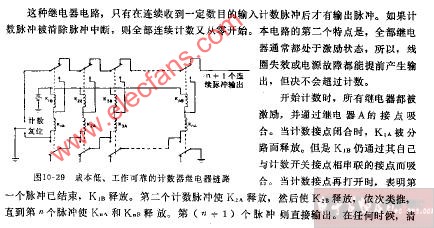

計(jì)數(shù)器繼電器鏈路電路圖

2009-06-30 13:10:32 2919

2919

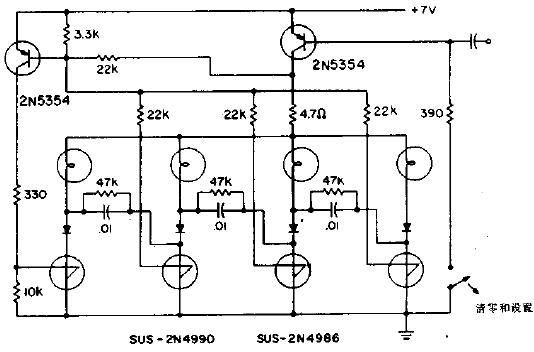

可逆線性計(jì)數(shù)器電路圖

2009-06-30 13:16:32 1181

1181

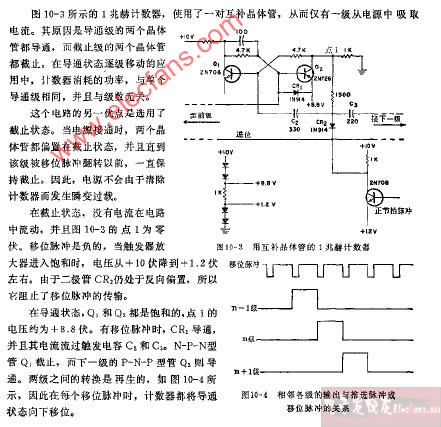

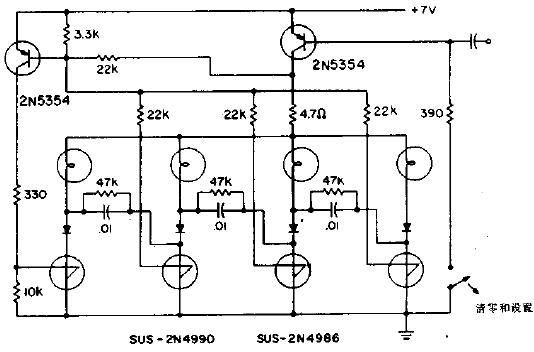

使用互補(bǔ)晶體管的計(jì)數(shù)器電路圖

2009-06-30 13:19:20 1114

1114

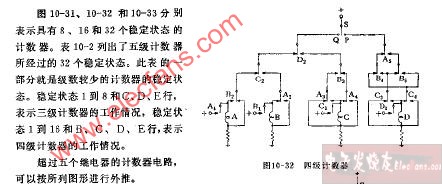

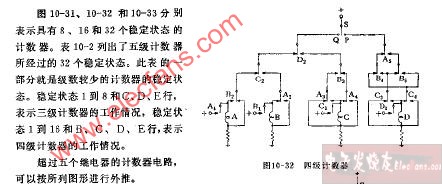

四級(jí)計(jì)數(shù)器電路圖

2009-06-30 13:20:33 917

917

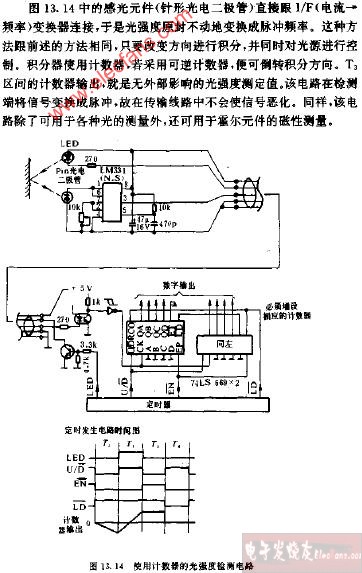

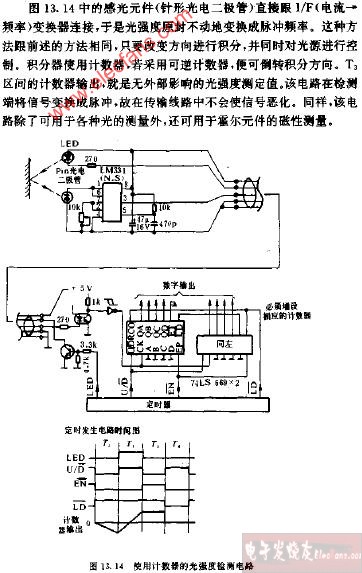

使用計(jì)數(shù)器的光強(qiáng)度檢測(cè)電路圖

2009-07-07 09:54:45 1673

1673

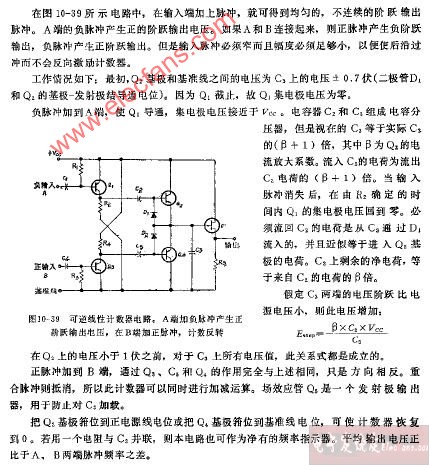

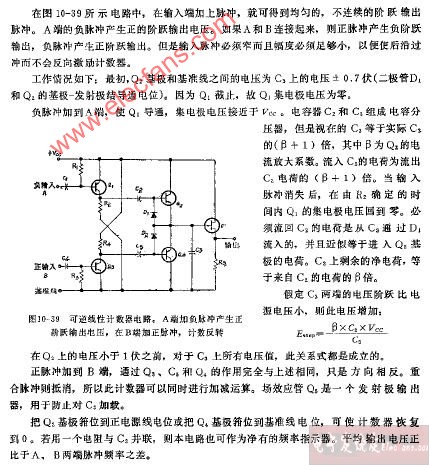

圖 可逆計(jì)數(shù)器原理圖

計(jì)數(shù)器部分全部采用CMOS電路,一是功耗低,

2009-07-21 14:53:07 6789

6789

計(jì)數(shù)器

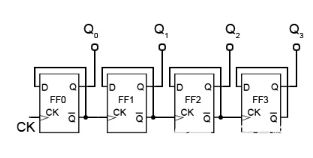

計(jì)數(shù)器的作用與分類

計(jì)數(shù)器(Counter)用于計(jì)算輸入脈沖個(gè)數(shù),還常用于分頻、定時(shí)等。

2009-09-30 18:30:15 1919

1919

計(jì)數(shù)器級(jí)聯(lián)及波形圖

2010-01-12 13:56:56 4763

4763

環(huán)形計(jì)數(shù)器和扭環(huán)形計(jì)數(shù)器

移位寄存器也可以構(gòu)成計(jì)數(shù)器,稱為移位型計(jì)數(shù)器。它有兩種結(jié)構(gòu):環(huán)形計(jì)數(shù)器和扭環(huán)形計(jì)數(shù)器。

2010-01-12 14:07:46 10310

10310 什么是二進(jìn)制計(jì)數(shù)器,二進(jìn)制計(jì)數(shù)器原理是什么?

計(jì)數(shù)器是數(shù)字系統(tǒng)中用得較多的基本邏輯器件。它不僅能記錄輸入時(shí)鐘脈沖的個(gè)數(shù),還可以實(shí)現(xiàn)

2010-03-08 13:16:34 31861

31861 計(jì)數(shù)器,計(jì)數(shù)器的工作原理是什么?

在數(shù)字系統(tǒng)中使用最多的時(shí)序電路是計(jì)數(shù)器。計(jì)數(shù)器不僅能用于對(duì)時(shí)鐘脈沖進(jìn)行計(jì)數(shù)還可以用于分頻、定時(shí),產(chǎn)生

2010-03-08 13:50:14 62401

62401 計(jì)數(shù)器的定義和分類

計(jì)數(shù)器定義在數(shù)字電路中,計(jì)數(shù)器屬于時(shí)序電路,它主要由具有記憶功能的觸發(fā)器構(gòu)成。計(jì)數(shù)器不僅僅

2010-03-08 17:37:35 14836

14836 C182可預(yù)置數(shù)1/N計(jì)數(shù)器基本上是一個(gè)減法計(jì)數(shù)器,均由四個(gè)"T"型觸發(fā)器和附加控制門組成,具有級(jí)連N個(gè)計(jì)數(shù)器

2010-10-19 15:23:07 1222

1222

MicroBlaze 核是嵌入在Xilinx FPGA之中的屬于32位RISC Harvard架構(gòu)軟處理器核。針對(duì)Xilinx MicroBlaze軟處理器的核間互連,實(shí)現(xiàn)多處理器核之間的快速通信的目的,采用了PLB和FSL總線混連的方法,

2011-07-20 17:22:21 68

68 所謂門光子計(jì)數(shù)器就是針對(duì)單自旋量子調(diào)控實(shí)驗(yàn)研究中對(duì)單個(gè)光子探測(cè)的需求所研制的。光子計(jì)數(shù)IP核與Mieroblaze軟核之間通過FSL總線進(jìn)行通訊,并且對(duì)FSL總線上的FIFO緩沖進(jìn)行了深度擴(kuò)充

2011-08-13 15:11:29 1917

1917

MicroBlaze嵌入式處理器軟核是Xilinx公司推出的基于fpga的微處理器,它采用32位精簡(jiǎn)指令集(RISC)哈佛總線架構(gòu),具有運(yùn)行速度快、占用資源少、可配置性強(qiáng)等優(yōu)點(diǎn)。借助Xilinx EDK(嵌入式開發(fā)

2011-11-16 11:54:22 66

66 目的是利用嵌入在Xilinx FPGA中的MicroBlaze核實(shí)現(xiàn)基于AXI總線的雙核嵌入式系統(tǒng)設(shè)計(jì)以及共享實(shí)現(xiàn)LED燈的時(shí)控.

2012-03-09 14:17:01 91

91 計(jì)數(shù)器是常用的時(shí)序邏輯電路器件,文中介紹了以四位同步二進(jìn)制集成計(jì)數(shù)器74LS161和異步二-五-十模值計(jì)數(shù)器74LS290為主要芯片,設(shè)計(jì)實(shí)現(xiàn)了任意模值計(jì)數(shù)器電路,并用Multisim軟件進(jìn)行了

2013-07-26 11:38:41 134

134 計(jì)數(shù)器原理圖介紹。計(jì)數(shù)器原理圖介紹。計(jì)數(shù)器原理圖介紹

2015-12-25 09:37:05 14

14 模擬脈沖計(jì)數(shù)器原理圖都是值得參考的設(shè)計(jì)。

2016-05-11 17:11:44 44

44 集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)集成計(jì)數(shù)器實(shí)現(xiàn)N進(jìn)制計(jì)數(shù)

2016-06-08 14:28:43 0

0 提出一種基于Proteus 軟件的任意進(jìn)制計(jì)數(shù)器的設(shè)計(jì)。以74LS163 集成計(jì)數(shù)器為基礎(chǔ),用置數(shù)法設(shè)計(jì)了兩種48 進(jìn)制計(jì)數(shù)器,采用Proteus 軟件對(duì)計(jì)數(shù)器進(jìn)行仿真。結(jié)果表明,Proteus 軟件具有實(shí)現(xiàn)48 進(jìn)制計(jì)數(shù)器的功能。仿真圖像清晰,能快速準(zhǔn)確地驗(yàn)證設(shè)計(jì)結(jié)果。

2016-07-29 18:53:03 0

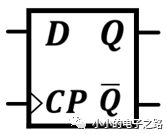

0 1、了解時(shí)序電路的經(jīng)典設(shè)計(jì)方法(D觸發(fā)器、JK觸發(fā)器和一般邏輯門組成的時(shí)序邏輯電路)。

2、了解同步計(jì)數(shù)器,異步計(jì)數(shù)器的使用方法。

3、了解同步計(jì)數(shù)器通過清零阻塞法和預(yù)顯數(shù)法得到循環(huán)任意進(jìn)制

2022-07-10 14:37:37 17

17 計(jì)數(shù)是一種最簡(jiǎn)單基本的運(yùn)算,計(jì)數(shù)器就是實(shí)現(xiàn)這種運(yùn)算的邏輯電路,計(jì)數(shù)器在數(shù)字系統(tǒng)中主要是對(duì)脈沖的個(gè)數(shù)進(jìn)行計(jì)數(shù),以實(shí)現(xiàn)測(cè)量、計(jì)數(shù)和控制的功能,同時(shí)兼有分頻功能,計(jì)數(shù)器是由基本的計(jì)數(shù)單元和一些控制門所組成

2017-09-25 10:13:37 8

8 計(jì)數(shù)是一種最簡(jiǎn)單基本的運(yùn)算,計(jì)數(shù)器就是實(shí)現(xiàn)這種運(yùn)算的邏輯電路,計(jì)數(shù)器在數(shù)字系統(tǒng)中主要是對(duì)脈沖的個(gè)數(shù)進(jìn)行計(jì)數(shù),以實(shí)現(xiàn)測(cè)量、計(jì)數(shù)和控制的功能,同時(shí)兼有分頻功能,計(jì)數(shù)器是由基本的計(jì)數(shù)單元和一些控制門所組成

2017-10-23 17:48:48 15

15 AXI總線的MicroBlaze雙核SoPC系統(tǒng)設(shè)計(jì)

2017-10-31 08:54:44 8

8 集成計(jì)數(shù)器常見的是多位二進(jìn)制計(jì)數(shù)器及十進(jìn)制計(jì)數(shù)器,當(dāng)需要實(shí)現(xiàn)其它進(jìn)制計(jì)數(shù)器時(shí),通常利用現(xiàn)有的集成計(jì)數(shù)器進(jìn)行適當(dāng)?shù)倪B接而構(gòu)成。對(duì)于當(dāng)設(shè)計(jì)要求沒有限定計(jì)數(shù)器的狀態(tài)編碼時(shí)電路設(shè)計(jì)的靈活性問題已有文獻(xiàn)進(jìn)行

2017-11-09 16:36:16 81

81 作者:薩其日娜 內(nèi)蒙古魯電電力工程有限公司 摘要: 應(yīng)用MicroBlaze軟核作為CPU的硬件平臺(tái),在此平臺(tái)上設(shè)計(jì)了基于AXI總線的通用實(shí)時(shí)時(shí)鐘IP核。給出了創(chuàng)建IP核的過程和導(dǎo)入IP核的方法

2017-11-17 16:34:42 4414

4414 設(shè)計(jì)了一款基于雙MicroBlaze軟核處理器、面向嵌入式領(lǐng)域的SOPC系統(tǒng),在信息處理繁忙的情況下,實(shí)現(xiàn)兩軟核處理器之間的同步、通信和中斷功能,提高信息吞吐率和系統(tǒng)靈活性,降低設(shè)備尺寸。兩處理器

2017-11-18 03:50:27 4439

4439

。系統(tǒng)采用的是一種基于MicroBlaze系統(tǒng)FSL總線的可擴(kuò)展計(jì)數(shù)器設(shè)計(jì)架構(gòu),該架構(gòu)能夠靈活的添加不同的計(jì)數(shù)功能,并通過統(tǒng)一的FSL總線和Microblaze CPU與PC通信。在該架構(gòu)的基礎(chǔ)上實(shí)現(xiàn)了針對(duì)量子單自旋調(diào)控實(shí)驗(yàn)中常用的計(jì)數(shù)模式。

2017-11-24 16:56:39 920

920

本文主要介紹了脈沖計(jì)數(shù)器電路圖大全(六款脈沖計(jì)數(shù)器電路設(shè)計(jì)原理圖詳解)。計(jì)數(shù)是一種最簡(jiǎn)單基本的運(yùn)算,計(jì)數(shù)器就是實(shí)現(xiàn)這種運(yùn)算的邏輯電路,計(jì)數(shù)器在數(shù)字系統(tǒng)中主要是對(duì)脈沖的個(gè)數(shù)進(jìn)行計(jì)數(shù),以實(shí)現(xiàn)測(cè)量、計(jì)數(shù)

2018-03-26 11:22:00 105426

105426

計(jì)數(shù)是一種最簡(jiǎn)單基本的運(yùn)算,計(jì)數(shù)器就是實(shí)現(xiàn)這種運(yùn)算的邏輯電路,計(jì)數(shù)器在數(shù)字系統(tǒng)中主要是對(duì)脈沖的個(gè)數(shù)進(jìn)行計(jì)數(shù),以實(shí)現(xiàn)測(cè)量、計(jì)數(shù)和控制的功能,同時(shí)兼有分頻功能,計(jì)數(shù)器是由基本的計(jì)數(shù)單元和一些控制門所組成

2018-02-24 15:31:08 50912

50912 MicroBlaze 是高度可配置的 IP 核,支持 70 多種配置選項(xiàng)。一些重要的配置選項(xiàng)為指令/數(shù)據(jù)高速緩存、浮點(diǎn)單元和存儲(chǔ)器管理單元等。用戶可使用高度靈活的可配置內(nèi)核,實(shí)現(xiàn)幾乎任何處理器使用案例

2018-03-16 16:10:26 11701

11701

觀看此視頻,請(qǐng)參閱ARTY Board與Xilinx MicroBlaze軟核處理器的配合使用。

ARTY是一款基于Xilinx Artix-7 35T FPGA的99美元評(píng)估套件,它使用MicroBlaze作為其軟核處理器。

2018-11-27 06:26:00 3013

3013 Xilinx公司的MicroBlaze 32位軟處理器核是支持CoreConnect總線的標(biāo)準(zhǔn)外設(shè)集合。MicroBlaze處理器運(yùn)行在150MHz時(shí)鐘下,可提供125 D-MIPS的性能,非常適合設(shè)計(jì)針對(duì)網(wǎng)絡(luò)、電信、數(shù)據(jù)通信和消費(fèi)市場(chǎng)的復(fù)雜嵌入式系統(tǒng)。

2018-12-05 17:18:05 13

13 計(jì)數(shù)是一種最簡(jiǎn)單基本的運(yùn)算,計(jì)數(shù)器就是實(shí)現(xiàn)這種運(yùn)算的邏輯電路,計(jì)數(shù)器在數(shù)字系統(tǒng)中主要是對(duì)脈沖的個(gè)數(shù)進(jìn)行計(jì)數(shù),以實(shí)現(xiàn)測(cè)量、計(jì)數(shù)和控制的功能,同時(shí)兼有分頻功能,計(jì)數(shù)器是由基本的計(jì)數(shù)單元和一些控制門所組成

2019-01-24 14:35:40 66786

66786 計(jì)數(shù)器

2019-09-03 06:11:00 4215

4215

計(jì)數(shù)器

2019-09-03 06:10:00 3683

3683

計(jì)數(shù)器

2019-09-03 06:09:00 3231

3231

計(jì)數(shù)器

2019-09-03 06:08:00 2461

2461

計(jì)數(shù)器

2019-09-03 06:06:00 3403

3403

計(jì)數(shù)器

2019-09-03 06:03:00 3009

3009

計(jì)數(shù)器

2019-09-03 06:02:00 2687

2687

計(jì)數(shù)器

2019-09-03 06:01:00 3592

3592

計(jì)數(shù)器

2019-09-02 06:10:00 6141

6141

計(jì)數(shù)器的工作是通過每個(gè)時(shí)鐘脈沖將計(jì)數(shù)器的內(nèi)容提前一個(gè)計(jì)數(shù)來計(jì)數(shù)。當(dāng)被時(shí)鐘輸入激活時(shí)推進(jìn)其數(shù)字或狀態(tài)序列的計(jì)數(shù)器被稱為以“遞增計(jì)數(shù)”模式操作。同樣,當(dāng)被時(shí)鐘輸入激活時(shí)減少其數(shù)字或狀態(tài)序列的計(jì)數(shù)器被稱為以“倒計(jì)數(shù)”模式操作。在UP和DOWN模式下工作的計(jì)數(shù)器稱為雙向計(jì)數(shù)器。

2019-06-23 07:47:00 16637

16637

本文參照CAN2.0 總線協(xié)議設(shè)計(jì)了一個(gè)CAN 控制器軟核。具體設(shè)計(jì)采用TOP-DOWN 方式,上層采用模塊化設(shè)計(jì),最底層模塊以Verilog 語(yǔ)言編寫而成。測(cè)試了軟核在Xilinx 公司

2019-07-19 17:48:41 27

27 本文主要介紹了電子計(jì)數(shù)器電路圖及電子計(jì)數(shù)器的接線方法。

2019-09-26 10:06:37 49358

49358

本文檔的主要內(nèi)容詳細(xì)介紹的是使用計(jì)數(shù)器中斷實(shí)現(xiàn)100以內(nèi)的按鍵計(jì)數(shù)的仿真電路圖免費(fèi)下載。

2019-12-26 09:44:31 15

15 本文檔的主要內(nèi)容詳細(xì)介紹的是實(shí)現(xiàn)0到9999的計(jì)數(shù)器程序和電路圖免費(fèi)下載。

2020-05-22 17:27:38 21

21 什么是計(jì)數(shù)器芯片? 一般來說,計(jì)數(shù)器芯片就是用來實(shí)現(xiàn)計(jì)數(shù)這種最基礎(chǔ)運(yùn)算的邏輯電路,計(jì)數(shù)器在數(shù)字系統(tǒng)中主要是對(duì)脈沖的個(gè)數(shù)進(jìn)行計(jì)數(shù),以實(shí)現(xiàn)測(cè)量、計(jì)數(shù)和控制的功能,同時(shí)兼有分頻功能,計(jì)數(shù)器是由基本的計(jì)數(shù)

2021-07-13 14:09:37 15826

15826 計(jì)數(shù)器(Counter)由基本的計(jì)數(shù)單元和控制門所組成,是在數(shù)字系統(tǒng)中對(duì)脈沖的個(gè)數(shù)進(jìn)行計(jì)數(shù),以實(shí)現(xiàn)測(cè)量、計(jì)數(shù)和控制功能,且兼有分頻功能的儀器。計(jì)數(shù)器按進(jìn)位制不同,分為二進(jìn)制計(jì)數(shù)器和十進(jìn)制計(jì)數(shù)器;按

2021-11-25 18:06:07 32

32 異步計(jì)數(shù)器是那些輸出不受時(shí)鐘信號(hào)影響的計(jì)數(shù)器。由于異步計(jì)數(shù)器中的觸發(fā)器提供有不同的時(shí)鐘信號(hào),因此在產(chǎn)生輸出時(shí)可能會(huì)有延遲。設(shè)計(jì)異步計(jì)數(shù)器所需的邏輯門數(shù)量非常少,所以它們的設(shè)計(jì)很簡(jiǎn)單。異步計(jì)數(shù)器的另一個(gè)名稱是“波紋計(jì)數(shù)器”。

2022-10-11 17:16:44 7306

7306

在數(shù)字電子產(chǎn)品中,計(jì)數(shù)器是由一系列觸發(fā)器組成的時(shí)序邏輯電路。顧名思義,計(jì)數(shù)器用于計(jì)算輸入在負(fù)或正邊沿轉(zhuǎn)換中出現(xiàn)的次數(shù)。根據(jù)觸發(fā)觸發(fā)器的方式,計(jì)數(shù)器可以分為兩類:同步計(jì)數(shù)器和異步計(jì)數(shù)器。了解這兩種計(jì)數(shù)器的工作原理以及它們之間的區(qū)別。

2023-03-25 17:31:07 29525

29525

Microblaze是32位/64位 RISC軟核處理器,可以用作微處理器、實(shí)時(shí)處理器和應(yīng)用處理器(Linux+MMU)。

2023-08-28 14:30:13 6240

6240

蓋格計(jì)數(shù)器是一種核探測(cè)器,能夠通過某種間接方法檢測(cè)不同類型的核輻射,例如α粒子、β粒子和伽馬輻射,在某些情況下還可以檢測(cè)中子。這種蓋格計(jì)數(shù)器所基于的原理非常有趣,但在我們深入講解之前,讓我們先討論這種計(jì)數(shù)器的結(jié)構(gòu)。

2023-08-28 16:48:33 2727

2727 在學(xué)習(xí)嵌入式系統(tǒng)的過程中,定時(shí)器有關(guān)內(nèi)容的學(xué)習(xí)是必不可少的一個(gè)環(huán)節(jié)。定時(shí)器定時(shí)功能的實(shí)現(xiàn),最主要的還是靠其內(nèi)部的計(jì)數(shù)器。那么,計(jì)數(shù)器是如何實(shí)現(xiàn)計(jì)數(shù)功能的呢?接下來就來簡(jiǎn)單介紹一下計(jì)數(shù)器的實(shí)現(xiàn)電路。

2023-09-25 14:18:48 4522

4522

同步計(jì)數(shù)器和異步計(jì)數(shù)器的區(qū)別詳解 同步計(jì)數(shù)器和異步計(jì)數(shù)器是數(shù)字電路中兩種常見的計(jì)數(shù)器類型,它們?cè)?b class="flag-6" style="color: red">實(shí)現(xiàn)方式和功能上存在明顯的區(qū)別。本文將詳細(xì)介紹同步計(jì)數(shù)器和異步計(jì)數(shù)器的區(qū)別,包括其工作原理、特點(diǎn)

2023-12-13 14:54:24 15772

15772 同步計(jì)數(shù)器和異步計(jì)數(shù)器是兩種常見的數(shù)據(jù)結(jié)構(gòu),它們都用于控制對(duì)共享資源的訪問。它們的主要作用是實(shí)現(xiàn)多個(gè)線程之間的同步和并發(fā)控制。盡管它們都被用于同步的目的,但它們有很多不同的特點(diǎn)和用例。 同步計(jì)數(shù)器

2023-12-15 10:49:43 3177

3177 計(jì)數(shù)器是一種被廣泛應(yīng)用于各個(gè)領(lǐng)域的實(shí)用工具,在我們的日常生活中隨處可見。無論是進(jìn)行時(shí)間統(tǒng)計(jì),協(xié)助工作任務(wù)的完成,還是用于科學(xué)研究和編程技術(shù),在各個(gè)領(lǐng)域都起到了重要的作用。本文將詳細(xì)介紹計(jì)數(shù)器

2024-02-03 10:04:14 9284

9284 在數(shù)字電子領(lǐng)域中,計(jì)數(shù)器是一種用于統(tǒng)計(jì)脈沖信號(hào)數(shù)量的重要設(shè)備。其中,同步計(jì)數(shù)器和異步計(jì)數(shù)器是兩種不同類型的計(jì)數(shù)器,它們?cè)诠ぷ髟怼⑻匦砸约皯?yīng)用場(chǎng)景等方面存在著顯著的區(qū)別。本文將詳細(xì)探討這兩種計(jì)數(shù)器的區(qū)別,以便讀者能夠更深入地理解它們的工作原理和應(yīng)用場(chǎng)景。

2024-05-24 14:36:12 7838

7838 本指南提供了有關(guān) AMD Vivado Design Suite 中包含的 32 位和 64 位 MicroBlaze V 軟核處理器的信息。該文檔旨在用作為處理器硬件架構(gòu)的指南,隨附《RISC-V 指令集手冊(cè)》第一卷和第二卷。

2024-10-16 09:17:55 1630

1630

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論