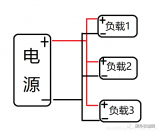

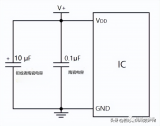

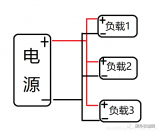

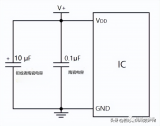

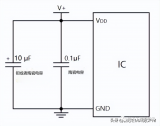

問題來了,這幾個(gè)不同規(guī)格的電容在PCB布局時(shí)該怎么擺,電源路徑是先經(jīng)大電容然后到小電容再進(jìn)入IC,還是先經(jīng)過小電容再經(jīng)過大電容然后輸入IC。

2022-08-30 10:22:23 3717

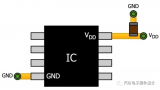

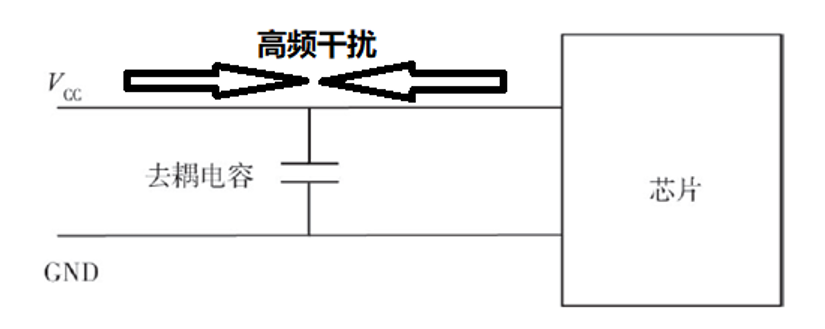

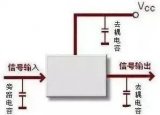

3717 去耦(decoupling)電容也稱退耦電容,一般都安置在元件附近的電源處,用來濾除高頻噪聲,使電壓穩(wěn)定干凈,保證元件的正常工作。

2022-10-24 10:46:49 5566

5566 相信大家都知道對于電路設(shè)計(jì),芯片的供電管腳需要增加一個(gè)去耦電容,往往很多“前輩”會告訴你,根據(jù)“前輩”的數(shù)十年的經(jīng)驗(yàn),容值選0.1uF就好了。

2023-05-15 10:32:08 5357

5357

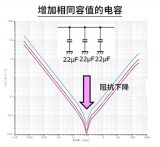

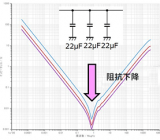

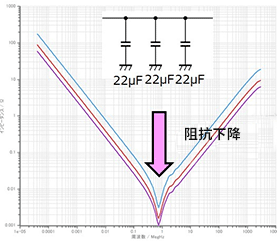

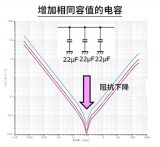

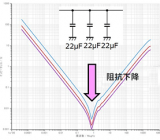

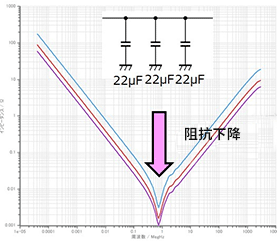

去耦電容的有效使用方法之一是用多個(gè)(而非1個(gè))電容進(jìn)行去耦。使用多個(gè)電容時(shí),使用相同容值的電容時(shí)和交織使用不同容值的電容時(shí),效果是不同的。

2023-08-02 12:34:43 870

870

去耦電容有效使用方法分為兩種: 使用多個(gè)去耦電容 使用多個(gè)去耦電容時(shí),使用相同容值的電容時(shí)和交織使用不同容值的電容時(shí),效果是不同的。 ①使用多個(gè)容值相同的電容時(shí) 當(dāng)增加容值相同的電容后,阻抗在整個(gè)

2023-08-07 09:43:14 2056

2056

使用多個(gè)去耦電容時(shí),使用相同容值的電容時(shí)和交織使用不同容值的電容時(shí),效果是不同的。

2023-08-23 16:44:42 1651

1651

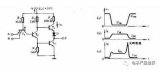

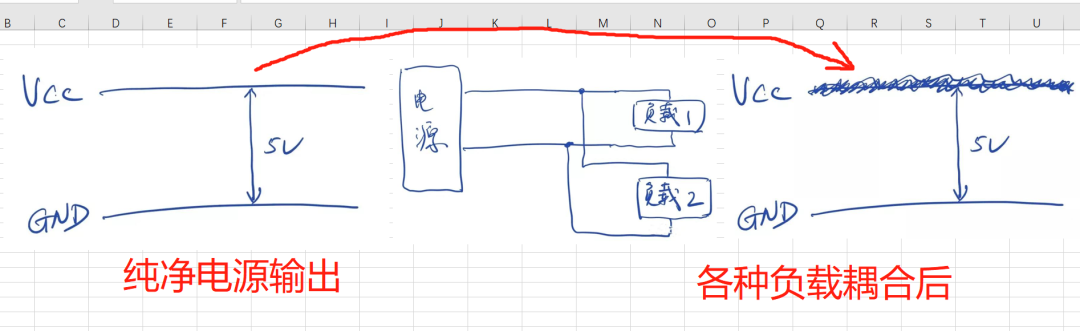

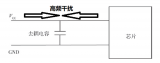

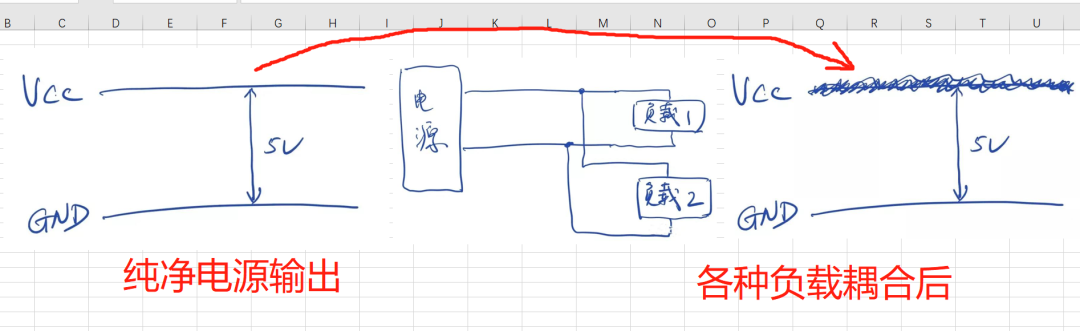

從電源上看,沒有去耦電容的時(shí)候如左側(cè)的波形,加上了去耦電容之后變成了右側(cè)的樣子,供電電壓的波形變得干凈了,我們稱該電容的作用是去掉了耦和在干凈的DC上的噪聲,所以該電容被稱之為去耦電容。

2024-03-27 14:08:48 7138

7138

為什么設(shè)計(jì)PCB電容要就近擺放呢,等看了資料后就能了解一些,可是網(wǎng)上的資料很雜散,很少能找到一個(gè)很全方面講解的。下面這些內(nèi)容是我轉(zhuǎn)載的一篇關(guān)于電容去耦半徑的講解,相信你看了之后可以很牛x的回答和避免類似問題的發(fā)生。

2016-07-26 11:30:51 6248

6248 較大,有些電路則需要以較快的速率提供電流。采用充分去耦的低阻抗電源層或接地層以及良好的 PCB 層疊,有助于將因電路的電流需求而產(chǎn)生的電壓紋波降至最低。例如,根據(jù)所用的去耦策略,如果系統(tǒng)設(shè)計(jì)的開關(guān)電流為

2020-11-18 09:18:02

,有些電路則需要以較快的速率提供電流。采用充分去耦的低阻抗電源層或接地層以及良好的 PCB 層疊,有助于將因電路的電流需求而產(chǎn)生的電壓紋波降至最低。例如,根據(jù)所用的去耦策略,如果系統(tǒng)設(shè)計(jì)的開關(guān)電流為 1

2022-05-07 11:30:38

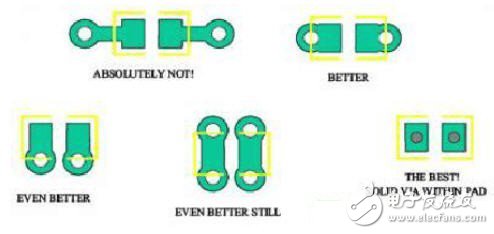

是否通過走線或通過一對過孔將去耦電容連接到IC電源引腳的問題。我們看到通孔技術(shù)是優(yōu)越的,因?yàn)樗档土穗姼校?dāng)我們試圖確保去耦電容在50-100] Vias和Planes在本文中,我們將探討與通孔

2018-07-27 11:59:50

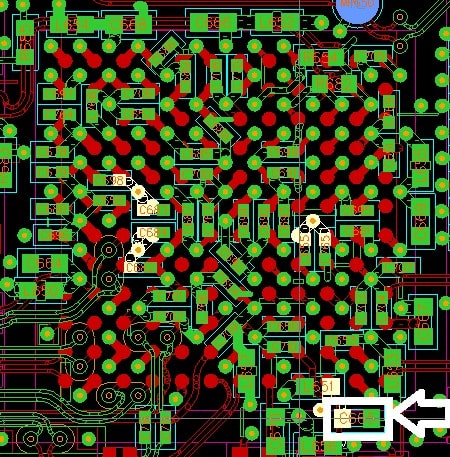

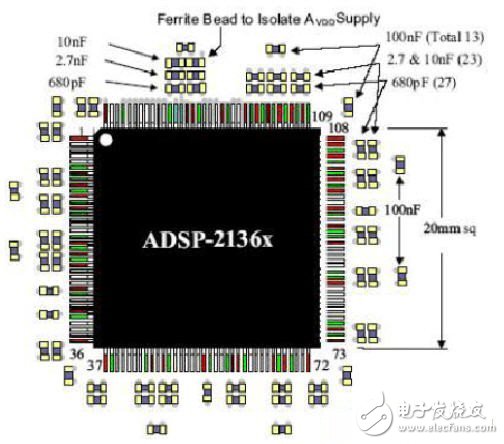

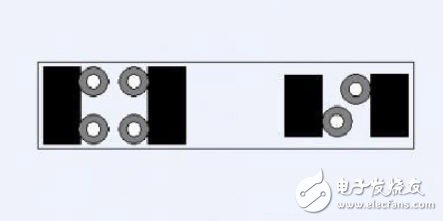

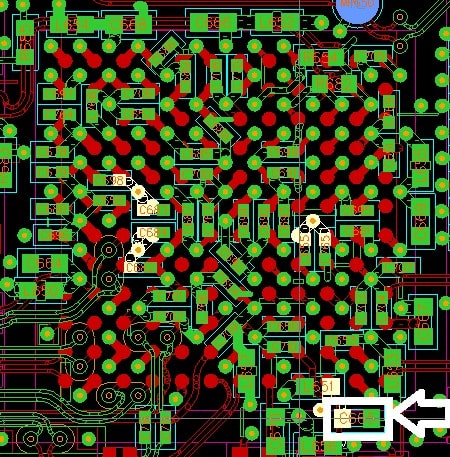

對于電容的安裝,首先要提到的就是安裝距離。容值最小的電容,有最高的諧振頻率,去耦半徑最小,因此放在最靠近芯片的位置。容值稍大些的可以距離稍遠(yuǎn),最外層放置容值最大的。但是,所有對該芯片去耦的電容都盡量

2018-09-18 15:56:26

PCB布局時(shí)怎么把元件呈現(xiàn)圓形擺放呢?如圖

2016-08-27 13:03:26

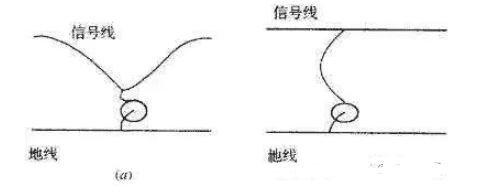

相信對做硬件的工程師,畢業(yè)開始進(jìn)公司時(shí),在設(shè)計(jì)PCB時(shí),老工程師都會對他說,PCB走線不要走直角,走線一定要短,電容一定要就近擺放等等。 但是一開始我們可能都不了解為什么這樣做,就憑他們的幾句經(jīng)驗(yàn)

2018-08-28 14:41:28

設(shè)計(jì)PCB時(shí),老工程師都會對他說,PCB走線不要走直角,走線一定要短,電容一定要就近擺放等等。但是一開始我們可能都不了解為什么這樣做,就憑他們的幾句經(jīng)驗(yàn)對我們來說是遠(yuǎn)遠(yuǎn)不夠的哦,當(dāng)然如果你沒有注意這些

2018-09-12 10:46:08

相信對做硬件的工程師,畢業(yè)開始進(jìn)公司時(shí),在設(shè)計(jì)PCB時(shí),老工程師都會對他說,PCB走線不要走直角,走線一定要短,電容一定要就近擺放等等。 但是一開始我們可能都不了解為什么這樣做,就憑他們的幾句經(jīng)驗(yàn)

2018-09-17 17:40:22

。對于小電容,因去耦半徑很小,應(yīng)盡可能的靠近需要去耦的芯片,這正是大多數(shù)資料上都會反復(fù)強(qiáng)調(diào)的,小電容要盡可能近的靠近芯片放置。 PCB布局時(shí)去耦電容擺放技巧與安裝 尖峰電流的抑制方法 1、在電路板

2023-04-11 16:26:00

pcb布局技巧擺放元件,既是科學(xué)也是藝術(shù)。其中有非常多關(guān)于布線線寬、布線疊層、原理圖等等相關(guān)的技術(shù)規(guī)范,但當(dāng)你涉及到PCB設(shè)計(jì)中具有藝術(shù)特質(zhì)元器件布局問題時(shí),問題就變得...

2021-07-21 06:50:10

去耦電容在PCB板設(shè)計(jì)中的應(yīng)用在板設(shè)計(jì)中應(yīng)充分考慮電磁兼容方面的問題,合理地使用去耦電容在PCB板防止電磁干擾中具有重要作用, 本文就去耦電容的容量及其具體應(yīng)用作了較為全面、詳細(xì)的敘述,同時(shí)還介紹了增強(qiáng)去耦電容效果的一些實(shí)用方法。[hide][/hide]

2009-12-09 14:08:29

我的STM32有四個(gè)電源引腳,現(xiàn)在確定要用四個(gè)小電容濾波。請問在布局時(shí),我這四個(gè)電容分別要靠近四個(gè)電源引腳,還是說四個(gè)電容放在一起,然后只靠近一個(gè)電源引腳就行了。

2016-07-26 18:24:31

時(shí),添加低阻抗的電容來提供電荷補(bǔ)給。高頻時(shí),回路電感影響會比較大,所以在電容的擺放位置,容值大小,ESL上的選擇要盡量使回路電感低。于爭博士在他的書和文章里曾經(jīng)提到去耦的兩種解釋,我個(gè)人理解上,覺得這兩種

2019-05-07 06:22:23

去耦旁路電路,不同規(guī)格的電容在PCB布局時(shí)該怎么擺

2021-03-17 07:33:04

變化,電容越大,儲能越多,在一定范圍內(nèi),滿足負(fù)載電流變化更有效。 說完了去耦和旁路,來到正題,電容的去耦半徑。 先記一下理論:小容值電容去耦路徑短,所以一般擺放靠近IC,否則起不到去耦效果;大容值電容去耦

2021-01-11 16:31:51

電容在高速 PCB 設(shè)計(jì)中起著重要的作用,通常也是 PCB 上用得最多的器件。在 PCB 中,電容通 常分為濾波電容、去耦電容、儲能電容等。 1 電源輸出電容,濾波電容 我們通常把電源模塊

2023-04-20 10:32:14

現(xiàn)在在畫一個(gè)ColdFire54455的板子,DDR2去耦電容這里有幾個(gè)不明白的問題,還望大家不吝賜教,萬分感激。DDR2我用的是MT47H32M16,官方Demo原理圖用的MT47H64M8,用了

2016-12-13 09:34:14

`各位大神,請問FPGA去耦電容如何布局、布線?1.根據(jù)文檔,一般去耦電容的數(shù)量都少于電源引腳,那么去耦電容要放到哪些管腳旁邊呢?2.以下三種方案哪種好?2.1電容放在PCB top層FPGA外圍

2017-08-22 14:57:10

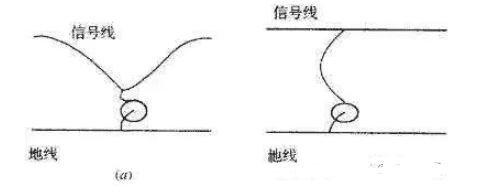

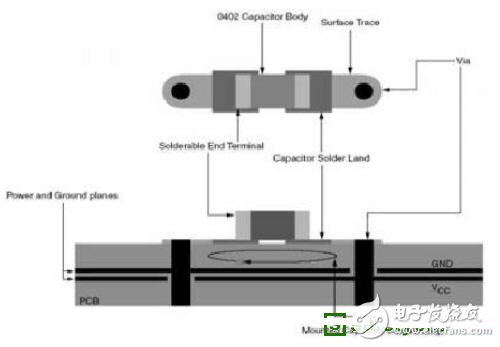

由于電源線必須為交流地,最大程度減小交流地回路的寄生電感非常重要。元件布局或擺放方向可能會引起寄生電感,例如去耦電容的地方向。旁路電容有兩種擺放方法,分別如圖所示:這種配置下,將頂層上的VCC焊盤連接

2020-07-15 08:30:00

電源線必須為交流地,最大程度減小交流地回路的寄生電感非常重要。元件布局或擺放方向可能會引起寄生電感,例如去耦電容的地方向。旁路電容有兩種擺放方法,分別如圖所示:這種配置下,將頂層上的VCC焊盤連接至內(nèi)層

2020-07-15 10:00:00

通過遵循一些在PCB布局中放置去耦電容器的準(zhǔn)則,了解如何減少二次諧波失真。 在上一篇文章中,我們討論了需要對稱的PCB布局以減少二次諧波失真。 在本文中,我們將看到,如果沒有適當(dāng)?shù)?b class="flag-6" style="color: red">去耦,我們

2023-04-21 15:24:03

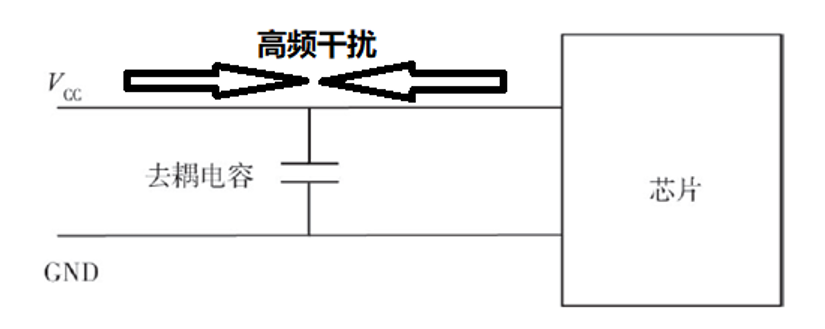

去耦電容的容值計(jì)算和布局布線 有源器件在開關(guān)時(shí)產(chǎn)生的高頻開關(guān)噪聲將沿著電源線傳播。去耦電容的主要功能就是提供一個(gè)局部的直流電源給有源器件,以減少開關(guān)噪聲在板上的傳播,和將噪聲引導(dǎo)到地。

2019-07-22 07:37:46

相信對做硬件的工程師,畢業(yè)開始進(jìn)公司時(shí),在設(shè)計(jì)PCB時(shí),老工程師都會對他說,PCB走線不要走直角,走線一定要短,電容一定要就近擺放等等。 但是一開始我們可能都不了解為什么這樣做,就憑他們的幾句經(jīng)驗(yàn)

2019-09-06 18:13:24

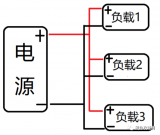

工程師們在設(shè)計(jì)PCB電源分配系統(tǒng)的時(shí)候,首先把整個(gè)設(shè)計(jì)分成四個(gè)部分:電源(電池、轉(zhuǎn)換器或者整流器)、PCB、電路板去耦電容和芯片去耦電容。本文將

2007-10-16 12:49:34 910

910 PCB布局的準(zhǔn)則和操作技巧

摘要: PCB布局的準(zhǔn)則操作技巧& 濾波電容、去耦電容、旁路電容作用& 在一個(gè)大的電容上還并

2009-11-18 09:19:12 2862

2862 去耦電容就是起到一個(gè)電池的作用,滿足驅(qū)動電路電流的變化,避免相互間的耦合干擾,旁路電容實(shí)際也是去耦合的

2011-02-15 16:02:12 659

659 電容去耦的一個(gè)重要問題是電容的去耦半徑。大多數(shù)資料中都會提到電容擺放要盡量靠近芯片,多數(shù)資料都是從減小回路電感的角度來談這個(gè)擺放距離問題。確實(shí),減小電感是一個(gè)重要

2011-11-28 18:06:04 2944

2944 耦電容器的作用你知道嗎?在眾多電路設(shè)計(jì)的應(yīng)用中都會用到去耦電容器,但設(shè)計(jì)者也往往嫌麻煩而省略了去耦電容器的使用。

2014-09-16 10:51:52 2204

2204 簡要的介紹了濾波電容、去耦電容、旁路電容以及他們的作用

2015-10-29 15:15:22 61

61 PCB布線技巧之去耦電容的擺放,學(xué)習(xí)資料,感興趣的可以看看。

2016-10-26 15:28:24 0

0 翻譯: TI信號鏈工程師 Michael Huang (黃翔) 以前談到電源去耦,我警告過糟糕的去耦會增加放大器的失真。一位讀者問了一個(gè)有趣的問題,去耦電容的接地腳應(yīng)該在哪里接地才能消除這個(gè)問題呢?這個(gè)問題升級到關(guān)于正確接地的技術(shù)。

2017-04-08 07:42:11 7092

7092

電容去耦的一個(gè)重要問題是電容的去耦半徑。大多數(shù)資料中都會提到電容擺放要盡量靠近芯片,多數(shù)資料都是從減小回路電感的角度來談這個(gè)擺放距離問題。確實(shí),減小電感是一個(gè)重要原因,但是還有一個(gè)重要的原因大多數(shù)

2017-11-12 10:53:40 7402

7402

去耦電容是電路中裝設(shè)在元件的電源端的電容,此電容可以提供較穩(wěn)定的電源,同時(shí)也可以降低元件耦合到電源端的噪聲,間接可以減少其他元件受此元件噪聲的影響。在電子電路中,去耦電容和旁路電容都是起到抗干擾的作用。

2017-11-27 16:35:50 3875

3875

去耦電容的容值計(jì)算和布局布線有源器件在開關(guān)時(shí)產(chǎn)生的高頻開關(guān)噪聲將沿著電源線傳播。去耦電容的主要功能就是提供一個(gè)局部的直流電源給有源器件,以減少開關(guān)噪聲在板上的傳播,和將噪聲引導(dǎo)到地。

去耦電容

2018-01-19 16:23:19 1094

1094

去耦電容的應(yīng)用的非常廣泛,在電路應(yīng)用過程中對于去耦電容的容值計(jì)算和PCB電路布局布線有一些我們必須要了解的技巧。

2018-01-28 18:28:00 15963

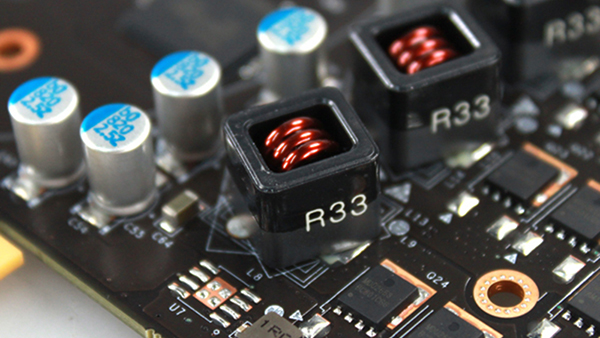

15963 對于電容的安裝,首先要提到的就是安裝距離。容值最小的電容,有最高的諧振頻率,去耦半徑最小,因此放在最靠近芯片的位置。容值稍大些的可以距離稍遠(yuǎn),最外層放置容值最大的。但是,所有對該芯片去耦的電容都盡量靠近芯片。

2018-03-12 16:32:21 8494

8494

對于電容的安裝,首先要提到的就是安裝距離。容值最小的電容,有最高的諧振頻率,去耦半徑最小,因此放在最靠近芯片的位置。

2018-12-28 13:53:33 5000

5000 SOIC的去耦局部的高頻濾波器可以優(yōu)化小小效果,去耦電容 可以減小回路電感經(jīng)驗(yàn)法則

2019-02-27 16:03:57 5686

5686

電容去耦的一個(gè)重要問題是電容的去耦半徑。大多數(shù)資料中都會提到電容擺放要盡量靠近芯片,多數(shù)資料都是從減小回路電感的角度來談這個(gè)擺放距離問題。確實(shí),減小電感是一個(gè)重要原因,但是還有一個(gè)重要的原因大多數(shù)

2019-08-15 17:32:00 5

5 去耦電容是電路中裝設(shè)在元件的電源端的電容,此電容可以提供較穩(wěn)定的電源,同時(shí)也可以降低元件耦合到電源端的噪聲,間接可以減少其他元件受此元件噪聲的影響。去耦電容和旁路電容都是起到抗干擾的作用,電容所處

2019-08-09 17:33:00 5

5 PCB布局的準(zhǔn)則操作技巧& 濾波電容、去耦電容、旁路電容作用& 在一個(gè)大的電容上還并聯(lián)一個(gè)小電容的原因。

2019-09-12 09:29:45 1132

1132 去耦電容是電路中裝設(shè)在元件的電源端的電容,此電容可以提供較穩(wěn)定的電源,同時(shí)也可以降低元件耦合到電源端的噪聲,間接可以減少對其他元件的噪聲影響。 市場上去耦電容有很多類型,但每種電容的電氣特性、極性

2020-12-03 11:25:53 5344

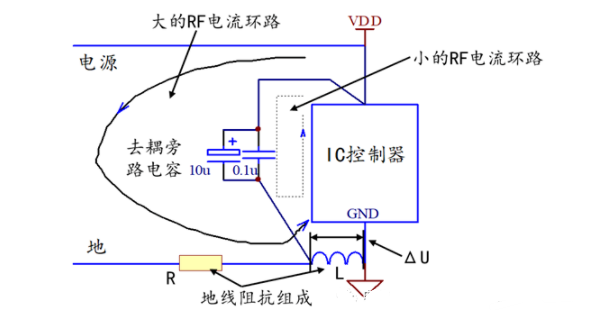

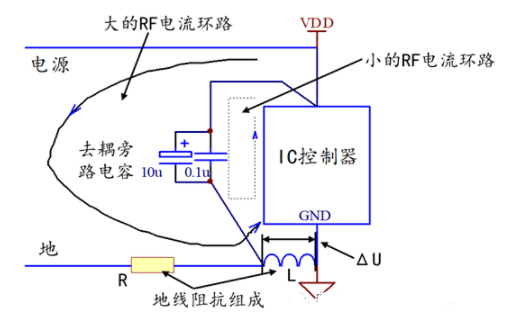

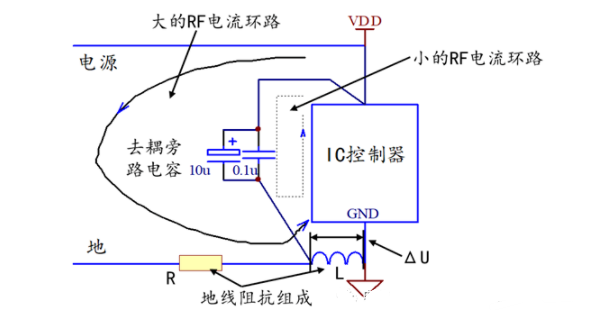

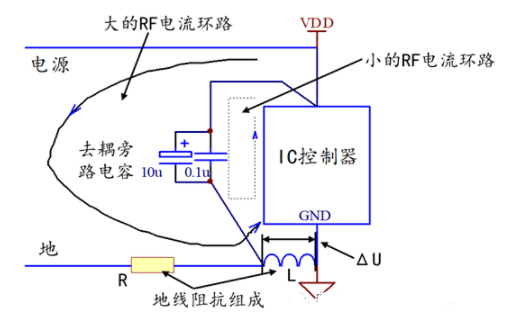

5344 能量從高頻器件的電源端泄放到電源分配網(wǎng)絡(luò)。去耦電容也為器件和元件提供一個(gè)局部的直流源,這對減小電流在板上傳播浪涌尖峰很有作用。 在數(shù)字電路及IC控制器電路中,必須要進(jìn)行電源去耦。當(dāng)元件開關(guān)消耗直流能量時(shí),沒有去

2021-01-07 14:30:28 3352

3352

超級電容器),以及石墨烯超級電容器可以做得很小。這些進(jìn)步令人振奮,可能只會增加電容器目前在 PCB 布局中所起的重要作用。包括信號去耦。讓我們?yōu)槟?PCB 布局定義最有益的去耦電容器放置準(zhǔn)則,但首先,我們討論去耦對電路板信號

2020-09-29 19:57:33 4768

4768 我們不時(shí)聽到客戶提出一個(gè)很好的問題。將去耦電容器放置在目標(biāo) IC 附近是否重要?一般的經(jīng)驗(yàn)法則是這樣說的,每個(gè) PCB 設(shè)計(jì)者都知道這一點(diǎn),甚至經(jīng)驗(yàn)不足。 但是,在現(xiàn)實(shí)生活中的布線實(shí)踐中,通常很難在

2020-10-12 20:59:45 4856

4856

一,什么是PCB中的板級去耦呢?

板級去耦其實(shí)就是電源平面和地平面之間形成的等效電容,這些等效電容起到了去耦的作用。主要在多層板中會用到這種設(shè)計(jì)方法,因?yàn)槎鄬影蹇梢詷?gòu)造出電源層和地層,而一層板

2022-02-10 11:34:48 2294

2294 一,什么是PCB中的板級去耦呢?

板級去耦其實(shí)就是電源平面和地平面之間形成的等效電容,這些等效電容起到了去耦的作用。主要在多層板中會用到這種設(shè)計(jì)方法,因?yàn)槎鄬影蹇梢詷?gòu)造出電源層和地層,而一層板

2022-02-10 10:03:29 1781

1781 從低頻設(shè)計(jì)過渡到高頻設(shè)計(jì)時(shí),PCB布局的某些方面變化不大,但亦不可等閑視之。 高頻去耦 但是,確實(shí)需要特別考慮的一件事是去耦。當(dāng)信號從低頻轉(zhuǎn)移到高頻時(shí),基本概念不會改變,但是實(shí)現(xiàn)可能需要進(jìn)行一些改進(jìn)

2021-01-26 10:23:11 2228

2228

一,什么是PCB中的板級去耦呢?

板級去耦其實(shí)就是電源平面和地平面之間形成的等效電容,這些等效電容起到了去耦的作用。主要在多層板中會用到這種設(shè)計(jì)方法,因?yàn)槎鄬影蹇梢詷?gòu)造出電源層和地層,而一層板與兩層

2021-02-19 06:38:42 14

14 一,什么是PCB中的板級去耦呢?

板級去耦其實(shí)就是電源平面和地平面之間形成的等效電容,這些等效電容起到了去耦的作用。主要在多層板中會用到這種設(shè)計(jì)方法,因?yàn)槎鄬影蹇梢詷?gòu)造出電源層和地層,而一層板與兩層

2021-03-14 06:08:22 22

22 什么是旁路電容、去耦電容、濾波電容?作用是什么??濾波電容——用在電源整流電路中,用來濾除交流成分,使輸出的直流更平滑。 去耦電容——用在放大電路中不需要交流的地方,用來消除自激,使放大器穩(wěn)定工作

2021-03-17 01:17:50 3451

3451 電子發(fā)燒友網(wǎng)為你提供去耦旁路電路,不同規(guī)格的電容在PCB布局時(shí)該怎么擺資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計(jì)、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-03-28 08:42:25 13

13 旁路電容、去耦電容、濾波電容的作用介紹 什么是旁路電容、去耦電容、濾波電容?作用是什么? 濾波電容——用在電源整流電路中,用來濾除交流成分,使輸出的直流更平滑。去耦電容——用在放大電路中不需要交流

2021-06-22 10:53:19 6238

6238 先談兩個(gè)比較重要的概念:旁路電容(Bypass Capacitor),去耦電容(Decoupling Capacitor)。

2021-06-23 14:54:27 5138

5138 去耦電容在集成電路電源和地之間的有兩個(gè)作用:一方面是本集成電路的蓄能電容,另一方面旁路掉該器件的高頻噪聲,數(shù)字電路中典型的去耦電容值是0.1μF。這個(gè)電容的分布電感的典型值是5μH。

2022-01-06 14:23:44 1996

1996 PCB PDN design guidelines (PCB電源完整性設(shè)計(jì)指導(dǎo)) ------PCB平面圖指南一、 不帶電源平面1.為每個(gè)有源設(shè)備至少提供一個(gè)“本地”去耦電容器,并為板上分布的每個(gè)

2022-01-06 12:25:33 9

9 對于電容的安裝,首先要提到的就是安裝距離。容值最小的電容,有最高的諧振頻率,去耦半徑最小,因此放在最靠近芯片的位置。容值稍大些的可以距離稍遠(yuǎn),最外層放置容值最大的。但是,所有對該芯片去耦的電容都盡量

2022-02-10 12:05:02 21

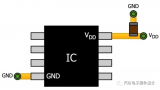

21 去耦電容的走線、焊盤,還有過孔將嚴(yán)重的影響到去耦電容的效果。因此在設(shè)計(jì)時(shí)必須充分考慮連接去耦電容的走線,應(yīng)盡可能的短而寬,連接到過孔的導(dǎo)線也應(yīng)盡可能的短。

2022-07-25 14:13:53 1584

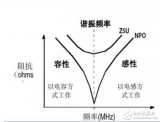

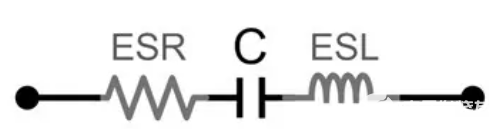

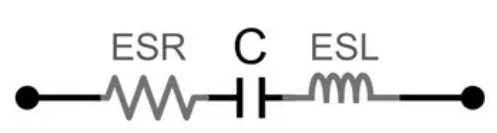

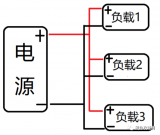

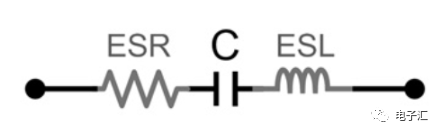

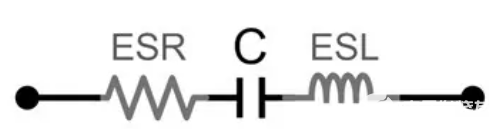

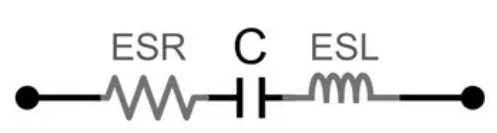

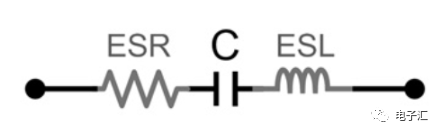

1584 問題來了,這幾個(gè)不同規(guī)格的電容在PCB布局時(shí)該怎么擺,電源路徑是先經(jīng)大電容然后到小電容再進(jìn)入IC,還是先經(jīng)過小電容再經(jīng)過大電容然后輸入IC。 我們知道,在實(shí)際應(yīng)用中,電容不僅僅是理想的電容C,還具有等效串聯(lián)電阻ESR及等效串聯(lián)電感ESL,如下圖所示

2022-09-04 10:42:16 3077

3077

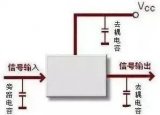

Part 1 旁路電容和去耦電容基礎(chǔ)知識 “旁路電容”和“去耦電容” 一、定義和區(qū)別 旁路(bypass)電容:是把輸入信號中的高頻成分作為濾除對象; 去耦(decoupling)電容:也稱退耦電容

2022-10-25 20:36:59 2343

2343 去耦(decoupling)電容也稱退耦電容,一般都安置在元件附近的電源處,用來濾除高頻噪聲,使電壓穩(wěn)定干凈,保證元件的正常工作。

2022-11-04 20:50:54 3796

3796 在電子電路中,去耦電容和旁路電容都是起到抗干擾的作用,電容所處的位置不同,稱呼就不一樣了。對于同一個(gè)電路來說,旁路(bypass)電容是把輸入信號中的高頻噪聲作為濾除對象,把前級攜帶的高頻雜波濾除,而去耦(decoupling)電容也稱退耦電容,是把輸出信號的干擾作為濾除對象。

2022-12-16 14:35:58 5886

5886 什么是去耦以及為什么要去耦? 模電書上講的去耦大多是講電源的去耦,就是一個(gè)電路的各個(gè)單元共用同一電源供電,為了防止各單元之間的耦合,需加去耦電路。 造成耦合的原因有:

2023-02-08 13:57:24 3703

3703 在PCB的設(shè)計(jì)中,使用去偶電容能夠有效濾除電源中包含的噪聲,電容的擺放是根據(jù)容值大小確定,電容的去耦作用是有一定的距離要求,滿足去耦半徑問題

2023-03-08 15:15:00 2794

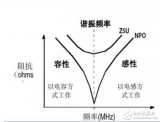

2794 自諧振頻率點(diǎn)是區(qū)分電容器是容性還是感性的分界點(diǎn),低于諧振頻率時(shí)電容表現(xiàn)為電容特性,高于諧振頻率是電容表現(xiàn)為電感特性。

2023-03-09 12:23:56 1650

1650 模電書上講的去耦大多是講電源的去耦,就是一個(gè)電路的各個(gè)單元共用同一電源供電,為了防止各單元之間的耦合,需加去耦電路。

2023-03-30 10:15:02 1707

1707

問題來了,這幾個(gè)不同規(guī)格的電容在PCB布局時(shí)該怎么擺,電源路徑是先經(jīng)大電容然后到小電容再進(jìn)入IC,還是先經(jīng)過小電容再經(jīng)過大電容然后輸入IC。

2023-04-18 09:11:56 982

982

相信大家都知道對于電路設(shè)計(jì),芯片的供電管腳需要增加一個(gè)去耦電容,往往很多“前輩”會告訴你,根據(jù)“前輩”的數(shù)十年的經(jīng)驗(yàn),容值選0.1uF就好了。

2023-04-24 11:49:34 4703

4703

電容在高速 PCB 設(shè)計(jì)中起著重要的作用,通常也是 PCB 上用得最多的器件。在 PCB 中,電容通常分為濾波電容、去耦電容、儲能電容等。

2023-05-29 10:26:30 8502

8502

工作時(shí)產(chǎn)生的ΔI噪聲電流,保證工作電源電壓的穩(wěn)定。它的大小為PCB上所有負(fù)載電容和的50~100倍。它應(yīng)放置在緊靠PCB外接電源線和地線的地方,印制線密度很高的地方。這不僅不會減小低頻去耦,而且還會為PCB上布置關(guān)鍵性的印制線提供空間。

2023-06-15 18:04:01 4129

4129

去耦電容用于濾除輸出信號的干擾,通常用于不需要交流電的放大器電路中,用來消除自激,使放大器溫度工作。

2023-07-05 09:35:33 1556

1556

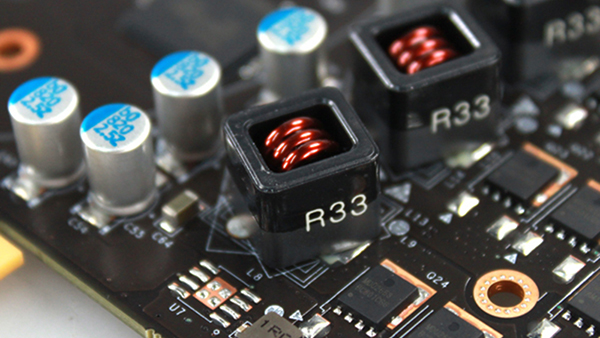

今天給大家分享的是:去耦電容,去耦電容PCB設(shè)計(jì)和布局。

2023-07-05 09:37:14 2167

2167

去耦(decoupling)電容也稱退耦電容,一般都安置在元件附近的電源處,用來濾除高頻噪聲,使電壓穩(wěn)定干凈,保證元件的正常工作。

2023-08-06 17:02:56 7619

7619

一站式PCBA智造廠家今天為大家講講PCB設(shè)計(jì)時(shí)電容如何擺放?PCB設(shè)計(jì)過程中電容作用及擺放位置。PCB設(shè)計(jì)為什么電容要就近擺放呢?因?yàn)樗杏行О霃剑诺倪h(yuǎn)了失效。電容去耦的一個(gè)重要問題是電容的去耦

2023-10-20 09:17:36 2118

2118 理解去耦半徑的辦法就是考察噪聲源和電容補(bǔ)償電流之間的相位關(guān)系。當(dāng)芯片對電流的需求發(fā)生變化時(shí),會在電源平面的一個(gè)很小的局部區(qū)域內(nèi)產(chǎn)生電壓擾動,電容要補(bǔ)償這一電流(或電壓),就必須先感知到這個(gè)電壓擾動。信號在介質(zhì)中傳播需要一定的時(shí)間,因此從發(fā)生局部電壓擾動到電容感知到這一擾動之間有一個(gè)時(shí)間延遲。

2023-11-22 15:39:23 761

761 去耦濾波電容怎么布局擺放,到底是先大后小還是先小后大?

2023-12-04 15:43:10 4108

4108

PCB去耦電容怎么放置?怎么選擇去耦電容? PCB(印刷電路板)去耦電容用于保持集成電路(IC)在運(yùn)行過程中的穩(wěn)定性,減少功率噪聲和干擾。它們通常由多個(gè)電解電容組成,安裝在布局上,以提供電源去耦

2023-11-29 11:03:19 2221

2221 在電子電路中,去耦電容和旁路電容都是起到抗干擾的作用,電容所處的位置不同,稱呼就不一樣了。對于同一個(gè)電路來說,旁路(bypass)電容是把輸入信號中的高頻噪聲作為濾除對象,把前級攜帶的高頻雜波濾除,而去耦(decoupling)電容也稱退耦電容

2023-12-10 14:26:02 2213

2213

在數(shù)字電路及IC控制器電路中,必須要進(jìn)行電源去耦。當(dāng)元件開關(guān)消耗直流能量時(shí),沒有去耦電容的電源分配網(wǎng)絡(luò)中將發(fā)生一個(gè)瞬時(shí)尖峰。這是因?yàn)殡娫垂╇娋W(wǎng)絡(luò)中存在著一定的電感,而去耦電容能提供一個(gè)局部的沒有電感的或者說很小電感的電源。

2024-01-10 15:31:13 949

949

去耦電容,也稱為去耦合電容或退耦電容,是電路中裝設(shè)在元件的電源端的電容。它的主要作用是為電路提供較穩(wěn)定的電源,并降低元件耦合到電源端的噪聲,間接減少其他元件受此元件噪聲的影響。

2024-02-18 15:20:35 1981

1981 去耦電容的作用是將信號電源引腳的輸出干擾作為濾除對象,防止干擾信號返回電源。

2024-02-20 15:55:59 2430

2430 去耦電容(Decoupling Capacitor)在電子電路設(shè)計(jì)中扮演著至關(guān)重要的角色,它們用于減少電源線上的噪聲,確保電路的穩(wěn)定性和性能。去耦電容的擺放位置和作用是電路設(shè)計(jì)中的一個(gè)重要考慮因素

2024-09-19 10:54:05 2175

2175 去耦電容,也被稱為退耦電容,是電路中裝設(shè)在元件的電源端的電容。它的工作原理基于電容器的基本原理,即通過兩個(gè)導(dǎo)體之間的電場來存儲電荷。當(dāng)電荷在電源線上發(fā)生波動或噪聲時(shí),去耦電容會吸收這些變化的電荷,從而保持電源電壓的穩(wěn)定性。

2024-10-10 15:19:08 2727

2727 去耦通過添加電容器減少電源噪聲,陶瓷電容因其高頻響應(yīng)好、ESR和ESL低,適合作為去耦電容器,提高電路穩(wěn)定性和性能。

2025-01-03 10:29:28 1864

1864

PCB設(shè)計(jì)電源去耦電容改善高速信號質(zhì)量?!What?Why? How?

2025-05-19 14:27:18 619

619

電子發(fā)燒友App

電子發(fā)燒友App

評論